#### **Future directions**

RCA's withdrawal from the general-purpose computer business intensifies the need for us to seek and achieve leadership in new fields of electronics and information technology. This is essential if we are to sustain a high long-term growth rate for RCA.

At the same time, in withdrawing from the commercial computer market, RCA is not turning away from computer technology. To the contrary, the engineering skills and knowledge that we have developed in this field over the past two decades must now support intensified research and development in data communications, specialized computer systems, and new information processing concepts and techniques for consumer as well as commercial and government applications. All of these constitute important areas of business which promise significant long-term profit growth for an alert and technically competent company.

Creative engineering is more essential today than ever in advancing RCA's position in all of our continuing operations—global communications, government and commercial systems, consumer products, components, and technical services across the entire spectrum of electronics. It will be a long time before the prospects are exhausted for substantial rates of business expansion in any of these fields.

Despite our structural changes in recent years, RCA is still a technologybased company, deriving over two-thirds of its volume and profit from electronic communications and information handling. We are, and intend to remain, a pace-setter in an electronics industry which should achieve a record domestic volume of more than \$26 billion in 1972—and even more if the economy regains its full health.

While we occupy a strong position in this industry, we cannot be complacent about it. We must reexamine our technological resources in the light of our new situation. We must then focus them more effectively than ever on development programs that will enable us to open new markets and enlarge our share in those we already serve.

Anthony L. Conrad President RCA

#### **RCA Engineer Staff**

#### Editor

Associate Editor

Assistant Editor Design and Layout

Editorial Secretary

Subscriptions

#### **Consulting Editors**

Technical Publications Adm., Electronic Components

Technical Publications Adm., Laboratories

Technical Publications Adm., Corporate Engineering Services

#### Editorial Advisory Board

VP, Technical Operations, Systems Development Division, Computer Systems

Mgr., Quality and Reliability Assurance, Solid State Div.

VP, Engineering, NBC Television Network

Mgr., Technical Information Services, RCA Laboratories

Manager, Consumer Products Adm., RCA Service Co.

Chief Engineer, Record Division

Chief Technical Advisor, Consumer Electronics

Div. VP, Technical Planning Electronic Components

VP, Engineering and Leased Systems, Global Communications, Inc.

Director, Corporate Engineering Services

Manager, Engineering Professional Development

Division VP, Government Engineering

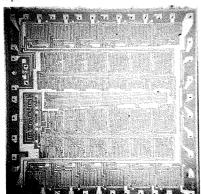

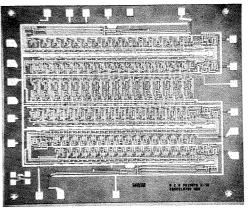

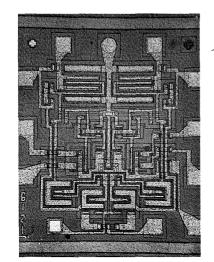

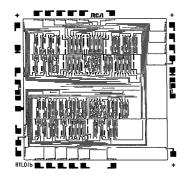

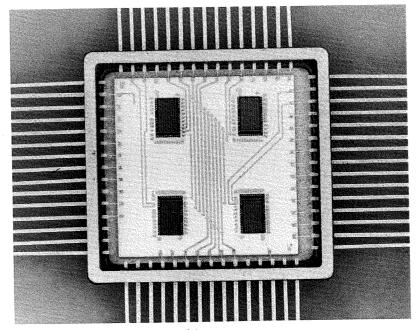

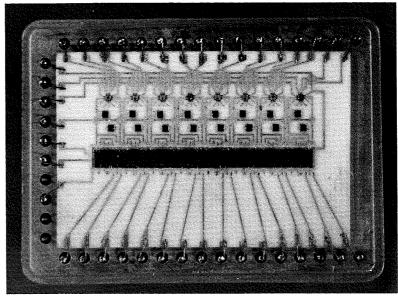

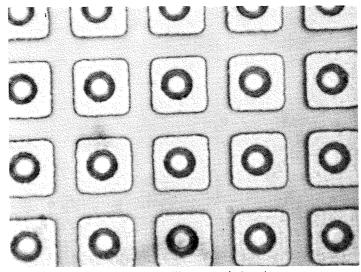

#### Our cover

... depicts a portion of the memory cells in silicon-gate PMOS beam-lead memory array. The array appeared on our last cover and is being repeated in different colors because of the large number of papers dealing again with solid state technology. **Photo credit:** John Semonish, Electronic Components, Clark, N.J.

.

Vol 17 | No 4 Dec 1971 Jan 1972

A technical journal published by RCA Corporate Engineering Services 2-8, Camden, N.J.

RCA Engineer articles are indexed annually in the April-May Issue and in the "Index to RCA Technical Papers."

#### Contents

## RGЛ Engineer

• To disseminate to RCA engineers technical information of professional value • To publish in an appropriate manner important technical developments at RCA, and the role of the engineer • To serve as a medium of interchange of technical information between various groups at RCA • To create a community of engineering interest within the company by stressing the interrelated nature of all technical contributions • To help publicize engineering achieve-

ments in a manner that will promote the interests and reputation of RCA in the engineering field • To provide a convenient means by which the RCA engineer may review his professional work before associates and engineering management • To announce outstanding and unusual achievements of RCA engineers in a manner most likely to enhance their prestige and professional status.

| Engineer and the Corporation | Engineering ethics and the consumer J. Hillier                                                             | 2  |

|------------------------------|------------------------------------------------------------------------------------------------------------|----|

| Papers                       | Simulation study for a circuit and message switch communication network.<br>K. Weir   P. Boehm             |    |

|                              | Basic time-sharing programs for business and long range plans R. R. Lorentzen                              | 1: |

|                              | Low-power COS/MOS memory system design J. R. Oberman   G. J. Waas                                          | 1  |

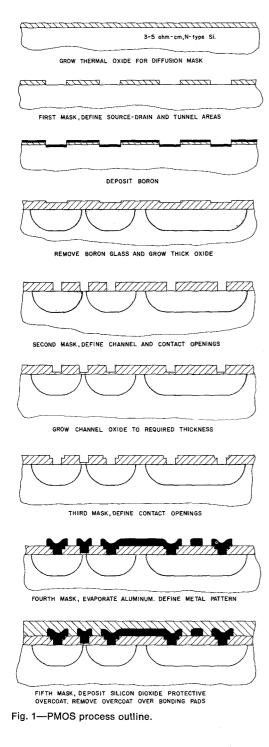

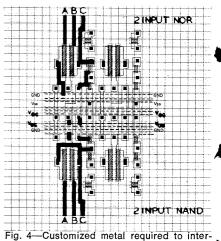

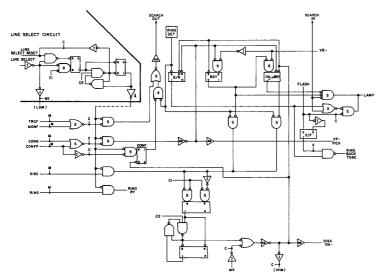

|                              | P-MOS technology for quick turnaround custom LSI T. R. Mayhew   K. R. Keller   H. Borkan                   | 2  |

|                              | Monolithic applications—divisional interface<br>R. H. Bergman   F. Borgini   L. Dillon, Jr.   G. E. Skorup | 2  |

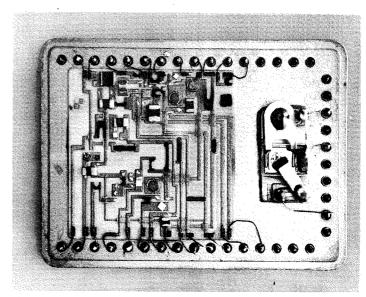

|                              | Hybrid packaging for high performance H. Fenster                                                           | 3  |

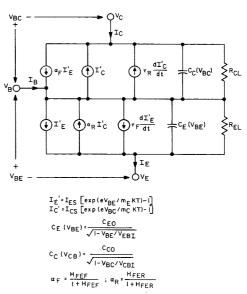

|                              | Digital simulation as a design tool C. B. Davis   Dr. J. C. Miller   Dr. L. M. Rosenberg                   | 3  |

|                              | Radiation-resistant COS/MOS devices L. A. Murray   Dr. J. M. Smith                                         | 4  |

|                              | Determining manpower for in-process inspection by use of queing theory J. Davin                            |    |

|                              | Books by RCA authors                                                                                       |    |

|                              | Silicon mosaic target—blending semiconductor and camera tube technologies A. D. Cope                       |    |

|                              | Automated design operations: a profile J. P. Le Gault                                                      | ;  |

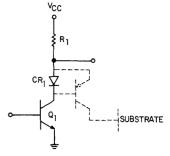

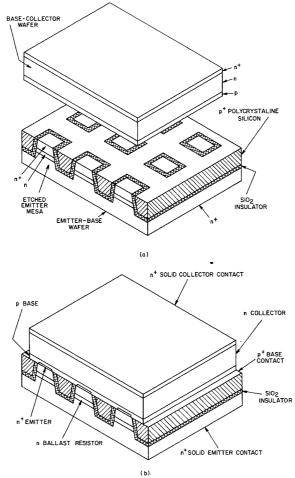

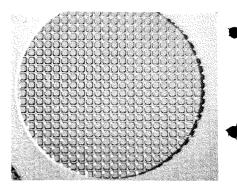

|                              | High-voltage laminated overlay power transistors<br>R. Amantea   H. Becke   P. Bothner   J. White          |    |

|                              | Trends in reliability engineering V. Lukach                                                                |    |

|                              | Schottky barrier devices R. T. Sells                                                                       |    |

|                              | Submitting to UL for safety D. K. Obenland   F. E. Korzekwa                                                | 1  |

|                              | There's more to typesetting than setting type P. E. Justus                                                 |    |

|                              | Central computer system—a manufacturing cost saver S. V. Cianfrone                                         |    |

| Notes                        | Single-transistor regulated fluorescent inverter J. Sondermeyer                                            | •  |

|                              | Measuring input impedance of ECL devices R. Au                                                             |    |

| Departments                  | Pen and Podium                                                                                             |    |

|                              | Patents Granted                                                                                            |    |

|                              | Dates and Deadlines                                                                                        |    |

|                              | News and Highlights                                                                                        | *1 |

Copyright 1971 RCA Corporation All Rights Reserved

#### The Engineer and the Corporation

### Engineering ethics and the consumer

**Dr. James Hillier**

I firmly believe that the lots of the consumer and the engineer have been steadily improving in the past 25 years because of natural correcting forces that have become built into our "system." I am worried that the present emphasis on "consumerism" will disrupt the natural correcting forces by replacing them with various forms of regulation. Again, I have no illusions regarding the fact that the absolute number of faulty products is too high. But the method of attacking the problem without completely understanding the system or the variations in it and by assuming that all industry is equally guilty, can only work to the detriment of the consumer in the long run.\*

Editor's note: In this era of the "consumer movement," the accusations leveled at industry have ranged from complaints of shoddy products to collusion in the suppression of advanced developments and even to the charge that potentially hazardous merchandise is knowingly put on the market. These indictments have even carried implications of a deeper, moral issue—that they are the result of corporate suppression of the professional integrity of engineers.

To examine the role of "engineering ethics" in industry, *The Cornell Engi*neer, an undergraduate magazine, conducted a survey to get views, opinions, and perspectives on the "real world" of business. A thought-provoking reply to this survey (published in the March 1971 issue of *The Cornell Engineer*) came from Dr. James Hillier, Executive Vice President, RCA Research and Engineering, Princeton, N.J. The questions in the survey and Dr. Hillier's responses are presented in this article.

In evaluating the queries, Dr. Hillier expressed his concern about the nature of the questions themselves. They could be construed "to be 'loaded' to the extent that 'knocking' the system would appear to be the only possible response." Or, "if the questions are 'straight' and prepared in innocence, they expose a naivete, or worse, create a fear about the

education, image, or propaganda mechanisms that give students such an incomplete and distorted view of the business world."★

Although the Cornell survey results are directed toward Cornell's engineering undergraduates, the issues are real and fundamental, and Dr. Hillier's perspective of the business world will be of interest to RCA's research and engineering community.

The questions asked in the survey are italicized.

RCA Reprint RE-17-4-23

<sup>★</sup> From a letter by Dr. Hillier to the editorial staff of *The Cornell Engineer*.

The dictionary defines ethics as "the standards of conduct and moral judgment of a group." What is your definition of engineering ethics?

My view of proper engineering ethics requires that an engineer have as his basic objective the designing of a product that gives the customer the best possible value for his money. In so doing the engineer must be concerned with the following:

a) Providing the best possible performance in a product to accomplish its intended purpose consistent with economic and other constraints.

b) Achieving a manufacturing cost of the product that is low enough to enable the manufacturer to provide reasonable pay for all his employees and a reasonable profit for the owners of the business so that the enterprise can continue to serve its customers and can continue to provide employment.

c) Taking every reasonable precaution to be certain that the product is not and will not become hazardous in any way or present an undue safety problem.

Does your company's selection process try to determine the "ethics" of prospective engineers? Why or why not?

Our company's selection process for prospective engineers concentrates on trying to determine their competence and creativity in the engineering fields related to our needs. We assume that a prospective engineer has acceptable engineering ethics. The total hiring process-application forms, reference checks, etc .-- that is quite standard for most industry has evolved over many years and has many implicit checks on ethics such as honesty, forthrightness, responsibility. We do not knowingly hire people when dishonesty or irresponsibility has been revealed in their past.

Does your company have seminars on engineering ethics? Does your company have codes or guidelines for engineers?

RCA does not have seminars on the specific subject of engineering ethics. However, we do have seminars and training courses on subjects that have an engineering ethics connotation such as Value Engineering and Analysis, Product Assurance, Product Safety, Product Reliability, and Product Quality. The Company has a comprehensive and continually evolving set of policies, procedures and guidelines that apply to all employees including engineers. Included in these are many that are specific to engineers.

When your company decides to manufacture a new product, how does it analyze its cost versus its quality? (For example: if for an increase in cost, your company can produce a superior product, what factors will go into choosing alternatives?)

Technology-dependent manufacturing companies fall into two distinct categories.

a) Those providing consumable materials.

b) Those providing products that, in turn, provide service to their customers.

RCA falls into the latter category for which the question is over simplistic and probably naive.

#### The fundamental and ultimate determinants of "quality" are the total service provided to the customer... and the total cost.

The fundamental and ultimate determinants of "quality" are the total service provided to the customer by the product and the total cost per unit time to the customer for that service. Thus life expectancy of the product and the frequency and cost of maintenance have to be included in "quality" in addition to technical level of performance. There are many other factors that also must be included.

The price the customer is willing to pay for the product is very dependent on the value he places on the service provided relative to his need for it. The price he must be charged is sensitively dependent on the number of customers willing to pay it. Thus the analysis of cost (manufacturer's) versus quality is only a small part of the total analysis that must be made. ... best "value" for the customer is usually the best business for the manufacturer...

Some of the relationships to be considered are:

- a) Volume versus price to customer.

- b) Manufacturing cost versus volume.

- c) Technical performance versus cost.

- d) Life expectancy versus cost.

- e) Volume versus technical performance at given customer price.

- f) Fixed initial investment in engineering versus the product-price times volume.

- g) Competitive offerings, etc.

It is to be noted in most of these relationships that the challenge transmitted to the engineers from management is always to provide the best possible quality at the lowest cost.

The specific example quoted can be used to illustrate the traps in simplistic thinking. Consider the case of a product that has a life expectancy of five years and a "superior product" that has a life expectancy of ten years but requires a price that is double or nearly so. We shall assume all other things are equal. From the customer's point of view the alternatives appear nearly equal. The cost per unit time for the service is the same in each case. The inconvenience of having to buy a second unit after 5 years is balanced by the added flexibility and the possibility of technical improvements occurring in the first five years. From the manufacturer's point of view the alternatives also appear nearly equal. The profits over the ten-year period are equal. The high immediate double profit on the ten-year product being balanced against cost reductions and competitive reactions that could occur when the five-year products have to be replaced.

All of this is correct in a fundamental and theoretical sense. In the "real world" the double price of the "superior product" would drastically cut the volume. The cost of production would be increased to such an extent that the increased life expectancy would have to be cut back to the point where it might not be significantly greater than the five-year product. Then the cost per unit time of service to the remaining customers would be considerably higher than if only the five year product had been offered at the original price.

This very elementary example illustrates what I believe is a more general principle—what is best "value" for the customer is usually the best business for the manufacturer, and the best "value" for the customer is not necessarily that provided by the "superior product" in a conventional engineering sense.

Similarly, when your company decides to manufacture a new product, how does it analyze production or process cost versus percent that will be defective and not "caught" before shipment?

I do not like the inference in this question. While it is true that statistical testing methods are used in our company for the testing of many components that go into our products, the manufacturing process is always designed to give the final product a 100% test for operation within specifications. The output is further checked, this time statistically, by a quality control group that is administratively independent from the production group. This general procedure has been used in every large company with which I have been familiar.

Symbolic of RCA's commitment to purchaser satisfaction, the "PS" on RCA color televisions assures customers that defects in the set will be repaired free of charge by RCA within one year from the date of sale.

Any time a company "plays games" with a product to raise sales, there is always a competitor waiting to play the other side of the game.

Every manager knows that the direct cost of repairing a defect after a product is sold is 20 to 50 times greater than detecting and repairing it in the factory. The additional and indirect cost arising from customer defection is much higher.

This does not mean that none of our products ever have defects. They are still designed by human beings, built by human beings, inspected by human beings, transported by human beings, and used and mis-used by human beings none of whom is perfect.

... the positive approach of designing, producing and testing products that are absolutely safe and not prohibitively expensive presents many extremely challenging engineering problems.

The same question for products that are potentially harmful if defective (such as car brakes).

The inference here that any large responsible manufacturer would knowingly permit potentially hazardous defects to exist in its products as a cost saving measure is incredibly naive. There is enormous economic incentive to do exactly the reverse. Any such cost savings are invariably trivial compared to the liability costs of the hazard and the concomitant loss of customers.

On the other hand, the positive approach of designing, producing and testing products that are absolutely safe and not prohibitively expensive presents many extremely challenging engineering problems.

Industry sometimes finds that its products are too good, that they do not wear out or fail for years. Therefore, the company finds sales falling as people only need buy the item once (case in point, the original run-proof nylon stockings.) The company then decides to shorten the life of the product to raise sales, a form of planned obsolescence. Who decides this in a corporation and what factors enter into this decision?

I disagree strongly with the basic premise implied in this question. It again shows a sad lack of understanding of the realities of the business world. Any time a company "plays games" with a product to raise sales, there is always a competitor waiting to play the other side of the game.

In spite of many statements to the contrary, competition in our business (and, in fact, in most businesses) is very intense and very real. This is the strongest and best form of protection the consumer has. As I have indicated elsewhere, outside regulation often tends ultimately to work to the disadvantage of the consumer.

Obviously the wrong inference is drawn from the example given. Sheer but fragile nylon stockings have replaced the heavy run-proof ones not because of any ethical or non-ethical decision by an engineer, but because a majority of women like the way sheer stockings look on them and are willing to accept the penalty of shorter life. Certainly one cannot sensibly argue that it is an engineer's ethical concern to insist that his customer buy what the engineer considers is technically, economically, or for that matter, spiritually best for the customer, no matter what that "best" product may do to the customer's id, ego, or super ego. Certainly, if women wanted the original run-proof versions, a competitor would have grown big supplying them.

Seriously though, we do feel it is both ethical engineering and good business to make yesterday's product less desirable by putting today's technical achievements in our products and thereby make them more desirable to our customers. Again, if we did not, a competitor would.

A case in point is the rectangular tube that replaced the round tube in color rv receivers. It took some solid, costly engineering to perfect that tube so that it could be made available commercially at a reasonable price. It provided the customer with a better looking rv set that had a better picture, and it increased the sales of color rv receivers. The overall result was more value for the customer, more profit for the business owners, and more stable employment for the engineers.

I am not trying to say that all the products of all large companies are always perfect or even good values. As with people, ethics and other characteristics vary from one corporation to another.

As with people, ethics and other characteristics vary from one corporation to another. However, in general, customer consciousness is good business and it tends to be highest with large corporations (one of the reasons they grow to be large) and lowest for the "schlock" or "fly-by-night" houses. Yet, it is still possible to pay more and get a "lemon" from a large<sup>-</sup> company and pay less and get a real "buy" from a small one.

If your answers indicate that you feel that industry regards the consumer as king, how do you explain the greaf number of faulty products, the shoddy construction, fraudulent claims and other forms of what we consider consumer fraud present today? If your answers indicate that you feel that industry holds a "consumer be damned" attitude, how can the situation be improved or do you feel it should be?

In my answers I have tried to indicate that to consider the consumer as king is simply good business. Speaking as a consumer, I have observed a steady improvement in the performance and quality of the manufactured products I buy. I agree that faulty products and shoddy construction still exist, but I believe it is on a relatively smaller scale.

As I indicated in the preceding question, there is a range of customer consciousness that can be very low in some types of organizations. However, I do not believe all manufacturers should be "tarred with the same brush."

Similarly there is a range of selling approaches that runs from putting one's product "in the best light" to outright misrepresentation. Here, too, for whatever reason, I have observed a steady improvement.

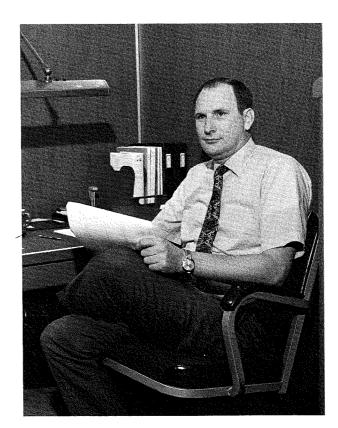

#### **Dr. James Hillier** Executive Vice President Research and Engineering, RCA

studied at the University of Toronto, where he received a BA in Mathematics and Physics in 1937, MA in Physics in 1938, and PhD in Physics in 1941. Between 1937 and 1940, while Dr. Hillier was a research assistant at the University of Toronto, he and a colleague, Albert Prebus, designed and built the first successful high-resolution electron microscope in the Western Hemisphere. Following this achievement, Dr. Hillier joined RCA in 1940 as a research physicist at Camden, N.J. Working with a group under the direction of Dr. V. K. Zworykin, Dr. Hillier designed the first commercial electron microscope to be made available in the United States. In 1953, he was appointed Director of the Research Department of Melpar, Inc., returning to RCA a year later to become Administrative Engineer, Research and Engineering. In 1955, he was appointed Chief Engineer, RCA Industrial Electronic Products. In 1957, he returned to RCA Laboratories as General Manager and a year later was elected Vice President. He was named Vice President, RCA Research and Engineering, in 1968, and in January 1969 he was appointed to his present position. Dr. Hillier has written more than 100 technical papers and has been issued 40 U.S. patents. He is a Fellow of the American Physical Society, the AAAS, the IEEE, an Eminent Member of Eta Kappa Nu, a past president of the Electron Microscope Society of America, and a member of Sigma Xi. He served on the Governing Board of the American Institute of Physics during 1964-65. He has served on the New Jersey Higher Education Committee and as Chairman of the Advisory Council of the Department of Electrical Engineering of Princeton University. Dr. Hillier was a member of the Commerce Technical Advisory Board of the U.S. Department of Commerce for five years. He was elected a member of the National Academy of Engineering in 1967 and is presently a member of its Council.

Most engineers, including myself, welcome continued pressure for improvement in both these areas. However, the pressure should be intelligent and realistic rather than a sequence of crusades, often politically motivated. The consumer should also recognize that ultimately he has to pay for all the advances in quality and safety. As I indicated in the earlier questions, this could lead to the customer obtaining less value per dollar and, ultimately, to less employment.

Are the "ethics" or policy of a company forced upon its engineers? Please give examples if possible.

Any large company with integrity requires that its engineers abide by its standards of ethics. There is no other way for it to provide the customer with products that meet its standards of quality and value.

I object to the word "forced" and the implications that a company's "ethics" and policy are always distasteful to engineers. This again shows a lack of understanding for the "real world." Large companies that are dependent on technology and have grown during the past twenty-five years have done so in a long period of extreme shortage of good engineers. It goes without saying that no engineer had to work for a company with whose ethics and policy he disagreed. While the situation is generally different today, it really has not changed for the best engineers who are still in short supply.

In other words, on problems of ethics, policy and freedom it has been "good business" for a company to have policies acceptable to the majority of engineers. Here again, I have to recognize that this situation varies from company to company. However, I doubt if any company that has grown large in a period that covers several generations of engineering graduates could have done so with distasteful engineering ethics and policies.

... pressure should be intelligent and realistic rather than a sequence of crusades, often politically motivated. If an engineer feels that a project he is working on is "unethical" and he therefore refuses to continue working on it, will he be fired? Please give examples if possible.

No—we respect individual's desires. If an engineer in our company is doing work on a military project and decides that his project has taken a turn that he considers unethical, he will certainly be replaced on that project. Whether he would be retained by the company would depend on the availability of a suitable opening on a project acceptable to the employee.

During World War II several "conscientious objectors" refused to work on military projects. Other projects were found; all the individuals I knew about are still with the company nearly thirty years later.

Do you feel that an outspoken advocate of ecology can get a job in industry?

Speaking for our own company, it depends on whether the "outspoken advocate of ecology" is destructive or constructive. The outspoken advocate of ecology who simply vilifies the "establishment" for the pollution mess, would not be welcome. On the other hand the outspoken advocate of a solution to the pollution mess would be welcome if the solution were relevant to our business.

Referring back to the four responsibilities an engineer should feel, which would you place first in importance and why? (Viz "moral responsibility to themselves, the engineering profession, then eventual employers, and their society.) Secondly, in a given situation, how do you evaluate what to do?

I think the engineer's primary feeling of moral responsibility has to be to himself. I do not want anyone working for me who feels that what he is doing is morally wrong. If a man is not honest with himself, then he will not be honest with his employer, his profession, nor, I believe, with society. ... convincing oneself that a true "ethical conflict" exists is often the most difficult part of the problem.

A man's moral responsibility should be to society next, and then to the two specific segments of society you mention, his eventual employer and his profession, and I don't see much point in trying to order the importance of the last two. A man who is morally responsible to himself and to society will be morally responsible to both his profession and his employer.

Presumably the "given situation" mentioned in this question refers to one of ethical conflict between the engineer and his employer. Perhaps the most difficult step in evaluating what to do is to first determine that it is truly an ethical conflict.

Is your employer really asking you to design an inferior product or do you have a hang-up because he's doing some judicious cost-cutting that eliminates some of your sophisticated engineering that unfortunately the customer is not willing to pay for? (As an aside, I would like to emphasize that sophisticated engineering does not necessarily mean safer or even better engineering.)

In practice, convincing oneself that a true "ethical conflict" exists is often the most difficult part of the problem. Value judgments have many shades of gray and the paycheck and all it represents have been known to warp men's judgments.

But if a man is honest with himself and is truly convinced that he is being asked to do something that is morally wrong, his path along the following lines should be clear.

a) Attempt to convince his superior and the management of the company that the company is asking for something unethical and that it should change to an acceptable ethical practice or procedure.

b) Failing this, the engineer should either ask to be transferred or resign his position, depending upon his conscience.

c) If he has a good reason to believe the company is doing something that is illegal as well as unethical, he should report this to the proper governmental authorities.

#### Kendall Weir

#### Government Communications Systems Communications Systems Division Camden, New Jersey

received the BSEE from Pennsylvania State University and the MSE from the University of Pennsylvania. Mr. Weir joined RCA in 1958 and has worked in various activities mainly concerned with Systems Assurance (i.e. Reliability, Maintainability, Availability; Systems Effectiveness, Safety, and Life Cycle Costing). Mr. Weir has worked on Techniques Development during study contracts, implementation of these techniques on small equipment and large system contracts, and administration of the implementation of these techniques during Project Management Office assignment. He is currently working in a Systems Engineering Activity as part of Information Processing and Control Systems. He is a member of Tau Beta Pi. Sigma Tau, and Eta Kappa Nu.

## Simulation study for a circuit and message switch communication network

K. Weir | P. Boehm

Simulation of complex electronic switching systems requires the use of many variables in the mathematical model which represents a particular system. The complex structure of the model dictates the use of a computer to facilitate calculations. This paper describes such a simulation which provides for an examination, evaluation, and manipulation of the system without any direct action on the system itself or on a physical model of the system.

#### Paul Boehm

#### Government Communications Systems Communications Systems Division Camden, New Jersey

received the BEE from Ohio State University in 1951. At RCA, Mr. Boehm has been active in the field of data processing systems and communication systems. He has participated in both a supervisory and working capacity in the generation of system concepts, the generation of functional and design specifications, the implementation of designs to meet these specifications, and the preparation and conduction of system tests on completed machines to verify performance. Mr. Boehm spent one year in Canada as a consultant

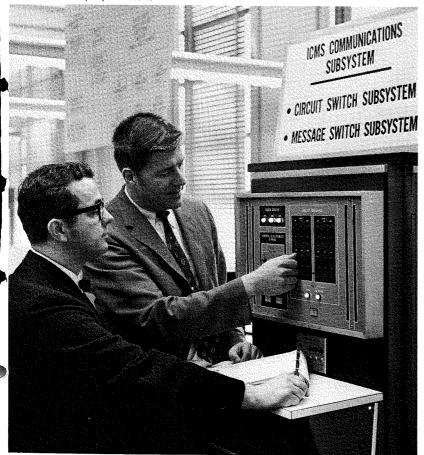

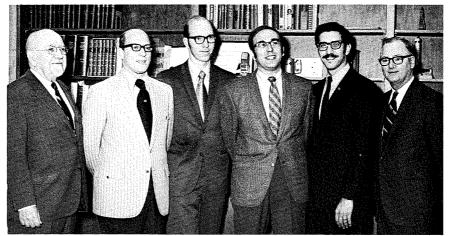

#### Authors Boehm (left) and Weir.

for the Canadian government assisting in the specification of a large, multi-node digital communication system. Mr. Boehm participated in the development of the requirements for a highlyparallel computer of the ILLIAC IV-type for use in an adaptive phased-array radar environment. In a one-year study and investigation of a combined circuit switch and/or store-and-forward switch for digitized voice or digital data, Mr. Boehm was responsible for the implementation of the system requirements on the software and hardware of the central control computer(s). As one part of the extension to the study, Mr. Boehm simulated a communication network on an RCA Spectra system using the FLOW SIMULATOR language.

THE PAYOFF for every technological system comes when the user is able to operate it in its intended manner. This settles beyond doubt that the system requirements have been satisfied. The design is a success. If this does not happen, the system is a failure. It must be redesigned or re-configured with associated added costs. When this happens, the additional cost may be such that the system loses its value to the user. He may want such a system, but cannot afford it.

An aircraft is well designed when it is loaded, becomes airborne, and flies to its destination. But the risks involved in proving out the design at this point are horrendous. Consequently, in the course of the aircraft design, various scale models are constructed which are subjected to scaled-down stresses in an endeavor to determine how this model will react. The accuracy built into this model to simulate what the actual aircraft will be like and the accuracy of the stresses imposed on it determine the probability of the test simulating the actual aircraft. Every aircraft is subjected to such simulated tests, but sometimes aircraft fail in actual flight. This is simply because the accuracy of the simulation is not very good. This type of simulation is a physical model of the intended design and is a step to a more generalized type of simulationthe mathematical model. A mathematical model is simply a mathematical equation which represents the

Reprint RE-17-4-24

Final manuscript received February 12, 1971

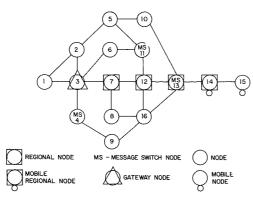

Fig. 1—16-node network.

strengths and stresses of the system to be proven. Thus, in its simplest terms, simulation is an endeavor to imitate mathematically what is actually the system design.

Stated more precisely, simulation is a problem solving technique which structures a mathematical model and observes model changes with time. It can derive new information as to performance by manipulating relationships between variables. In some technological systems, such as a complex electronic switching system, the simulation would require many variables to represent the system and it would be necessary to use a computer to facilitate calculations.

Consider a communications switching system which is capable of handling voice or data lines and can accept circuit-switched (CS), message-switched (MS), or optional messages (MSO). Circuit-switched messages cannot be stored and, therefore, are lost when a connection cannot be made. Message-switched messages are stored at least once and can be stored and forwarded in the event a connection cannot be made. Optional messages are either circuit switched or message switched. They are handled as circuit-switched messages unless a connection cannot be made at which time they are handled as message-switched messages. The model which will simulate the operation of this communication switch will produce outputs such as delay times for signalling, lost call statistics, summary statistics for circuit-switched messages, and the time in the system for message-switched messages. The

mathematical model for the switching system is programmed using the RCA FLOWSIM Simulation Language and has been run on an RCA Spectra 70/45 computer.

The work performed in the simulation study is divided into four parts. The structuring of the simulation model is described, program flow diagrams are shown, the simulation runs are identified, and finally the results obtained from the work already completed are given.

#### **Simulation model**

The system operating parameters used in the simulation model include:

Network size Trunk capacity Message priorities Message destination percentage Traffic Message types Message routing Trunk and node outages Mobile subscribers and nodes

Each of these parameters is described separately below and their relationship to the simulation model is given.

#### Network size

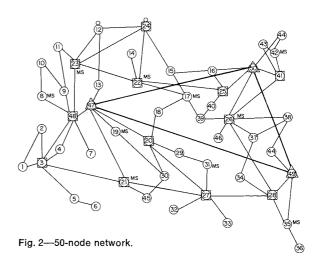

A 16-node network and a 50-node network (Fig. 1 and 2, respectively) were simulated. These networks were entered as input data in the form of connectivity matrices rather than as part of the program structure. Each node in each network simulates a communication switch.

#### **Trunk capacity**

Trunks are the connecting paths between nodes and consequently limit traffic flow between nodes depending on their size. Signalling is "in-band,"\* hence, signalling and supervision data will utilize part of the network trunk capacity. Trunk capacity is specified in terms of the number of simultaneous voice, data, and supervision signals that can be handled. Simulations are run with unlimited trunk capacity to measure trunk utilization. Having measured trunk utilization, further simulations are run at that utilization level.

#### Message priorities

Since a communication switch will always have call priorities, such priorities will be assigned for simulating a real situation. Five priorities were used; the percentage of messages assigned to each of the priorities is as follows:

| Priorities           | Percent of messages | Cumulative<br>percent of<br>messages |

|----------------------|---------------------|--------------------------------------|

| 5 (highest priority) | 1                   | 1                                    |

| 4                    | 3                   | 4                                    |

| 3                    | 15                  | 19                                   |

| 2                    | 31                  | 50                                   |

| 1 (lowest priority)  | 50                  | 100                                  |

These priorities are based on previous experience and will be used throughout the simulation.

#### Message destination percentages

Messages are categorized as to their destinations and from this each destination will be assigned a numeric which gives its percentage of the total messages transmitted. To facilitate simulation, the message destination

\* In-band signalling is a term used to describe the use of the same frequency band for both signalling and supervision information and voice and data information transfer. percentages will be assumed to be as follows:

- Messages local to originating node (25%)

- Messages to immediately adjacent nodes (15%)

- Intra-net messages (35%—split equally by nodal distance from originating node)

Messages to mobile subscribers (5%) Messages to mobile nets (10%) Inter-net messages (10%)

With normal traffic of 0.25 erlangs<sup>\*\*</sup> per subscriber, it will be assumed that 25% of all attempted calls will get SUBSCRIBER BUSY.

#### Traffic

Traffic refers to the rate that messages are generated and introduced into the node processing program. Four variations in traffic are included in the simulation runs:

Normal traffic

Reduced traffic (0.8 x normal)

- Increased traffic (1.2 x normal)

- Variable traffic (normal traffic with occasional peak loads)

Normal traffic is further defined as:

- All messages will be generated by subscribers

- All subscribers will generate the same traffic

- The number of subscribers per node will be rectangularly distributed between 200 and 500

- The mean time between message originations will be 200 seconds per subscriber with an exponential distribution

- Voice messages will have a mean duration of 180 seconds

- Data messages will have a mean duration of 15 seconds

- Message durations will be exponentially distributed.

#### Message types

There will be seven message types with a percentage of messages assigned to each type for all simulation runs. These are:

Data Messages (70.0%)

- Multiple address circuit switched (2.0%)

- Single address circuit switched (22%) Multiple address message switched (2.0%)

- Single address message switched (22%) Single address optional (22%)

Voice Message (30.0%) Conference calls (6.0%) Two party calls (24%)

\*\* Erlang is a unit of measurement for traffic intensity and is equal to total circuit usage during an interval of time divided by the time interval. Additionally, multiple address messages including conference calls involve 3, 4, or 5 subscribers each having a probability of occurrence of  $\frac{1}{3}$ . This means that one third of the multiple address messages will involve three subscribers; one third, four subscribers; and one third, five subscribers.

#### Message routing

Message routing is concerned with the route a message will follow from its origination node to its destination node. In the simulation, fixed message routes are utilized. There is one primary path and one or two secondary paths established for communication from any node to any other node. If a connection cannot be made using a primary path, the secondary path (s) is tried. If a connection still cannot be made, the message is stored and forwarded later or lost depending on the message type. Adaptive routing schemes are planned for future simulation runs. With adaptive routing the message route may be modified at any time based upon the then extant system operating conditions.

#### Trunk and node outage

Trunk/node outages will be simulated in some of the simulation runs by providing additional input information which will indicate which trunk/node(s) are to be removed from the net. The simulation program will take trunk/node outages into account when calculating message routes or paths.

#### Mobile node and subscriber

Within the system concept, a mobile node is one which moves geographically,\*\*\* taking most or all of its subscribers with it. (A mobile subscriber is a subscriber who does not stay associated with a particular node.) The relative location of all nodes and subscribers is known and stored in regional nodes. When a subscriber or node moves, the new location is transmitted to regional nodes rather than to all nodes. Some simulation runs include mobile subscribers and nodes to evaluate transient conditions between the stable system periods before and after the moves.

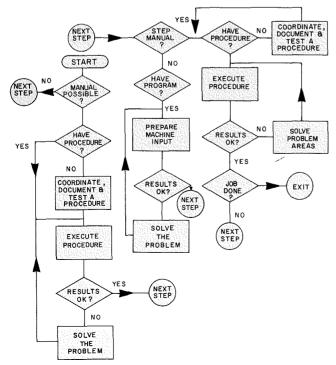

#### **Program Flow diagrams**

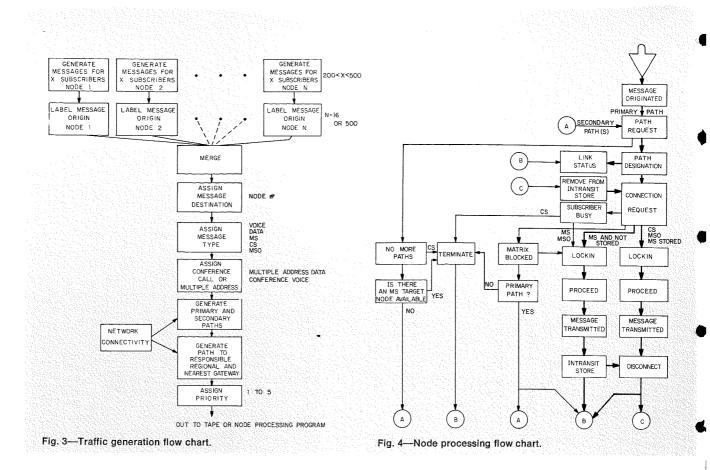

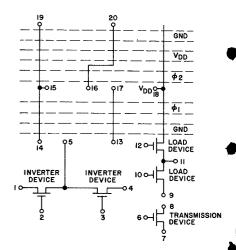

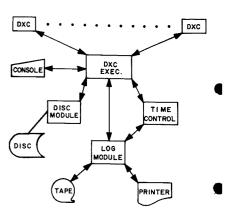

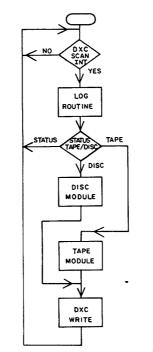

Since the simulation of the switching system is logically subdivided into traffic generation and nodal processing, it was decided that separate programs should be written to handle traffic generation and node processing. The output of the traffic generation program will serve as the input to the node processing program. Separating the two programs allows the traffic generation program to be run once, the results stored on tape, and these results used with almost all node processing program runs. This approach, therefore, reduces the computer processing time and cost when compared with several system simulations using a single program. Traffic generation and node processing program flow diagrams are shown in Figs. 3 and 4, respectively.

#### The traffic generator

The traffic generation program provides an output which is a list of transactions representing messages or traffic to be handled. As shown in Fig. 3, transactions are initiated in "generate blocks," each representing a system node and each transaction representing a message. Each node has an assigned number of subscribers rectangularly distributed between 200 and 500. It is assumed that each subscriber generates the same traffic. Therefore, the number of messages (transactions) per unit time initiated at each node "generate block" is directly related to the number of subscribers. Each subscriber generates messages in accordance with the exponential distribution with a mean of 200 seconds. A fixed percentage of messages are assigned as voice or data messages; as circuit-switched, message-switched, or optional messages; and as single-address (two party call for voice messages) or multiple-address messages (conference calls for voice messages). Message destinations are also assigned on a fixed percentage basis. The traffic generator then determines, based on network connectivity, a primary transmission path from the originating node to the destination node. Additionally, the path to the nearest regional and gateway nodes are identified. Message priorities are then established which completes the required information concerning messages.

<sup>\*\*\*</sup> A mobile node which moves geographically is typically a communication van in the front lines or a ship at sea. A mobile subscriber would typically be the President, or a general.

#### Node processing

Fig. 4 presents a node processing flow diagram or the sequence of signalling required for a single transaction from its initiation to its completion. The paths indicated with heavy arrows represent normal operation and the other paths represent contingency paths which include:

a) Matrix blocked (insufficient node crosspoints or node outage).b) No more paths (insufficient trunk lines or trunk outage).c) Subscriber busy.

#### Normal operation

When a message has been originated, the PATH REQUEST is made to the appropriate regional node (see Fig. 4). This regional, after determining a primary path considering the existing status of the network, transmits the PATH DESTINATION to the originating node and updates the LINK STATUS (reserves the path designated for transmission). At the originating node, the path information is modified to become a CONNEC-TION REQUEST and is transmitted. When the terminating node receives the CONNECTION REQUEST and it is a CS or MSO message, a LOCKIN is transmitted back to the originating node, which in turn signals the subscriber to PROCEED. Following the information transfer (MESSAGE TRANS-MITTED), a DISCONNECT breaks down the matrix connections and another housekeeping message is transmitted to update the LINK STATUS. For an MSO message, DISCONNECT also releases another message from INTRANSIT STORE if a message has been stored.

For MS messages, the CONNECTION **REQUEST** is transmitted to the responsible MS node. Upon receipt of the CONNECTION REQUEST, A LOCKIN is transmitted back to the originating node, who in turn signals the subscriber to proceed. The message is transmitted to the responsible MS node, stored, and placed on INTRAN-SIT STORE (a permanent record is made). It remains there until the completion of another call (DISCON-NECT). At DISCONNECT, the oldest message is removed from INTRANSIT STORE and now represents a new con-NECTION REQUEST. This request is handled as though it were a CS or MSO message unless it encounters a MATRIX BLOCKED OF BUSY SUBSCRIBER.

#### Contingency paths

There are three contingency paths or exceptions to normal operation; namely MATRIX BLOCKED, NO MORE PATHS, and SUBSCRIBER BUSY.

When a MATRIX BLOCKED condition occurs, the next action depends on the type of message. For CS messages or for other type messages that are blocked before an MS node, a request for a secondary PATH REQUEST is initiated. If a secondary PATH REQUEST has already been tried, the message will be lost. If the message was not a CS message and an MS node was reached, a LOCKIN is obtained and the message is transmitted from the originating node to the furtherest MS node from the originating node. The message is then stored and placed on INTRANSIT STORE.

When the termination node is reached and a SUBSCRIBER BUSY is obtained, CS messages are lost. MS and MSO messages are transmitted to the closest MS node to the termination node along the designated path. The message is stored and placed on INTRAN-SIT STORE. INTRANSIT STORE messages are taken out of storage and an effort is made to transmit them every time another message is completed. These messages are handled as CS messages unless problems are encountered.

When NO MORE PATHS are available, CS messages are lost. MS and MSO messages request a path to a "target" MS node. A target MS node is any MS Table I-Simulation runs

|   |                                                     |                                                          |                                                     |                                                                         |                                                               | Syst                                                          | em o                                      | pera          | ting | r con | dition                                                   |                                                               |                            |                                                |                  |   |                                           |                  |           |

|---|-----------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------|---------------|------|-------|----------------------------------------------------------|---------------------------------------------------------------|----------------------------|------------------------------------------------|------------------|---|-------------------------------------------|------------------|-----------|

| 6 | Simulatic<br>run                                    | Network<br>size<br>(note A)<br>1 2                       |                                                     | runk<br>ipacity<br>1 Unlimited                                          | Fixed<br>message<br>priority<br>percent                       | Fixed<br>message<br>destination<br>percent                    |                                           | Trafj<br>(not |      | 4     | Fixed<br>message<br>type<br>percent                      | rou                                                           | sage<br>ting<br>te C)<br>2 | None                                           | Outage:<br>Trunk |   |                                           | Mobilit<br>Subs. | y<br>Node |

|   | A<br>B<br>C<br>D<br>E<br>F<br>G<br>H<br>I<br>J<br>K | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | x<br>x                                                                  | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | x             | x    | x     | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | x                          | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | x                | x | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | x                | x         |

|   | 1                                                   | A. Network si<br>—16 Nodes<br>2—50 Nodes                 | ze                                                  | <i>B. Traffic</i><br>1—Normal<br>2—Reduced<br>3—Increased<br>4—Variable |                                                               | C. Message<br>1Determi<br>2Adaptive                           | nistic                                    |               |      |       |                                                          |                                                               |                            |                                                |                  |   |                                           |                  |           |

node in the path closer to the destination node than to the originating node. Moving the message toward the destination node tends to reduce the blocking probability and message delay in the system. If there is no available target MS node, the MS or MSO message is stored at the originating node until a path is available. If a path to a target MS node is available, the message is transmitted to the target MS node, stored, and placed on IN-TRANSIT STORE.

#### **Simulation runs**

The system operating conditions are varied in the various simulation runs to determine the effect of those changes on selected performance parameters. Table I depicts the planned simulation runs indicating the specific operating conditions to be varied. The system performance parameters which are examined in each simulation run are shown in Table II.

#### **Results of simulation study**

The results of the work described are not complete in themselves. They do, however, give useful immediate results and also permit general conclusions to be drawn.

The traffic generation program works. It is currently being used in conjunction with other programs to estimate the R-100 processors traffic handling capability. Its input variables are readily changed to represent difficult systems and operating conditions. Its output provides a chronological list of messages with all associated pertinent information as follows: Time of message initiation Message priority Message type Message origin Message destination Primary and secondary paths from origin to destination Path to the nearest gateway node Path to the responsible regional node

A signalling and supervision concept for a message- and, circuit-switched communication system was developed. The sequence and specific signalling and supervision messages utilized in control, management, and connection of subscribers are delineated. Hence, this concept is of use in the design of both hardware and programs for communication systems.

Table II---System performance parameter

#### Standard output

- 1. System operating conditions or simulation

- run designation (as in Table I) 2. Number of lost calls (grade of service)

- 3. Data Message delay time (mean and standard deviation)

- Data Message total time thru system (mean and standard deviation)

Voice message total time thru system (mean

- and standard deviation)Percent of system trunk utilization

#### Optional output

- 1. Tabular data of distributions of items in standard output

- 2. Lost calls versus type message

- Traffic volume at any node

Message delay versus priority

- 5. Transit time (mean and standard deviation) from origin to destination for each type message

- 6. Size and distribution of queues

- 7. Percent occupancy of various facilities

- Percent of messages using primary route, secondary route

- Time after check-in when mobile subscriber or node can be located (available only on selected runs)

- Increased traffic or increased delay as a function of routing method (available only on selected runs)

The path generation subroutine has immediate utility also. It is a routing scheme and in addition to determining paths for communication between terminals is of use in related fields such as setting up distribution systems and analyzing PERT networks. In its application here, it takes input data in the form of a matrix and generates a primary path (shortest path) and secondary paths between any two nodes. Provisions are incorporated to include an MS node in the path if required and also provisions are included to generate all paths if desired.

From the foregoing, one can conclude that the following additional results will be forthcoming:

- A generalized operational program which simulates communication networks allowing the user to vary parameters and evaluate system performance.

- Verification of the signalling and supervision concept.

- Identification of figures of merit for the communication networks as delay times for signalling, lost call statistics, etc.

The completion of all the work will yield:

- A tool to facilitate the design of communication networks (number of trunks, operational discipline)

- A vehicle to demonstrate compliance or lack of compliance of communication networks with their requirements.

- A guide to the solution of related problems, e.g., setting up a multiple processor configuration with its associated operational discipline and communication problems.

### Basic time-sharing programs for business and long range plans

R. R. Lorentzen

A series of programs using the RCA BTSS capability can determine how changes in an individual product program will affect both that program and the entire product line. Product development programs and investments and proposed financial strategies can be evaluated for optimization of business plans and long range plans.

M <sup>UCH</sup> HAS BEEN WRITTEN<sup>1,2,3</sup> and spoken<sup>4</sup> about the concepts and practices of business planning. Kottler,<sup>5</sup> Dove,<sup>6</sup> and others have described what planning is or should be, and occasionally someone (*e.g.* Drucker<sup>4</sup>) comments or what planning is not. A paper by Gilmore and Brandenburg<sup>7</sup> gives an example of one good planning Bentint BE-17-4-22

Final manuscript received August 20, 1971.

#### Robert R. Lorentzen

Microwave Engineering Projects Planning Microwave Devices Operations Department Industrial Tube Division Electronic Components Harrison, New Jersey

received the BSEE in 1961 and the MSEE in 1965 from Newark College of Engineering. He has also done a year of graduate work at Rutgers University. After working at Western Electric, Hewitt-Robins, and Federal Telephone and Radio, he joined what is now the RCA Microwave Devices Operations Department (MDOD) in 1956, in Equipment Development. In 1957, he entered the Microwave Applications Engineering Activity where he was responsible for resolving the technical interface problems between RCA devices and customer systems. From 1963 to 1969 he held a variety of assignments in engineering program planning, R&D Marketing, and Microwave Solid-State Engineering. Since July 1969, Mr. Lorentzen has been responsible for engineering projects planning. Mr. Lorentzen has written papers on rocketsonde transmitters and microwave solid-state sources, and is a member of Eta Kappa Nu, Tau Beta Pi, and the IEEE

model and repeatedly suggests that the plan can be optimized by asking key questions which are intended to uncover opportunities for synergy. But there is very little in the literature to facilitate the financial analysis and evaluation of these plans. Furthermore, when one piece of data is changed (as a result of a change in the plan, or the forecasts), it is difficult to track all the ramifications of this change. The problem is compounded when several inputs are changed.

In order to deal with this situation, a series of four complementary computer programs has been developed to aid the Microwave Devices Operations Department to prepare and financially optimize its business plans and long range plans (BP/LRP). Other RCA operations within the Industrial Tube Division have also found these programs useful for this purpose.

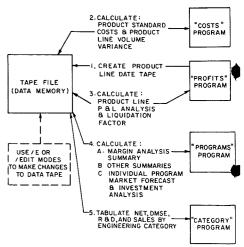

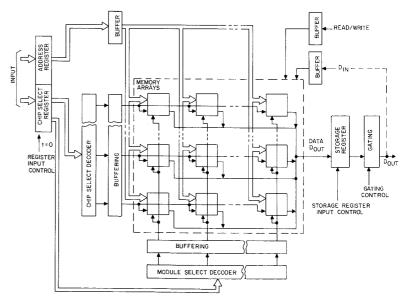

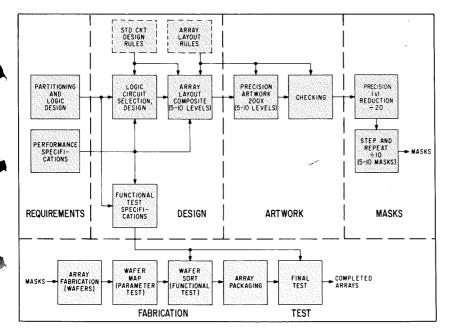

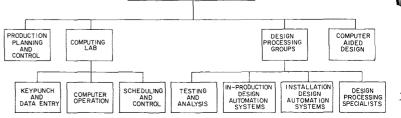

The five key elements of this system are (See Fig. 1):

PROGRAMS—a computer program to calculate a financial analysis of individual product development programs in the BP/LRP, *i.e.* to show the relationships between the market forecast, the engineering and capital investment, the external R&D funding, and the hardware costs and margin. This program also prepares, on request, a cumulative margin to engineering ratio analysis of all programs, or any of several one-page summary reports of specific individual parameters (*e.g.*, sales, margin, or costto-sales ratio), showing all programs over the total time span.

PROFITS—a program to assemble all the costs and income from the product development programs, together with those not related to specific individual product programs, and to calculate and print out a Profit and Loss (P&L) analysis of the entire product line based on this data. This program also calculates the "liquidation factor" (to be dis-

Fig. 1-The system of programs.

cussed below) which is used to calculate the profitability of individual product programs as a function of the entire product line P&L. Hence, this program makes it possible to determine what effect a single change in any parameter will have on the product line P&L and on the P&L of each individual product program.

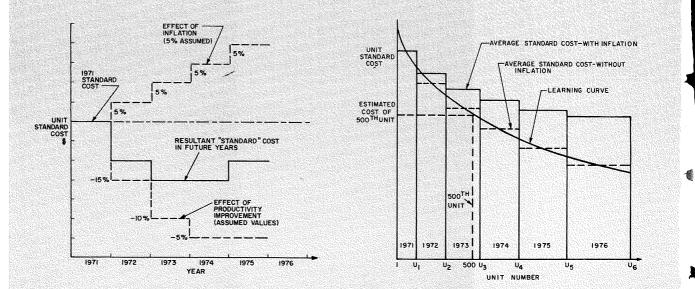

costs-a program to calculate the present and future "standard" costs of individual product programs and the volume variance (under- or overliquidation of fixed expense) for the product line. There are three optional methods (discussed later) for calculating product costs, depending on the nature of the product and its state relative to the product life cycle. CATEGORY-a program which tabulates the various sales and engineering investments by engineering category. DATA MEMORY-a tape file used as the data memory to store all input data, plus the calculated data (e.g., the liquidation factor or volume variance). The present data memory, has capacity for the product line data plus the data for 40 individual product programs for six vears.

#### Purpose

Work on the development of PRO-GRAMS was started in 1969 in an attempt to reduce the manual arithmetic effort—and the errors—that went into putting together a financial analysis of the returns on individual product development engineering investments. These analyses related sales to investment in order to evaluate engineering projects, and also described the multiyear investment often necessary for a product development.

Additional work on engineering budgets and business plans led to an expansion of the data base to include the non-product development aspects of a gross engineering budget in terms that were compatible with and complementary to the RCA accounting practice.

This expansion of the data base made it possible to calculate the product line P&L, and thus made it possible to analyze investments in specific product programs relative to all other programs to optimize the long range P&L for the entire product line.

Today, although these programs have undergone several major revisions to expand the purposes or to improve the algorithm, they are not in a completed final form. We in Microwave are still improving our ability to use this tool and are improving the tool in the process; the programs are a dynamic thing, constantly being improved. To fully grasp what the programs can do today, we must delve into the more intricate details of the construction of the data memory and then take a closer look at the computer programs themselves.

#### "Microwave disguised" example

The business programs, data, and calculations used as illustrations in this paper are taken from the author's imagination and are purposely not intended to describe the real Microwave Operation. (It is for this reason that the title chosen for the illustrative product line is "Microwave (8)—Disguised." The figure 8 represents an imaginary issue number).

#### **Data memory**

A data memory (tape file) should be constructed for each business for which we want to calculate a P&L analysis, by building up from the detail of individual product programs (a section of the PROFITS program is used to create a new data tape).

The data memory can be better visualized if we divide it into four sections (see Fig. 2):

- -Housekeeping and general data.

- -Programs.

- -Other engineering budget elements.

- ---Adjustments, reserves, assessments, and R&D factor.

#### "Microwave disguised" example

The tape file sentinel (line 0 in Fig. 2) is the date that the data memory was created or revised. Line 10 contains

| 10001174 TADEEA 2 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| PRINT TAPESO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                   |

| a 10 1971 6 85 0 5 5 5 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | s//                                                               |

| 20 MICROWAVE (8)-DISGUISED 20 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                   |

| W 5 30 MARKET 20 UNIT 21 UNIT IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                   |

| 2 40 YEAR UNITS PRICE COST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NET DMSE CAPTL R&D SHX X                                          |

| 50 SONDE: A10 PENCIL TUBE A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P 1.00 1.50 2.50                                                  |

| 7051971 300000 510.00 /6.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FØ FØ. F1. FØ. FØ. F95 100]                                       |

| 8 80 1972 300000 9 10.00 6.44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 0. 1. 0. 0. 95 100                                              |

| 90 1973 250000 10.50 n 6.63 p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 13 0.14 1.15 0.16 0. 95 100 18<br>1 0.14 1.15 0.16 0. 95 100 18 |

| 100 1974 250000 11.00 6.90<br>110 1975 200000 11.50 7.24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 0. 1. 0. 0. 95 100<br>0 0. 1. 0. 0. 95 100                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 0. 1. 0. 0. 95 75                                               |

| 130 COMM: A20 PENCIL TUBE A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P 2.00 3.00 2.50                                                  |