# RBA Engineer

Vol 22 No 5 Feb Mar 1977

Microprocessors-design in transformation

# RB/II Engineer

A technical journal published by **RCA Research and Engineering** Bidg. 204-2 Cherry Hill, N.J. 08101 Tel. PY-4254 (609-779-4254) Indexed annually in the Apr/May issue.

#### **RCA Engineer Staff**

John Phillips **Bill Lauffer** Joan Toothill Frank Strobl Pat Gibson **Joyce Davis**

Editor Assistant Editor Art Editor **Contributing Editor** Composition **Editorial Secretary**

#### **Editorial Advisory Board**

| Jay Brandinger  | Div. VP, Engineering,<br>Consumer Electronics             |

|-----------------|-----------------------------------------------------------|

| Bill Brook      | VP, Engineering,<br>RCA Americom                          |

| Joe Donahue     | Div. VP, Engineering,<br>Picture Tube Division            |

| Hans Jenny      | Manager, Technical<br>Information Programs                |

| Arch Luther     | Chief Engineer, Engineering,<br>Broadcast Systems         |

| Howie Rosenthal | Staff VP, Engineering                                     |

| Carl Turner     | Div. VP, Solid State<br>Power Devices                     |

| Joe Volpe       | Chief Engineer, Engineering,<br>Missile and Surface Radar |

| Bill Underwood  | Director, Engineering<br>Professional Programs            |

| Bill Webster    | VP, Laboratories                                          |

|                 | Consulting Editors                                        |

| Ed Burke        | Ldr., Presentation Services,<br>Missile and Surface Radar |

| Walt Dennen     | Mgr., News and Information,<br>Solid State Division       |

| Charlie Foster  | Mgr., Scientific Publications,<br>Laboratories            |

•To disseminate to RCA engineers technical information of professional value • To publish in an appropriate manner important technical developments at RCA, and the role of the engineer

Not much to look at, but microprocessors are transforming the world of electronics; the ideas are still blossoming. Clockwise from the bottom left, in the butterfly's wings, the application areas manufacturing, radar, photography, are: transportation, communication, home entertainment, marine and navigation, spacecraft, test equipment, calculators, medicine, and agriculture.

Concept: Ed Burke, Missile and Surface Radar, Moorestown, N.J. Photography: Tom Cook, RCA Laboratories, Princeton, N.J.

<sup>•</sup> To serve as a medium of interchange of technical information between various groups at RCA

<sup>•</sup> To create a community of engineering interest within the company by stressing the interrelated nature of all technical contributions

<sup>•</sup> To help publicize engineering achievements in a manner that will promote the interests and reputation of RCA in the engineering field

<sup>.</sup> To provide a convenient means by which the RCA engineer may review his professional work before associates and engineering management

<sup>.</sup> To announce outstanding and unusual achievements of RCA engineers in a manner most likely to enhance their prestige and professional status.

### the microprocessor

technological change economic opportunity

Today, the microprocessor is causing a major technological change in the electronics industry. We are now in the early phase of this change, which will eventually produce major market dislocations and significant leadership changes in various segments of the electronics market. The microprocessor's impact on the industry can be compared in magnitude to the conversion from tube circuits to solid state. At such a major point of inflection, opportunity is greatest for those who recognize the change and capitalize on it.

The RCA microprocessor program represents a success story; it was started in the RCA Laboratories in 1971, nurtured by the Solid State Technology Center through 1973 and 1974, and transferred to the Solid State Divison in early 1975. It has now expanded to a full line of large-scale integrated circuits, complete with support hardware and software. The Solid State Division is solidly behind the microprocessor program, with strong continuing support from the Laboratories and the Solid State Technology Center.

The significance of this product to RCA, however, does not lie with the sales of the microprocessor circuits themselves. The real potential is in new electronic equipment products that creative RCA engineers can develop using this product line—new products fully exploiting the advantages of LSI economics coupled with computer architecture and software flexibility. This is the area where there is excitement and opportunity for both management and engineering within RCA to do something innovative in end products, to apply new design techniques, and to take a fresh unencumbered look at solutions to problems and needs.

In short, it is a time for RCA to use the cost-effectiveness and flexibility of microprocessors to seize the opportunity that is occurring in the industry today.

Philip R. Thomas Division Vice President Solid State MOS Integrated Circuits Solid State Division Somerville, N.J.

### How the microprocessor is affecting all of us

Software specialists are saying, "I told you so," as specialized hardware is replaced by standard microprocessors and custom software. Some industry forecasts indicate an eventual shift to an 80/20 software/hardware mix. 37 -Designers and manufacturers of ICs have a lot of work ahead, because the microprocessor chip is only part of the microcomputer picture. What happened in the minicomputer business will probably happen with microcomputers-memories, I/O interfaces, and peripherals will represent the bulk of the sales-and that means an extensive design and production effort. -16. 71. 76 -Systems, equipment, logic, and circuit designers are finding that their specialties are no longer separate parts of the design process. In microprocessor-based products, the work is best done by the same person or a closely cooperating group. - 16, 28, 50, 68 -Manufacturing, process-control, and testing engineers have virtually boundless opportunities ahead. Microprocessors are increasing the capability of controllers and inspection systems; at the same time they are making custom units economically justifiable. - 50, 58, 64 -Reliability and field engineers are finding that microprocessors are being used in an increasing number of the systems and equipment they work with. Service philosophy may change drastically-the "signature analysis" method of identifying troublespots represents an entirely new service philosophy that should be evaluated. 50 -**Technical managers** are in the midst of vast market changes. The microprocessor can usually do more and do it more reliably-and often with cost and schedule advantages. This is a definite plus, but improvements are happening so fast that today's products are obsolete tomorrow. - 4, 76 – No matter what kind of engineer you are, microprocessors will affect your work, if they haven't already. Get involved now. - 7, 12, 15 –

## B/I Engineer 1977

Vol 22 No. 5 Feb Mar

#### overview

| R.O. Winder                                                       | 4  | The microprocessor business                                         |

|-------------------------------------------------------------------|----|---------------------------------------------------------------------|

|                                                                   |    | introduction to microprocessors                                     |

| J.C. Phillips                                                     | 7  | Getting involved with microprocessors                               |

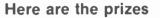

| G.B. DiGirolamo                                                   | 12 | Learning to use microprocessors                                     |

| W.D. Lauffer                                                      | 15 | Getting your hands on COSMAC hardware                               |

|                                                                   |    | COSMAC                                                              |

| A.W. Young                                                        | 16 | The CDP1802: a powerful 8-bit CMOS microprocessor                   |

| D. Block                                                          | 22 | A low-cost hardware prototyping system for<br>microprocessor design |

| P.M. Russo                                                        | 28 | Architectural trade-offs in designing microcomputer systems         |

| L.A. Solomon                                                      | 37 | COSMAC resident software development aids                           |

| C.A. Meyer                                                        | 43 | COSMAC support literature: keeping users informed                   |

|                                                                   | 47 | IEEE Fellows                                                        |

|                                                                   |    | on the job/off the job                                              |

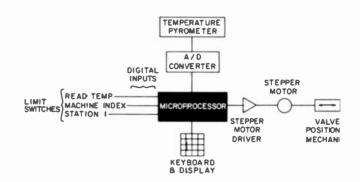

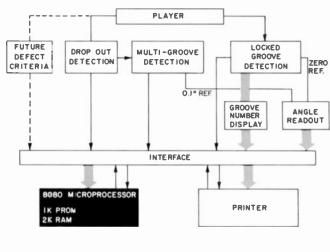

|                                                                   | 48 | COSMAC contest                                                      |

|                                                                   |    |                                                                     |

|                                                                   |    | microprocessor applications                                         |

| Engineering Research Notes                                        | 50 | How RCA engineers are using microprocessors                         |

| M.D. Lippman                                                      | 54 | Microprocessors in telecommunications                               |

| C.C. Wang  C.T. Wu  P.M. Russo<br>A. Abramovich  A.R. Marcantonio | 58 | Microprocessors in manufacturing and control                        |

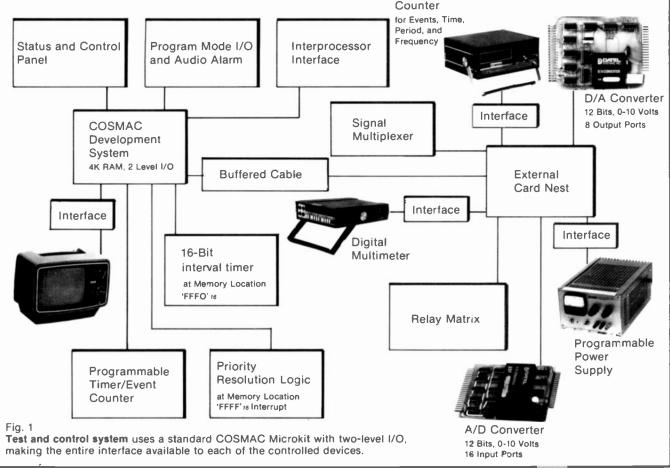

| P.M. Russo A.R. Marcantonio                                       | 64 | A microcomputer for test and control applications                   |

| J.D. Callaghan                                                    |    |                                                                     |

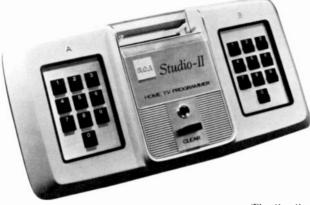

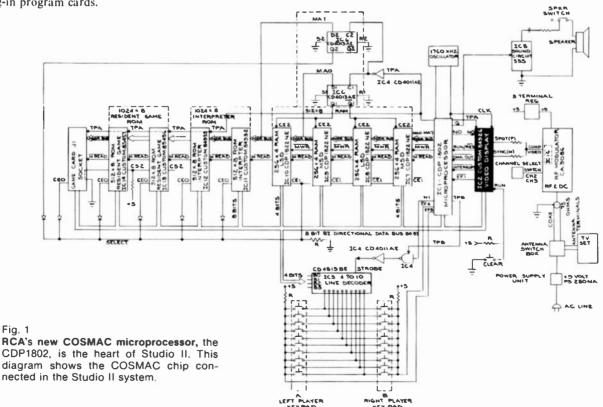

| W.M. Stobbe W.M. Stonaker                                         | 68 | Studio II—using COSMAC in a home entertainment product              |

|                                                                   |    | advanced microprocessor technology                                  |

| G.R. Briggs S.J. Connor                                           | -  |                                                                     |

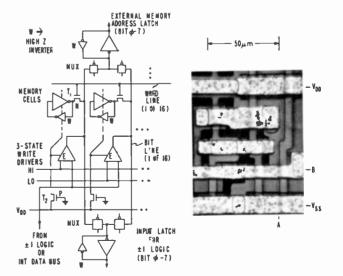

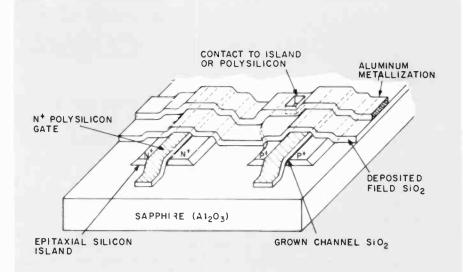

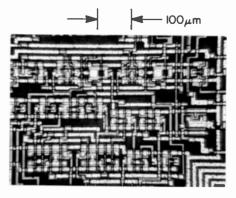

| J.O. Sinniger R.G. Stewart                                        | 71 | 20-MHz CMOS-on-sapphire COSMAC microprocessor                       |

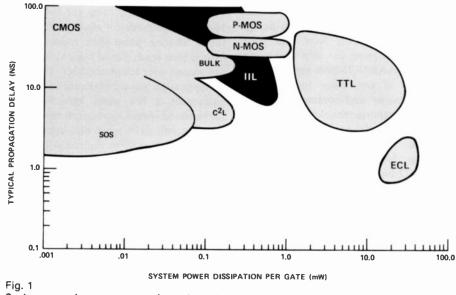

| W.A. Clapp A. Feller                                              | 76 | Technology impact on microprocessors                                |

|                                                                   |    | special—short course                                                |

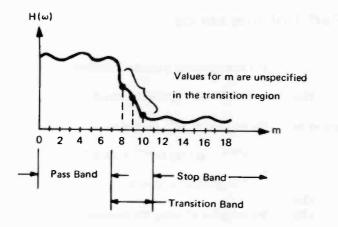

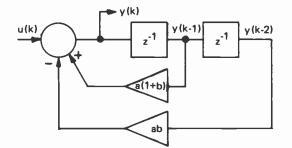

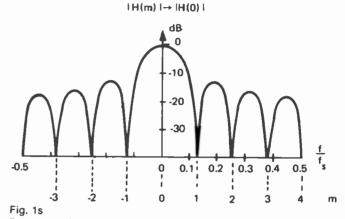

| L. Shapiro                                                        | 80 | Digital filters                                                     |

|                                                                   |    | departments                                                         |

|                                                                   | 92 | Pen and Podium                                                      |

|                                                                   | 93 | Dates and Deadlines                                                 |

|                                                                   | 94 | News and Highlights                                                 |

|                                                                   |    |                                                                     |

Copyright 1977 RCA Corporation All rights reserved

**Robert Winder** is Director of Memory and Microprocessor Products in RCA's Solid State Division. His work with microprocessors began in 1971 at the RCA Laboratories, continued in the Solid State Technical Center in 1973, and moved to SSD in 1975. Dr. Winder received the David Sarnoff Award for Outstanding Technical Achievement in 1976 for his work with RCA's microprocessor products.

Contact him at: Memory and Microprocessor Products Solid State Division Somerville, N.J. Ext. 6005

# The microprocessor business

How and why it's grown, and how it's going to affect you.

#### R.O. Winder

"The microprocessor is the biggest thing in electronics since the transistor."

I agree with this often-expressed view, and feel that the excitement being generated by the trade journals represents a true revolution in the design of electronic products. Certainly the IC makers see a need to offer these new components—the major manufacturers are investing heavily in the microprocessor business. And you, the readers of this special issue, should look for opportunities to apply the new technology in RCA's many diverse markets.

In these few pages I would like to make some estimates of the size of the market, outline who is using microprocessors and why, and discuss the manner in which "micromakers"—the manufacturers of microprocessors—must support their customers (i.e., you). I'll use the RCA Solid State Division microprocessor product line as an example throughout—not only because I'm familiar with it, but because Solid State Division is competing directly and vigorously with Intel and the others in 8-bit microprocessors, a fact that many of you may not realize.

#### What the products are

Semiconductor memory circuits were the first generalpurpose large-scale integrated (LSI) circuits. They, together with the more specific calculator, watch, and tvgame circuits, plus numerous custom chips, take advantage of LSI technology to provide greater function, miniaturization, and reliability, at lower cost. Microprocessors, which contain the CPU (Central Processing Unit) of a computer on one (or a few) ICs, may be thought of as complements to memories, so when Intel introduced them, it meant that LSI could be used for the entire "main frame" of a computer that part of a computer common to all applications. Even though customers had to provide SSI and MSI logic for interface to the outside world, the resulting systems had great advantages in flexibility, miniaturization, and cost the revolution was underway.

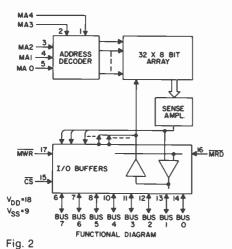

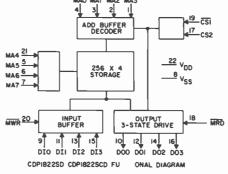

Solid State Division's offering in standard memory parts includes CMOS, CMOS/SOS, and NMOS RAMs (random-

Reprint RE-22-5-1 Final manuscript received October 18, 1976.

| Rapid market expansion for the microprocessor families will be even more rapid in the |  |

|---------------------------------------------------------------------------------------|--|

| next few years. (Source: Electronics, Jan 6, 1977.)                                   |  |

| (millions of dollars)          | 1975   | 1976   | 1977   | 1980 |

|--------------------------------|--------|--------|--------|------|

| Integrated circuits, total     | 1086.2 | 1512.7 | 1927.3 | 3106 |

| Standard logic families, total | 422.1  | 581.0  | 728.2  | 922  |

| Microprocessor families, total | 70.9   | 108.2  | 188.2  | 438  |

| CPUs, total                    | 24.9   | 38.5   | 63.9   | 166  |

| MOS                            | 23.1   | 35.6   | 58.9   | 150  |

| 4-bit                          | 13.7   | 16.6   | 22.8   | 26   |

| 8-bit                          | 5.8    | 13.0   | 25.0   | 70   |

| 16-bit                         | 1.6    | 3.0    | 7.6    | 50   |

| 1-chip controllers             | 2.0    | 3.0    | 3.5    | 4    |

| Bipolar, total                 | 1.8    | 2.9    | 5.0    | 16   |

| Bit slice                      | 1.8    | 2.5    | 4.0    | 8    |

| Full CPU                       | _      | 0.4    | 1.0    | 8    |

| ROMs                           | 14.5   | 16.7   | 32.0   | 80   |

| RAMs                           | 8.0    | 15.0   | 30.5   | 79   |

| I/O interface chips            | 10.0   | 21.0   | 39.3   | 80   |

| Peripheral chips               | 13.5   | 17.0   | 22.5   | 33   |

|                                |        |        |        |      |

access memories) in 32x8, 256x4, 1024x1, 4096x1, and 1024x4 configurations, and CMOS ROMs (read-only memories) in 512x8 and (soon) 1024x8 configurations. Solid State Division does not presently offer a PROM (programmable read-only memory); their customers buy competitors' PROMs if their volume (under 50 or so) is too low for hard-wired ROMs.

Solid State Division's microprocessor business is built around the CDP1802 microprocessor, a CMOS implementation of Joe Weisbecker's COSMAC architecture, which is radically different from the Intel and Motorola architectures. COSMAC was specifically developed to minimize logic complexity, allow very compact programs, and interface efficiently with the outside world. This lower complexity permits us to manufacture the CDP1802 in CMOS at a cost comparable to NMOS and PMOS competition with its more complicated logic. And Solid State Division is able to compensate for its late start in this business by capitalizing on the well-known electrical benefits of CMOS technology—low and flexible power requirements, unexcelled noise immunity, and tolerance to wide temperature extremes.

#### The four-chip computer

Table

As the market has grown, other kinds of product have become increasingly important—the circuits that interface the microprocessor to the outside world. These I/O (Input/Output) circuits consist of a mixture of custom and standard circuits. A typical custom I/O circuit would contain all the interfacing logic for the microprocessor, including A/D inputs, real-time clocks, and outputfrequency generators. A customer would then have a 4-chip computer: 1-chip CPU, 1-chip RAM, 1-chip ROM, and 1chip I/O circuit. Such systems will sell for less than \$20 in 1978 in automotive volumes. However, not everyone buys in automotive volumes. Most customers will be using "I/O ports" to pass 8bit data to and from the CPU, UARTs (universal asynchronous receiver-transmitters) to pass serial data, MDUs (multiply-divide units) to do fast arithmetic when required, and a collection of "connective tissue" parts to facilitate memory and I/O expansion. Solid State Division presently offers a simple byte I/O port, and the other parts listed are in various stages of development.

#### The one-chip computer?

Finally, I will point out that the virtues of LSI suggest pulling the various pieces of a microcomputer into common ICs— CPU and memory together, or ROM and RAM together, or even CPU, ROM, RAM, and I/O together. These products lose flexibility, but gain in cost advantages. As indicated in the market-summary table, they will gain in importance as LSI technology matures.

#### What they're used for

The market-forecast table lists the estimated size of the total digital IC market. In my opinion, the percentage growth of microprocessor products within this market represents the combination of two important trends: 1) microprocessors are displacing other digital markets, and 2) they are creating their own.

First, an increasingly higher number of digital systems that might have been implemented using SSI and MSI will instead be done in LSI—using microprocessor technology. In other words, what might have been an *ad hoc* collection of event-recognition circuits, counters, shift registers, miscellaneous imbedded RAMs, A/D converters, and messy control logic will become organized into an efficient computer structure instead.

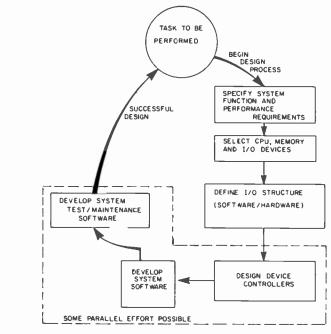

Why this trend? Because the microprocessor design process is better organized, more modular, more likely to implement the desired function, and generally is better understood. The various I/O interfaces to a computer are separate and work through a common bus structure and control scheme with the CPU. This makes deletions, modifications, and I/O additions easier. Control algorithms are implemented in subroutine-organized software—again, easier to modify. The payoff is in less engineering to reach a better product that is more easily maintained and enhanced.

The second trend swelling the market for microprocessors is the lower cost of LSI logic, which makes new products possible. For example, the automobile engine controllers that have been mechanical up to now—distributors, carburetors, etc.—will be electronic in the future. Computers will become commonplace in the home, beginning as tvgame add-ons. And LSI technology will accelerate the use of electronics in business and industry with new low-cost microcomputer-based products.

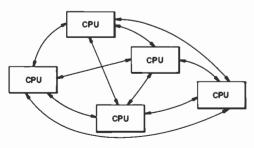

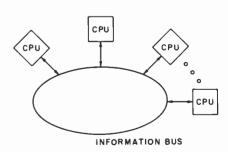

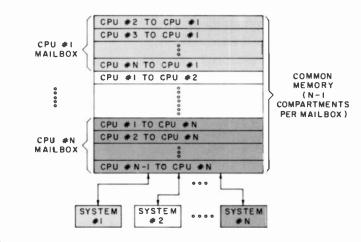

#### What will be left to SSI, MSI, and non-computer-like logic?

First, some I/O interfaces will never be offered as off-theshelf products-they will have to be built up with the standard logic building blocks. Second, some systems are so simple that the "overhead" of a computer structure is too expensive. Third, there is a clear performance limit to what microcomputers can do. They are basically sequential devices. For a given stage of a technology, ad hoc logic--the "messy" printed circuit board full of standard logic circuits-can do many functions in parallel that will overtask a microprocessor trying to perform the same functions sequentially using that same technology. Although multiple microprocessors can be used, cost goes up. And fourth, for very-high-volume applications, certain functions will be done in custom LSI in an ad hoc manner (generally because they require high-speed parallel information processing). But the central core of digital systems will need a reasonable amount of "intelligence" and can be operated by one sequential processor, so that the microcomputer approach will be the best, whether it is done with custom microcomputers, with assemblies of standard microprocessor components, or with a single-chip microcomputer.

#### How they're supported

The micro-makers recognized early that their customers needed more help in using microprocessors than they needed with SSI, MSI, or memories. Few of the early producers had the benefits that RCA has: an in-house system capability, and even a few computer buffs left over from the good old days. Early support systems were primitive and were redesigned repeatedly. Applicationsengineering help, always in short supply as the business grew, took some time to mature in quality. Early documentation was atrocious, and training seminars nonexistent.

RCA Solid State Division customer support is typical of that

now offered by micro-makers. Support systems we sell include:

• the Microtutor, a minimum complete computer used for learning the basics of microprocessors;

• the Evaluation Kit, (see Block, p. 22) a PC board and package of parts sufficient to put together a small computer for electrical experimentation and prototyping (add only a power supply and terminal);

• the COSMAC Software Development Package, (see Solomon, p. 37) a FORTRAN program that provides an assembler, simulator, and interactive debugger (available as card deck or tape, or on any of several time-shared systems, including CMS in Cherry Hill);

• the COSMAC Development System, a complete, expandable rack-mountable microcomputer (just add terminal), with empty slots to support prototyping or small production volumes, software for assembly and editing, a floppy-disc option for fast and convenient software development, and a higher-level-language operating-system option for the most efficient design and debugging of microcomputer hardware and software;

• and (early in 1977) the RCA version of Intel's "in-circuit emulator," a microcomputer that monitors and controls the activity of prototype or production microcomputer products—in short, the microprocessor engineer's oscilloscope.

Data sheets, manuals, application notes, seminars, and application engineering consultation—by phone and by direct visits—are an essential part of the support offered by all micro-makers (see Meyer, p. 43). Your access to application engineers will be a function of the supplier you work with and your importance to them. I'd like to say, on that subject, that you RCA customers, no matter how small the volume you need, are extremely important to us in Solid State Division. This is not only because of the obvious image impact, but because we believe we have the best products available, and that it is in RCA's best interest that you use them!

A final, especially interesting area of support the micromakers offer is custom engineering for fee. This work ranges from implementing ROM patterns, through the design of custom I/O circuits, and into complete system design and software implementation. The Solid State Division, using RCA's unusual system-design capabilities, has done very well with this kind of service, getting prospective customers into production quickly with products likely to be succesful.

The Advanced Technology Laboratory and the the Solid State Technology Center's Design Automation group provide an essential set of tools for these jobs—APAR (Automatic Placement and Routing) for fast turnaround custom I/O chips, and a ROM design system that generates IC masks and test programs automatically. I strongly recommend that RCA engineers working in microprocessors acquaint themselves with these capabilities—it costs suprisingly little to generate ROMs and custom ICs quickly. The SSTC will be happy to work with you in putting its arsenal of tools to work. Getting involved with microprocessors

#### J.C. Phillips

If the lessons of history and present trends mean anthing, the electronics world is going through a digital revolution and the microprocessor is a primary catalyst. Digital technology—and specifically microprocessor technology—has grown so fast that many of you may still be groping for a place to start.

Start here. Those of you who have little or no knowledge of microprocessor technology should be able to pick up some of the buzzwords from this article—at least in sufficient depth to comprehend the message of this special issue, which focuses on the importance and the versatility of the microprocessor.

#### What is a microprocessor?

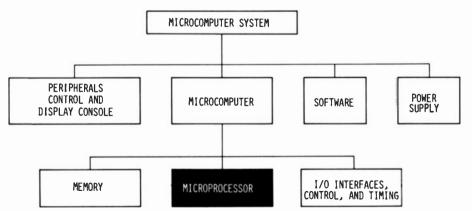

A microprocessor is the central processing unit of a microcomputer, and a microcomputer is simply a computer constructed from a handful of integrated circuits. Thus, any discussion of microprocessors and microcomputers can start with some general remarks about computers.

Start with this article if you think that every computer is bigger than a breadbox.

All computers perform five rather human-like functions: input, storage, control, processing, and output; Table I outlines these functions for humans and computers, including microcomputers. Although Table I is general, it places the control and processing functions in proper context with the input, storage, and output functions.

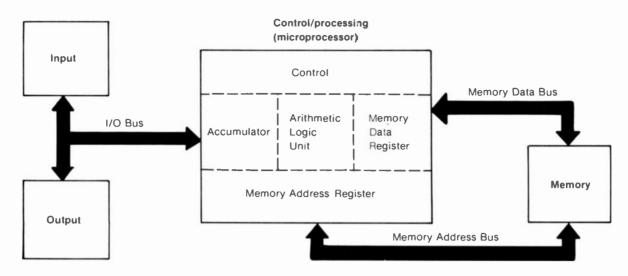

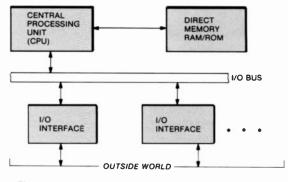

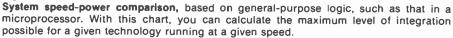

All microcomputers are based on these building blocks, with information exchanged among the blocks via a group of wires (one for each binary digit) called a *bus*; see Fig. 1.

#### How information is handled

The basic unit of information in any computer is the binary digit, or bit, capable of only two stable states, called "one" and "zero." All computers (including microcomputers) operate on groups of bits called words. The word is the primary group of bits that the computer manipulates (reads in, stores, reads out, etc.) in a single step. Word length for any given computer is usually determined by the number of bits that can be stored in a specific memory location;

#### Table I

All computers perform these five functions. These are known as *Harvard*-class machines. If, in addition to these properties, the machine stores instructions in the same form as data in memory—each equally accessible to the calculating section of the computer—then instructions may be treated as data, and the machine can modify its instructions. Such a machine is called a *von Neumann* or *Princeton*-class computer. Microcomputers are available in Harvard and von Neumann classes.

|            | Human                             |                                                                 | Computer (microcompu                                                                        | ter)                                                                                              |  |

|------------|-----------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|

| Function   | Device                            | Action                                                          | Device                                                                                      | Action                                                                                            |  |

| Input      | Five senses<br>(maybe six)        | Receive sensory data<br>and convert it to<br>impulses for brain | Keyboards, magnetic tape,<br>paper tape, punched cards,<br>switch closures<br>A/D converter | Receive data as<br>binary "ones" and<br>"zeros"                                                   |  |

| Storage    | Brain                             | Store facts in brain<br>for recall and<br>reaction.             | Tapes, discs, drums,<br>cores, solid-state<br>circuits                                      | Place data (1s &<br>0s) in specific<br>locations for later use.                                   |  |

| Processing | Brain                             | Interpret data<br>and instructions<br>stored in memory.         | Central Processor<br>Unit (microprocesor)                                                   | Gather information from<br>appropriate locations<br>in memory (storage)<br>and interpret results. |  |

| Control    | Brain                             | Select appropriate<br>action based on<br>data and instructions. | Central Processor<br>Unit (microprocessor)                                                  | Select an alternative<br>course of action on<br>the basis of computed<br>results.                 |  |

| Output     | Voice, actions,<br>gestures, etc. | React                                                           | Printer, keyboard,<br>switch closures,<br>CRT, D/A converters,<br>alphanumeric displays     | Deliver results for user.                                                                         |  |

Fig. 1

**Microcomputer architecture** is based on four basic building blocks: input, output, memory, and microprocessor. The blocks are interconnected by buses—groups of lines [one for each *binary digit* (bit) to be transferred].

common word lengths are 4, 8, 12, or 16 bits. In general, the longer the word length, the greater the precision (number of significant digits). Also, the longer the word length, the richer the *instruction set* and the more varied the *addressing modes*.

An *instruction set* is the set of general-purpose instructions available with a given computer; generally, different computers have different instruction sets. *Addressing modes* are the ways that a given computer will specify the memory location containing the word to be operated upon. These modes are important factors in programming (and hence, in computer efficiency).

Two types of words are used in every computer: *data words* and *instruction words*. Data words contain the information that the computer processes; instruction words cause the computer to execute a particular operation. For example, an instruction may move data, do arithmetic and logic functions, control input or output (I/O) devices, or decide which instruction to execute next.

Byte is another commonly used term that is sometimes confused with word. A byte is any sequence (regardless of machine architecture) of n bits operated on as a unit. The most frequent size is 8-bits. A half-byte (4-bits) is called a *nibble*.

# The basic task is to fetch and execute instructions

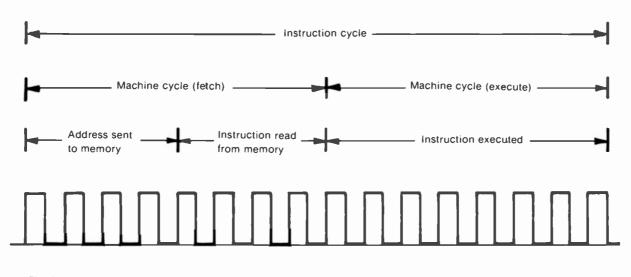

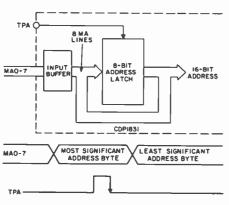

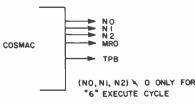

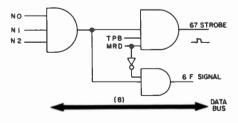

All of the operations of a computer are synchronized by a clock, and usually several clock pulses are required to accomplish the tasks specified by a single instruction. The execution of that single instruction is called an *instruction cycle*. For the RCA COSMAC microprocessor, a typical instruction cycle requires 16 or 24 clock pulses; a machine cycle requires eight clock pulses (see Fig. 2). Each instruc-

tion cycle typically consists of one or more *machine cycles*; the machine cycle is the basic microprocesor operation cycle. It usually consists of one of the following operations:

*Fetch*: The microprocessor uses an *address* (a number identifying a specific memory location) to read an instruction word from memory for use by the microprocessor; or

*Execute:* The instruction that has been fetched is decoded and the requested operation is performed.

There are other types of machine cycles (e.g., some types of interrupts), but most either fetch or execute.

Since a microprocessor must have sufficient hardware to fetch and execute instructions, it must contain:

—a program counter, which specifies the address of the next instruction to be fetched and executed. Normally, the counter is incremented automatically each time an instruction is fetched.

—an *instruction register*, which is a fast-access circuit used to store bits or words.

—an arithmetic logic unit (ALU), which executes such binary transformations as add, subtract, shift, AND, OR.

—a control section, which provides a way to address memory and to perform *branch instructions* (alter the sequence in which instructions are fetched based on the results of ALU operations).

#### Memory stores data and instructions

Instructions and data must be stored in *memory* so that they can be recalled at the appropriate time for the microcomputer to perform its function. Each instruction or data word is assigned a unique *address* that the microprocessor refers to when fetching or storing information. Memory is broadly divided into two classes: read-only memory (ROM); and read/write or random-access memory (RAM).

Fig. 2 Instruction cycle for COSMAC consists of one or more machine cycles; a machine cycle requires 8 clock pulses.

*ROM* (fixed memory) is used to store program steps and constant data values. It is difficult and time-consuming (and often impossible) to write into ROM; therefore, it is used in situations where the memory values do not change, e.g., in dedicated systems. Since this is a primary application of microcomputers, most of these machines use ROM for program storage. Some microcomputers use only ROM for storing program steps.

RAM (random-access memory) has both read and write capability. RAM is used to store data that changes during the operation of the system, e.g., results of calculations, or programs that are changed frequently.

Although most of the memory in a microcomputer is on separate chips, the microprocessor itself contains several fast-access storage units, called *registers*, that are used for temporary storage of data and instructions. The common registers are:

• *Memory address register* (MAR), which holds the address of the memory location being accessed.

• Memory data register (MDR), which accepts and temporarily stores the word coming from, or going to, memory (during read and write operation, respectively). • Accumulator (AC), which holds the result of an arithmetical or logical operation to be used by the microprocessor. For example, the AC can provide an input to the arithmetic logic unit—ALU.

• Program counter (PC), which is automatically incremented to identify the next instruction to be fetched or executed.

• Stack pointer, which identifies (addresses) the last element in a stack. The stack is an array in RAM, separate from the microprocessor, which allows words or addresses to be accessed in a last-in, first-out fashion. A LIFO array is sometimes referred to as a *pushdown* array. Typically, a stack is arranged similar to a stack of papers, with each new input placed on top of the pile. • Scratch-pad memory, which consists of generalpurpose registers (RAM) that temporarily store data and addresses. The number and flexibility of such registers varies greatly among microprocessors.

• Instruction register (IR), which contains the instruction that has been fetched from memory and is being decoded and executed. This register usually has some external method of control (e.g., reset pushbutton or toggle switches) since the instruction register is typically used to direct the microcomputer to the location of the first program step.

• Status register (SR), which consists of one or more flipflops (flags), provides information that is crucial to many arithmetic operations (for example, overflow from operations, zeros in the accumulator, sign of a number in the accumulator). This information is often used to decide what program step comes next.

# Software —instructions that tell the microcomputer exactly what to do.

All operations that the microcomputer performs must be broken down into a series of individual tasks called *instructions*. The details and number of these instructions vary greatly depending on the microcomputer. Theoretically, any program may be written using the instruction set of any microcomputer. The length of the program and the time of the execution, however, may differ greatly with different instruction sets.

The instructions used may be divided into five functional types: transfer of data, control, subroutine linking, operation, and input/output. Such instructions may reference data from memory or from microprocessor registers, or may simply control the operation of the machine. Those that reference memory require an extra memory cycle to obtain the data and, therefore, may require more time to execute. In COSMAC, all instruction executes are identical. A sequence of these detailed instructions needed for the computer to accomplish a specific task is called a *program*. Since the memory can store only 1s and 0s, the instructions must be encoded in binary. A program in this form is in *machine language*.

This is the lowest-level language in which programs can be written. Using it is tedious in that the value of every bit in every instruction of the program must be specified (e.g., by a string of binary digits for every word in memory).

Symbolic language allows instructions and storage locations to be represented by alphanumeric symbols. These symbols are chosen to make memorization easy and are therefore called *mnemonics*. (For example, in the COSMAC instruction set, OUT 1 represents *output* 1, IDL stands for *idle*, and SHLC means *shift left with carry*.) A program written in symbolic language must be translated to machine language before it can be stored and executed. The translation is performed by an *assembler* program. Most statements written in symbolic (or assembly) language translate to only one instruction in machine language.

To make programming easier, *higher-level languages* have been developed in which statements more clearly resemble English and mathematics, mostly for use on large-scale computers. Each is developed with a particular class of problem in mind. Some of the more popular languages are Fortran, ALGOL, APL, BASIC, COBOL, and PL/1. In these higher-level languages, one statement may correspond to many machine-language instructions. The conversion from a higher-level langauge to assembly code or to machine code is performed by a program called a *compiler*. (In a sense, a compiler is an assembler for higher-level languages.) Still another possibility is the popular BASIC, which is an *interpretive* language; i.e., the translation into machine code is accomplished at run time.

In preparing a program, it is frequently necessary to make numerous corrections and changes—for example, to correct a symbol or to insert one or more instructions into the program. This task is facilitated by the use of a special program called an *editor*. The editor allows the program to be stored into RAM and made available on an instructionby-instruction basis for the purpose of making alterations easy.

Once written, a program is stored in one of the two types of memory. If the program is stored in ROM, it is always present in the machine and may be executed by branching to the address of the first instruction. This is the normal procedure in dedicated microcomputers. If the program is to be stored in RAM, which is volatile, then the program is usually loaded from keyboard, tape reader, or disc. To facilitate this loading, a special program called a *loader* is necessary and is often made resident in ROM. The loader is frequently combined with the capability to *read* or *write* directly into locations in memory so it can perform various housekeeping and debugging chores. In this case it is called a *monitor*. Once a program is loaded, it is started by jumping to the first address in the program. Since most microprocessors are in dedicated systems, the program is usually stored in ROM. During the development process, however, it is very advantageous to store the program in some type of memory that can be modified easily. Most microprocessor manufacturers provide support systems (development systems) to aid in software development. (See the paper by Solomon in this issue.)

# Advantages—lower cost, more flexibility, and new functions are just a few.

As demonstrated by several papers throughout this issue, the microprocessor offers significant advantages over both hardwired discrete logic and custom LSI (large-scale integrated) logic. The key advantage, of course, is that a given microprocessor chip can be used for a multitude of applications by simply changing the support hardware and the software. Thus, the cost of rather complex equipment is quite low because the microprocessor can be produced in large production volumes. In his excellent "Overview of microprocessor applications," in the June 1976 *Proceedings of the IEEE*, A.J. Nichols identified seven primary advantages of microprocessor-based designs, compared with discrete-logic designs.

1) The manufacturing costs of the product are lower. Typical microprocessor-based designs cost 20% to 60% of their TTL discrete-logic equivalents.

2) The time and cost for the original development is lower. An accomplished design team can cut the design time by about two thirds. As support tools improve, the design cycle will continue to decrease.

3) As a consequence, products can be brought to the market faster and in closer correlation with market needs. This can provide a significant edge in obtaining or increasing market share.

4) The microprocessor's inherent flexibility makes quick response to competitive pressures in the marketplace possible, with consequent increases in product lifetimes.

5) Greater functional capability can be provided at reasonable cost. This means better products for the same or lower prices.

6) The smaller number of components in a microprocessor system increases the reliability of the final product.

7) Should failure still occur, the microprocessor can, in some cases, perform self-diagnosis, providing substantial reductions in service charges.

In essence, the microprocessor offers the advantages of LSI without the cost penalty of designing the various mask and metalization patterns needed for custom LSI. Of course, high system complexity and significant production quantities will demand a custom design.

#### But there are some limitations

As stated previously, in doing its job of fetching and executing instructions by communicating with memory and with input/output devices, the microprocessor is a one-chip central processor unit for a microcomputer. However, placing all these central processor functions on a single integrated circuit imposes two very practical restraints:

1) The number of pins available for connection to the outside world—memory, I/O, power, and timing.

2) The number of functions that can be put on that chip.

The number of available pins limits the speed of information exchange.

Because the number of pins is limited, some type of serial (or multiplexed) data-transfer technique is used to carry information to and from the processor. In serial transfer, pins are traded for execution time; that is, entering 8 bits serially on a single pin takes 8 times as long as full parallel entry. Serial entry requires additional gating and storage circuits. Typically, memory interface pins are also used for I/O functions.

Functional limitations—designers are focusing on the rest of the system.

The number of functions that can be placed on a chip is limited primarily by the integrated-circuit technology used, and this limit is constantly changing (see the Clapp and Feller paper in this issue).

In general, several types of one-chip microprocessors have evolved to include the functions outlined above. Further work will probably be focused on improving the rest of the microcomputer system, with particular emphasis on input/output chips, and on multiprocessor systems (see the paper by Russo in this issue).

#### Implications for engineers put your soldering iron on the shelf next to the tube tester and slide rule

In a sense, the microprocessor is bringing a breath of fresh air to the engineering lab. Probably the most tangible, albeit mundane, change brought about by the microprocessor is that the labs no longer reek of burning resin and carbon resistors. Breadboards are created in a new way—with manufacturer-supplied development systems (see the paper by Block, this issue). Design changes are implemented via software. Thus, learning about microprocessors also requires learning computer programming—the soldering gun and needlenose of the future!

RCA has made it easy for you to learn about microprocessors and computer programming (see the DiGirolamo paper in this issue). If you still don't think you should, reread Phil Thomas' inside cover message and glance at the market projections in Bob Winder's paper; also note the numerous applications cited in this issue. Your efforts will be amply rewarded. A powerful, pocketsized computer readily and economically available as a tool and as a design element carries significant implications for every engineer, regardless of discipline. There is a microprocessor in your future, and the future is now.

#### References

In anticipation of this special microprocessor issue of the *RCA Engineer*, we asked several microprocessor experts to identify the microprocessor literature that may be useful and interesting—particularly to neophytes.

Mort Lewin of Rutgers University (consultant to the Solid State Divison) called our attention to an exhaustive bibliography compiled by Ann R. Ward of Bell Laboratories. This bibliography appeared in two separate issues of the IEEE Computer Society journal *Computer* (part I in July 1974 and part II in January 1976).

Dr. Lewin then identified four introductory books with which he has had contact:

- 1. Hilburn, J.L. and Julick, P.M.; *Microcomputers/ Microprocessors: Hardware, Software, and Applications* (Prentice-Hall; 1976).

- 2. Soucek, B.; Microprocessors and Microcomputers (Wiley; 1976).

- Barna, A. and Porat, D.I.; Introduction to Microcomputers and Microprocessors (Wiley: 1976).

- 4. Adam Osborne and Associates, Inc.; An Introduction to Microcomputers (Berkeley, CA.; 1976).

Dr. Lewin particularly recommended the first and last, as did R. Smith from MSR, Moorestown, and several engineers from RCA Globcom. The Globcom engineers—John Frankle, Nick Giacketti, Bill Henn, and Tony Longo—also identified the following as useful sources:

- 5. Wester, J.G. and Simpson, W.D.; Software Design for Microprocessors (Texas Instruments, Inc.; 1976).

- 6. Motorola Semiconductor Products, Inc.; *Microprocessor Application Manual* (McGraw-Hill Book Co.; 1975).

- 7. Proceedings of the IEEE, Special issue on microprocessor technology (June 1976).

- 8. EDN, Special microcomputer reference issue (Nov. 20, 1976).

Specific microprocessor types are covered by the manufacturer.

Complete information on specific microprocessor types is usually available in the form of data sheets, instruction manuals, and application notes. For more information on COSMAC literature, refer to the paper by Meyer in this issue.

Applications areas papers are covered elsewhere in this issue.

Literature sources dealing with broad applications are listed with the papers in this issue that cover those application areas. For example,

| Manufacturing and process control    |

|--------------------------------------|

| Wang/Wu/Russo/Abramovich/Marcantonio |

| Test and control Marcantonio/Russo   |

| Communications Lippman               |

| Benrint BE-22-5-2                    |

Final manuscript received February 17, 1977.

### Learning to use microprocessors

#### G.B. DiGirolamo

You can learn microprocessor technology and gain hands-on experience in microprocessor applications through a comprehensive course developed by Corporate Engineering Education exclusively for the RCA technical staff.

Engineers are generally aware of the enormous promise of the microprocessor, but many are unprepared technically and psychologically to use this tool effectively. In May 1975, Corporate Engineering Education introduced a course called "Microprocessors for Logic Design" that has helped more than seven hundred members of RCA's technical staff at seventeen locations understand microprocessor technology and develop "hands-on" skills in using microprocessors. "Hands-on" learning is built into the course through team projects using a microcomputer, the RCA COSMAC Microtutor. Several examples of in-course team projects recently completed by engineers at Automated Systems in Burlington, Mass. are shown below.

#### About the course

The objective is to teach microprocessor technology.

The course is intended to teach microprocessor technology in depth and to help develop skills in designing with, and for, microprocessor systems. Those who complete the course will be able

• To understand the internal structure of a microprocessor,

• To understand microprocessor interfaces with both random-access and read-only memories as well as input/output devices,

• To use microprocessors as a powerful tool in logic design.

Alumni of this course will also be able to do microprocessor system design—configuring a multiplicity of input and output devices and memories into a microcomputer. Finally, participants will learn the state-of-the-art in available hardware and software, be able to interpret manufacturers' specifications, and use effective criteria to evaluate competitive products.

As prerequisites, you should know something about logic design and computers.

To get the most out of this microprocessor course, participants should start with knowledge and experience in logic design equivalent to CEE course C30—Modern Logic Design I. Some exposure to programming and to computer concepts is helpful, but not essential.

The success of the microprocessor course depends heavily upon the effectiveness of an on-site instructor in dealing with the students' learning problems. Therefore, the course

Jonathan Goode, Marc LeVarn, and Tony Macadino developed a "Random Number Game" in which a player attempts to correctly identify a random number generated by the microprocessor. Ed Kramer, Roger Plaisted, and Ted Kupfrian decided to expand the limited input/output capabilities of the Microtutor by interfacing it to a video terminal as their project. They named their project "Microtutor 'UART'." Systems in Burlington, taught the microprocessor course and believes microprocessors are getting into all of our products, so he advises all designers to get aboard this new technology. As emphasized in the paper, the Associate Instructor is crucial to the success of this course. also requires an Associate Instructor, who must have some prior microprocessor knowledge and understand computer fundamentals. Also he must know some assembly language, have written a program which has run successfully, and have logic design capability.

Optimum class size is sixteen participants.

Teams of four are formed in each class, and a Microtutor is assigned to each team.

Seventeen class sessions are suggested.

Included in the seventeen class sessions (2½ hours each) are fourteen video taped lectures, two sessions devoted to review and project demonstrations, and a session for the final examination. Homework is assigned between each session with "hands-on" team exercises between Sessions 5 and 9.

How to sign up for the course.

If you want to take this course, or any other CEE course for that matter, tell your supervisor or your local training manager. When a sufficient number of engineers (usually eight or more) express an interest, the training manager will arrange to get the course materials from Corporate Engineering Education.

Video-taped lectures, hands-on experience, and class participation are the important features.

The primary instruction medium is video-taped lectures. Each class session consists of the primary instruction supplemented by reviews of homework, class discussions, and class exercises, all led by the Associate Instructor.

A study guide, specially prepared for this course, contains printed forms of all the visuals and illustrations used on video tape. In addition, it contains several selected papers and reprints and represents a substantial presentation of

Bill Shubert and Ron Tetrev devised a "Microtutor Editing Keyboard" using a hex keyboard and a two-character hex display to develop a unit to easily accept and modify machine-language programs.

and **Robin Hulls** programmed music in a modern-day version of "His Master's Voice." Snoopy is listening to the "William Tell Overture" as programmed on the COSMAC Mictotutor appropriately titled "Microtutor Music Master."

#### Where are all the others?

As mentioned in the article, about 700 RCA engineers have completed the CEE course, "Microprocessors for Logic Design," since its release in May 1975. This interest is indeed gratifying and actually not suprising in view of the excitement and importance of microprocessor technology. But 700 represents only a small fraction of RCA's engineers. How about you? Why haven't you signed up for the course?

#### Afraid it's too hot to handle?

Well it is tough. Requires a lot of homework. But think about the other tough things you've done. Why not accept it as a technical challenge that will be stimulating? Our very competent Associate Instructors will help you.

#### Figure you don't need it?

Come on now! How long can you really pass yourself off as a knowledgeable engineer without being conversant with one of the most significant technologies ever developed? How can you know you won't find an application for the technology when you really don't understand it? And isn't it just a matter of time? Why be last?

#### Maybe you'll learn it some other way?

Sure! It'll come as if by magic. You'll talk a little with this fellow and with that fellow, you'll read a few articles, and.... Sound familiar? Don't count on it. This technology is more complex than that. Oh, you can learn some of the jargon, but let's see you write a program—even a simple one.

#### You're too busy?

Right! You've got all those commitments competing for your time. Don't we all! I bet every one of the 700 who've completed the course was just as busy. This is a matter of priorities. Think a little about the importance of microprocessors.

#### Don't have the prerequisites?

OK, that's legitimate. Why not get a group together and take our C30 course "Modern Logic Design." Then you'll have the prerequisite.

#### You'll wait for a better course?

There are all sorts of microprocessor courses available. Practically everyone in engineering education has one. But you'll have to go where it is and that won't be where you work. Also, it won't be tailored to RCA as this one is. And we doubt if you can find one as good as ours.

It's high time you think some about all this. Don't allow youself to be obsolete in microprocessor technology. Now's the time to get in. It's going to become more difficult as time passes.

-W.J. Underwood

**Bill Underwood** is Director of Engineering Professional Programs and responsible for the Continuing Engineering Education function.

Contact him at: Corporate Engineering, RCA Bldg. 204-2, Cherry Hill, N.J., Ext. PY-4383 microprocessor technology. A syllabus of the course is given in Table I.

Extensive use is made of the RCA COSMAC Microtutor, which is a microcomputer designed by RCA Laboratories. As mentioned previously, this small device is used by class participants for "hands-on" experience. Participants write programs in assembly language and run them on the "Tutor." This activity has resulted in several interesting projects.

### Future courses will deal with single-chip microprocessors and new applications.

Future course development, involving the COSMAC singlechip processor that replaces the two-chip version, is now being considered. As in the present course, the single-chip course would cover the hardware and software aspects of the microprocessor as well as the practical aspects. This includes the "hands-on" use of a Microtutor as an integral part of the course. More recent information on new applications of microprocessors and microcomputers will be included in the applied segment of the course.

The present course, C55, responded to a need and was successful because it was timely. This course brought a newly unfolding technology to the engineering work force. However, microprocessors differ from other technologies in that they put unprecedented power in the hands of the individual design engineer. The microprocessor course made this design tool understandable and useful.

#### Acknowledgment

Credit for the development and preparation of the microprocessor course is due Dr. Robert O. Winder, Solid State Divison, Somerville; Dr. Anthony Robbi, Solid State Technology Center, Somerville; Dr. Paul Russo and Michael Lippman, RCA Laboratories, Princeton; Richard Smith, Missile and Surface Radar, Moorestown; and Dr. Morton Lewin, formerly with RCA Laboratories and now with Rutgers University. The author acknowledges with gratitude their contributions in making the microprocessor course possible.

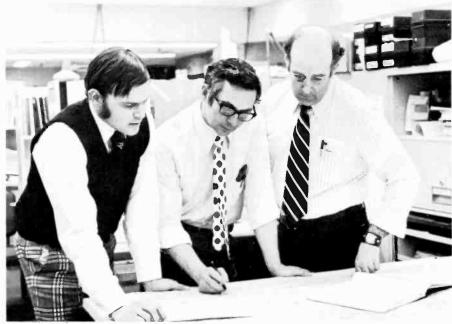

Gerry DiGirolamo is the course development administrator for the microprocessor course described in this paper. He has been working in Corporate Engineering Education since 1965. In the photo, he is directing a video-taping session.

Contact him at: Continuing Engineering Education RCA Bldg. 204-2 Cherry Hill, NJ Ext. PY-5141

Table I

**Microprocessors for logic design,** course outline. Sessions 16 and 17 are for review and final examination, respectively.

| Session                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 — overview                                                                                        | What a microcomputer is, and what a microprocessor is; why and when to use a microprocessor.                                                                                                                                                                                                                                                                          |

| 2 — basic processor<br>operations                                                                   | Binary numbers. Hexadecimal notation<br>and the concept of a "byte." Random-<br>access memory and its addressing<br>Read-write vs. read-only memories. In-<br>struction format of COSMAC.                                                                                                                                                                             |

| 3 — COSMAC<br>architecture I                                                                        | COSMAC instruction actions, including<br>the concept of the conditional branch.<br>The input/output instruction.                                                                                                                                                                                                                                                      |

| 4 — COSMAC<br>architecture II                                                                       | COSMAC binary arithmetic instructions.<br>COSMAC arithmetic-logic-unit.                                                                                                                                                                                                                                                                                               |

| 5 — architecture and<br>assembly language                                                           | COSMAC architecture review. COSMAC<br>instruction set. Assembler directives.                                                                                                                                                                                                                                                                                          |

| 6 — stacks<br>and subroutines                                                                       | Subroutines. Nesting. Stacks. Interrupt service routine.                                                                                                                                                                                                                                                                                                              |

| 7 — software techniques<br>and system<br>development                                                | Assembly-level programming. Trade-<br>offs between assembly level and higher<br>level languages. Time-sharing software<br>development systems. Stand-alone<br>microprocessor development systems.                                                                                                                                                                     |

| 8 — input/output<br>structures                                                                      | One-level I/O structure. Two-level I/O concept. Microprocessor-based system design. Operation of the DMA channel. External flags (EF1-EF4) to identify and decode interrupts. Interrupt priority.                                                                                                                                                                     |

| 9 — single-chip<br>COSMAC<br>microprocessor                                                         | Differences between the single-chip<br>COSMAC and its two-chip predecessor<br>The 1800 family of support chips.                                                                                                                                                                                                                                                       |

| 10 — midterm<br>review and test                                                                     | Review of sessions 1 through 9.<br>Demonstration of team projects.                                                                                                                                                                                                                                                                                                    |

| <ol> <li>11 — comparing<br/>microprocessors</li> </ol>                                              | LSI-oriented technologies. Intel 8080<br>and the Motorola 6800. Comparisons<br>with RCA COSMAC system.                                                                                                                                                                                                                                                                |

| 12 — bit-slice<br>processor                                                                         | Bit-slice microprocessor. Monolithic<br>Memories (MMI) 5701/6701. Application<br>to coordinate conversion.                                                                                                                                                                                                                                                            |

| 13 — RCA FRED<br>system                                                                             | FRED, an experimental model of a<br>minimum-cost home/school computer.<br>Use of an unmodified tv set as a display.<br>The power and flexibility of the dot-<br>matrix display philosophy.                                                                                                                                                                            |

| 14 — microprocessor-<br>based data<br>communications<br>system                                      | Narrowband dedicated leased-channe<br>store-and-forward data communications<br>system. The TTY and RS-232 com-<br>munications interface. Floppy discs and<br>floppy disc drives.                                                                                                                                                                                      |

| 15 — microprocessor-<br>based data<br>communications<br>systems and<br>multiprocessor<br>structures | Difference between bits/second and<br>baud rate. Floppy-disc seek, and latency<br>access, and data transfer times. Worst-<br>case and average disc thruput rates. Disc<br>thruput rates, related to data com-<br>munication system thruputs. The<br>general network and master-slave<br>organization. Two-microprocessor im-<br>plementation of leased channel system |

## Getting your hands on COSMAC hardware

Eventually, you're going to have to stop reading about microprocessors and start using them. Here are the COSMAC options available for when that time comes.

W.D. Lauffer

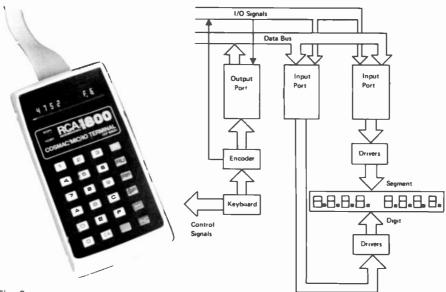

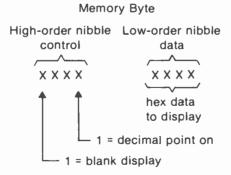

If you have no previous computer knowledge, Microtutor II is the place for you to start.

An improvement on the popular Microtutor I, it includes everything you need to write and run machine-language programs. You can learn to program games, educational exercises, and controllers quickly the *Microtutor Instruction Manual*'s lively style is an excellent example of making technical education painless.

Specifically, Microtutor II includes the CDP1802 microprocessor, 8-bit toggle-switch inputs, a crystal clock, a two-digit hex display, power supply, and a 256-byte RAM—all contained on two printed-circuit cards. There are also sockets for memory expansion and external options. For example, built-in operating system memory addressing is possible with only one more 256-byte RAM card.

# Or, start from scratch with the COSMAC "ELF."

The true experimenter will want to start with the individual chips and components and build up a microcomputer system. If this is the route you'd like to take, consider the COSMAC "ELF." Joe Weisbecker has written a series of articles on its construction, programming, and expansion in *Popular Electronics*. The issues are August '76, September '76, and March '77; a future article will cover video interfacing.

# COSMAC VIP is designed specifically as a home computer.

Sometime this year, VIP will appear on the market. A lowcost home computer aimed at video graphics and games, it uses a video monitor, audio cassette recorder, and a 16position key pad as I/O devices—keeping total system cost down. As designer Joe Weisbecker says, "It's not fair to ask the limited-budget, unsophisticated beginner to buy a system for several hundred dollars but then require an

Reprint RE-22-5-13

additional \$1000 for a terminal and enough RAM to make it useful." These I/O devices and a hex interpretive language make is possible for users to write and load their own games and programs simply and inexpensively.

#### Compare COSMAC with the competition.

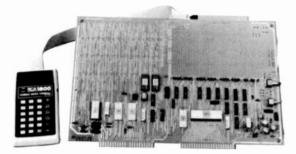

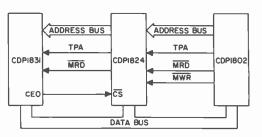

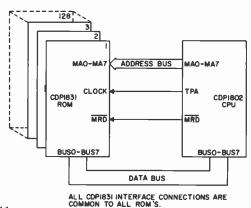

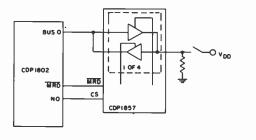

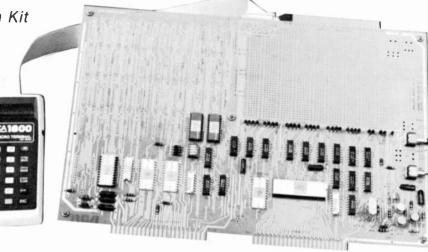

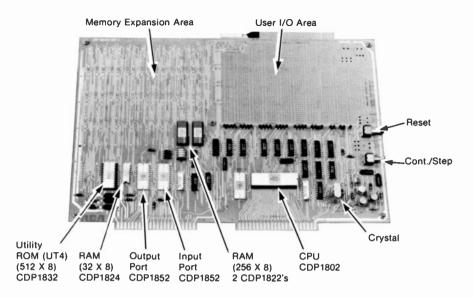

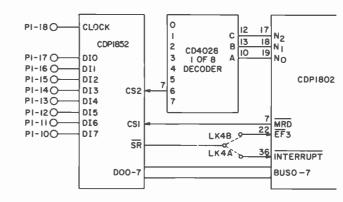

The COSMAC Evaluation Kit was designed to let you see just how RCA's 1800-series components work. The kit includes a printed-circuit board, a manual, and all the parts you'll need to evaluate, and design various systems around, the CDP1802 CPU, the CDP1832 ROM, the CDP1824 RAM, and the CDP1852 byte I/O port.

By adding a teletypewriter, hand-held Microterminal, or other terminal, you can use the built-in ROM utility routines to write programs and exercise the system. The board has room for memory and I/O expansion. For a detailed description, see Dennis Block's article on the Evaluation Kit is this issue.

# Do system design with the COSMAC Development System.

When you get down to making prototypes, you'll need to breadboard and debug hardware/software configurations on the way toward the final design. This is where the COSMAC Development System (CDS) fits. Its 19-inch rackmountable chassis provides a power supply, front-panel controls, printed-circuit backplane, a set of small printedcircuit boards, and 22 empty card slots. The basic set of cards can support up to 65,536 bytes of memory.

The CDS can be used with a number of different terminals ranging from paper tape to floppy disc; speed will depend on the investment you decide to make.

CDS software includes the COSMAC resident assembler and resident editor. Larry Solomon's paper in this issue should tell you how to go about using them while developing your COSMAC system.

# The CDP1802: a powerful 8-bit CMOS microprocessor

A.W. Young

The RCA CDP1802 microprocessor is a powerful and efficient single-chip 8-bit CPU that forms the heart of a generalpurpose microcomputer. It is easy to understand, easy to use, and low in cost. COSMAC architecture is based on the efficient use of short-word-length instructions within an interface restricted to 40 pins. Instead of using a minicomputer instruction set forced into 8-bit bytes with multiple-byte instructions, the COSMAC architecture has been developed around single-byte instructions.

Reprint RE-22-5-12 Final manuscript received November 29, 1976.

Alex Young, as Manager of Memory/ Microprocessor Design Engineering, is responsible for the design of the RCA1800 microprocessor family and its support systems. Previously, he had been Manager of COS/MOS Engineering and had designed over 20 CMOS circuits as a member of the Custom Circuit Design Group.

Contact him at: Memory/Microprocessor Design Engineering Solid State Division Somerville, N.J. Ext. 6468 Learn the advantages of COSMAC and its supporting family of chips; then find out what's involved in putting a system together.

The applications addressed by the CDP1802 include low-end minicomputer replacement, general-purpose controllers, emulation of hardwired logic, and totally new areas made possible by the advent of low-cost, stored-program, general-purpose data processing.

The CDP1802 is fabricated with a selfaligned silicon-gate CMOS technology, giving these results:

1) Full temperature range (-55°C to +125°C) for ceramic-packaged devices. 2) Low power dissipation—generally an order of magnitude or more less than other 8-bit microprocessors at maximum processor speed. Specifically, 50 mW at 6.4 MHz and 10 V; less for lower voltages and slower clock rates.

3) Single noncritical wide power-supply range. The CDP1802 will operate from 3 to 12 V over its full temperature range. Since the low-current single-voltage supply does not require sophisticated regulation, power-supply design is straightforward and simple. The CDP1802 has captured these CMOS technology features to the extent that it "looks like" another CD4000-series CMOS device. The COSMAC design, however, provides additional CMOS technology advantages, including:

1) *High noise immunity*. Inputs have been specifically designed to switch at 50% of supply voltage. To account for normal processing tolerances and the effects of temperature and voltage range, the design point translates to a guarantee of 30% of supply voltage.

2) Static operation. The CDP1802 is completely static. No minimum clock frequency is required and no complex multiphase clock generators are necessary. An on-chip oscillator amplifier is provided and requires a single feedback resistor and crystal connection to operate the clock. Alternately, an external single-phase RC oscillator could be used as the system clock.

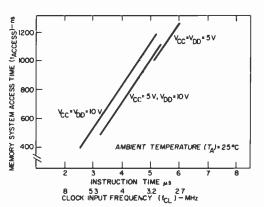

3) *High speed*. The CDP1802 will operate at 10 volts with instruction times

Table I

#### Features of the CDP1802 microprocessor.

Static silicon-gate CMOS technology-CD4000-series compatible Instruction times of 2.5 or 3.75 µs at 10 V Compatible with CDP1801 software Full temperature range (-55°C to +125°C) 30% noise immunity Single supply voltage Wide operating voltage range: 3-12 V No minimum clock frequency Low power-50 mW at maximum 10-V instruction time **TTL-compatible** Single-phase clock Optional on-chip crystal-controlled oscillator

Simple control of reset, start, pause, and load modes

8-bit parallel organization with bidirectional data bus

Works with any combination of the standard RAM and ROM

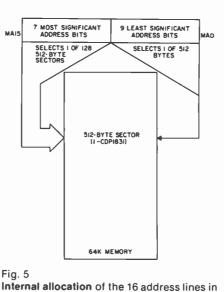

Memory addressing of 65,536 bytes

- 91 instructions

- On-chip DMA

- Program interrrupt

- Programmed I/O

- Four input flags

- Programmed output port (1-bit)

$16 \times 16$  register matrix for use as multiple program counters, data pointers, or data registers

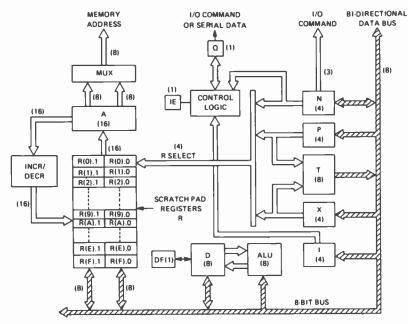

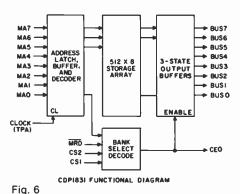

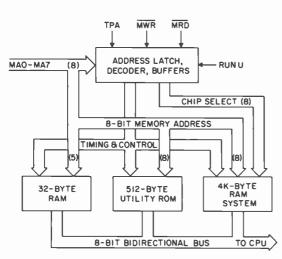

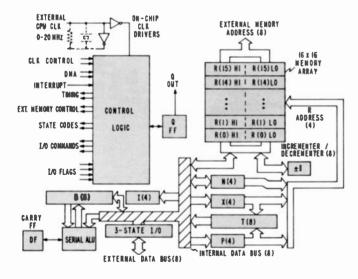

Fig. 1

**COSMAC** architecture is based on sixteen on-chip 16-bit scratchpad registers. Three 4-bit pointers (N, P, and X) can designate any of the 16 general-purpose registers as a program counter, memory address register, data source, or data destination.

of 2.5 or 3.75  $\mu$ s. All but long-branch and long-skip instructions execute in 2.5  $\mu$ s.

High output drive, low input current, low quiescent power, and extra static protection are also provided by design. The combination of COSMAC architecture and CMOS technology make the CDP1802 a high-performance costeffective device for a broad range of applications. Specific features of the CDP1802 are summarized in Table I.

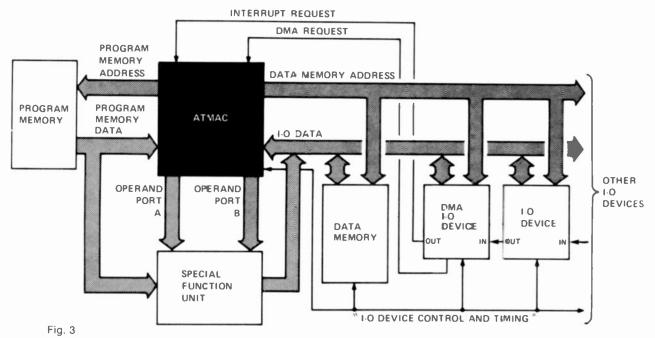

#### COSMAC architecture

The COSMAC architecture has been carefully developed for efficient operation in an 8-bit environment. Fig. 1 shows the internal processor architecture.

### The basic architecture provides 16 on-chip 16-bit scratchpad registers.

These registers (R) can be used to point to data in memory, point at programs, or store data (two bytes per register). An additional 8-bit data register (D) is used to buffer data transfers between an R register and the data bus and also functions as a conventional accumulator.

Any of the 16 general-purpose registers can be designated as a program counter, a memory address register, a data source, or a data destination by means of one of three 4-bit pointers. The register labeled P holds the 4-bit program-counter pointer. One instruction loads P with any 4-bit number, so the program counter can be changed by simply changing the number in P.

A second 4-bit register, N, stores a variable pointer carried along with the instruction. For example, a load instruction designates one of the 16 registers as an address register. The bits in the instruction doing the pointing are stored in N to designate the appropriate register.

A third 4-bit register, X, stores a pointer used to designate an address register during input/ouptut and some ALU instruction. Like P, it can also be loaded with any number by a single instruction.

Using four-bit pointers to indirectly specify a 16-bit address is a key feature of the COSMAC architecture.

This feature results in compact code because operand addresses can be efficiently carried by a short 8-bit instruction. By providing a generous quantity (16) of general-purpose registers, the programmer can set up many pointers to data tables and utility routines and so access them quickly and efficiently.

The notation R(P), R(N) or R(X) refers to the general-purpose register designated by

the 4-bit code in P, N, or X, respectively. M(R(P)), M(R(N)), or M(R(X)) refers to the memory byte pointed to by R(P), R(N), or R(X), respectively. Using hex notation, R(3) designates the general-purpose register corresponding to binary code 0011. R(3).0 refers to the least-significant byte of R(3), and R(3).1 refers to the mostsignificant byte of R(3).

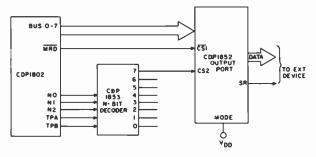

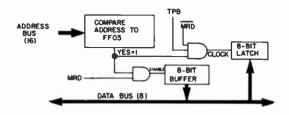

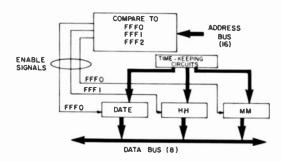

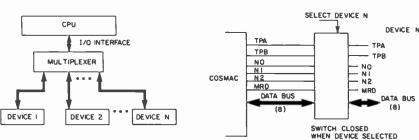

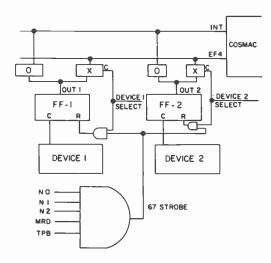

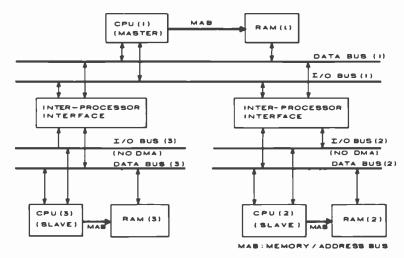

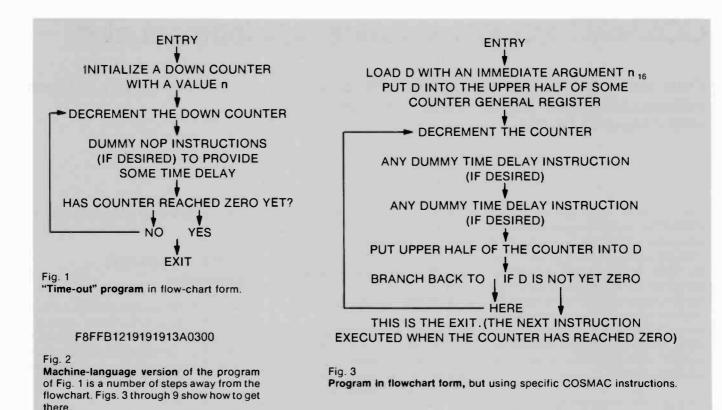

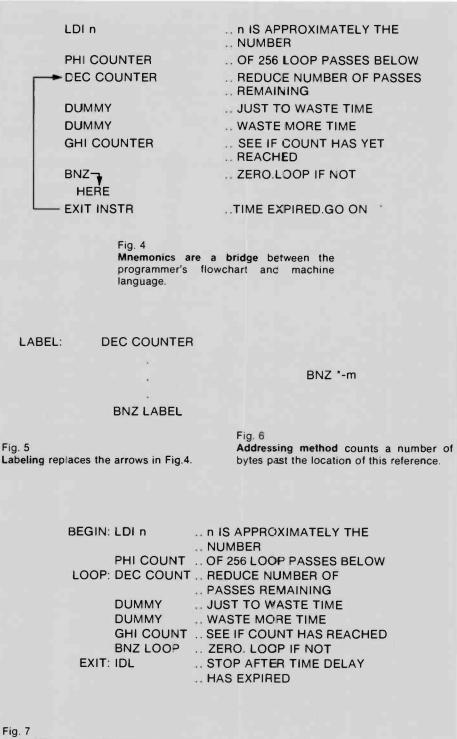

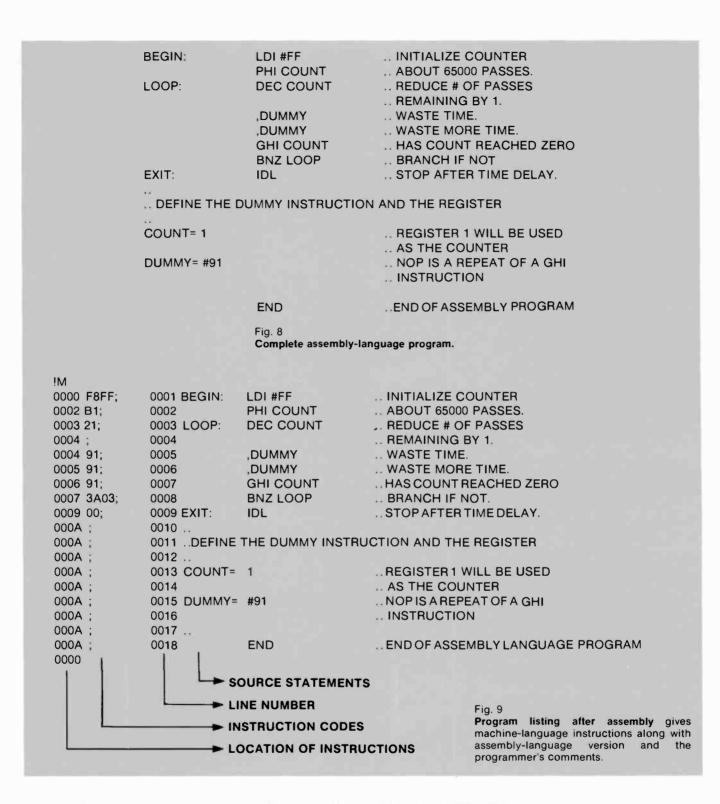

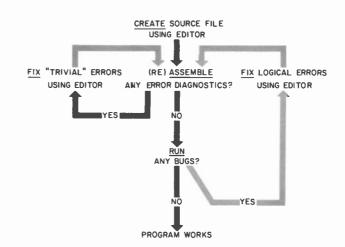

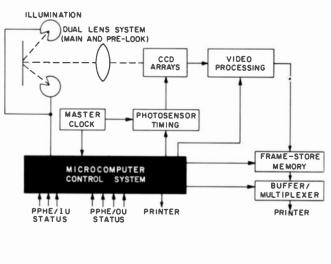

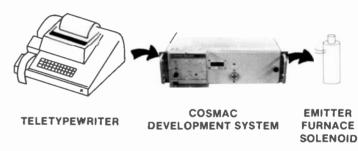

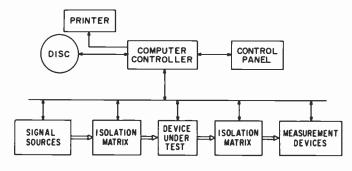

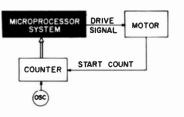

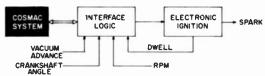

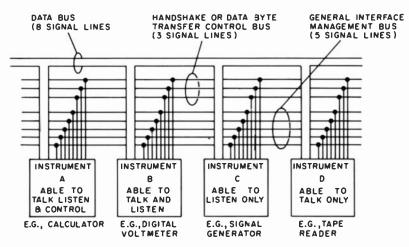

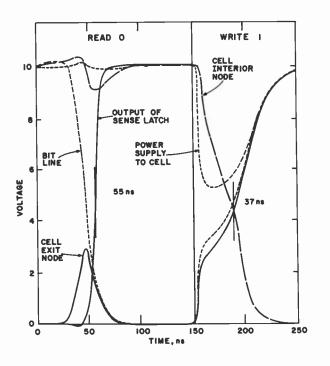

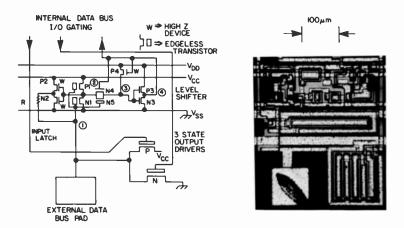

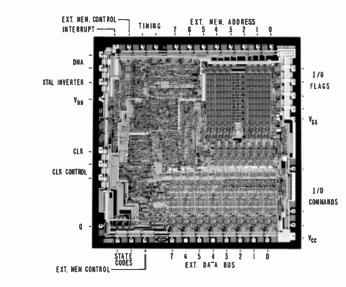

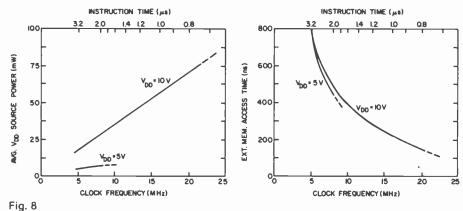

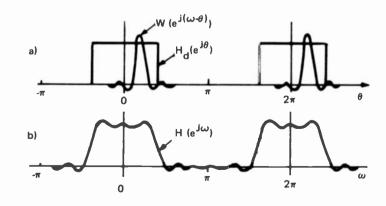

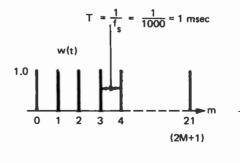

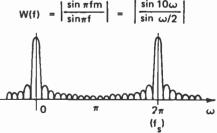

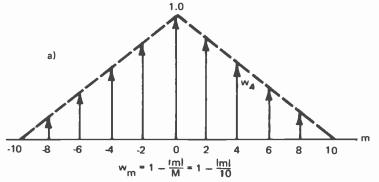

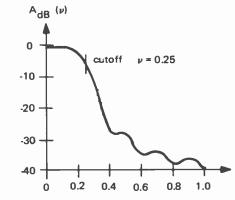

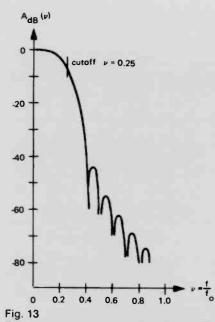

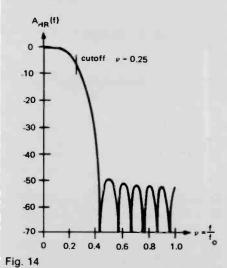

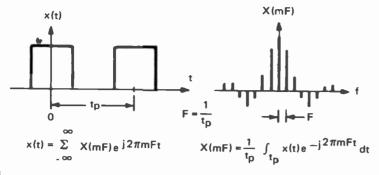

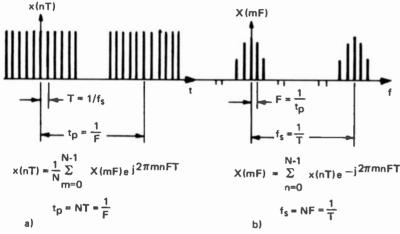

In addition to the general-purpose register array, data register, and register pointers, the COSMAC architecture provides a conventional ALU that performs arithmetic and logic operations between operands stored in D and M(R(X)) or M(R(P)), with the result stored in D. An overflow bit, DF, can be used for conditional branching.