## RBЛ Engineer

Vol. 25 No. 3

Oct./Nov. 1979

**Microprocessor applications**

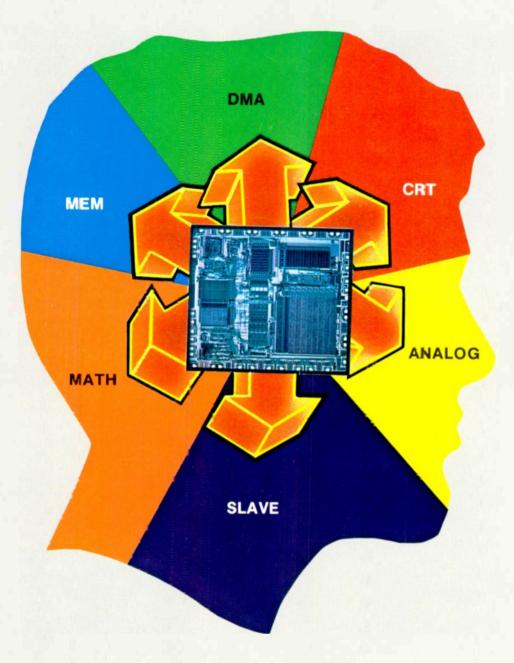

The cover is an artist's interpretation of an "intelligent" product with the microprocessor as its "brain." (In this case, we show the 1804 microcomputer, soon to be released on the market.) Each of the surrounding segments represents the types of devices which make the microprocessor work effectively in a product.

The ANALOG segment represents those devices which convert the incoming and outgoing signals from analog to digital and vice versa. CRT (cathode ray tube) refers to a display device for microcomputer to operator information. DMA (direct memory access) devices permit high speed access to data stored in the computer's memory without disrupting normal computer operation. The memory (MEM) segment represents the stored information of the system. MATH: Because microprocessors are usually not designed to perform arithmetic operations efficiently, special chips have been designed to perform these operations while interfacing with the microprocessor. Most multi-microprocessor systems consist of a master processor along with SLAVE processors that run in parallel with the master but take their direction from it.

The importance of choosing the appropriate microprocessor and peripheral devices for each application is stressed in Don Latham's cover message on the next page.

## **RB/I Engineer**

A technical journal published by **RCA Research and Engineering** Bldg. 204-2 Cherry Hill, N.J. 08358 Tel. 222-4254 (609-338-4254)

#### **RCA Engineer Staff**

**Tom King Betty Stotts** Louise Carr Frank Strobl **Betty Gutchigian Dottie Snyder**

Editor Assistant Editor Art Editor **Contributing Editor** Composition **Editorial Secretary**

#### **Editorial Advisory Board**

| Pete Bingham     | Div. VP, Engineering,<br>Consumer Electronics Div.                                     |

|------------------|----------------------------------------------------------------------------------------|

| Jay Brandinger   | Div. VP, SelectaVision<br>VideoDisc Operations                                         |

| John Christopher | VP, Tech. Operations,<br>RCA Americom                                                  |

| Bill Hartzell    | Div. VP, Engineering,<br>Picture Tube Division                                         |

| Jim Hepburn      | VP, Advanced Programs<br>RCA Globcom                                                   |

| Hans Jenny       | Manager, Engineering<br>Information                                                    |

| Arch Luther      | Chief Engineer, Commercial<br>Communications Systems Div.                              |

| Howie Rosenthal  | Staff VP, Engineering                                                                  |

| Carl Turner      | Div. VP, Product Assurance<br>and Planning,<br>Solid State Div.                        |

| Bill Underwood   | Director, Engineering<br>Professional Programs                                         |

| Joe Volpe        | Director, Product Operations,<br>Missile and Surface Radar                             |

| Bill Webster     | VP, Laboratories                                                                       |

|                  | Consulting Editors                                                                     |

| Ed Burke         | Administrator, Marketing<br>Information and Communications,<br>Government Systems Div. |

| Walt Dennen      | Director, Public Affairs,<br>Solid State Division                                      |

| Charlie Foster   | Mgr., Scientific Publications,<br>Laboratories                                         |

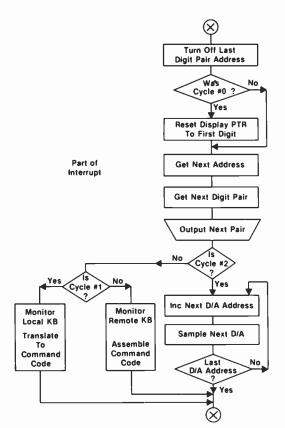

| John Phillips    | Mgr., Proposals and Publicity,<br>Automated Systems                                    |

•To disseminate to RCA engineers technical information of professional value . To publish in an appropriate manner important technical developments at RCA, and the role of the engineer . To serve as a medium of interchange of technical information between various groups at RCA . To create a community of engineering interest within the company by stressing the interrelated nature of all technical contributions . To help publicize engineering achievements in a manner that will promote the interests and reputation of RCA in the engineering field . To provide a convenient means by which the RCA engineer may review his professional work before associates and engineering management . To announce outstanding and unusual achievements of RCA engineers in a manner most likely to enhance their prestige and professional status.

#### **Microprocessors:**

#### their impact on system designs and systems designers

**Donald C. Latham**

r

Microprocessors are a milestone achievement in technology which will very likely have an impact on our lives comparable to that of the printing press, the internal combustion engine, and the transistor. Fulfillment of a technological promise can be so

long in coming that the impact of new products is not immediately recognized, but microprocessors have had an impact while still in their infancy. Significantly, the microprocessor potential continues to grow and promises to be overwhelming. On-chip density and speed improvements in the next three to five years may reach 100.000 gates per chip with internal clock rates over 100 MHz. With this level of technology, extremely complex computer and signal processing systems could be integrated on a single chip. Application designs will become even more software intensive, and hardware costs in both computer and memory will be driven down to a small fraction of the overall costs.

Full realization of microprocessor potential requires new and perhaps radical approaches and discipline in system design, software and firmware development, test and evaluation, and field service. Imagination and resourcefulness will be as necessary in this process as they were 25 years ago in the initial attempts to apply the transistor.

For many years after the invention of the transistor and its availability, we had to wean electronic equipment designers from the notion of replacing vacuum tubes with transistors on a one-for-one basis. Once this elementary notion was dismissed, the full potential of transistor circuits was realized, and an entirely new generation of electronic products appeared. An analogous situation exists with microprocessor applications. Many early applications simply mimicked hardware features in software, basically, doing the same thing in a different way. More recently, however, with the maturing of microprocessor architecture and software design and testing, we are beginning to realize applications which were initially considered impossible or unreasonable.

The necessity for radical departures in the way of doing business places new demands on design and systems engineers. Each engineer must become familiar with the new technology. Selecting the "right" microprocessor for an application is not a trivial chore: 60 to 80 different microprocessor architectures are readily available on the commercial market, and an additional three to ten times that number are available in supporting functional LSI arrays. Many key characteristics must be evaluated, such as flexibility of instruction set, data type manipulation, memory address modes, and flexibility of the I/O and of the arithmetic and logic operations.

Typically less than ten percent of a microprocessor-based project involves pure hardware design issues, while the remaining 90 percent is devoted to microprocessor selection, systems architecture planning, software design, system integration, and testing. As a result, today's microprocessor systems designers must make extensive hardware/software tradeoffs at the front end of the program, develop innovative programmable designs, create test philosophies, and employ key testing tools such as logic analyzers, pattern generators, and in-circuit emulators.

In this issue, we have a sampling of RCA microprocessor applications. A host of exciting, and even revolutionary, new microprocessorbased products and systems are soon to follow.

wald C. Lat

**Donald C. Latham** Division Vice President, Engineering Government Systems Division Moorestown, N.J.

## Highlights

#### introduction

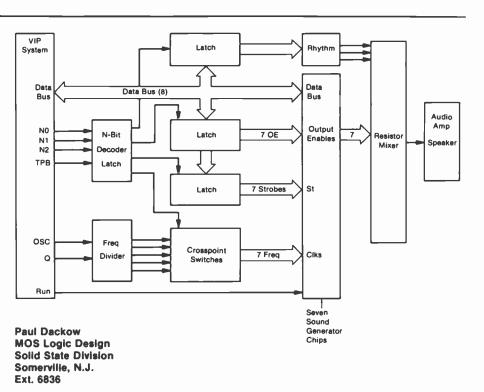

why is the microprocessor industry growing at such a rapid pace and what will be its effect on the application's concept?

#### microprocessor-based products

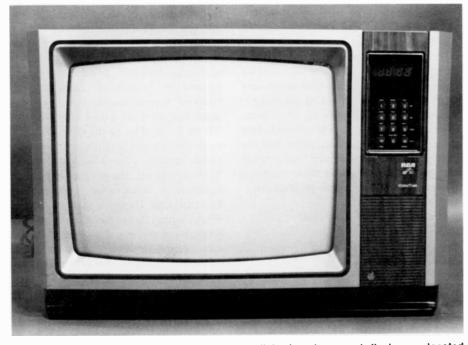

RCA is making intelligent TV receivers and cameras.

#### microprocessors in systems

microprocessors aid in energy conservation for automotive, temperature-regulation and communication systems.

#### microprocessors in manufacturing

introducing intelligence into automatic testing saves money and reduces errors in electrical parts inspection.

#### In future issues

quality & reliability, RCA worldwide, color TV receivers, anniversary issue

## CB/A Engineer

Vol 25|No. 3 Oct.| Nov. 79

, **\***

.

,

.

| introduction                        | 4  | The microprocessor industry and the emerging<br>applications revolution<br>P.M. Russo               |

|-------------------------------------|----|-----------------------------------------------------------------------------------------------------|

|                                     | 14 | A microcomputer glossary<br>P.P. Fasang                                                             |

| microprocessor-based<br>products    | 17 | The "berry picking" approach to computer systems development<br>B. Astle¦M. Lurie¦K. Schroeder      |

|                                     | 22 | Intelligent controllers for color-television receivers<br>K. Karstad                                |

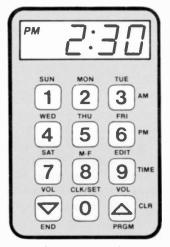

|                                     | 27 | The AutoProgrammer<br>B.W. Beyers A.J. Suchko                                                       |

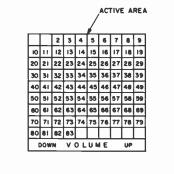

|                                     | 30 | 82-channel, single-touch TV tuning system<br>D. Sprague                                             |

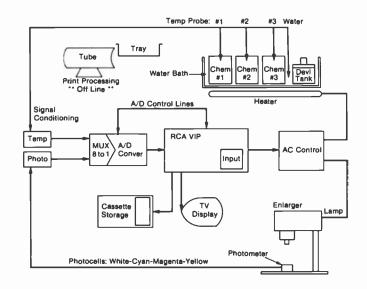

| microprocessors<br>in systems       | 34 | Software techniques for a microprocessor-based data<br>acquisition device<br>H.A. Goldstand         |

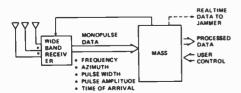

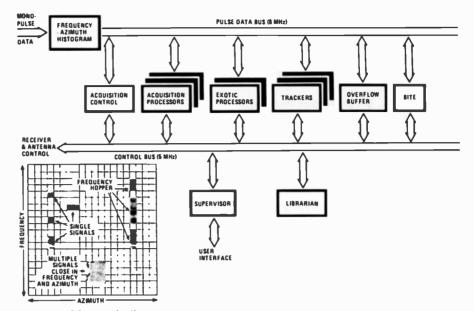

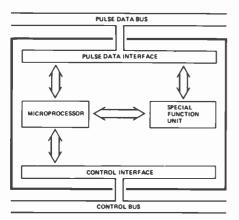

|                                     | 39 | MASS—a modular ESM signal processor<br>A. Kaplan D.L. Sherwood                                      |

|                                     | 43 | Microprocessors in automotive electronics<br>D.R. Carley                                            |

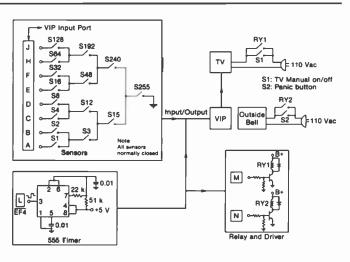

|                                     | 47 | Alarm status monitoring and reporting<br>W.D. Henn                                                  |

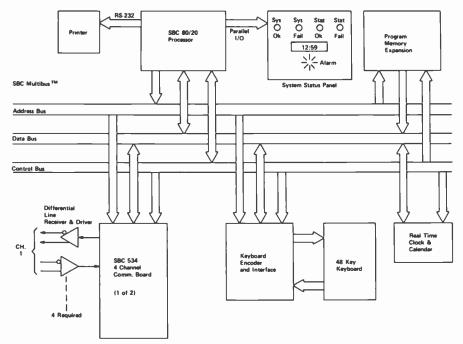

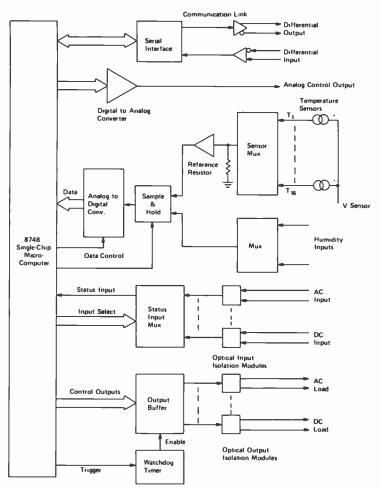

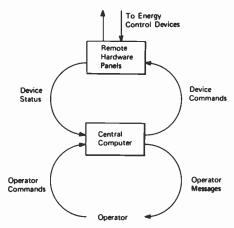

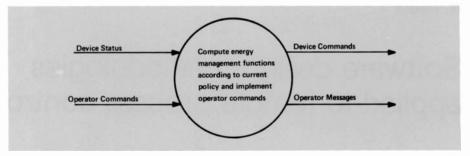

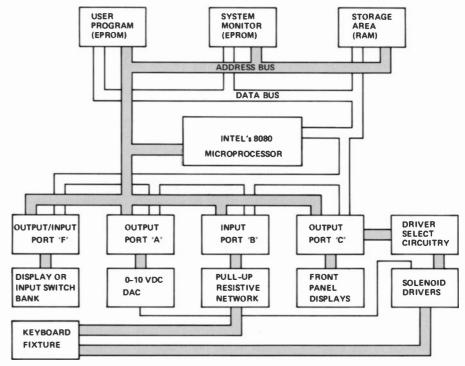

|                                     | 50 | Microcomputer system design for remote process control<br>A. Abramovich A.K. Patel                  |

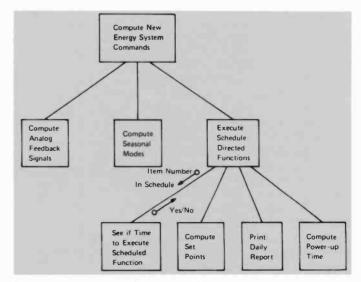

|                                     | 55 | Software design methodologies applied to remote process contro<br>R. Poulo                          |

| microprocessors<br>in manufacturing | 60 | Dedicated microprocessor-based testers for improved<br>fault isolation<br>M. Herskowitz N.J. Fedele |

| on the job/off the job              | 64 | Reports on how RCA people are using microprocessors                                                 |

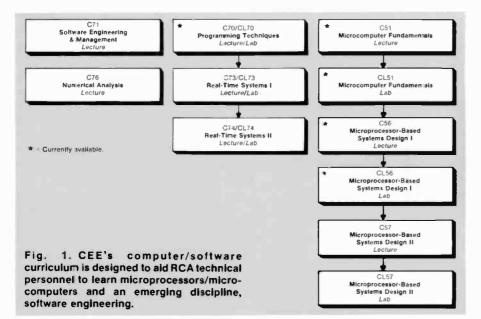

| learning about<br>microprocessors   | 68 | Microprocessor/software-oriented educational program at RCA<br>P.P. Fasang                          |

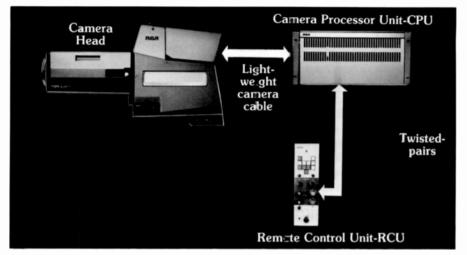

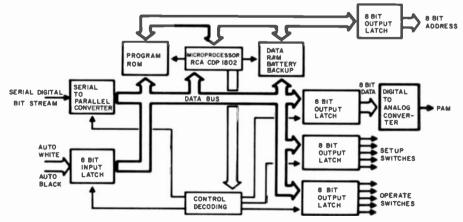

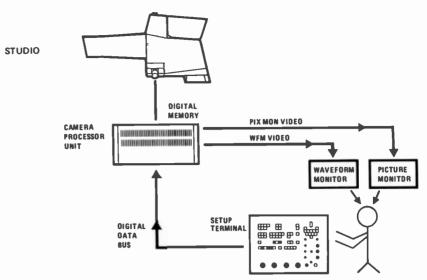

| general interest                    | 72 | The TK-47 Autocam television camera<br>L.J. Thorpe R.A. Dischert                                    |

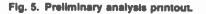

|                                     | 76 | Rapid RMA assessment — the painless plot<br>F.A. Eble/E.W. Richards, Jr.                            |

| departments                         | 81 | Dates and Deadlines                                                                                 |

|                                     | 82 | Pen and Podium                                                                                      |

|                                     | 84 | Patents                                                                                             |

|                                     | 85 | News and Highlights                                                                                 |

|                                     |    | Copyright © 1979 RCA Corporation<br>All rights reserved                                             |

. . ۲

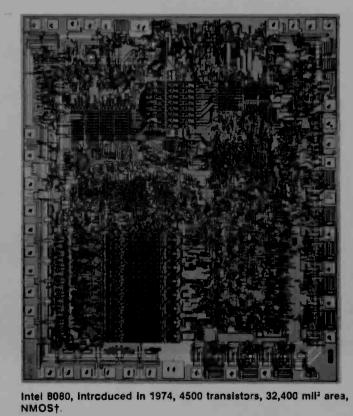

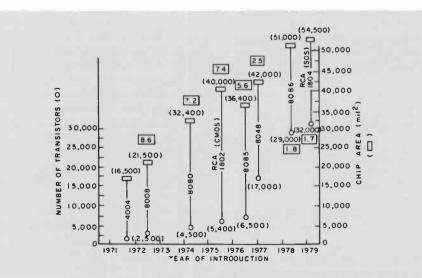

RCA 1802, Introduced in 1975, 5400 transistors, 40,000 mil<sup>2</sup> area, CMDS.

intel 8086, introduced in 1978, 29,000 transistors, 51,000 mil2 area, HMOST.

**†Courtesy of INTEL corporation**

Russo: The microprocessor industry and the emerging applications revolution

RCA 1804, Introduced in 1979, 32,000 transistors, 54,500 mil<sup>2</sup> area, CMOS SOS.

4

## The microprocessor industry and the emerging applications revolution

Microprocessor and microcomputer applications have a profound impact on industry as well as the individual consumer — yesterday, a computer; today, a microprocessor; tomorrow, personalized microcomputer systems.

Abstract: The capability of large scale integration and its interaction with rapidly evolving computer and microprocessor technologies are reviewed. The microprocessor industry is discussed with special emphasis on categorizing microprocessors and projecting unit and dollar sales volumes. Industrial, commercial and consumer applications of microprocessors are reviewed, focusing primarily on new products made possible by this new technology. Finally, a brief look is taken at future trends in microsystem evolution and their impact on the emerging applications revolution.

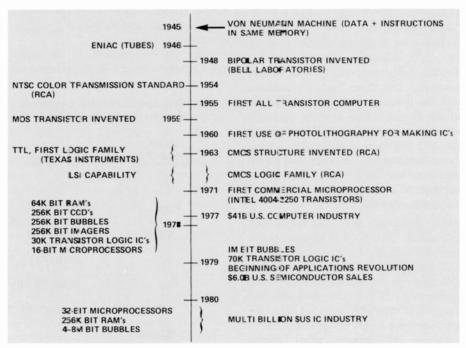

The rapidly unfolding digital LSI revolution, which began in the late 1960s, is leaving a permanent imprint on many aspects of our lives. The first computer revolution began with Von Neumann's work in 1945,<sup>1</sup> and rapidly evolved to today's highly computerized and dataoriented society. The second computer revolution began with the commercialization of the microprocessor in 1971, when Intel introduced the 4004, 4-bit single chip central processing unit (CPU).<sup>2</sup> It took a few years for the business impact of microprocessors to be understood, and a few more years for the potential effect on the consumer to be visualized.<sup>2</sup>

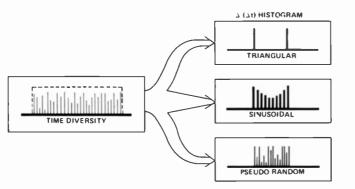

The rapid progress in computer and digital electronics technology is illustrated

Reprint RE-25-3-1

in Fig. 1. It took a decade from the 1945 invention of the stored program computer (instructions and data stored in same memory) to the development of the first alltransistor machine. A decade later, standard digital logic families such as Texas Instrument's TTL and RCA's COS/MOS began to emerge. This is the era when Large Scale Integration (LSI) capability, which allowed one to interconnect large numbers of transistors on a single piece of silicon substrate, began to evolve. As stated above, the first microprocessor  $(\mu P)$ , the Intel 4004, was commercialized in 1971. The 4004 concept arose from attempting to satisfy several custom calculator chip designs with a single family of LSI parts. Though Intel is often granted the honor of inventing the  $\mu P$ , it is fair to point out that many computer architects with an interest in LSI were postulating, and working towards microprocessors prior to this date. The early work on the RCA 1802, for example, predates the Intel

Fig. 1. Evolution in technology.

Final manuscript received Aug. 29, 1979.

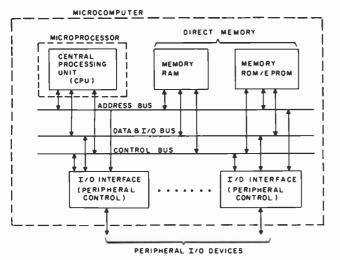

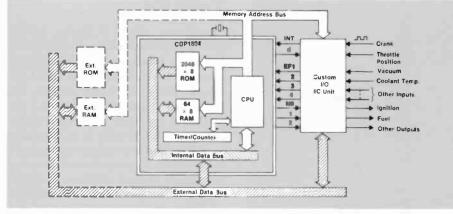

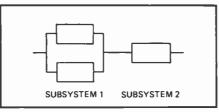

Fig. 2. The fundamental sub-systems of any single-processor system.

4004 announcement. Less than a decade after the Intel 4004, million-device integrated circuits (ICs) are being sampled, powerful 16-bit microprocessors are a reality, and the applications revolution marches on to the accelerating rhythm of the LSI drum.

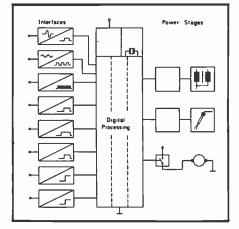

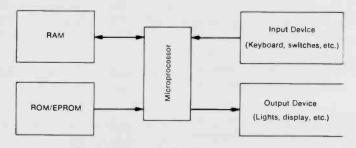

### Microprocessors and microcomputers

Any single-processor computer system, from the simplest microwave oven controller to a sophisticated data processing system, consists of three classes of subsystems: the central processing unit (CPU); direct memory, which can be READ/WRITE (RAM) and/or READ-ONLY (ROM); and input/output (I/O) interfaces for peripheral control (Fig. 2). The CPU subsystem performs all the classical arithmetic, logic, and control functions. The direct memory contains both the program (instructions to be executed by the CPU) and the currently active data on which the CPU is operating. The 1/O interfaces represent the critical communication links between the internal computer operations and the external world of I/O devices such as mass memory, keyboards, displays, etc.

Microprocessors  $(\mu Ps)$  are single chip realizations of the CPU function of a computer system. Microcomputers  $(\mu Cs)$ , in the context of this paper, are single chip realizations of the entire computer system function, i.e., CPU, RAM and ROM, and enough I/O capability to permit the single chip implementation of desired control functions. Additionally, many microcomputers sport an option of having either mask-programmed ROM (low-cost for high-volume applications) or EPROM (UV light erasable, reprogrammable for low-volume applications). From the above, it appears that minimal configurations for microprocessor-based systems require three chips. Other system architectures may require the use of multiple CPUs to achieve desired objectives.<sup>4,5,6</sup>

#### Trends in LSI/ VLSI technology

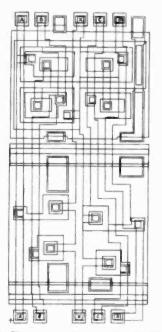

The history of LSI and VLSI (Very Large Scale Integration) is brief but explosive. Figure 3 illustrates the rapid evolution in IC capacity, with the upper boundary representing regular structures (e.g., RAMs, ROMs, etc.) while the lower boundary represents random logic (e.g., microprocessors).

Since the development of the metal oxide semiconductor (MOS) transistor in

Table I. Evolution of EPROM technology.

| M                                                                                     |                       | INTEL BUBBLE             |

|---------------------------------------------------------------------------------------|-----------------------|--------------------------|

| C 4K REGULAR<br>C 4K STRUCTURES<br>C 4K (RAM, ROM, CCD)                               | TI 64 K<br>BIT<br>RAM | MOTOROLA<br>MC 68000     |

| STRUCTURES<br>4K<br>STRUCTURES<br>(RAM, ROM, CCD)<br>256<br>RANDOM<br>LOGIC<br>RANDOM |                       |                          |

| Ö<br>60 '65 '70<br>YEAR                                                               | /75                   | /<br>/79 <sup>/</sup> 80 |

Fig. 3. Evolution in digital semiconductor IC complexity.

the late 1950s, device complexity has doubled every year. The primary contributing elements to this growth rate are larger die size, higher density (finer microstructure), and advances in device design. This rate of progress has not been uniform for all technologies — for example, EPROM technology has been evolving at a rate where doubling in complexity has occurred about every two years (Table 1).

Beyond 1979, the growth rate in IC complexity will probably slow to doubling every 1.5 to 2 years. The reasons for this slowing are due partially to technological limits being approached, but primarily to the fact that it is not yet clear how designers can effectively make use of these complex ICs containing hundreds of thousands of transistors.<sup>7,8</sup>

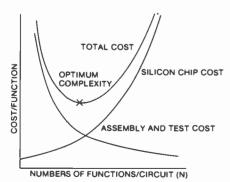

The growth in complexity has a direct effect on the cost of integrated circuits. The cost of LSI integrated circuits consists of two major components: silicon chip cost and assembly/test cost. Based on the

| YEAR<br>(SAMPLED) | EXAMPLE             | BITS | BYTES |

|-------------------|---------------------|------|-------|

| <b>'71</b>        | 1702                | 2K   | 256   |

| '73               | 2704                | 4K   | 512   |

| '75               | 2708/2758           | 8K   | 1K    |

| '77               | 2716 INTEL,TI       | 16K  | 2К    |

| <b>'79</b>        | 2532/2732 TI, INTEL | 32K  | 4K    |

| <b>'80/'81</b>    | TI, MOSTEK, INTEL   | 64K  | 8K    |

| <b>'82/'85</b>    | -                   | 128K | 16K   |

|                   |                     |      |       |

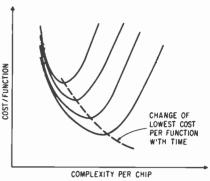

available design techniques and process technology, silicon chip cost is roughly an exponential function of complexity. On the other hand, the assembly/test cost, as a first approximation, can be treated as independent of complexity. This leads to an inverse relationship between assembly/test cost per function and complexity. By combining these two components, the cost per function will have a minimum corresponding to the optimum complexity for the current state of the art design technique and process technology (Fig. 4). As time goes on, the silicon chip cost will decrease due to improving density. processing technology, and material. This will result in the optimum cost per function decreasing with time as shown in Fig. 5.

From Table I and Figs. 4 and 5, it is apparent that, as time progresses, more and more of the system will fit on a single integrated circuit, and the cost per computation function will decrease exponentially. This will make possible distributed intelligence in the broadest sense, where every sub-system will have local processing capability and the ability, where needed, to interact with other intelligent sub-systems or systems.

## Microprocessor impact on LSI/VLSI technology

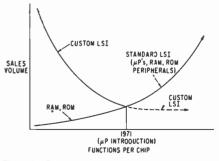

The rapidly increasing use of LSI and VLSI in non-memory applications would not have occurred if the microprocessor had not come to the rescue. Figure 6 illustrates this phenomenon. Prior to the invention of the microprocessor, ever more complex ICs were developed to perform ever more specialized applications. Hence, except for a few large volume market segments (e.g., data communications), IC volume decreased rapidly with complexity.

With the invention of the microprocessor, it became economically viable

Fig. 4. LSI cost contributing factors showing optimum complexity for lowest cost per function.

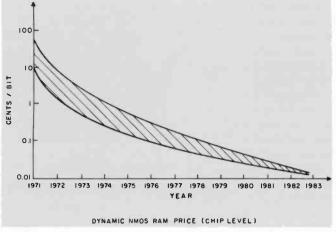

to develop large complex random logic ICs and then specialize their application in software. In fact, it is the invention of the stored-program computer itself (of which  $\mu$ Ps and  $\mu$ Cs are embodiments) that has spurred the use of RAM and ROM and has generated the volumes needed to attain the exponentially decreasing per-bit costs. Figure 7 illustrates the evolution of dynamic NMOS (N Channel MOS) RAM cost during the past decade, projected through the early 1980s. It is our best guess that costs of 0.012 cents/bit will be reached in the early 1980s with 64 K-bit dynamic RAM chips selling for about \$8 each in volume. These costs are possible because NMOS RAMs are the dominant memory chips used in computer systems giving rise to extremely large volume production with the attendant learning curve benefits. For example, Mostek Corporation, which controls about 30% of the 16K NMOS dynamic RAM market, is expected to double production to about 30 million units in 1980 - a very large volume indeed. Density improvements in NMOS RAMs are yielding average areas under 0.50 mils<sup>2</sup> (1 mil = 0.001 in.) per transistor (e.g., National NCM 4164 64K-bit RAM chip has an area of 3400 mils<sup>2</sup>).

#### Categorizing microprocessors and microcomputers

In categorizing  $\mu$ Ps and  $\mu$ Cs, discussion will be restricted to MOS devices. Bipolar devices, to date, have been extensively used only in specialized applications requiring high throughput. The bulk of bipolar  $\mu$ Ps (there are no bipolar  $\mu$ Cs) are of the bitslice variety requiring multi-chip CPU implementations (the Fairchild 9440) which emulates the Data General NOVA instruction set is a noteworthy exception). Finally, 4-bit  $\mu$ Ps will not be discussed (4bit  $\mu$ Cs will be discussed), since they are obsolete and their days are numbered — in fact, Intel Corporation is no longer taking orders for its 4040 family of 4-bit  $\mu$ Ps.

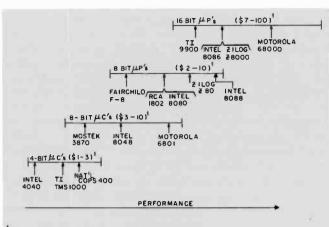

Microcomputers range from relatively simple 4-bit devices (Texas Instruments TMS 1000 series, National COPS 400 series, etc.) with volume costs in the \$1-3 range, to more powerful 8-bit devices (Mostek 3870 series, Intel 8048 series, etc.) with volume costs in the \$3-10 range.

Microprocessors, on the other hand, vary from mid-range machines (Intel 8085, RCA 1802, Zilog Z80, etc.) with volume CPU costs in the \$2-10 range, through

Fig. 5. Cost per function decreases with time.

higher performance 16-bit CPUs (Motorola 68000, Zilog Z8000, Intel 8086, Tl 9900, etc.) whose capability approaches that of mid-1970s minicomputers, and whose chip costs may range from tens to hundreds of dollars. These latter devices are relatively new to the market (8086 sampled in 1978, Z8000 and MC68000 sampled in late 1979), and hence their costs will tumble as we move down the learning curve.

Figure 8 presents a rough view of processor performance ranges vs computer category. Note that the dollar figures shown represent mature product, i.e., those in volume production. Note also that even though many 8-bit  $\mu$ Ps cost less than 8-bit  $\mu$ Cs, the latter have on-board RAM, ROM and 1/O, which usually results in far lower system cost.

Microprocessors and  $\mu$ Cs exist in a wide variety of technologies. *p*-channel MOS (PMOS) is fading as a viable technology. *n*channel MOS is the dominant technology and is the standard for all existing 16-bit machines. In the 4- and 8-bit categories, CMOS parts are available for low power applications (RCA 1802, CMOS TMS 1000, etc.), at nominal cost premiums along with bipolar devices (Fairchild 9440, etc.) for high performance. Silicon-onsapphire (SOS) parts are not yet commercially available.

Fig. 6. Custom vs. standard LSI sales volume vs. chip complexity.

Russo: The microprocessor industry and the emerging applications revolution

ALL COSTS ASSUME MATURE PRODUCT

Fig. 7. Evolution in the chip level price per bit of NMOS RAM. Fig. 8. Categorizing  $\mu$ Ps and  $\mu$ Cs.

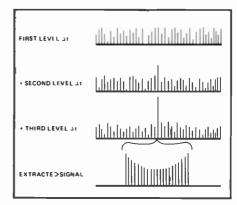

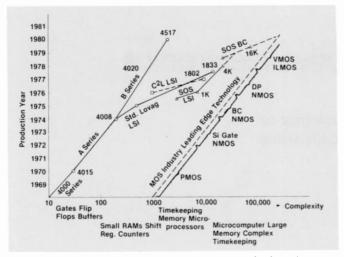

The unquestionable technological leader in the microprocessor industry has been Intel Corporation. Figure 9 illustrates the evolution of its  $\mu P$  and  $\mu C$  families. Note the rapid improvements in technology (average transistor area) which went from 8.6 mil<sup>2</sup>/transistor for the 8008 in 1972 to  $1.8 \text{ mil}^2/\text{transistor}$  for the 8086 in 1978. RCA's only commercially available  $\mu P$ , the 1802, is included for completion, along with the soon-to-be-sampled SOS 1804  $\mu$ C. The average transistor area for the RCA 1804 is slightly lower than that of the Intel 8086. This is probably due to the 1804 containing a significant amount of on-chip memory (2 K bytes ROM, 64 bytes RAM), whose regular structures yield higher packing densities. Photomicrographs of the Intel 8086 and of the RCA 1804 are presented on page 4.

## The microprocessor industry

The  $\mu P$  has changed the early trends of LSI development and has reoriented those efforts to the design of CPUs, memories, and ever more complex peripheral ICs which permit the rapid development of low chip count dedicated computer systems. As the industry matures, it is rapidly moving away from merely making ICs towards a fullsystem-capability industry. Intel, the leader in IC technology, is also the leader in the development of support circuits, single board computer systems, and development systems. More recently, Intel has begun to market preprogrammed devices which satisfy desired system level functions. The manufacturing cost of these devices is the same as that of unprogrammed devices, but, since there is added value in the eyes of the customer, margins can be improved.

#### Projecting trends

Major microprocessor and microcomputer application areas will be discussed in the following section. Here, we will attempt to summarize business trends and to project them a few years into the future. Before doing so, it is noteworthy to point out that most published sales figures and forecasts relate to non-captive markets. Captive markets (such as TI, IBM, DEC and ATT production for internal use) account for a significant fraction (close to 50%) of world production.

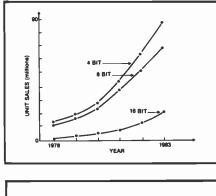

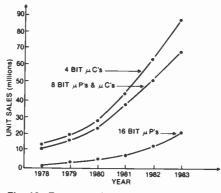

The market for microprocessors will have a compound growth rate of about 25% through the early 1980s, approaching an annual volume of 200 million units by 1983, with a market value approaching 500 million dollars. When one adds sales of supporting ICs such as peripherals, RAMs, ROMs, and EPROMs, the market swells to about 1.5 billion dollars per year. Figure 10 presents, roughly, how unit sales for 4bit  $\mu$ Cs, 8-bit  $\mu$ Ps and  $\mu$ Cs, and 16-bit  $\mu$ Ps are expected to grow.<sup>9-12</sup>

The numbers for 8- and 16-bit devices are similar to the ones generated in a recent Creative Strategies report.<sup>11</sup> Figure 10, however, projects larger unit sales for 4-bit devices than does Creative Strategies (19.5 million units in 1983). It should be noted, however, that the Creative Strategies numbers are not consistent with current industry production trends. Texas Instruments, in their sales presentations, claims that it has a capacity to produce "several million" TMS 1000 machines per month. Additionally, the real volume applications for 4-bit devices are in the consumer area, and this area is just beginning to explode. The trend in this area will be to pull more system capability onto the 4-bit chip to lower system cost rather than to go for unneeded computing power represented by 8-bit architectures.

Fig. 9. INTEL and RCA microprocessor and microcomputers. (Products showing chip area and complexity evolution. Control denotes average transistor area in mil<sup>2</sup> (D/O).

#### Support items count in the cost

Key ingredients in the success of a microprocessor manufacturer in addition to price and delivery, are system development support and the availability of support chips and of single board computer families. The microprocessor itself usually represents a small fraction of the system LSI cost, usually less than 1% for industrial and commercial applications and perhaps 5-25% for consumer products (note that for  $\mu$ Cs, the CPU portion usually takes up much less than half the IC area). Because of the above, microprocessor applications are rarely designed to maximize CPU utilization but rather to minimize system cost (development and production). Thus the ease with which one can develop a system (development support) and the availability of peripheral ICs (low system chip count) usually dominate the CPU selection process.13

#### Applications overview

The  $\mu P$  revolution has truly become an applications revolution. By the year 2000, 5 to 10 *billion*  $\mu Ps$  and  $\mu Cs$  will be in service — about one for each living person on earth. In the majority of cases, the person interacting with the  $\mu P$  or  $\mu C$  will not know that a computer is involved. One will simply have improved service or functionality for the task at hand.

The applications of  $\mu$ Ps and  $\mu$ Cs break down into three broad categories industrial, commercial, and consumer.

Industrial applications are those that employ microprocessors in the design or manufacturing processes of the industry under consideration. These include process control, testing, data acquisition, numerical control, instrumentation, and robotics.

Commercial applications are those used in providing new or improved services and/or ways of doing business. These include communications (data and telephone), point-of-sale systems, intelligent cash registers and business uses (word processing, accounting, etc.).

Consumer applications are those that either add features or improve the cost/performance of existing consumer products (ignition control in automobiles, timing control in microwave ovens, etc.), or those that give rise to entirely new classes of consumer products (personal computers, programmable video games, etc.).

The following three sections briefly

Fig. 10. Forecast of annual unit  $\mu$ P and  $\mu$ C sales through 1983.

overview industrial, commercial, and consumer applications of microprocessors, and provide references to permit the interested reader to pursue the subjects in depth. One measure of the extent of the ongoing microprocessor application revolution is the February 1978 issue of the *IEEE Proceedings*, which was dedicated to that very subject. This special issue of the *RCA Engineer* that you are reading gives further testimony to this rapidly evolving technology.

#### Industrial applications

Microprocessors are having a major impact on industrial applications, including the areas of testing, control, instrumentation, data acquisition, numerical machine control, and even robotics. In all these areas, equipment offering expanded functions, better human interfaces, improved reliability, and lower cost are emerging.

Testing. Automatic Test Systems (ATS), which can be used to automatically identify component, subsystem and system faults, are becoming increasingly important from the view of reliability and maintainability. Reliability is improved with ATS since marginal components and subsystems are replaced prior to equipment shipment, resulting in a lower probability of field failure. Ease of maintenance is also improved since system-level tests can identify the probable subsystem failures, and so give rapid repair turnaround and, hence, reduced downtime.

ATS has historically been used in large military applications and in automatic testing of complex parts, where expensive test fixtures can be economically justified. The advent of microprocessors has opened many avenues for low-cost dedicated testers which means that industries can now economically justify automated and more complete testing of low-cost/lowcomplexity subsystems right on down to the component level.

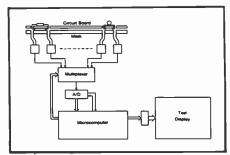

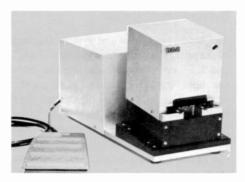

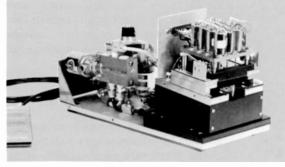

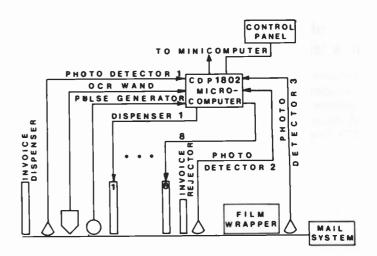

Reference 16 describes a very successful application of RCA's COSMAC microprocessor to 100% testing of populated TV convergence boards (Fig. 11). Another example is an RCA-developed potentiometer tester.<sup>17</sup> Further examples of  $\mu$ P testing applications are presented in this issue. Many other examples can be found in the *Proceedings* of the IECI '79.<sup>18</sup>

Process Control and Data Acquisition. The process control and data acquisition areas differ from testing in that they must operate in real time.<sup>19-21</sup> This implies that the microcomputer must have time responses rapid enough to accommodate the process control or data acquisition system under consideration. Whether we are talking about controlling a power generation system or a complex chemical plant, the system must sample critical system outputs and generate suitable system inputs often enough to achieve the desired level of control.

The advent of low cost  $\mu$ Ps means that dedicated, intelligent subsystems are now viable. For example, a  $\mu P$  system can be dedicated to data acquisition alone. A dedicated microprocessor can perform statistical analysis on the job, format data for more efficient off-line processing, and perform periodic self-checking and autocalibration. However, its main advantage may, in fact, be the flexibility resulting from distributed software control. Simple software changes can alter the sampling rate, specify new data formats, or alter the self-checking algorithms. This results in better human engineered outputs, modularity in hardware (improved maintenance) and slower system obsolescence.

Before the use of  $\mu$ Ps became

Fig. 11. A COSMAC-based system for 100% testing of TV convergence boards (on-line in Bloomington).

#### Careful choice of system development support items is a must.

The importance of quality system development aids cannot be overemphasized for any  $\mu P$  or  $\mu C$  to be selected by a significant fraction of users. On the software side, editors, file management systems, assemblers and high level language translators are essential. These may be time-sharing based or resident in a stand-alone development system (e.g., COSMAC CDS, or Intel MDS). On the hardware side, In-Circuit Emulators (ICE pioneered by Intel), are necessary for efficient system debugging<sup>14</sup>, along with standard facilities such as mass memory (usually floppy disc), hard copy output, terminal input, EPROM burning facility, and standard I/O ports (e.g., IEEE 488 or RS-232).

Each manufacturer of  $\mu$ Ps or  $\mu$ Cs provides the user with a variety of hardware and software development aids. Additionally, several independent companies are marketing general purpose development systems (Tektronix, Futuredata, Hewlett-Packard). In these systems, the user need only plug-in the appropriate characterization module, and insert the appropriate software diskette to create an environment customized to the  $\mu$ P/ $\mu$ C at hand.

#### Support systems options

Advantages of using the vendor's own development systems are their

timeliness (they can usually support a new device soon after it is sampled), and lower cost. The key advantage of the more universal systems is that one capital investment permits the development of products using different microprocessor families. For example, the Tektronix 8002 system supports the Intel 8080/8085, the TI 9900, the Motorola 6800, the Zilog Z80, and the RCA 1802.

One may be tempted to conclude from the above that  $\mu P/\mu C$  vendors may be able to relegate the development of support systems to companies such as Tektronix or Hewlett-Packard. That conclusion, however, is a fallacy. Good development support by the  $\mu P/\mu C$  vendor will encourage the proliferation of that device family. This *latter* development is what spurs the general development system manufacturers to invest in support of a specific device family. In fact, the order in which a company like Tektronix will develop support systems for  $\mu P/\mu C$  families is closely correlated to their popularity (e.g., support on the Tektronix 8002 for the INTEL 8080 was available in 1977 whereas support for the RCA 1802 became available in October, 1979.)

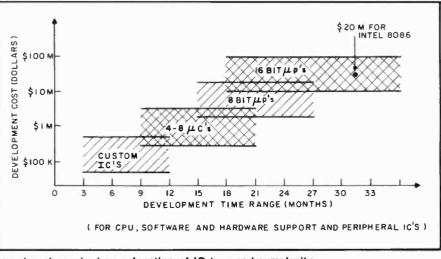

Investments required to support  $\mu P$ and  $\mu C$  lines are a strong function of the device sophistication (shown above). It takes a few hundred thousand dollars to develop a custom IC. A few million are enough to support a  $\mu C$  family. For general purpose  $\mu Ps$ ,

Investment required as a function of IC type and complexity.

widespread, mini or large computers were the hearts of complex controllers. Because of this centralization, controllers were economically practical only for large and complex systems. Furthermore, these early systems had all the attendant disadvantages of centralized control — large cabling costs, decreased reliability, and less flexibility. Smaller systems were designed with relay logic, sequencers, or, perhaps, analog feedback control.

Through the use of low-cost microprocessors, it became possible to decentralize the control function and use intelligent controllers dedicated to specific tasks. Many advantages result from localloop and distributed control, including lower cabling costs, reduced noise pickup, improved overall reliability (if one small system fails, the remainder keep operating), simpler maintenance, and more flexibility.

An example of a  $\mu$ P-based process control system is a prototype wafer silicing machine developed at RCA Laboratories. Keeping the cutting force constant, via  $\mu$ P control, resulted in fewer wafers being damaged.<sup>22</sup> Numerous other examples are presented in reference 18.

Instrumentation and IEEE Standard 488. The impact microprocessors are having on instrumentation is just beginning to be felt.<sup>23-26</sup> From simply adding new features to instruments (digital read outs, averaging, etc.) to auto-calibration, instruments will never be the same again.

A major factor in the increasing sophistication and flexibility of instruments has been the development of the 1EEE Standard 488 Instrumentation Bus pioneered by Hewlett-Packard. The 1EEE 488 Interface Bus provides a versatile effective communication link<sup>27,28</sup> for exchanging digital information in an unambiguous manner. It can accommodate a wide range of devices with similar protocols and is being proposed as an international standard. The number of instruments supporting the bus grows almost daily, and currently exceeds 300.

Other more specialized industrial

this number is much larger. Intel has already spent about \$20 million on the Intel 8086 support. These large investments merely reflect the levels of support needed by customers to effectively use these new parts. Increasingly, the level of support and service available is given high priority in selecting  $a \mu P$  or  $\mu C$  vendor.

## The single board computer

Besides system development aids, the availability of single board computer (SBC) families significantly influences processor selection. For low volume applications, development costs greatly exceed hardware costs and hence the emphasis is on minimizing design time. The availability of a standard rack with power supply, standard CPU and memory boards, and standard I/O boards (A/D, D/A, IEEE 488 bus, etc.) greatly reduces system design. testing, maintenance, and documentation costs. Examples of such families include the Intel SBC 80 line and the newer RCA Microboard family. For manufacturers such as Intel system level sales (including development systems and SBC parts) represent a significant and increasing portion of their revenue base.

applications of microprocessors abound. From energy-subsystem control, to motorspeed control, to numerical-machine control, to robotics, all are increasingly applying  $\mu$ Ps to obtain new levels of performance at economically viable cost levels. References 29-31, along with the *Proceedings* of the IECI '79,<sup>18</sup> contain a wealth of information on these subjects.

#### Commercial applications

Commercial applications of  $\mu$ Ps include their uses in communications (telephony and data), in medical applications and in business applications (from word processing to intelligent supermarket weighing devices).

The most significant emerging trend in communications is the switch from predominantly analog (voice) traffic to a more balanced mix between voice and data. By 1985, communications traffic will be evenly divided between voice and data. This will most certainly spur the development of all-digital terestrial channels. This, in turn, will greatly accelerate the use of distributed intelligence within the network. Intelligent multiplexers, concentrators, PABXs, modems, etc., incorporating the ubiquitous  $\mu P$ , will emerge. More and more, computers will take over the traditional role of operators. As all-digital networks emerge, there will be an increasing need for efficient techniques for transmitting voice in digital form. References 32-36 discuss a variety of  $\mu P$ applications to communications.

Microprocessors are being increasingly used in medical applications. Because of the technical and legal complexities of using new technologies in diagnosing, monitoring or treating humans,  $\mu$ Ps today are being widely used on an experimental basis. Their routine use is at the embryonic stage of development. Reference 37 overviews the entire subject and contains a bibliography of 129 papers.

Word processing and intelligent terminals are emerging as major users of  $\mu$ P technology. For example, approximately 13 million Americans have a hearing or speech defect. This represents a major potential market for a portable telephone terminal. Except for the lowest end "dumb" terminal, most terminals sport some  $\mu$ P control. Many typewriters and other word processing machines employ  $\mu$ P control — not only to add capability but also for internal use to reduce cost.

One interesting example is the intelligent typewriter from the Qyx Division of Exxon Enterprises, Inc., introduced in 1978. It contains three  $\mu$ Ps, a Zilot Z80 for word processing and master control, and a pair of Fairchild F8s for drive motor control of the carriage and the rotary print head. It offers ultra-accurate print head positioning to permit automatic erase backspace. In addition, it incorporates intelligent features such as the ability to store and recall stock phrases, to center a line of type, and to automatically line up decimal points in columns of numbers. All this capability costs under \$1700.

Other commercial applications of  $\mu$ Ps include their use in security systems, environmental control systems, and intelligent weighing devices. In the latter, for example, the store clerk need only type in "price per pound" or "price per quarterpound," and the price will be computed automatically and displayed. A multimicrocomputer energy management system is described in this issue. Other examples include taxi meters, automated gasoline dispensing pumps, and traffic controllers. In the latter,  $\mu$ Ps combined with sensors, can adaptively vary light sequences to maximize traffic throughput, while minimizing waiting time for individual drivers.

#### Consumer applications

Microprocessors and associated LS1 technology are having a major impact on consumer products. From simply adding new features to standard products to making possible entirely new product categories, the consumer computer revolution is just beginning.

Microcomputer controls. Low-cost  $\mu$ Cs are already changing a host of consumer products. From exercise and coffee machines to electric ranges, from sewing machines to microwave ovens, from white goods to home security systems, a whole new generation of intelligent consumer products is emerging. Most home appliances typically need only relatively simple controls. For that reason 4-bit devices, with their low costs, are being shipped by the millions. In fact, it can be said that the 1979-1980 timeframe represents the transition period during which it is becoming cheaper to implement timing functions with a 4-bit  $\mu$ C than with traditional methods. This will result in the across-the-board use of these devices in appliance control rather than only in the higher feature-oriented models.<sup>38</sup> The RCA Programmable TV, described in this issue, is an excellent example of how a  $\mu C$ can add value to a big ticket consumer product. The products discussed above were predominantly examples where electronics have replaced mechanical controls in consumer applications. More interesting, however, are the host of new consumer products spawned by the ongoing revolution in LSI.

*Microcomputer-based games*. Nonvideo microcomputer-based games are just beginning to appear, but already most of the major toy manufacturers are getting heavily involved.<sup>39,40</sup> Judging from the success of action games such as Parker Brothers' "Code Name: Sector," a one player submarine chase game, Milton Bradley's "Battleship," a missile-firing twoplayer naval warfare game, and more cerebral games such as Mattel, Inc.'s "Football" — toys will never be the same again. A more complex example is the Chess Challenger from Fidelity Electronics (Fig. 12). The Texas Instruments' "Speak and Spell," which contains voice synthesis circuitry, is currently being shipped at a rate of about 60 K per month. The latter two products would not have been possible without  $\mu$ P technology.

The video game revolution began in the early 1970s on two fronts. Atari pioneered the development of video arcade games with the 1972 introduction of "Pong." That same year, Magnavox introduced "Odyssey," a consumer ball-and-paddle game based on circuitry patented by Sanders Associates.

More recently, the consumer market has begun to evolve away from dedicated games and towards microprocessor-based programmable games. Examples include the Atari VCS and the recently announced Mattel Intelvision.

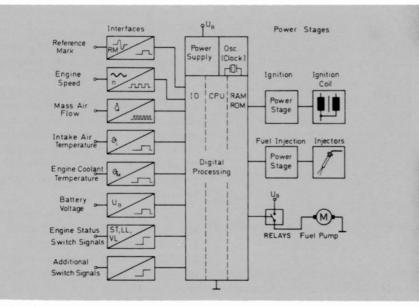

Personalized microprocessors for auto and home. Automotive applications of  $\mu$ Ps will have a major impact on the car of the future. From "under-the-hood" functions such as engine control (spark timing, fuel metering, etc.) and braking to "dashboard" functions (e.g., digital display of MPG), new levels of performance, economy, and information display will be achieved.<sup>41-43</sup>

Another area of major current interest is that of the home computer. There are two divergent paths in this development. One is towards the more specialized "hobby" market (e.g., RCA VIP), and the other is towards the "programmer" market (e.g., Radio Shack TRS-80). The true consumer computer product is yet to be announced although Atari (models 400 and 800) and TI 9914 are steps in the right direction. The consumer computer area is of major interest to both computer- and consumeroriented corporations. Related developments in home data services such as

Fig. 12. Chess challenger from Fidelity Electronics.

Viewdata and Teletext offer intriguing potential. References 45-48 discuss the ongoing revolution in personal computing and television-related data information systems. Reference 15 is an entire issue of the *IEEE Transactions on Consumer Electronics* dedicated to consumer text display systems.

The intelligent (programmable) thermostat is also emerging as a major consumer product. Selling in the \$100-200 range to a market of 70 million U.S. homes, annual volumes of 3-5 million units will be reached in a few years. This is but one of many examples of products that were not economically feasible prior to the invention of the microprocessor.

Other consumer applications of  $\mu$ Ps are under development, e.g., simple home control systems, electronic calendar/ reminders, and wireless security systems, although it is not yet clear which of these developments will evolve into viable volume markets. Reference 44 presents an overview of the impact microprocessors are having on the consumer market.

#### Conclusion

The computer and LSI/VLSI revolutions are moving ahead hand in hand, and are becoming an integral part of our society. The computer industry, born only 32 years ago, has passed \$50 billion/year in sales and is streaking towards the \$100 billion/year mark. IBM received orders for over 32,000 System/38s, small business systems which range in price from \$100,000 to \$600,000 during the first year following product announcement. By 1983, the minicomputer business will grow to an annual volume of over 500,000 units per year. Marketing Development, Concord, Mass., predicts that the market for computers under \$2,000 will grow from \$442 million in 1979 to \$1.5 billion by 1984. All of the above attests to the fact that computer technology has become inextricably entwined both in our lives and in the world economy. Reference 49 documents the pervasiveness of the computer and presents a comprehensive bibliography of its impacts.

Lower costs will impact consumer products. The semiconductor business, which is growing 15-20% annually, will reach \$6 billion in sales by 1979. Explosive developments in digital LSI and VLSI are the fuel of the computer revolution. These developments led to the  $\mu$ P and the beginning of the second computer revolution where distributed intelligence systems will be used by the millions. Each year, the complexity of ICs doubles and the cost per function falls by about 25%. This is resulting in powerful computing elements costing but a few dollars. These costs are coming into the area required to impact volume consumer products — and the existing consumer applications are but the tip of the applications iceberg.

Entire LSI/VLSI systems on one chip. As LSI/VLSI technology continues to evolve,  $\mu$ Ps and  $\mu$ Cs will evolve in two directions. At the low end, ICs will be designed with standard cells representing entire sub-systems (e.g., RAM, ROM, CPU, A/D, D/A, etc.). Entire systems, including analog interfaces, will be put on the same chip to reduce system cost. At the high end, ever more powerful CPUs, peripheral ICs and co-processors along with ever larger and faster memories will vield exponentially increasing computing power with but a handfull of chips. The INTEL 8089 co-processor is one such example. It is built with HMOS II technology which is 30% faster and 10% denser than the HMOS technology used in the 8086 CPU.

Portability plus lower cost. Increasingly, especially in  $\mu$ C-based consumer applications, low power dissipation and product portability will become realistic design goals. The potent mix of liquid crystal displays (LCDs) with CMOS circuitry will yield an array of portable game, computer and other intelligent products. No longer will you have to leave your computer chess game behind when you board the train or hit the beach! Though CMOS technology trails NMOS in density by about two years, the price differential for equivalent parts will decrease to small levels as we move down the learning curve. For this reason, the current exploding usage of 4-bit NMOS  $\mu$ Cs will be duplicated by CMOS devices in the next few years. Furthermore, since the bulk of true volume applications does not need 8-bit CPU throughput, the trend will evolve towards pulling more and more I/O onto the chip resulting in lower system cost.

From microprocessor-based automobile ignition systems to intelligent thermostats, from hand-held computer games to consumer computers, from programmable TVs and VCRs to microwave oven controllers, we are witnessing the beginning of a consumer applications revolution. With over 150  $\mu$ Ps and  $\mu$ Cs to choose from, the real challenge is in the development of new products and uses that fully exploit the potential of LSI and VLSI technology.

#### References

- von Neumann, J., "First Draft of a Report on the EDVAC," University of Pennsylvania, Philadelphia (June, 1964).

- 2. "Here Comes the Second Computer Revolution," *Fortune* (Nov., 1975).

- 3. "The Computer Society," TIME (Feb., 20, 1978).

- Russo, P.M., "Architectural Trade-Offs in Designing Microcomputer Systems," RCA Engineer (Feb./ March, 1977).

- 5. Peatman, J.B., Microcomputer-Based Design, McGraw-Hill, New York (1977).

- Russo, P. M., "Interprocessor Communication for Multi-Microcomputer Systems," *IEEE Computer*, pp. 67-75 (April, 1977).

- 7. Noyce, R.D., "From Relays to MPUs, IEEE Computer, pp. 22-29 (Dec., 1976).

- 8. Moore, G "VLS1: Some Fundamental Challenges," *IEEE Spectrum* (April, 1979).

- 9. Electronics, p. 90 (May 10, 1979).

- "U.S. Markets Forecast 1978," *Electronics*, p. 134 (Jan. 5, 1978).

- 11. "The Microprocessor Industry," Creative Strategies International (May, 1979).

- "U.S. Markets Forecast 1979," *Electronics*, p. 114 (Jan. 4, 1979).

- "Peripheral Chips Shift Microprocessor Systems into High Gear," *Electronics*, pp. 93-106 (Aug. 16, 1979).

- Kelley, J.M., "Cut Hardware, Software Development Costs – Take Advantage of In-Circuit Emulators," *Electronic Design*, pp. 66-71 (Aug. 16, 1979).

- "Consumer Text Display Systems," Special Issue on, *IEEE Transactions on Consumer Electronics* (July, 1979).

- Marcantonio, A.R., "Microprocessor-Based Printed Circuit Board Tester," *Proceedings of IECI* '78, Philadelphia, Pa. (March 20-22, 1978).

- Marcantonio, A.R., "Microcomputer-Controlled Potentiometer Test System," *Proceedings of IECI* '79, Philadelphia, Pa., pp 308-311 (March 19-21, 1979).

- Proceedings of IECI '79, the IEEE Industrial Electronics and Control Instrumentation Society's Annual Conference on Industrial and Control Applications of Microprocessors, Philadelphia, Pa. (March 19-21, 1979).

- Wang, C.C., Wu, C.T., Russo, P.M., Abramovich, A., and Marcantonio, A.R., "Microprocessors in Manufacturing and Control," *RCA Engineer*, special issue on microprocessor technology (Feb./ March, 1977).

- Wittke, J., and Simpson, T.F., "Microcomputers in Picture Tube Manufacturing," RCA Engineer (April/ May, 1978).

- Abramovich, A., "An Interpolating Algorithm for Control Applications on Microprocessors," *Proceedings of IECI* '78, Philadelphia, Pa (March 20-22, 1978).

- Van Le, D., Demers, R., Etzold, K.F., and Firester, A.H., "Wafer Slicing with Microprocessor-Based Controller," *Proceedings of IECI*'79, Philadelphia, Pa. (March 19-21, 1979).

- Randle, W.C., and Keith, N., "Microprocessors in Instrumentation," IEEE Proceedings, special issue on microprocessor applications (Feb., 1978).

- Wu, C.T., "CVM A Microprocessor-Based Intelligent Instrument," *RCA Engineer*, special issue on microprocessor technology (Feb./ March, 1977).

- Oliver, B.M., "The Role of Microelectronics in Instrumentation and Control," *Scientific American* (Sept., 1977).

- 26. "Instruments '79," Special Report, *Electronic Design* (Nov. 22, 1978).

- Loughry, D.C., and Allen, M.S., "IEEE Standard 488 Microprocessor Synergism," *IEEE Proceedings*, special issue on microprocessor applications (Feb., 1978).

- "IEEE Standard Digital Interface for Programmable Instrumentation," *IEEE*, IEEE Std. 488, (1975).

- Sohrabji, N., "Microprocessors Extend Scope of Automated Manufacturing," EDN (March 5, 1978).

- Doi, Y., "Robots Get Smarter and More Versatile," IEEE Spectrum (Sept., 1977).

- Goksel, K. and Parrish, E.A., Jr., "The Role of Microcomputers in Robotics," *Computer Design* (Oct., 1975).

- Lippman, M.D., "Microprocessors in Data Communications," RCA Engineer, special issue on microprocessor technology (Feb./ March, 1977).

- Stanzione, D.C., "Microprocessors in Telecommunications Systems," *IEEE Proceedings*, special issue on microprocessor applications (Feb., 1978).

- Gundlach, R., "Large-Scale Integration is Ready to Answer the Call of Telecommunications," *Electronics* (April, 1977).

- Melvin, D.K., "Microcomputer Applications in Telephony," *IEEE Proceedings*, special issue on microprocessor applications (Feb., 1978).

- Mayo, J.S., "The Role of Microelectronics in Communication" Scientific American (Sept., 1977).

- Klig, V., "Biomedical Applications of Microprocessors," *IEEE Proceedings*, special issue on microprocessor applications (Feb., 1978).

- Walker, G.M., "LSI Controls Gaining in Home Appliances," *Electronics* (April 14, 1977).

- Rosenblatt, A., "Electronic Games No Longer Need TV," *Electronics* (Aug., 18, 1977).

- Mennie, D., "Self-Contained Electronic Games," IEEE Spectrum (Dec., 1977).

- Robbi, A.D., and Tuska, J.W., "A Microcomputer-Controlled Spark Advance System," RCA Engineer, special issue on microprocessor technology (Feb./ March, 1977).

- Lile, W.R., and Tuska, J.W., "Electronic Control of Vehicle Brakes," *RCA Engineer*, special issue on microprocessor technology (Feb./ March, 1977).

- Marley, J., "Evolving Microprocessors Which Better Meet Needs of Automotive Electronics, *IEEE Proceedings* (Feb., 1978).

- Russo, P.M., Wang, C.C., Baltzer, P.K. and Weisbecker, J.A., "Microprocessors in Consumer Products," *IEEE Proceedings* (Feb., 1978).

- Key, A.C., "Microelectronics and the Personal Computer," Scientific American (Sept., 1977).

- Doerr, J., "Low-Cost Microcomputing: The Personal Computer and Single-Board Computer Revolutions," *IEEE Proceedings* (Feb., 1978).

- McKee, K.M., "Data Television A Bright Star on the Color TV Horizon, *RCA Engineer* (April/May, 1979).

- Lipoff, S.J., "Mass Market Potential for Home Terminals," IEEE Chicago Fall Conference on Consumer Electronics (Nov. 6-7, 1978).

- Russo, P.M. and Wang, C.C., "The Pervasive Computer," RCA Engineer (April/May, 1978).

Paul M. Russo is Head of Microsystems Research, RCA Laboratories. During the 1969-70 academic year he was on the faculty at Berkeley, California, where he developed and taught courses in circuit theory and computer-aided-design. He joined RCA Laboratories in 1970 as a member of the technical staff, was appointed Head, TV Microsystems Research in 1977. He has been involved with microprocessors since their inception, and has contributed to the early efforts that led to the RCA 1802 product and to the use of microprocessors in a variety of current and future RCA products and systems. Dr. Russo was a guest co-editor of the February, 1978 issue of the IEEE Proceedings special issue on microprocessor applications, and is the General Chairman, of IECI '80, an annual conference on industrial, control and instrumentation applications of mini and microcomputers to be held in Philadelphia, Pa., March 17-20, 1980.

Contact him at: RCA Laboratories Princton, N.J. Ext. 3234

### A microcomputer glossary

Computer technology is creating a new language that not only incorporates new terms, but often redefines standard English. Words, such as address, bit and stack, assume extended meanings that relate to computer technology, while maintaining their original connotations. A few of the most common microcomputer terms are defined for the layman and, as a refresher, for the engineer.

- access time: the time between a request for information from a storage medium and the time the information is available.

- accumulator: register(s) which contain results of the arithmetic/logic unit operations.

- address: a computer word used for designating a specific location in memory.

- A/D converter: (analog-to-digital converter) an electronic device for changing a DC voltage to a binary-coded value. Computers cannot process a continuous voltage waveform but can process binary value.

- addressing mode: techniques for specifying memory locations for the purpose of storing and/or retrieving information.

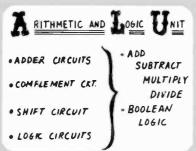

- ALU: (arithmetic/logic unit) the hardware portion of a computer which performs arithmetic functions, such as addition and subtraction and logic functions such as shift, AND and OR.

- architecture: the logical organization of the hardware portion of the CPU.

assembler: a program which translates application programs written in English-like symbolic language (assembly language) into machine language (binary).

- assembly listing: a listing which shows the assembly-language program and the translated machine-language program.

- ASCII: (American standard code for information interchange) a 7-bit code for representing the English alphabet, numbers, and special symbols, such as \$, ↑, and ←.

- **baud:** a data transmission-rate unit. For most applications, a baud is equal to one bit per second.

- **BCD:** (binary coded decimal) a coding scheme for representing the ten decimal numbers.

- **binary number:** a number whose digits are either zero or one. Computers can "read" and "write" only binary numbers.

- bit: a binary digit.

- **bit-slice microprocessor:** an *n*-bit wide processing element usually connected in parallel to implement a microcomputer of *n*-bit word length.

The instruction set is customer defined (by a micro-code).

- **buffer:** a register for holding temporary data.

- **bus:** a set of conductors which carries all necessary computer signals, such as data, address, and control signals.

- byte: a computer word of 8 bits.

- cell: a memory bit.

- **CMOS:** (complementary metal oxide silicon) a very low power logic technology.

- **CPU:** (central processing unit) the arithmetic/logic unit (ALU), registers, and control circuits of a computer. The CPU decodes instructions, issues timing signals, and performs all control functions.

- **cross assembler:** an assembler for use in a computer with an instruction set other than the one which the application program is written for.

- cycle time: the shortest period of time at the end of which a sequence of events repeats itself. Some of the events may be retrieving a word from a memory cell, interpreting the meaning of the word, and executing the instruction.

Reprint RE-25-3-2 Final manuscript received Sept. 27, 1979.

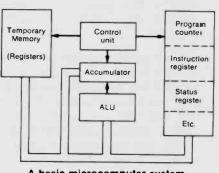

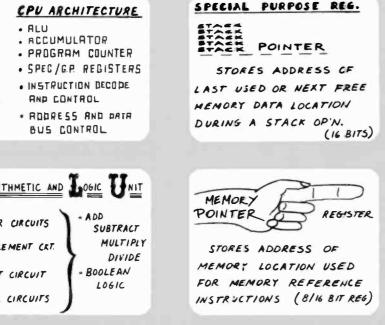

#### The microprocessor is the "brain" for the microcomputer.

A basic microprocessor contains an ALU which performs arithmetic and logic functions, an accumulator which contains the results of the ALU operations, a control unit which generates timing and control signals, a program counter which holds the address of the next instruction to be executed, and other registers. Although a very complex integrated circuit, by itself, the microprocessor is not useful. To realize its potentials, the m croprocessor must be augmented with other necessary support circuits. A microcomputer

A basic microcomputer system

Block diagram of a basic microprocessor

system makes possible the realization of the potentials of a microprocessor.

In the basic microcomputer system, the microprocessor serves as the "brain" of the system, RAM allows information to be stored as well as to be retrieved. ROM/EPROM allows information to be retrieved (read) only, the input device allows information to be entered into the system, and the output device allows information from the computer to be displayed or printed.

Information stored in the ROM/EPFOM is information that requires no alteration by the computer program and generally this information is a program. One advantage of storing information in a ROM/EPROM is that unauthorized people cannot tamper with the program.

Harcware such as A/D converter, D/A converter, drivers, and other circuits may also be needed in a realworld application. These and other hardware are incorporated into the system depending on the specific application at hand. Because of their low costs, microprocessors are ideal for dedicated systems which require "intelligence."

- D/A converter: (digital-to-analog converter) a device which changes a binary signal into a dc voltage level.

- decode: to translate or interpret a computer word into something familiar or useful for performing tasks.

- display: a device which shows a letter or a number or simply emits light; as a miniature light bulb.

- DMA: (direct memory assess) a technique for receiving information from or transferring information to the main memory of a computing system without having the CPU involved.

- drivers: circuits which increase the driving capability of an output circuit.

- encoder: a device for translating a onebit signal into a multibit signal.

editor: a computer program which aids a programmer in his source program creation. An editor helps to perform the following functions: typing in program, making corrections, assigning line numbers to all lines, resequencing of line numbers, locating selected characters, and listing of partial or entire program.

- EPROM: (erasable programmable read only memory) a type of non-volatile random-access memory chip which can be programmed in the field.

- execute cycle: the amount of time for an instruction, that has been fetched, to be executed.

- fetch cycle: the amount of time for an instruction or data to be retrieved from a memory location.

- flag: a bit in a register which is used to keep tract of the state of an input/output device, the state of a register, or the state of the microprocessor. For example, a flag can be used to keep tract of the state of the interrupt feature by setting the flag to 0 for an uninterrupted state and to 1 to denote an interrupted state.

firmware: software that is stored in random-access read-only memory.

handshaking: a predefined procedure for sending information from a terminal (sender) to a computer (receiver) or vice versa that informs the sender that the receiver is ready to receive.

hardware: computer circuits and peripheral devices.

- hexadecimal: a number with a digit value ranging from 0 to 15. The 16 hexadecimal numbers are: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F.

- high-level language: a computer language such as FORTRAN or BASIC which resembles English. One high-level language instruction is translated by a compiler or interpreter program into. several machinelanguage instructions.

The author wishes to acknowledge the assistance of K.R. Wurtzel who read the manuscript and made many valuable contributions.

- IC: (Integrated circuit) very small electronic circuits contained in a single package which perform sophisticated functions.

- interface: as a noun, a physical circuit or subsystem which allows two different types of circuits or systems to be connected together. As a verb, to perform the above-mentioned function.

- index register: a register whose function is to store a number which is used as a pointer to reference a parameter.

- instruction: the machine language words in a computer program that tell the computer what to do.

- I/O device: (input/output device) an input device or an output device. Examples of input devices are keyboards, sensors, and switches. Examples of output devices are displays, audio indicators, and X-Y plotters.

- interrupt: a request to the computer to service an external device. The external device can get the attention and the service of the computer by sending an interrupt signal to the computer. The computer will first finish the execution of the current instruction and then it will service the external device.

- **keyboard:** portion of a terminal that is used to input information to the computer. A terminal has two separate logical entities; one is the keyboard which is used to input information to the computer. The other is the printer or display.

- **LED:** (light emitting diode) an electronic device which sends out light when it is turned on.

- micro-code: the logic-level definition of the instruction set of a bit-slice microcomputer or similar type of machine. Some microprocessors have a micro-coded architecture.

- microcomputer: a computer whose CPU is a microprocessor.

- microprocessor: a micro-electronic chip which contains an ALU, registers, input/output ports, and control and timing circuits. It is capable of performing arithmetic and logical operations.

- mnemonic: the short-hand symbolic names or abbreviations which have

pre-defined meanings, and which represent instructions in assembly language.

multiplexer: a circuit which performs path selection function so that a computer can "talk" to several external devices one at a time.

**object codes:** the binary codes which are obtained as a result of the translation done by an assembler.

octal number: a number with a value ranging from 0 to 7.

- operand: the number which follows an instruction. Example: LDA 5. LDA is a mnemonic which represents an instruction that tells the computer to load the operand into the accumulator. The operand in this case is 5. When this instruction is executed, the number 5 is loaded into the accumulator.

- page: a number of consecutive memory locations, nominally 256. If the memory of a computer has 4096 locations, the computer has 4096 ÷ 256 = 16 pages of memory.

- **parity bit:** a bit which is used to detect a transmission error.

- **pointer:** an address which corresponds to the beginning address of a program or table.

- **PROM:** (programmable read-only memory) a random-access type of memory which can be programmed once only with a PROM programming machine.

- RAM: (random access memory) memory devices which can store and retrieve information in any location in an amount of time which is independent of the memory location selected.

- **ROM:** (read only memory) memory devices which allow only retrieval of information. The information in the ROM is stored during manufacture before the ROM is put in operation. The computer can only read information out of the memory device, therefore, altering the information by the program is not possible.

- register: an electronic device for storing information. In addition, a register may perform other functions such as shifting of bits, selectively clearing some bits, and selectively setting some bits.

- resident assembler: an assembler that runs in a system that executes the object codes which are generated by that assembler.

- sequential memory: memory in which information storage and retrieval is done in a sequential manner. For example, to read the contents of location 50, the computer must search through locations 00 through 49. It cannot jump from location 00 to location 50.

- software: computer programs which are written using instructions, operands, and labels in a logical fashion to accomplish the required task.

1

- source code: the program as it appears in high-level language or in assembly language (as opposed to machine language).

- stack: storage and retrieval of information in a first-in-last-out fashion, i.e., the word that is stored first will be the word which is read out last. The term also refers to a collection of sequential memory cells which store and retrieve information in a first-inlast-out fashion.

- stack pointer: a register whose contents correspond to the address of the top of the stack.

- table-driven: a technique of branching to different subroutines. The starting address of a subroutine is contained in a table and in order to branch to a subroutine, the computer must first go to the appropriate location in the table.

- terminal: an input/output device through which a person can "talk" to a computer.

- tristate: a type of logic circuit whose output can assume three states: a logical zero, a logical one, or a high impedance state. In the high impedance state, the operation of other tri-state devices connected to the same point is uneffected.

- word: a group of bits (the most common are 8, 16, 32, or 64, depending on the computer) which comprises a single unit of information.

- Pat Fasang's biographical sketch and photograph appear with his article on microprocessor education programs on page 71.

## The "berry picking" approach to computer systems development

A successful development strategy for automating the TK-47 television camera.

Abstract: Development of computer systems requires extensive interaction among those involved, unlike picking berries. Berry picking can be accelerated in proportion to added manpower, but computer systems development cannot. It is also difficult to expand the scope of a project while maintaining the original time schedule. If these goals must be accomplished, then innovative strategies are required. The strategy illustrated here is an example of how the bricklaying method worked in solving an automation problem.

The example which will be used to demonstrate one useful technique to ac-

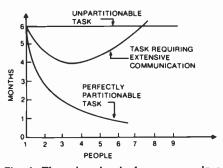

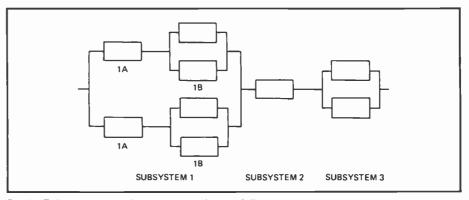

Projects can be divided into several categories. A perfectly partitionable project is one which can be partitioned into tasks requiring little or no communication among the workers. Progress in such projects is essentially proportional to manpower. Examples, given in reference 1, are reaping corn and picking cotton. At the other extreme is the unpartitionable project which takes a certain time no matter how many people work at it. An example of such a project is tuning a piano. It is not likely that two piano tuners could cooperate effectively on one piano and finish in less time. In fact, the opposite is more probable. Most projects fall somewhere between these two extremes. Some number of people can work together effectively, as shown by the minimum in the middle curve in Fig. 1, but there is a level of manpower beyond which further increases do not help. In fact, it is possible that these additional people will serve only to delay the completion of the project, as indicated by the rising portion of the curve.

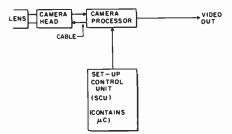

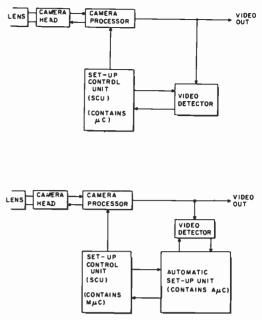

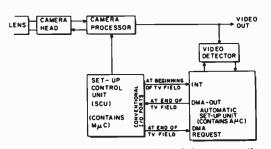

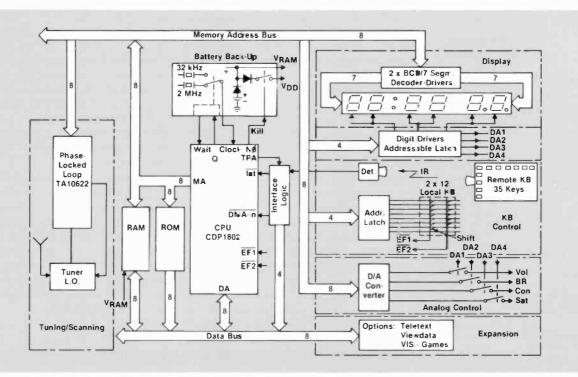

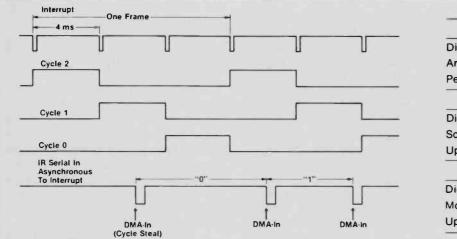

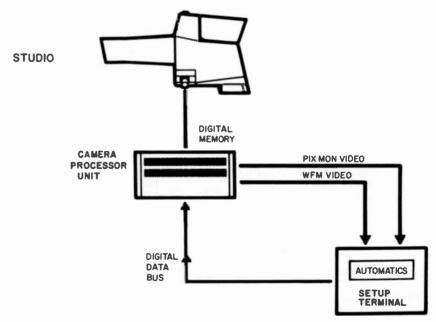

complish this is the history of the development of the RCA TK-47 professional color TV camera. This project was expanded early in its development to include automation of the camera set-up adjustments, while retaining the original schedule. The strategy used to accomplish this expansion was to partition the automation feature into an autonomous processing element (microcomputer) and to interface it to the existing design by means of a simple interface. This approach successfully met the time schedule, demonstrating its feasibility.

tuning, computer systems development is a complex set of interdependent software and hardware tasks requiring manpower to perform the tasks, a plan to coordinate them, and the tools to support their execution. The planning of such an effort can itself be a complex process. It involves the enumeration of the system development tasks, specifying both the time and resources required to accomplish each of the tasks and their appropriate sequencing. This plan often is represented on charts such as a PERT chart that specifies the magnitude and skills of the manpower required and identifies the serial or parallel relationship between the tasks.

#### Nonlinear effects of increased manpower in computer systems

The use of planning tools like a PERT chart is prone to several common mis-

conceptions. First, there is the belief that all the tasks will actually follow the predicted schedule. Maybe this misconception exists because of the tendency to believe what we read. Certainly it is because we believe that all will go well, or that tasks will only take as long as they ought to take.<sup>1</sup> Anyone familiar with Murphy's Law knows this is certainly not true.

A second common misconception is the belief that effort is equivalent to progress. Although cost is usually proportional to effort, progress often is not. This is partially due to the tremendous differences in individual productivity and to the level of success of the organization of the effort. The larger the work force the more critical its orchestration.

Another common misconception is the belief that people and months of effort are interchangeable in achieving progress; e.g., if one person can do a project in six months, then six could do it in one month. This belief is not even approximately true for software development where addition of manpower may not decrease the completion time at all, as indicated by the middle curve in Fig. 1.

There are several reasons for the lack of interchangeability of people and months in a computer systems development project. Perhaps the most important reason is the extensive interaction required among the participants. The amount of communication among them is almost proportional to the square of their number (N). More explicity, the number of interfaces is N(N-1)/2. If each interface requires a time t per month of each of two

Reprint RE-25-3-3 Final manuscript received May 25, 1979.

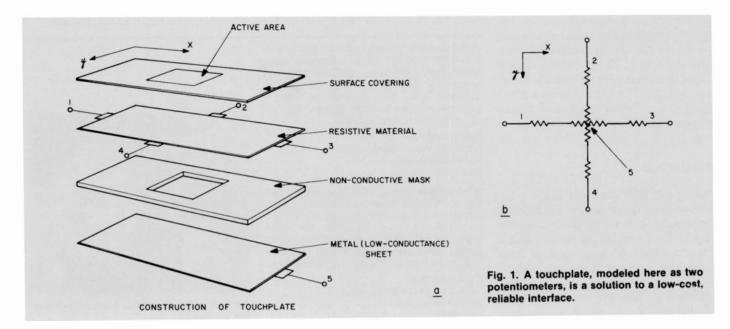

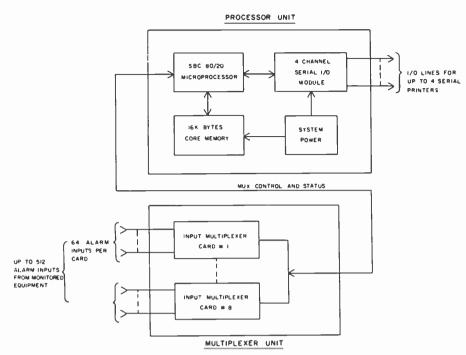

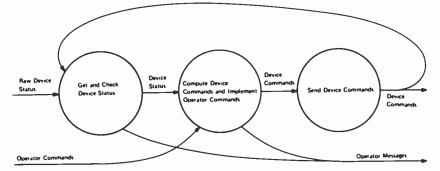

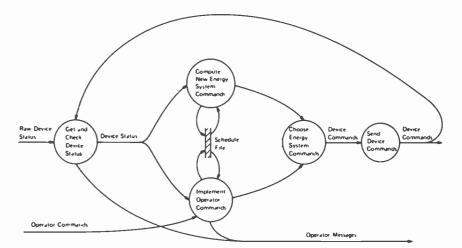

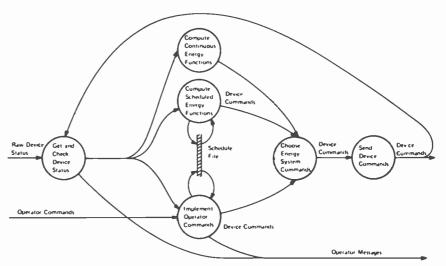

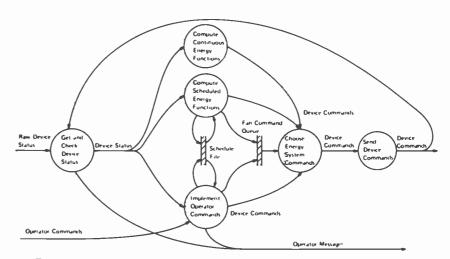

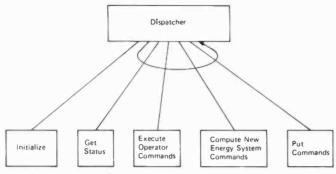

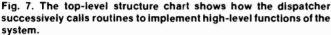

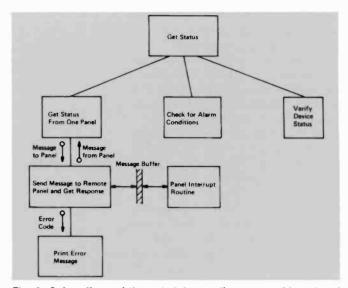

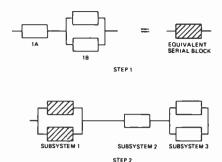

Unlike either berry picking or piano