# Vol. 26 No. 8 Sept./Oct. 1981

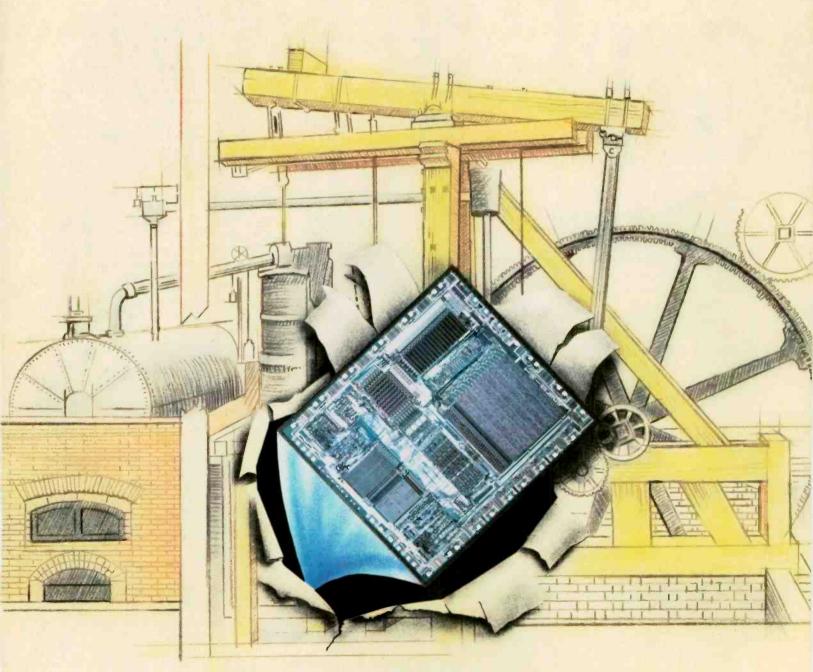

Technology Breakthrough: The Microprocessor Revolution **Cover design** by Louise Carr and Mike Sweeny **Cover illustration** by Michael Katz of NBC News Graphics

Our cover shows the RCA 1804 microprocessor breaking through an old-style rendering of the original Watt steam engine. Because of the power of the engine and the mechanical improvements that accompanied its development, people devised production methods that drastically altered the shape of societies in the 1800s, leading to a cluster of technological breakthroughs and applications known as the Industrial Revolution.

Since that time, many new technologies have helped or affected us in "revolutionary," though somewhat limited, ways. But microelectronics will affect such a broad range of activities that advanced industrial societies will need to organize their production systems around electronics in order to stay competitive.

Already, sales of electronic goods are well over \$100 billion a year. By 1990, the market may reach about \$400 billion a year, and the economy will be global. Microprocessor technology is so sophisticated and laden with potential applications that it could be characterized as the catalyst for a "Second Industrial Revolution." This technological breakthrough may relegate the idea of mechanical control to little more than a torn page in an old book.

American companies, currently accounting for more than 70 percent of the world's production of integrated circuits, will need to develop and maintain their competitive edge. This issue of the *RCA Engineer* samples a variety of microprocessor applications spanning several RCA businesses.

Our cover design is an extension of an idea by Bob Mausler, the *RCA Engineer*'s Technical Publications Administrator at NBC. He is part of the network of talented, dedicated publications people and engineers throughout RCA who invaluably assist in planning and recruiting articles, and producing the issues accurately and on time.

#### - MRS

### **RGA** Engineer

A technical journal published by RCA Research and Engineering Bldg. 204-2 Cherry Hill, NJ 08358 TACNET: 222-4254 (609-338-4254)

|                  | RCA Engineer Staff                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Tom King         | Editor                                                                                                          |

| Mike Sweeny      | Associate Editor                                                                                                |

| Louise Čarr      | Art Editor                                                                                                      |

| Frank Strobl     | Contributing Editor                                                                                             |

| Betty Gutchigian | Composition                                                                                                     |

| Dorothy Berry    | Editorial Secretary                                                                                             |

|                  | Editorial Advisory Board                                                                                        |

| Pete Bingham     | Division Vice-President, Engineering,<br>Consumer Electronics Division                                          |

| Jay Brandinger   | Division Vice-President and General<br>Manager, SelectaVision<br>VideoDisc Operations                           |

| John Christopher | Vice-President, Technical Operations, RCA Americom                                                              |

| Bill Hartzell    | Division Vice-President, Engineering,<br>Picture Tube Division                                                  |

| Hans Jenny       | Manager, Engineering Information                                                                                |

| Arch Luther      | Division Vice-President, Engineering<br>and Product Assurance,<br>Commercial Communications<br>Systems Division |

| Howie Rosenthal  | Staff Vice-President, Engineering                                                                               |

| Ed Troy          | Director, Operations Planning and<br>Support, Solid State Division                                              |

| Bill Underwood   | Director, Engineering<br>Professional Programs                                                                  |

| Joe Volpe        | Division Vice-President, Transmission<br>Systems, Commercial Communications<br>Systems Division                 |

| Bill Webster     | Vice-President, Laboratories                                                                                    |

|                  | Consulting Editors                                                                                              |

| Ed Burke         | Administrator, Marketing<br>Information and Communications,<br>Government Systems Division                      |

| Walt Dennen      | Manager, Naval Systems Department<br>Communications and Information,<br>Missile and Surface Radar               |

| Charlie Foster   | Manager, Systems and Procedures,<br>RCA Laboratories                                                            |

| John Phillips    | Manager, Proposals and Publicity,<br>Automated Systems                                                          |

■To disseminate to RCA engineers technical information of professional value ●To publish in an appropriate manner important technical developments at RCA, and the role of the engineer ●To serve as a medium of interchange of technical information between various groups at RCA ●To create a community of engineering interest within the company by stressing the interrelated nature of all technical contributions ●To help publicize engineering achievements in a manner that will promote the interests and reputation of RCA in the engineering field ●To provide a convenient means by which the RCA engineer may review his professional work before associates and engineering management ●To announce outstanding and unusual achievements of RCA engineers in a manner most likely to enhance their prestige and professional status.

C.J. Santoro

### Microprocessors: A Revolution Put into Practice

As investment and ingenuity have driven the cost of the microprocessor down from the hundreds of dollars of the mid-1970s to the several dollars of today, this technological breakthrough in computing capability has found itself in the hands of greater numbers of creative engineers and designers. As a result, a multitude of new electronic systems now work for us every day from uses in entertainment to protection, from control to display functions.

A broad spectrum of architectures and a wide selection of word lengths have made available a once-only-dreamed-of computing capability at a low cost. Microprocessor systems are even being used to generate and test newer microprocessors. Communications, data processing, transportation, and defense systems' features are enhanced by microprocessors. Few days pass when we fail to come in personal contact with a microprocessor of some kind. The externals of these systems are so simple to use and so easy to understand that we tend to forget the complexity of the subcomponents within them.

And yet, we are less than ten years into "the microprocessor revolution." Chips have integration levels of less than 100,000 transistors and we still have not reached an ultimate cost level. We can be assured that the fertile engineering minds that have led us this far will continue to extend the capabilities of these chips.

A key to expansion is the the application of the "micros" today's and tomorrow's. Most of today's systems use substantially less than the full capabilities of the existing microprocessors, and as we begin to more and more fully use them, we will see an even broader spectrum of electronic services with truly astounding sophistication.

At RCA we have been a leader in this microprocessor revolution and we will continue to establish new directions. We have talent in every aspect of this technology, from chip design to system manufacture. By pooling our creative energies, we can continue to find applications that will transform our world. This issue features a selection of applications for microprocessors. These are but a small sample of the multitude of exciting ideas that clearly show how microprocessors can exert an everincreasing influence on our lives.

*Carm Santoro* Division Vice-President, Integrated Circuits, Solid State Division

| microprocessor<br>applications oyerview  | 4  | Designing and building microcomputer-based systems<br>D.N. Caracappa N.O. Ny G.D. Ripley               |

|------------------------------------------|----|--------------------------------------------------------------------------------------------------------|

| the 1800-series<br>microprocessors       | 17 | New CDP1805 microprocessor upgrades<br>CDP1800-based systems<br>J.P. Paradise                          |

|                                          | 23 | CDP1800-series peripherals are building blocks of a<br>complete processor family<br>J.P. Paradise      |

|                                          | 29 | CLIP-3 is a high-level controller language for<br>1802 microcomputers<br>J.K. Wright, Jr.              |

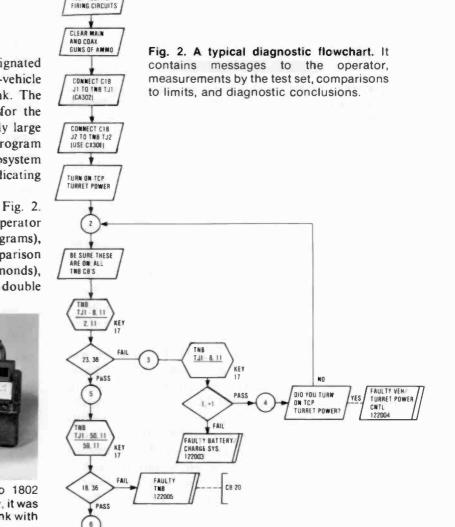

| microprocessor<br>test sets              | 36 | For Army vehicles: Memory design in a<br>microprocessor-based test set<br>D.A. Milley H.L. Resnick     |

|                                          | 41 | Multimicroprocessor-based transistor test equipment<br>W.J. Hepp R.H. Isham                            |

|                                          | 51 | Microboard equipment control<br>W.H. Schilp, Jr.                                                       |

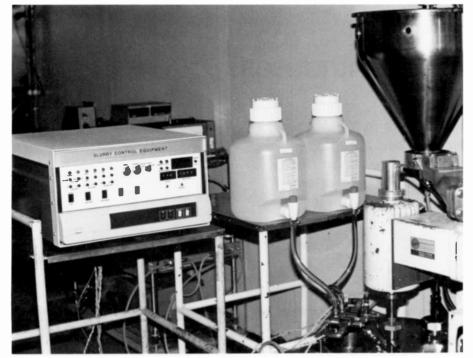

| microprocessor<br>control applications   | 56 | Slurry control equipment uses microprocessor<br>J.W. Woestman                                          |

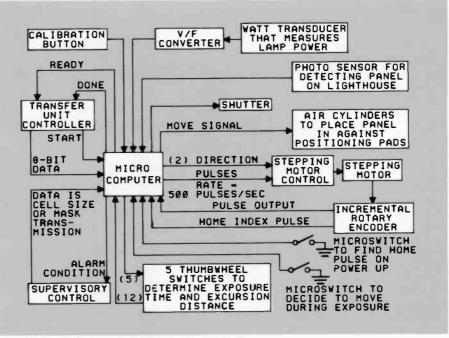

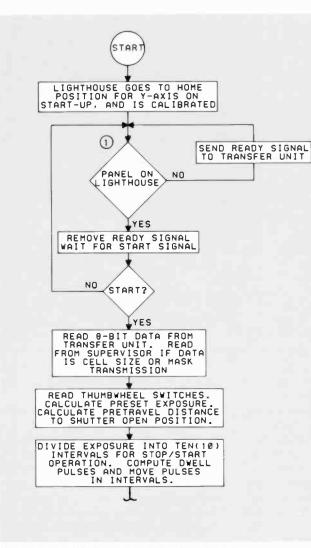

|                                          | 60 | Microprocessor-based lighthouses<br>E.J. Alvero                                                        |

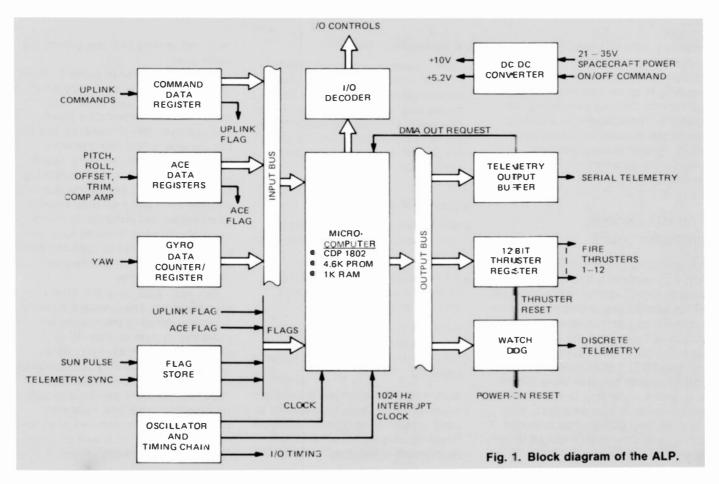

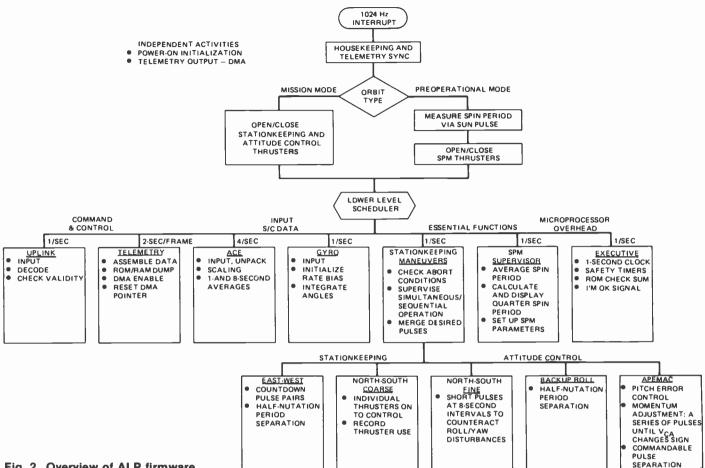

|                                          | 63 | Microcomputers in space: Automatic thruster control<br>for Satcom<br>S. Malyszka                       |

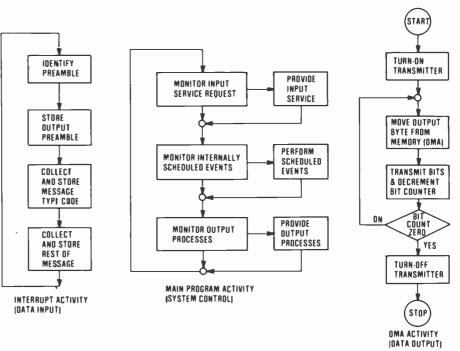

|                                          | 66 | The REMBASS repeater<br>G.D. Chin L.C. Kaye                                                            |

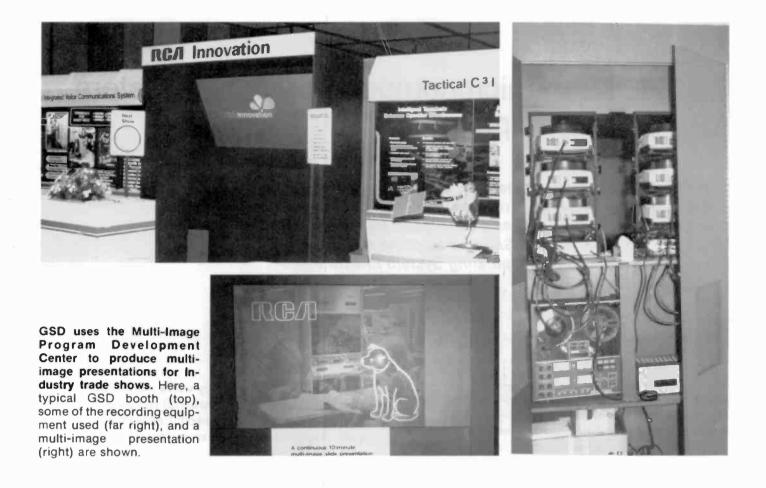

|                                          | 73 | Multi-image programming: Using microprocessors<br>to "move" people<br>F.E. Papke                       |

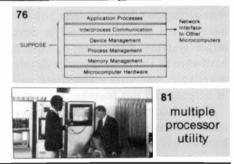

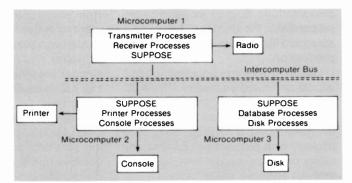

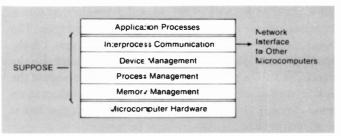

| distributed<br>microprocessor<br>systems | 76 | SUPPOSE: A microcomputer operating system<br>for distributed applications<br>D.E. Britton M.E. Stickel |

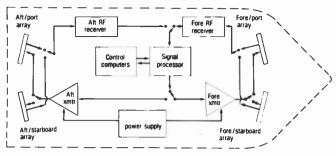

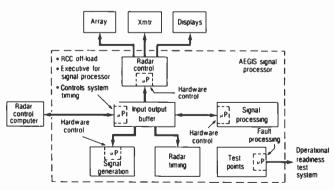

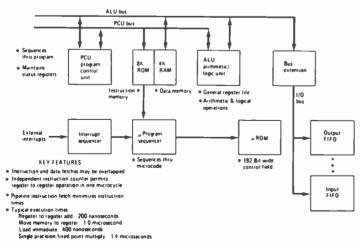

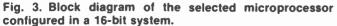

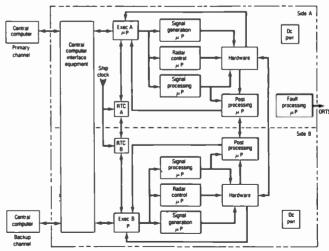

|                                          | 81 | A multiple-processor solution for the advanced<br>AEGIS signal network<br>J.O. Horsley S.L. Clapper    |

|                                          | 87 | Microprocessor network in operation<br>C.L. Ricker R.J. Moran                                          |

| departments                              |    | Patents, 92 Pen and Podium, 93 News and Highlights, 94                                                 |

|                                          |    | Copyright   9 981 RCA Corporation All rights reserved                                                  |

### in this issue...

### Microprocessor applications and development

**Caracappa** Ny Ripley "When developing small microcomputer systems, you often do not need the power of the latest development system with all its options."

■ Paradise "The RCA CDP1800 microprocessor series is a well-tried LSI product line that implements control-oriented microcomputer functions in CMOS."

■ Paradise "These types of components and their functions more closely match equivalent NMOS offerings found in recent catalogs."

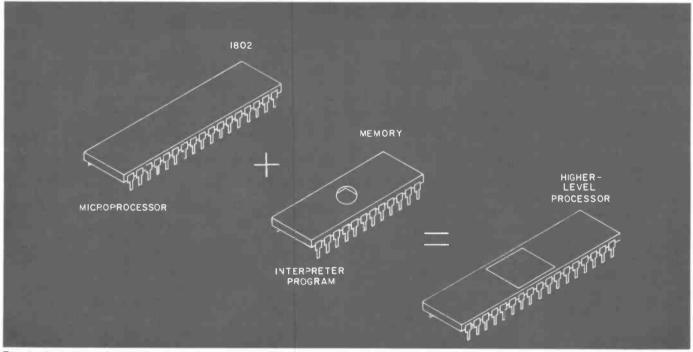

• Wright "If a higher-level program language could be designed easy to learn and not requiring a high-cost development system to use — many new microprocessor applications would open up and others would dramatically drop in cost."

■ Milley Resnick "EPROM technology is attractive in this application because it is cost competitive with ROM."

■ Hepplisham "A system of this type provides a clean break between the logic that performs the test and the logic that decides which test to perform."

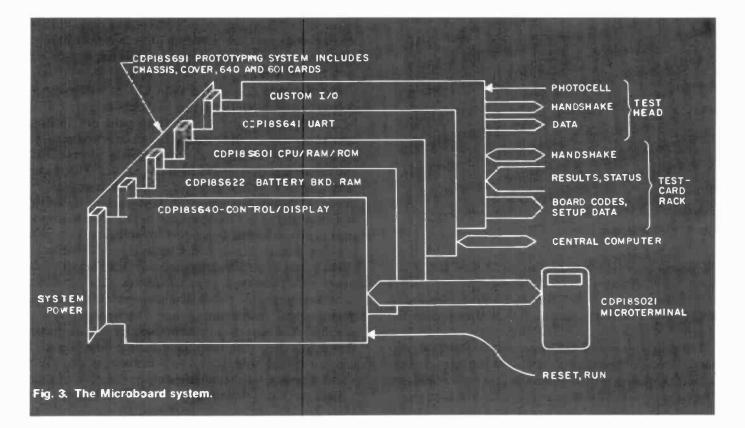

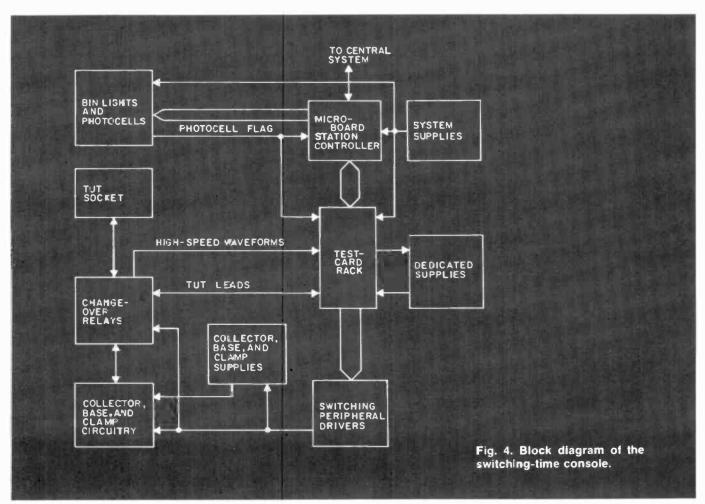

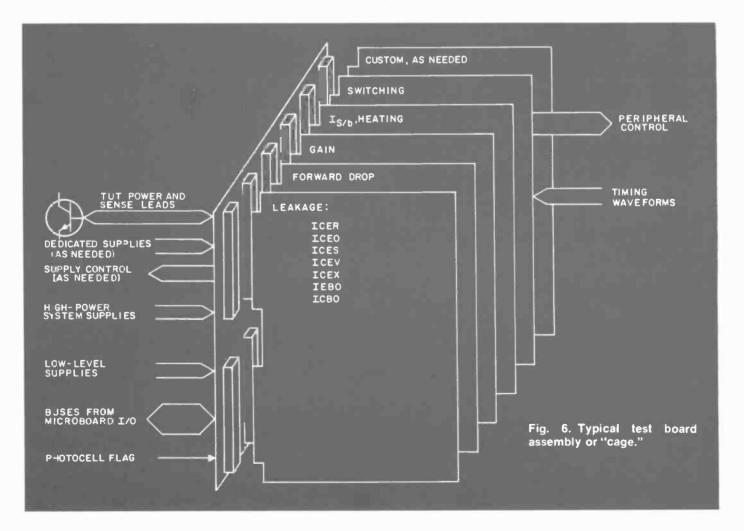

Schilp "The purpose of the project described was to build a piece of equipment to demonstrate the use of RCA Microboards in specialized manufacturing-test equipment."

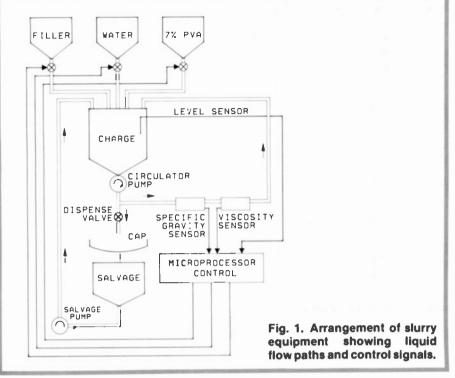

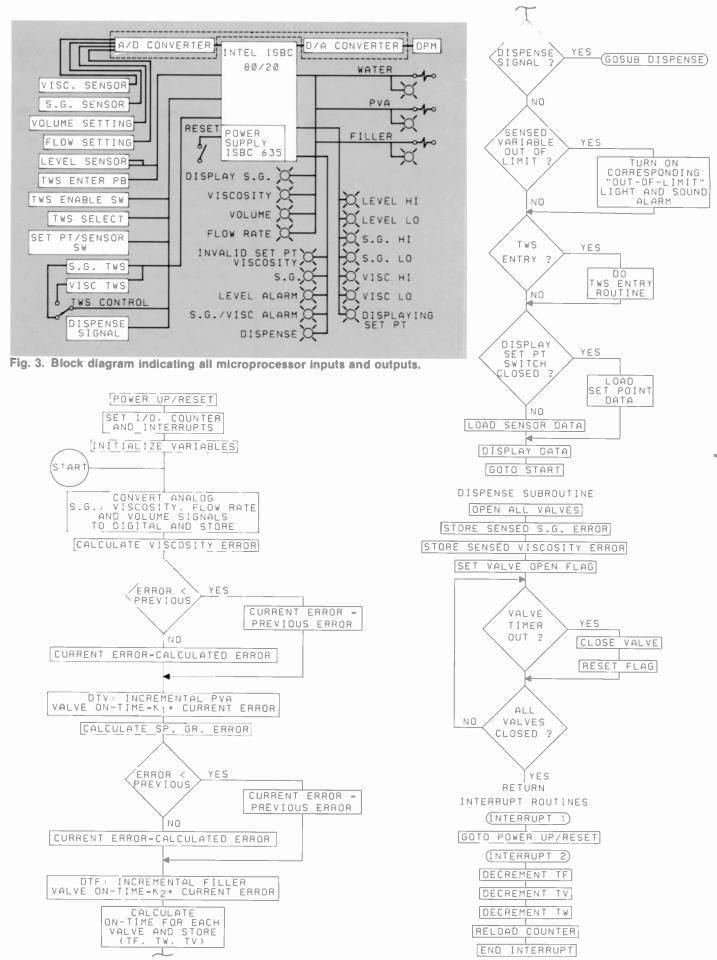

• Woestman "The quantity of each of these three liquids added to the charge vessel at each dispense is determined and controlled by the microprocessor."

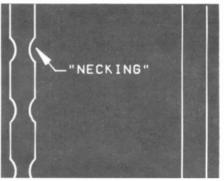

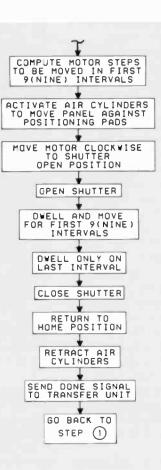

■ Alvero "A new microprocessor-based lighthouse control needed to assure that the panel was exposed equally about the optical axis."

■ Malyszka "Satcom D will be the first RCA communications satellite to employ a microcomputer for fully automatic thruster control."

**Chin** Kaye "As implemented in the REMBASS repeater, the microprocessor provides most, but not all, of the control and processing functions."

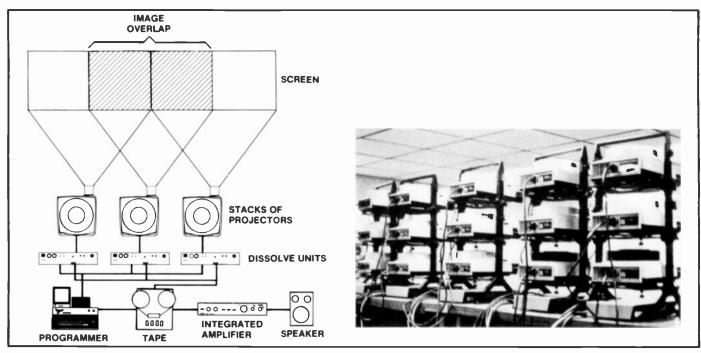

**Papke** "With the subsequent growth of the A/V industry in both size and sophistication, the manufacturers have turned to programmable, non-dedicated microprocessors."

**Britton** Stickel "With SUPPOSE, an application is organized around shared resources."

**Horsley** Clapper "Further upgrading of the signal processor was a prominent part of the plan, specifically in terms of application of VLSI technology and distributed microprocessors."

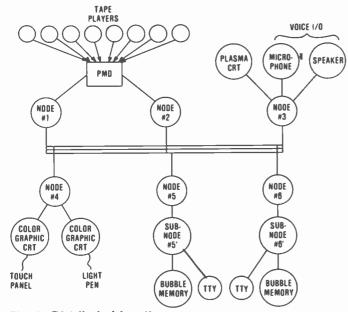

**Ricker** "The microprocessor was seen as the ideal host computer for the architecture — distributed single process nodes — that has been identified."

### in future issues...

SelectaVision® VideoDisc, manufacturing engineering, electro-optics

D.N. Caracappa N.O. Ny G.D. Ripley

### Designing and building microcomputer-based systems

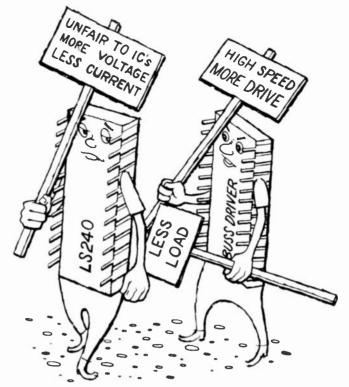

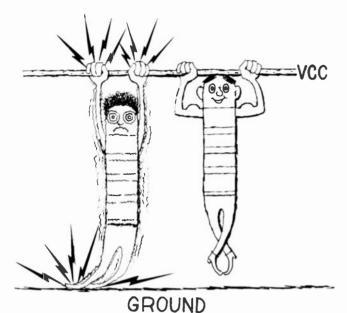

What do you do when your program works... almost all the time? How do you handle it when your constants aren't and your variables don't? What do you do when your pull-ups are down and your bus drivers are on strike?

**Abstract:** This tutorial on microprocessor software development begins with a discussion of overall system design concerns, then addresses the special advantages and disadvantages of working in a minimum-resource environment. Next, the authors cover typical mediumresource tools, MDS and other resident systems, and the development environment when you have these tools. Finally, mini-sized systems and non-resident tools provide a large-resource development environment that the authors examine. The conclusion shows future trends in development hardware and software.

Has this ever happened to you? You've worked all week to finish a phase in the development of a microcomputerbased system. On Monday, after a weekend of celebration, you begin the next step and find that the functions that worked so well on Friday are now totally inoperative. And all you did was turn the system on.

Developing any computer-based system can be frustrating indeed. But if you're considering building a microcomputer-based system, you'll be facing some special hazards not normally found in developing software for larger systems. For example, both the software and the hardware in the system you're developing will initially be unreliable. And your system itself will prove nearly useless in helping you put together the software.

These hazards are not found in developing software for maxi- or even minicomputer-based systems, because the hardware is generally reliable — any bugs are automatically isolated to the software. And the computer itself provides many tools to help develop the software, from language translators to debuggers.

Reprint RE-26-8-1 Final manuscript received July 6, 1981.

Do you have those days when your bus drivers appear to be on strike and your pull-ups don't?

We'll give some tips on how you can deal with these and other problems in developing microcomputer-based systems, answering questions such as:

- □ What are some good analysis and design tools to help me simplify the task?

- □ Suppose I can't afford the best development tools money can buy what then?

- □ How do I decide what to implement in hardware, and what in software?

- □ You've sold me but now how do I obtain these wonderful tools and the expertise needed to use them in building my system?

First we'll review the all-important early stages of microcomputer-based system development: analyzing and designing the system. Then, we'll focus on implementation tools for a range of development environments, from "bare bones" to "large resources." We conclude the guide by looking at trade-offs and other pragmatic considerations. You may want to keep the myriad of tools straight in your mind by referring to the glossary on page 15.

### Analyzing and designing a microcomputer-based system

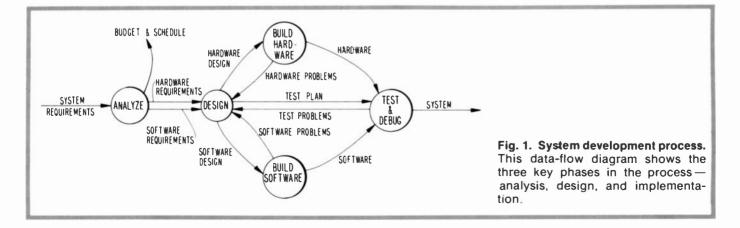

Three key phases make up the development of any system: analysis, design, and implementation. Each stage feeds vital information into the succeeding stage, information that bears directly on the ultimate outcome of the project (Fig. 1).

An analysis of the problem identifies the inputs to the system and the outputs the system should generate in response to these inputs. In addition, analysis should resolve such questions as: when must the system be

All cartoons were drawn by Darwood F. Taylor, RCA Labs, Princeton

finished? at what cost? and who is available to work on the project? The information developed during this stage is then spelled out in such documents as data-flow diagrams (Fig. 1 is an example) and data dictionaries. While we'll only mention a number of these documents in passing, Reference 1 describes them in more detail, with examples and annotated references to "how-to" books on the subject. The key point here is that analysis is sometimes not recognized as a formal step in system development. But by paying more attention at this stage, you'll usually save a bundle of trouble later in the project.

A system designer must determine how to apply available resources to the hardware and software requirements in order to arrive at a solution. The choices that face the designer are not always obvious, and making a particular choice sometimes increases the risk of project failure. As an example, at some point the designer must choose to do a particular function in hardware or software. A decision to use off-the-shelf hardware components will mean higher product cost. On the other hand, the decision to develop (custom) software may increase the risk of slipping the schedule. Clearly, the life of a system designer is far from easy!

#### What aids will help with the design task?

One aid is a system block diagram, which shows the different subfunctions and how they are connected. Another is a diagram showing the interface between the microcomputer and the rest of the system: how the input data arrives at the micro, and what outputs from the micro go where. This interface diagram reflects some of the trade-offs that have been made between hardware and software.

So, now that you've analyzed and designed the system, it's time to start building it, right? Almost, but not quite. It pays to first plan how you'll go about testing the system once it's put together. You need to plan tests for the stepby-step integration of hardware and software, and to develop a final acceptance test that checks that the system satisfies the original requirements. If testing is not planned now, while requirements are still fresh in mind and you're not yet in the heat of the test-debug-modify battle, testing is likely to be inadequate, and reliability of the resulting system will suffer.

On the other hand, with these documents — the test plan and acceptance test — hardware and software development can take place somewhat independently and concurrently, with a fair chance of successful integration of these two portions when the time comes.

#### Is it really that simple?

Unfortunately, as you've probably suspected, issues involved in analysis, design, and implementation are often complex and interrelated. You'll find that you'll return to the design and even the analysis stages as problems and changes arise. For example, maybe the hardware could be much cheaper if a timing spec is loosened. The system designer's job is to determine the ramifications of such a change to ensure that the system will still work.

Before we move on to the implementation stage, note that tools are no substitute for a common-sense approach to designing a system. For example, in the analysis stage, sit down with the ultimate user to determine the real requirements. A visit to the installation site can sometimes

Caracappa, et al.: Designing and building microcomputer-based systems

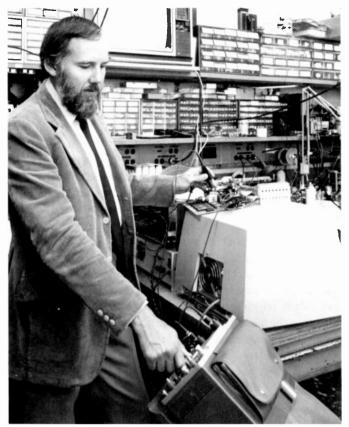

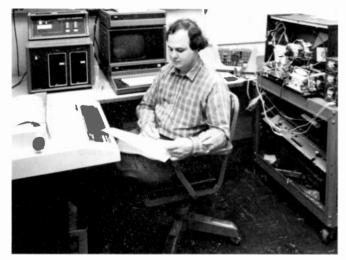

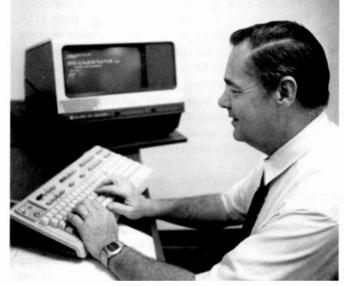

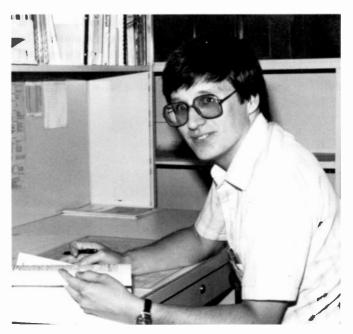

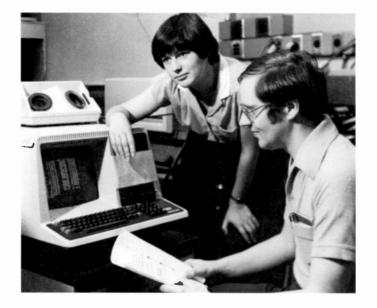

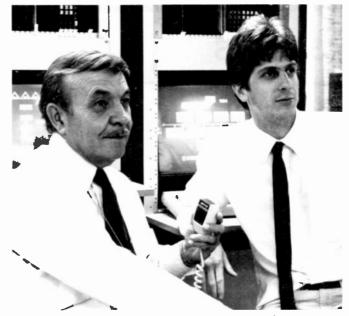

Author Ny debugging a microcomputer-based system in a "bare-bones" environment. Scope is in the foreground.

be helpful. If previous or existing solutions are available, an examination of these can sometimes give further insight into the problem. The best tool available for designing a system is thought. Clear-minded, unbiased, unbridled thought (maybe even blue-sky rambling) can sometimes lead to a unique and clever approach to the design.

Pictures — block diagrams, data-flow diagrams, schematics — will give many insights into the analysis and design process since they usually present a lot of information in small, easily understood packages. In short — think, draw lots of pictures, and communicate with users and other project members.

### Implementing in a "bare-bones" environment

You are faced with implementing a small microprocessorbased control system, or you simply want to build a small system to educate yourself about microprocessors in general. You go to your manager and subtly suggest that you need \$15,000 for a minimal microcomputer development system. Using that special tact which is bestowed only on managers, he counters with something like, "As you know, this year's budget is very tight. Perhaps we can use the company time-sharing system and if things go well, we might be able to get a new oscilloscope next year." And you hadn't even gotten to the part about needing a \$10,000 logic analyzer yet! Does this sound familiar? Do you need to implement a small microprocessor system without the desired resources? Don't despair! This section describes what we've dubbed the "bare-bones" development environment.

First of all, note that we used the word "desired" rather than "necessary" resources. When developing small microcomputer systems, you often do not need the power of the latest development system with all its options. You need not implement your small control programs in Ada. If you are building a small microprocessor-based system for your own education, you can assemble your program by hand. Hand assembly is a means to an end that also gives you valuable insight on the inner workings of an assembler (for example, how it handles the symbol table, or why it needs two passes). You'll be putting the assembled code in an EPROM (or else a large pile of PROMs), so you'll need some means of burning the code into the EPROM. One of the ultraviolet EPROMs, like a 2708 or 2716, will do very nicely. You'll also need access to an EPROM eraser.

On the other hand, if your task is project-related, you will need some additional support, even to implement only a small system. First, you will need access to an assembler. Here almost anything will do, for example, a resident assembler on someone else's system, or a cross-assembler on a larger time-sharing system. The other piece of equipment needed is a decent oscilloscope. Although additional available resources would be convenient, you can implement even medium-complexity microprocessor systems using nothing more than these tools.

### Can I really debug without sophisticated tools?

Yes — by using the system you are building as both your hardware and software debugging tool. Just be sure to avoid building all the hardware and then trying to figure out why it doesn't work. Trying to debug fully-built hardware with a few hundred connections is not a job for a single-trace scope.

Instead, build a small piece at a time. Start with the clock circuitry and convince yourself that it works correctly. Then connect the microprocessor chip and the EPROM chip. This usually requires only that you connect the address and data lines and a few control lines with some small-scale integrated circuitry. "How can I check that this is working since I don't have any input or output?" youask. The idea here is to keep it simple. At this point, your whole system consists of only three or four chips with perhaps 20 or 30 connections. Keep the test software simple, since this is the only time that you have no working system to help debug the rest of it. A short program that branches someplace and then branches back again is all you need. You can then sync the scope on one address line (unique to one of the locations) and look at the address lines to see if you are branching between the two locations.

After you have this minimal configuration working, you now have a valuable tool to help you debug the rest of the system. You now add the RAM chips and the I/O ports to your system. Again, do it a step at a time. Add just the RAM and write a short test program to see if you can read

Attempting more complex systems design in the "barebones" environment may be more than you can handle.

and write to memory before you add the I/O. What is needed in these test programs is pure simplicity to avoid programming errors. In general, you can read from a nonexistent memory location in order to provide the scope with a strobe. Then, follow with a simple loop (for RAM, just write a constant to memory followed by a read from the same location, then repeat). Now, if things don't work, it becomes a relatively simple matter to trigger the scope and look, one at a time, at the data lines, the write line, and so on, to see what is not working.

Keep this process going, one block at a time, until you have a good-sized system working (perhaps 20 to 50 chips with many hundreds of connections). If at any time in the process the hardware does not work with the previous test program, you have only the handful of connections to the additional chip to worry about.

### How about debugging the software?

At this point you are probably one step ahead of us, and have concluded that you should use a similar step-at-a-time approach to the software development. You are absolutely right! To debug the software, one very useful piece of hardware is a box with eight switches tied to an input port and eight LED lights tied to an output port. Now have your suspect program perform a single task and output some intermediate result to the lights, so that you can see the state of affairs. If things are not what you expected, then you have only a few lines of code to look at carefully. If it does work, you simply move your test down past the next task in the program. As with the hardware, the basic theme is to keep things simple (even though your overall software may be quite complicated).

As an example of a system developed in a "bare-bones" environment, one of the authors recently developed a Z80based controller for a future consumer product. The Zilog Z80 processor used 4 kbytes of EPROM and 1 kbyte of RAM (1k = 1024). The system included two programmable I/O chips, a programmable counter/timer, interrupt controller, and a handful of miscellaneous low-level chips. The author used a scope, an assembler on an MDS (see the next section), and an EPROM burner. Excluding the (borrowed) MDS, this development environment cost less than \$5,000.

Many diehards who have been playing with microprocessors from the beginning have built entire systems without an assembler or even a scope. System development in the "bare-bones" environment, although feasible when you have nothing better to work with, has some disadvantages. It can become extremely frustrating. Furthermore, system implementation can require as much as an order of magnitude more time. It's not that one cannot develop systems this way, but rather that it becomes much more productive — and pleasant — with better tools.

### Implementing in a medium-sized environment

As in any other discipline, better tools will let you spend more time fighting the real problem, and less time fighting your equipment. What are these wonderful tools that will free you from a life of drudgery? In this section we'll mention some of the key development aids.

#### Can existing tools in the Corporation help?

Yes. For example, simulation programs for electronic circuit design are available on RCA's IBM 370 system in Cherry Hill. Two of these programs are RCAP (RCA Circuit Analysis Program), for use in analyzing analog circuits, and MIMIC, a circuit analysis program for analyzing digital circuits. These tools are accessible by merely opening an account with the people in Cherry Hill.

Other valuable sources of development assistance are all those manufacturers out there who are so eager for you to use their products. A well-placed call to the manufacturer of an IC or piece of equipment you plan to use may bring you an applications note, or if you are lucky, access to a good applications engineer.

Several techniques exist for implementing a piece of the hardware system. You can put together an easily modifiable breadboard, with quick-connect tools or even services which can wire-wrap as many boards as you want, given a wire-connect list. Alternatively, a printed circuit board approach can be useful when the system must be replicated many times. There are also computers that aid in laying out PC boards (such as an Applicon system).

To test the hardware once it's built, you'll generally have to rely on your wits. However, a few tools can make the job of testing the digital/microprocessor components a lot easier. These include: a good multitrace, wide-bandwidth oscilloscope; a logic analyzer; and a function generator. As you know, an oscilloscope records one or more analog signals for some period after it receives a trigger signal and displays that information as a graph on a CRT. A logic analyzer is basically an oscilloscope for digital signals. It records digital words (usually 8 to 32 bits) and saves some number of them when it receives a trigger word, and displays them in either numeric or graphical form on a CRT. A function generator might be useful for stimulating the inputs to the system with a known waveform.

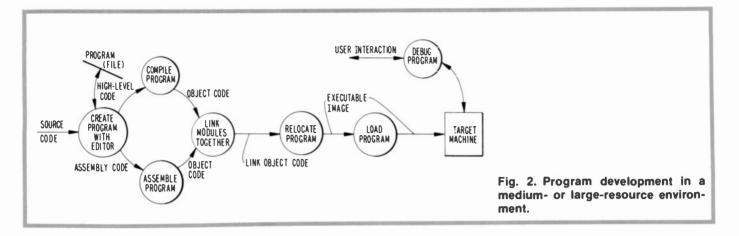

So much for the hardware. But what about the software? In fact, it is software tools that will make the biggest difference to your efficiency. We noted in the "bare-bones" environment the value of an assembler over handassembling your program. This is but one of many useful software tools. Figure 2 shows the different steps in developing software in a medium-sized (and largeresource) environment. The details follow.

### How can a higher-level programming language help?

Certainly the most important tool in software development is a high-level language such as BASIC, FORTRAN, or Pascal. Programs written in these languages are generally much shorter and easier to understand, debug, and modify than those written in assembly language. A compiler is then used to translate these programs into machine code, corresponding to the assembler used in translating assembler programs. For those programs complex enough to be broken into separate modules, their compiled and assembled code modules must then be linked together into a single module, using a linker, and that module must be relocated to the memory location at which it will reside during execution.

Stand-alone Microprocessor Development Systems may not have adequate resources to accommodate the more complex projects.

Finally a program, whether originating as one module or a collection of modules, is loaded into memory using a "loader" (often a linker also does the job of the relocater and loader, combining the three processes into one program).

### Where do these software tools live?

Compilers, assemblers, linkers, relocators, and loaders are all computer programs, and must have a computer on which to run. A computer with these facilities, which can support a single engineer, is called a microcomputer development system, or MDS. If program preparation has all been done on such a separate (host) computer, the process of placing the program into the (target) computer's memory is called downloading. On occasion you'll want to send data from the target to the host, using what is called an uploader.

An MDS also provides an editor for entering your program into a file prior to compilation or assembly. Since much of your time will be spent interacting with an editor, its ease of use and reliability are quite important. If it is hard to use, making even the simplest change can be very frustrating. For example, if it loses track of a file after several hours of creating and correcting it, you may feel like physically abusing what otherwise might have been a fairly good MDS!

### OK — but who can help me with the really hard part of finding my program's bugs?

Once a program has been loaded into memory, it is ready to be executed. This is the supreme test and the moment you've been waiting for! Unfortunately, for some strange reason only the simplest of programs run correctly the first time. Most require many, many iterations of testing, locating and fixing bugs, recompiling, and relinking. In fact, the program test phase can easily be the most timeconsuming and frustrating phase of all. If there were ever a need for assistance, now's the time!

Enter the debugger, which will help monitor and control execution of the program in memory. A debugger initiates execution of the program, allows you to look at and modify the contents of those memory locations you are interested

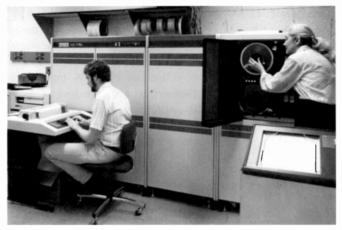

Author Caracappa debugging a system (to his rear and left) in a medium-sized environment. Intel MDS is in the background, on the left.

in, and stops at specified locations to enable you to check values of variables and so on. As with the editor, you'll be spending a good deal of your time interacting with your debugger.

Another important form of assistance at the execution stage is the In-Circuit Emulator (ICE), which physically stands between an MDS and the target system. An ICE module comes with a cable that plugs into the socket in your micro system where the microprocessor normally goes. It takes over the functions of, or emulates, the microprocessor. The software portion of the ICE system resides in the MDS and it allows you to debug as described in the preceding paragraph. The big edge an ICE system gives you over a software debugger is that it also provides a debugger for the hardware. You can check on interrupt operations, clock operation, address lines, and so on, using an ICE.

#### What's a typical medium-sized system cost?

An example of a system recently developed as a joint project by the Labs and the Manufacturing Technology Center at Indianapolis using medium development resources is a system to aid in color television instrument alignment. The system consisted of an Intel 8086 16-bit processor, two wire-wrapped boards of custom analog and

In-circuit emulation hardware can be a valuable tool to help you eliminate the bugs from your design.

digital logic, 12 kbytes of EPROM and I kbyte of RAM. The software was developed on an Intel MDS 230, using the usual steps of editing, compiling, linking, relocating, and loading. The programming language used, Intel's PLM, is roughly a small subset of PL/I. A multitrace oscilloscope and Intel ICE were the hardware development aids. This development environment cost approximately \$30,000, although medium-sized systems range from as low as \$15,000 to \$50,000 or more.

### What is the common thread running through these medium-sized development tools?

You've guessed it — in building these tools, we've harnessed some of the power of the computer to help us to solve our problem. For assistance in hardware tasks, we have the 370 (or other large computer) to assist with the design, and the (microprocessor-based) logic analyzers and function generators to assist with testing and debugging. For software assistance, the computer has done most of the dirty work for us, from editing our source code to helping debug our object code. In short, many of the things that could be done better by a computer were, indeed, done by a computer.

### You've mentioned the good news in using a mediumsized system — how about the bad?

There are still plenty of problems left in developing our microcomputer-based system. The problems lie almost exclusively in the software area, however. Sometimes, for example, you will realize that a version of a program that you've since modified, was correct in the first place. Unless there is a backed-up copy of the original program, your only alternative is to recreate this version manually, and go through the debugging process again. Other times, you'll want to know the value stored in a variable you've called X. The debugger in the medium-sized environment may only know numeric storage addresses. So, you have to read through the address table produced by the relocator to find X's address. This activity does not contribute directly to the development of your system and is error prone.

These are but two examples of weaknesses in this collection of tools. Nevertheless, these tools can dramatically increase your productivity, and enjoyment, in developing a microcomputer-based system.

### Implementing in a large resource environment

We've seen that a few well-chosen tools, both hardware and software, can do a great deal for us. In this section, we'll see that, when necessary, we can carry this approach even further; the result in doing so is what we've called a "large resource environment (LRE)."

#### What's different about a Large Resource Environment?

Well, first of all, it has as its core a relatively large computer, such as a Digital Equipment Corporation VAX

VAX 11/780 large-resource environment from Digital Equipment Corporation similar to the DEC20 system mentioned in the article. The system currently supports up to 32 simultaneous users. A high-speed printer/plotter is in the foreground.

11/780 or even the much larger IBM 370 computer system at Cherry Hill, in place of the smaller MDS of the mediumsized environment. It may be dedicated to a particular project or shared with many other users, such as the Cherry Hill machine. An LRE should provide a very convenient cross-development environment with which to prepare and sometimes execute programs that will eventually run on the target microprocessor. Hence, as with the medium-sized environment, we are "cross-developing" programs partially developing them on one machine, to ultimately run on another.

You might be wondering why in the world we would want to do such a thing? Why fool around developing our microprocessor program on an entirely different machine? After all, now we'll have to learn how to use two machines — not only the micro, but the cross-development machine as well! Well, you have a point, but sometimes depending on the nature of the project — a crossdevelopment environment can provide enough benefits to make the effort of using it well worthwhile. Let's first look at the tools found in a typical LRE, and then get back to the pros and cons of this approach.

Now, as we've said, an LRE might be thought of as a larger, more powerful version of the MDS used in the medium-sized environment. There are, after all, the usual editors, compilers, and so on, found on an MDS. But there are important differences — some good, a few not so good. The good ones include not only a difference of scale, but also the amount of software tools available and the number of simultaneous users.

An LRE computer is likely to be at least several times faster than most MDSs, typically executing up to a million or more instructions a second. This means that compilations and linkings will be done more quickly, assuming the computer is not heavily loaded by other users. There are generally very large disks (each holding hundreds of millions of characters), tape drives, fast printers, and other convenient peripherals.

### Do I get more than speed for my money in an LRE?

A good LRE will also have a wealth of software tools, depending on how long the particular model LRE computer has been in existence and how many other installations use it for applications similar to yours. In fact, so important is the software to the success of an LRE, that the rule of thumb in selecting an LRE should be: choose the richest and most appropriate software environment you can find, then buy the hardware that it runs on.

An LRE is likely to include a greater depth of tools containing, for example, several editors and compilers for several languages. Some of these tools will be more reliable than others, some will have better features than others. Having the freedom to choose between tools with differing features leads to a better fit for a particular project, and may lead to higher individual productivity.

There will also likely be a wider range of tools in an LRE. For example, in addition to source code editors, there may be special document editors (for producing and quickly updating specs, memos, and so on) and graphics editors (for creating graphics scenes to be integrated into and manipulated by graphics programs). There may be automatic backing up and archiving of files. There will likely be cross-compilers and cross-assemblers for a variety of target microcomputers, extending the usefulness of the development environment — and the expertise built up in using it — to other projects. Debuggers may be more powerful, allowing you to work in terms of your high-level language program (for example, variable X) instead of in terms of the raw machine (X's object code address).

Unlike its smaller cousin, the MDS, an LRE is a multiuser facility. The computer is time-shared by users, each getting but a fraction of the computer's attention on a millisecond-by-millisecond basis. This means improved communications between several project members developing software; they may "talk" to one another while remaining at their respective terminals by sending messages. The LRE's electronic mail system may also be used for sending notes, to be read and responded to at the receiver's convenience. And last, but far from least, data and programs in a time-sharing system are naturally sharable among its users. Sharing is but a single command away - no computer-to-computer link, no magnetic tape transfer of files from one machine to the other, and no changing of dialects from one machine's high-level language to the other's - simply copy the program with one command and run it.

### What's the role of the MDS in an LRE?

The MDS is used in an LRE as a kind of intermediary between the large computer and the micro, rather than as a program development facility as in the medium environment. Downloading often goes through the MDS, on whose disk downloaded programs can be stored before they are passed on into the micro. This allows for generally quicker reloading of the micro's memory after aborts, and is especially useful for those pieces of the software that haven't changed lately.

An essential role of the MDS in an LRE is in debugging using its ICE capability. As we mention later, an LRE can simulate execution only so far, and then an ICE capability is needed.

### What does a particular LRE look like?

A recent joint project at the Princeton Labs and the Consumer Electronics Division in Indianapolis, Indiana, employed a Digital Equipment Corporation DEC20-based LRE. This computer supported a dozen or so simultaneous users producing software for an Intel 8086 microcomputer. The software used for this project included two editors, two graphics editors, two cross-assemblers, three cross-compilers, two linker/relocator/loaders, an 8086 simulator/debugger, and a test monitor to assist in systematically applying the tests in the test plan. It also included a source-code-version control program to ensure that changes to a module were recognized by all users of the changed module; a Pascal debugger; a Pascal programperformance monitor to identify program bottlenecks; downloaders to Intel MDSs and to the 8086 directly; document formatters; and a mail system. In addition to the DEC20 itself, there were a graphics terminal, two MDSs, single-board 8086s (the targets), logic analyzers, EPROM burners, and oscilloscopes.

### What are the disadvantages of an LRE?

You've probably been wondering about the price tag of such a grandiose system. An LRE can be quite expensive. For example, the above DEC20-based LRE ran well over \$300,000 for hardware and software, over \$20,000 per year for equipment maintenance, and the equivalent of one fulltime person to maintain the system. And these figures don't include the MDSs and associated equipment. In addition, over three person-years were spent tailoring the software tool environment to the project. Of course, the process of customizing an LRE to your needs is an on-going one, and cost must be spread over more than one project. On the other hand, if you plan to use your LRE on another project, you may well have to purchase, modify, and/or build from scratch additional tools needed specifically for the particular micro. This effort can be extensive, and should be considered from the beginning.

A time-shared LRE can result in productivity losses if it becomes heavily loaded — and most of them seem to get that way eventually. Not only does it take longer for the machine to perform each development step (for example, compiling your program) on a loaded system, but the unpredictability of the time that a step will take makes it hard for you to plan your other activities. At least on a single-user MDS, if you've found that a particular compilation will take, say, half an hour, other things can be accomplished during this period.

We've mentioned the ability to simulate execution of a micro on an LRE. Just how accurate is such a simulation?

Sometimes not very. For one thing, timing is different. Socalled "real-time" programs depend on certain things happening in a certain amount of time — for example, an interrupt should be processed in a known time interval. If these assumptions are violated, the program will likely fail. Furthermore, most simulators don't really simulate the entire microprocessor environment; in particular they don't simulate most peripherals. So when it comes time to exercise these peripherals, the simulator is no longer useful and you must execute on the MDS using ICE or on the target system itself.

Finally, an LRE increases the number of things to be learned (all those handy tools come with manuals), and often (depending on how effective your simulator is) it greatly increases the number of steps you must go through to test and debug a program. If any steps are particularly slow, such as downloading (which is fine at 960 bytes per second but terrible for large programs at 30 bytes per second), the debug cycle can become very time-consuming. Furthermore, additional steps mean more things to go wrong: bugs in the software, hardware problems in the central computer system, terminals, communications equipment, or download link.

Nevertheless, an LRE is particularly useful in large projects. It also offers the longevity that is often missing in dedicated development systems. Even if the target microprocessor changes from project to project, many tools will remain the same: editors, mail system, document system, and utilities.

### Dealing with other system development problems

We've seen three levels of development environments, and some of the pros and cons of tools at each level. But there are other issues and considerations besides tools in developing microcomputer systems.

### When can I trust my development tools?

This is a very hard question to answer, but we can offer some guidelines. First, like almost everything else in life,

Large-system response times can become unbearably slow when the systems are heavily loaded.

When you can't find the cause of your problem, let friends look at your program because they can often locate errors which escape you.

you generally get what you pay for. It is often, but not always, true that a \$3,000 software debugger will contain more of the desired features and be more reliable than a \$300 debugger. At least the higher-priced software usually comes with more maintenance support (that is, assurance of bug fixes).

Secondly, the newer the software package, the higher the risk. Generally, if the version-update number is newer (version 3.37 instead of version 3.26), chances are that you will receive a more bug-free version because this denotes that specific bugs have been found and corrected. On the other hand, if the version number itself has increased (version 4.03 instead of version 3.37), you run the risk of getting an increased number of bugs because a new version number corresponds to major changes (usually new features). Unfortunately, companies who turn out new processor chips are under pressure to deliver development software and provide in-circuit emulation and debugging tools quickly. This leads to hardware and software that has not had the time to be adequately tested.

Even though most tool reliability problems are due to software failures, occasionally hardware tools will fail. We have purchased development tools from a manufacturer (who shall remain nameless!) where we spent several days trying to find out what was wrong with our hardware, only to discover that the hardware emulation and debugging aids were in worse shape than the system we were trying to debug! It is often better to use an existing tool, which someone, who knows where the bugs are, has used before, than to experiment with a new tool.

### How do I separate hardware from software problems?

The answer to that question is a rather easy one: always suspect the software. Provided that the hardware was checked by simple-minded test routines, future problems are almost always caused by software errors. This is a concept which can be difficult to put into practice because many of us have a rather large ego to contend with. The typical process goes something like this. We make a change to the software and notice the program no longer works. We note the symptoms and start looking at the appropriate piece of code and sure enough, we find some obvious errors and fix them. We try it again and it sort of works but not all the time, and we can't quite isolate the precise conditions that cause it to fail. At this point, we have carefully looked at every line of code and convinced ourselves that it cannot possibly be in error! And now we make the big mistake and conclude that the only explanation must be that we have a hardware bug, which we now proceed to look for instead of looking at the software again.

What went wrong? We sometimes don't like to suspect ourselves. Often the hardware is designed by us and constructed by someone else. Even when we build it ourselves, we like to put the blame on someone or something physical. After all, when we wrote the program code, we faithfully wrote the instructions which performed just the function we had in mind. Or did we? Well, we did make that obvious error that we found and corrected but now it must be correct... Actually, instead of suspecting the hardware at this point, it's often better to have someone else look at your program. But don't describe each piece of your program and how it works. If you do, that person will go down the same rosy path that you did and reach the same conclusion that you did - that there is nothing wrong with the program. Often, someone unfamiliar with your program will quickly find an error in a piece of code that you must have looked at hundreds of times. The problem is that when you wrote it, you were sure it was correct, and each time thereafter you only further convinced yourself of its correctness. We'll admit that this procedure can be somewhat humiliating, but it's often very worthwhile indeed.

Of course, if you (and your friends) have spent days or weeks looking for a software problem to no avail, then you might begin to suspect the hardware. At this point, you'll drop back to simple hardware test routines to try to isolate the problem.

### Which processor should I use?

When it comes to choosing a processor or deciding whether or not to perform a given task in software, many factors should be considered. How much computing power do you really need? How much effort will be required to perform this task in software? How much will the finished system cost?

First, let's start with some realities. It always requires more effort (often ten or more times more effort) to implement a given task in software instead of using a specialty hardware chip. In contrast to the hardware situation, there are presently very few off-the-shelf software building blocks. Software is generally written to exactly fit a situation, and hence is not reusable in a different context.

The hardware/software choice is often dictated by the ultimate use of the system, and other times by the tools and development facilities available. Or, the choice may be based on the experience that the people involved have with a particular processor.

### Shouldn't the ultimate usage guide my choices?

Absolutely. If your system is going to be part of a device that will be sold by the tens of thousands, then you will choose the processor with the minimum required capabilities at the lowest possible cost: Almost every function possible will be performed in software to reduce hardware replication costs. For this kind of a situation, the cost of development tools (although they may be very expensive) is insignificant. It is also worthwhile to spend a month to develop a routine in software that eliminates a \$2.00 hardware chip. In short, it is almost worth any effort (and a lot of effort will be required since it will be just barely possible to perform the functions with the processor that is chosen) in order to reduce the system replication cost by a few pennies.

On the other hand, suppose you are developing a system that will be one of a kind, or perhaps replicated a few times. Then you should not be afraid to include a liberal sprinkling of sophisticated hardware support chips in your design, as it will reduce the development time and effort required. And if the processor you choose is more expensive and has capabilities that you will not fully use, so what? It is also perfectly reasonable to use a processor that you are familiar with even if it may not be the best choice, particularly if you want something working in a relatively short period of time.

### How can I obtain the necessary equipment and expertise?

Obtaining microprocessor development equipment can be an expensive proposition (remember your manager's reaction!). Also, if you don't have some system design experience it is very difficult to know what you should buy. First, you must determine your needs. If you will have to implement a wide variety of systems, then one of the general-purpose systems that support several of the popular processors might be appropriate (such as one from Tektronix or General Radio). On the other hand, if your needs can be met by one family of processors from a single vendor, then you will be better off with a development system from that vendor. The reason for this is that you will be able to get support for the latest product the vendor has to offer almost as soon as it is available. Also, you can usually get help with problems from vendors who are anxious to sell you their processors.

We should point out that a general-purpose development system, although more flexible and adaptable to new processors, does have some drawbacks. Availability in these systems of in-circuit debugging hardware and

### Where do you go from here?

A wide range of available tools can greatly improve your productivity in developing a micro-based system. What does this mean for you? Well, productivity is a complex issue, depending on sucn things as the "friendliness" of the system, the ease of learning the operating system and applications programs, the languages and other software available for the system, and the expandability for future *epplications*.

Common sense tells us that we don't need the power of a time-sharing system to develop a simple controller and likewise wa cannot nave twenty people working on a complicateo project in the "bare-bones" environment. In most cases, however, we are no\* faced with such an cbvious choice. Jsually more than one person and less than twenty must be considered. Also, the project is often neither simple nor extremely complicated.

What choice should one make? Part of the ar swer lies in understanding the minimum resources needed to implement your particular application. There is a problem if you are getting into microprocesso: systems for the first time with little awareness of the options available to you. You could listen to the saiesmen for the various micro, mini and time-sharing development systems, but when you listen to a salesman you may get the impression that with a few expensive options the system could double as a boat or an airplane for weekend recreational purposes.

If you are inexperienced, try to get some advice on what your minimum resource requirements are. After you have a good feel for the features you need, talk to development system vendors and ask a lot of tough questions such as: how does your option really fit my needs? If the option is new, how soon will it be installed in my plant, and what happens if it doesn't work? If you find that you need a lot of expensive options to the basic system in order to meet your needs, you should probably consider a more powerful basic system. In many cases, a less powerful system with lots of options will be the more expensive choice.

The main point is to let your demonstrated (as opposed to imagined) needs drive your quest for and selection of development tools. This way you're more assured of using what you buy — at least until the next incompatible project comes along!

software for a new processor usually lags behind that available from the manufacturer by many months or even years in some cases. The general-purpose systems are also usually rather slow by comparison and are designed to be a jack-of-all-trades and consequently master of none. Still, if you need to work with a variety of processors that are not the very latest that technology has to offer, then the general-purpose system is your best choice.

### But how do I learn to use all these tools?

If may not be as hard as it sounds. If you learn well in a classroom environment, then there are several microprocessor courses offered as part of RCA's continuing education program. There are also many good books on microprocessors and system design—some from the manufacturers themselves are free. If you learn best by doing, then there are several microprocessor courses offered that include a small computer system (yours to keep). This is particularly useful since you can continue to play with your small system to gain additional insight and expertise. If you are also an incurable experimenter (once having gained the necessary experience, this person probably makes the best small-system designer), you will probably want to obtain a microprocessor and some support chips and design your own system from the start. You can get by with very little, other than your desire to learn what makes the system tick. You can start off in the "bare-bones" environment, as discussed earlier, and obtain some valuable experience and insight. If you have the desire don't be afraid to dig right in with only a handful of chips. Even if you have no hardware experience, you can usually gain what is needed from a manufacturer's applications note.

### Trends in microprocessor system development

It seems hard to imagine that the microprocessor field began only a few short years ago with the lowly 8008 from Intel. Even the term "microprocessor" has lost some of its original meaning. Some of the newer "micros" can legitimately be considered minicomputers or even mainframes. Micros now come in assorted flavors from singlebit controllers up to 32-bit machines with 4-, 8-, 12-, and 16bit machines in between. The trend is forever upward in size and complexity. Where will it all lead? Will we have handheld 370s before the decade is out? Everyone is squeezing more and more into the same silicon real estate as before; even the limits of optical lithography do not seem to have slowed anyone down.

### How will this trend affect my hardware/software system designs?

For the one-of-a-kind system, life will become increasingly easier as you make use of the specialty support chips now becoming widely available. The software task in many cases will center on merely sending data to and from the support chips. For medium size systems, it will be hard to justify anything written in anything other than a high-level language. With the low cost of memory, you can now reasonably implement your software in FORTRAN, BASIC, Pascal or even PL/1 on even the low-cost 8-bit

Intelligent peripheral control chips essentially reduce the programming burden to one of handshaking.

machines. Microprocessor manufacturers are also designing machines for specific languages by gearing instruction sets to particular languages, such as the Pascal Micro Engine from Western Digital or the Ada-oriented iAPX 432 microprocessor from Intel.

All these advances lead to reduced effort to develop useful applications software. This is very significant when you consider that software development costs and effort are often an order of magnitude greater than those for hardware development. Even the cost-sensitive applications which cannot use these new wonders will benefit from the lower cost of the simpler chips due to the experience gained in making the more complex ones. Overall, we see the trend continuing with more and more specialty chips to reduce your software effort as well as a steady trend towards high-level language development for small systems implementation.

### Will cheaper, more powerful hardware affect software development tools?

Most certainly. The new, much more powerful dedicated computer systems are beginning to blur the distinctions between the LRE and MDS environment. In fact, systems for around \$30,000 combine the best of these two environments—the power and peripherals of a minicomputer, plus a high-speed network for tying systems together (providing the vital communications link found in a time-sharing system). Although these systems can be shared by several users, the tendency as they become cheaper and more plentiful, will be to use them as singleuser ("personal") systems.

Perhaps the most important software trend is the ongoing implementation (through the combined effort of many companies and universities) of generally useful software tool sets. These tools run on any machine that supports FORTRAN (virtually all machines). This effort was motivated by the work at Bell Labs on a system called Unix<sup>™</sup>. Unix<sup>™</sup> consists of an operating system and a very wide and deep set of software tools, all implemented in the high-level language C. For a while Unix<sup>™</sup> only was implemented for PDP/11 computers, but it is now becoming available on a wide variety of computers, including Digital's VAX, IBM's 370, and many microcomputers. This commonality of tool sets across projects and machines will help improve productivity in the software development area.

### It sounds exciting, but...

Although all of these developments help reduce the software effort required for a given application, things are becoming more complex with each new processor. Gaining expertise with each of these new developments will become a greater burden. Development tools will also be more sophisticated and costly, and as everything becomes more complex, you will not be able to do without them. For example, programs written for Intel's 8086 processor are nearly impossible to hand-assemble due to the complexity of both the machine and the assembly language.

### Microcomputer systems and development terms

acceptance test Final test of a system — tests a system's functionality, reliability, etc.

Ada A powerful, new, U.S.-government-sponsored high-level programming language for embedded computer systems, but generally useful for a wide range of applications. It has its origins in Pascal.

assembler Translates an assembly-language program into object code (see "object code").

**BASIC** An old but still thriving high-level programming language used for scientific and other applications. It emphasizes interactive computing.

breadboard The initial hardware part of a system used to iron out the flaws (usually wired by hand).

**circuit analysis program** From a description of an electronic circuit, initial circuit condition, and input (driving) functions, this program simulates the circuit and generates a set of output (response) functions.

Although each of the new chips tends to make things easier than they were before, each of them promises more processing power and speed. At the same time, we are attempting to implement much larger, more complex applications.

Are things becoming too complex? No! There will always be applications which are just out of reach of the current technology. But more and more applications are coming within reach of the ever-expanding microprocessor frontier. This same technology, coupled with sophisticated software packages, means that we will also have the necessary tools to build tomorrow's systems.

### Reference

1: Ripley, G.D., "Some Software Engineering Techniques," RCA Technical Report (Oct. 1980).

David Caracappa has been with RCA since 1974, and is currently a Member of Technical Staff at the Laboratories. Originally he was with Astro-Electronics in Hightstown. While there, he worked on the TIROS weather satellite program and did advanced system design work on utilizing microprocessors in command decoders, telemetry processors, and the space shuttle camera controller. Since joining DSRC in 1978, he has been involved in the design and implementation of microprocessor-based systems for new Consumer Electronics products and color TV manufacturing systems.

Contact him at: RCA Laboratories Princeton, N.J. TACNET: 226-3278

Nils Ny originally joined RCA in 1965 at Astro-Electronics in Hightstown and came to the Laboratories a year later. He has been involved with minicomputer and microprocessor systems for a variety of applications including colorimetry analysis, cable TV communications and factory automation. He is currently a Member **compiler** Translates high-level language programs on host machine into object code for the host machine.

cross-assembler Translates assembly-language programs on host machine into object code for the target machine.

cross-compiler Translates high-level language programs on the host machine into object code for the target machine.

cross-developing Developing software on the host computer for the target computer.

data-flow diagram Shows flow of data and data transformations in a system.

**debugger** Provides execution-time help to programmer in finding bugs in his or her program.

downloader See loader.

editor A text editor (or just "editor") is used to compose and modify a program's source code. A document editor formats a document as it is entered

Authors (left to right): Nils O. Ny, G. David Ripley, David N. Caracappa.

of Technical Staff with the Microtechnology Research Group where he works with microprocessor hardware and software for future consumer electronic products.

Contact him at: RCA Laboratories Princeton, N.J. TACNET: 226-2209

David Ripley originally joined RCA Laboratories as a Member of Technical Staff in 1970, doing research in programming languages and translators. After spending six years at the University of Arizona on the Computer Science Department faculty doing research in language translators and program performance measurement, Dr. Ripley rejoined RCA Laboratories in 1978. He is presently involved in the software for new consumer electronic products and the design of user-computer interfaces.

Contact him at: RCA Laboratories Princeton, N.J. TACNET: 226-2884 into the machine. A graphics editor is used to compose and modify graphics scenes for presentation on a usually high-resolution, color CRT.

electronic mail Enables users of a time-sharing system (or collection of connected computers) to communicate by sending each other messages, or "mail."

emulator Hardware that mimics a particular processor chip.

**EPROM** Eraseable Programmable Read-Only Memory; can usually be erased by exposure to ultraviolet light, and reused.

**executable image** The binary version of a program that can be loaded directly into memory and executed.

**FORTRAN** An old but active high-level programming language used primarily for science and engineering applications, and available on nearly all machines.

function generator Hardware used to produce electrical signals of desired waveshape. These may be analog or digital functions.

**high-level language** A programming language that contains terms and constructs that are high-level (or English-like) and applications-oriented.

**host system** The computer system on which software is cross-developed (see "target system").

**ICE (In-Circuit Emulation)** Debugging by using an emulator instead of the processor chip in the target system.

interface diagram Shows connections of external signals to the microprocessor in the system.

linker Combines separately compiled or assembled object modules into one program by filling in linkages (calls and data references to the various modules).

**loader** Loads an executable image into a computer's memory. If there is loading from host machine to target machine, it consists of two parts: the "pitcher" or the host, sending the image to the "catcher" or the target, which then loads into the target memory. combination is called the downloader.

**logic analyzer** Hardware that displays a state diagram of some of its inputs (usually 8 or 16) upon occurrence of a specified condition of the other inputs (usually 16).

MDS Microcomputer development system.

micro See microcomputer.

**microcomputer** A single chip containing a processor, RAM, ROM (or EPROM), and I/O.

microcomputer development system A host system

consisting of a computer, I/O devices (e.g., CRT, printer), mass storage (e.g., floppy disk), and software for developing software for a target system.

**microprocessor** A single chip containing only a processor.

**module** A single main program, subroutine, procedure, or function.

**object code** The binary representation of a program — translated source code.

**oscilloscope** Hardware which displays a graphical representation of one or two inputs.

**Pascal** A modern, high-level programming language, used for a wide range of applications, that emphasizes flexible data types and error checking.

**PL/I** A large high-level programming language for general-purpose use that has features from FOR-TRAN, COBOL (a popular business language), and ALSOL (an early scientific language).

**port** The physical means through which a computer communicates with external devices (there are typically at least several of these per processor).

**processor** The central processing unit in a computer. It fetches and executes instructions.

**RAM (Random Access Memory)** A memory device, an arbitrary location of which can be read from or written into.

**relocator** Relocates object code addresses to enable the code to reside in a specified memory location.

**ROM (Read Only Memory)** A memory device, an arbitrary location of which can be read from but *not* written into.

simulator Simulates the execution of one computer on another computer.

**source code** The original, human-readable representation of a program.

**strobe** An electrically generated pulse that can be used to synchronize other events.

system block diagram Shows basic functional portions of the system and their relationships to each other.

target system A computer system for which software is developed (see "host system").

test plan Describes tests to be made on the target system and specifies intent, expected results, and chronology.

time-sharing Scheme for sharing a computer between a number of simultaneous users, each of which appears to have the computer to himself or herself.

### New CDP1805 microprocessor upgrades CDP1800-based systems

A new microprocessor, the CDP1805, speeds throughput and reduces chip count while retaining all the advantages of the register-based CDP1800-series architecture.

Abstract: The CDP1805, an updated version of the timetested CDP1802 microprocessor, possesses on-chip hardware and software functions that are similar to those found on many microcomputers. These additional functions, coupled with a higher clock rate than on the CDP1802, can offer significant improvement in both system throughput and integration, as well as widen the field of application of CDP1802-based systems.

The RCA CDP1800 microprocessor series is a well-tried LSI product line that implements control-oriented microcomputer functions in CMOS technology. The preeminent device of the series, the CDP1802, has been in production since 1977, with yearly output now exceeding one million devices per year. Finding its way into a wide range of applications that require low power for portability, high noise immunity for satisfactory operation in industrial environments, or a wide operating temperature and voltage range to assure optimum performance under a wide variety of ambient conditions, the CDP1802 has established itself as the leading CMOS microprocessor. With the introduction of the CDP1805 by RCA, CDP1800-based designs can be further enhanced, and proposed new or improved system designs whose performance requirements previously exceeded the capability of the CDP1802 can now be implemented.

### The CDP1800-series microprocessor architecture

This section will help readers unfamiliar with CDP1800series architecture to understand its fundamentals and salient features, so that the enhancements achieved in the CDP1805 can be more fully appreciated.

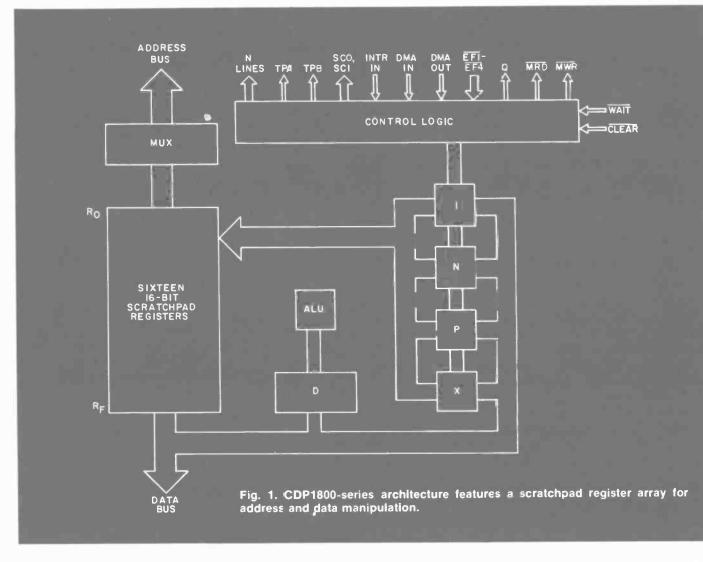

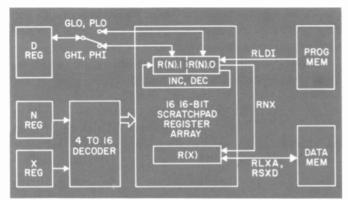

Reprint RE-26-8-2 ST-7009 Final manuscript received July 15, 1981. As shown in Fig. 1, the central feature of the CDP1800series microprocessor is an array of sixteen 16-bit scratchpad registers used to provide control over memory addressing and internal housekeeping. When used to address memory, the registers are selected by software instructions that load 4-bit values into register selectors (P,N,X). These selectors program the scratchpad registers as program counters, memory pointers, and stack pointers. This assignment flexibility allows the use of multiplepointer and context-switching techniques, and provides quick subroutine-call implementation and efficient stack and interrupt handling in real-time control applications. In addition, these same registers can be used for variable data storage, providing up to 30 bytes of data memory on-chip.

The 16-bit-wide register-array matrix provides two advantages in its dual use in address and data operations. A  $2^{16}$  or 65,536-byte memory address range is possible for RAM/ROM addressing in main program, subroutine, and stack operations. For data storage, the contents of each 16bit register can be used as a 16-bit data word, with instructions for increment, decrement, register-to-register, and register-to-memory manipulation of 16-bit operands. Thus, 16-bit arithmetic and logic operations can be supported by this internal architectural configuration.

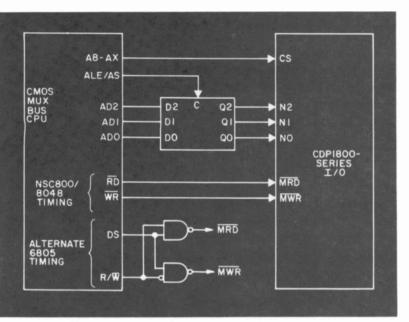

Externally, CDP1800-series devices interface with a variety of bus and I/O pins to external memory and peripheral functions. Memory addresses are generated via a multiplexed address bus; a latching TPA signal is provided for the high-order byte. I/O addressing is accomplished via a separate 3-bit I/O bus with dedicated instructions for data transfer between memory and peripherals.

Other I/O lines are provided for on-board DMA address and control-line generation, for interrupt vectoring, for use as flag lines for polling, and for implementation of a Q-lineoutput port for control of external devices. The flag and Q lines, in conjunction with a software-driver routine, can also be used as a serial port to external I/O.

The remainder of this article describes specific CDP1805 features and explains how they are optimally applied in a microcomputer system.

### CDP1805-the specifics

### **On-board RAM complement**

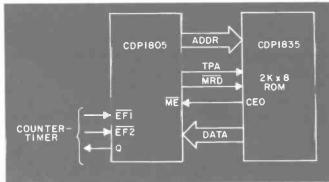

The CDP1805 includes, on-board, a 64-byte RAM array in addition to the 16 x 16 scratchpad register array described above. The RAM's six address lines are internally connected to the CPU section; the eight data lines are part of the CPU's external bus. The chip-select function for the RAM is available through pin 16 (the  $V_{cc}$  connection on the CDP1802). Thus, the RAM is essentially configured as independent memory, with its 64-byte block locatable anywhere in memory space, and with its data lines available to external 1/O for reading and writing. The 64-byte block is of adequate size for a stack area, being able to handle many levels of subroutine and interrupt nesting, as well as providing sufficient space for a modest data stack for main program or 1/O routines. Figure 2 shows a typical connection of the CDP1805 in a CDP1800-based system.

Fig. 2. Minimum connection diagram for a CDP1800based system that includes CPU, 2-kbytes ROM, 64 bytes of RAM, and a counter-timer.

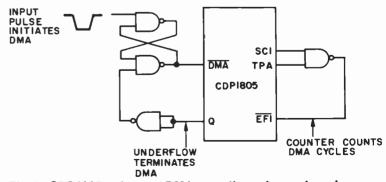

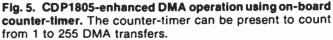

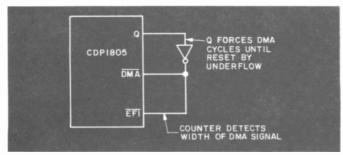

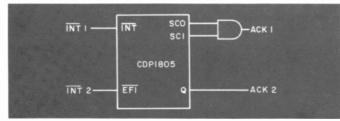

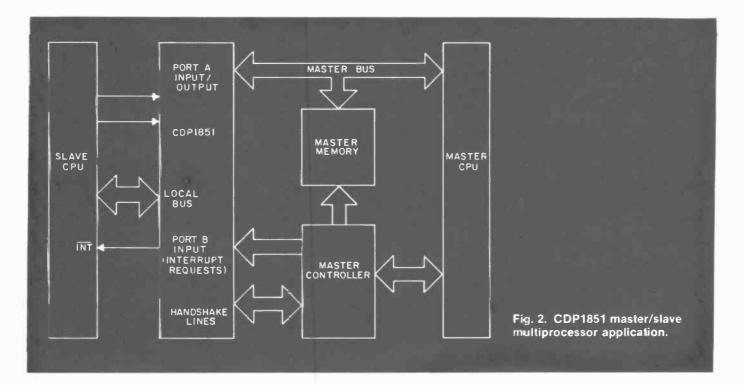

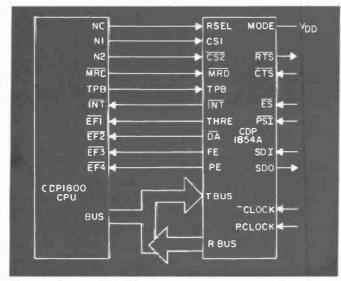

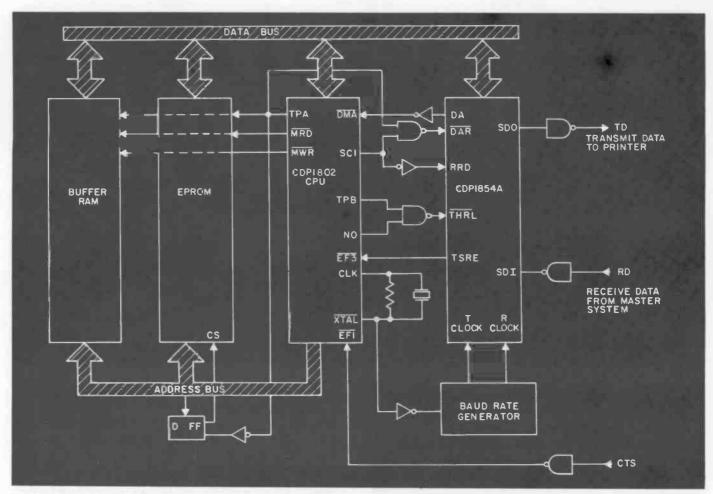

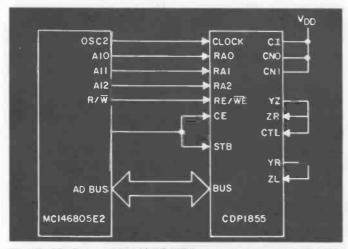

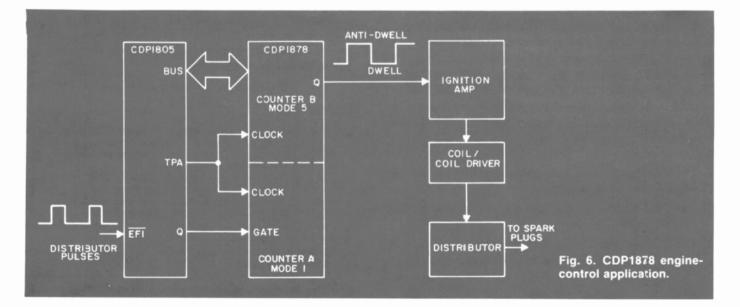

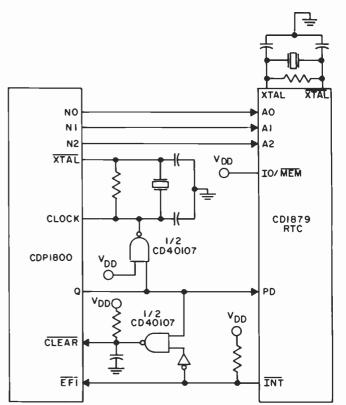

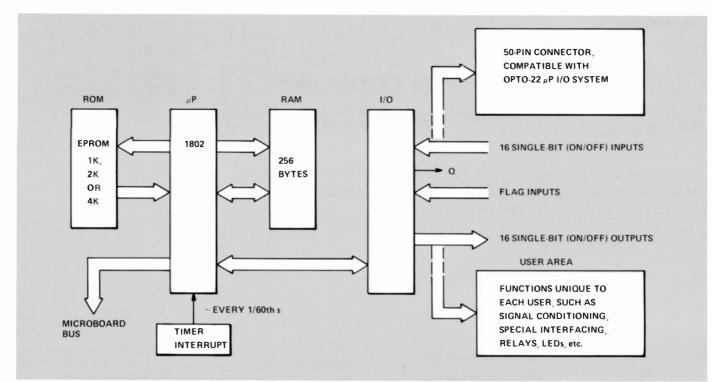

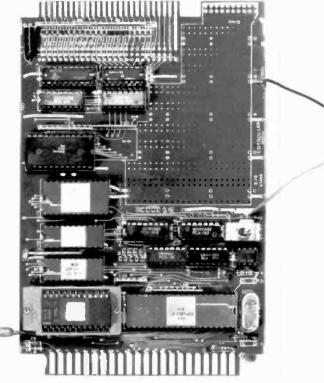

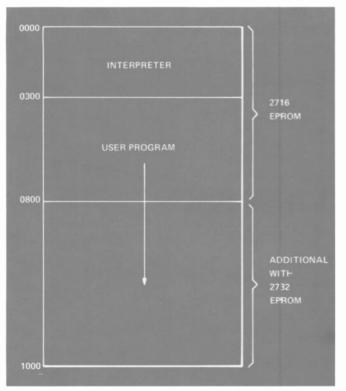

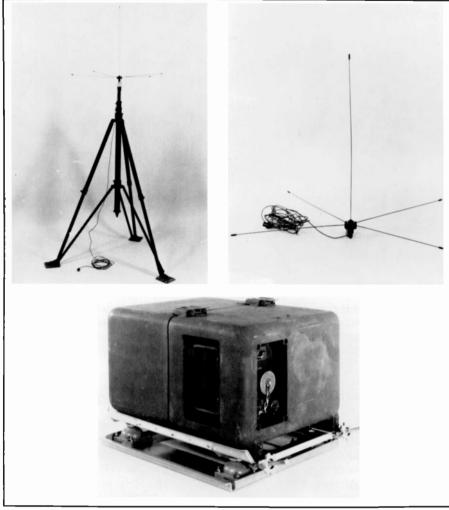

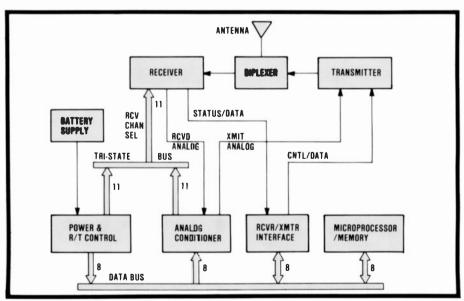

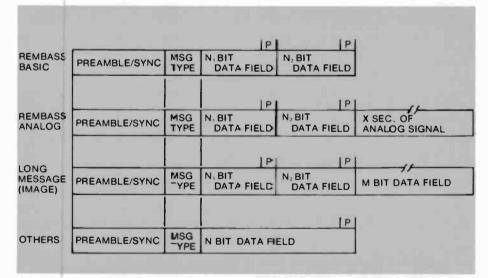

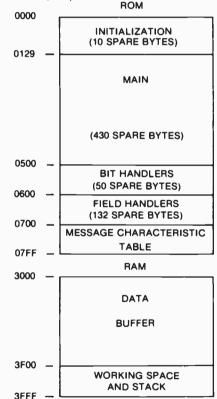

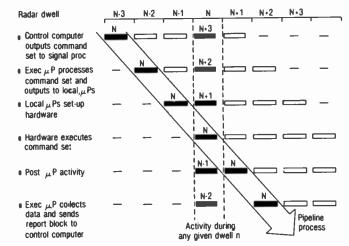

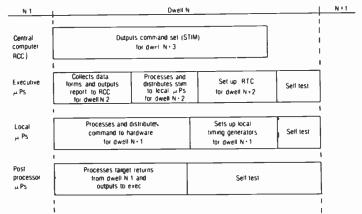

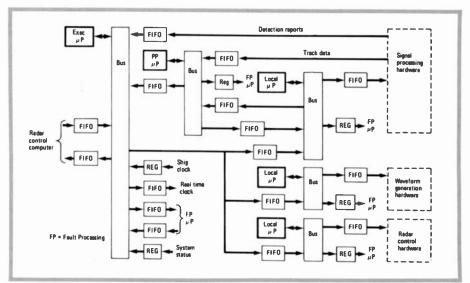

### On-board counter-timer