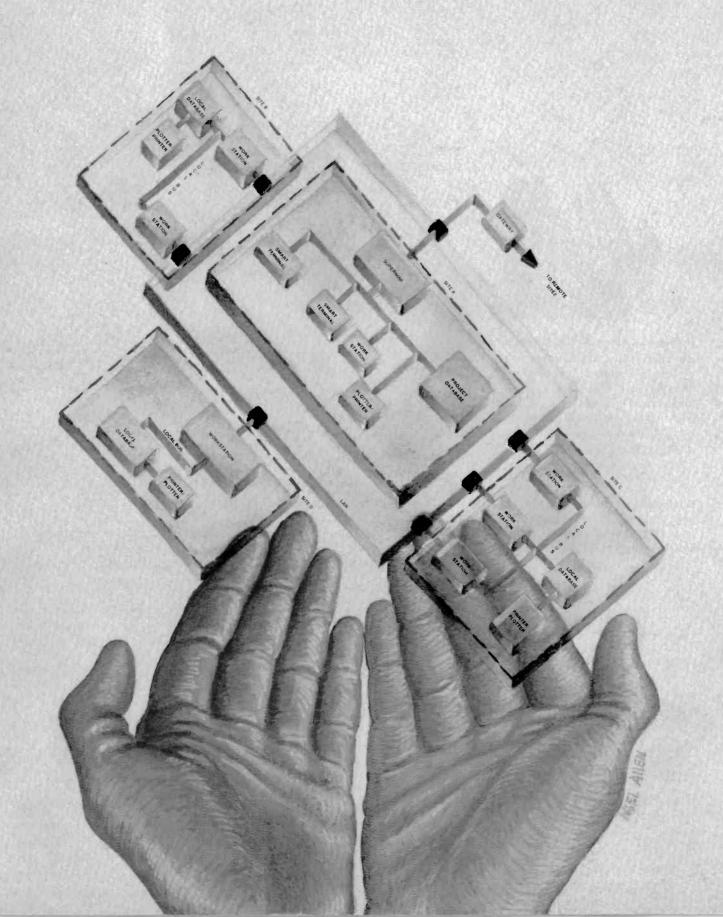

Cover illustration by Mel Allen

#### Putting computer power at the engineers' fingertips.

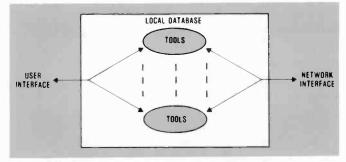

Our cover depicts the possible shape of future systems that could allow engineers at different sites to have system-wide access to tools on other stations and on a superminicomputer. In this issue, RCA authors describe today's realities—the ongoing and successful efforts to automate the engineering workplace.

-MRS

**Illustrations** on pages 7 and 12 by Mel Allen; page 13 by Diane Farkas; page 20 by Helen Mary; page 28 by Denise Miller; and page 61 Joseph McGarrity.

### **RGA** Engineer

A technical journal published by RCA Technical Excellence Center 13 Roszel Road P.O. Box 432 Princeton, NJ 08540 TACNET: 226-3090 (609-734-3090)

#### **RCA Engineer Staff**

**RCA Laboratories**

**RCA** Americom

Staff Vice-President, Systems Engineering,

Vice-President, Technical Operations,

Division Vice-President, Engineering, Government Systems Division

Division Vice-President, Engineering,

Video Component & Display Division

Senior Staff Scientist, RCA Laboratories

Division Vice-President, Engineering,

Manager, Engineering Information,

Staff Vice-President, Engineering

**Technical Excellence Center**

**RCA Service Company**

Director, Technical

**Excellence** Center

Tom KingEditorMike SweenyAssociate EditorLouise CarrArt EditorFrank StroblContributing EditorBetty GutchigianCompositionPhyllis GrimmSecretaryEditorial Advisory Board

Jay Brandinger

John Christopher

Jim Feller

unit i ener

Mahlon Fisher

Tony Bianculli

Arch Luther Howie Rosenthal Joe Steoger

Bill Underwood

Bill Webster

Ed Burke

Walt Dennen

John Phillips

Consulting Editors

Administrator, Marketing Information and Communications, Government Systems Division Manager, Naval Systems Department

Vice-President, Laboratories

Communications and Information, Missile and Surface Radar

Manager, Business Development and Planning, RCA Service Company

● To disseminate to RCA engineers technical information of professional value ● To publish in an appropriate manner important technical developments at RCA, and the role of the engineer ● To serve as a medium of interchange of technical information between various groups at RCA ● To create a community of engineering interest within the company by stressing the interrelated nature of all technical contributions ● To help publicize engineering achievements in a manner that will promote the interests and reputation of RCA in the engineering field ● To provide a convenient means by which the RCA engineer may review professional work before associates and engineering management ● To announce outstanding and unusual achievements of RCA engineers in a manner most likely to enhance their prestige and professional status.

C.A. Quinn

# Bringing computer power to the engineer

The strength and vitality of our engineering community sets the pace for RCA's future. Increasing pressures for shorter design cycles, better quality designs, and faster response to changing market needs, all focus on the effectiveness of the engineering staff. The growing complexity of the engineering task reaches beyond the design cycle into vital areas of the manufacturing process. This demands better coordination and control.

Sheer numbers of engineers will not suffice in the solutions to these types of problems. We must ensure that each engineer is operating at maximum potential—increasingly, this means engineers must have direct access to computer tools that improve individual productivity. Personal computers, graphic work stations, electronic communications, retail software, and so on, offer new options that complement and extend the conventional mainframe solution. At the same time, the multitude of choices can lead to chaos if a broad plan is lacking.

RCA management is addressing these issues by investing heavily in programs that bring computer power directly to the engineers. The productivity and performance gains that will ensure our future are dependent on meeting this challenge.

Many exciting steps are underway across the Corporation. This issue of the *RCA Engineer* reports on some of the leadership efforts.

1 A

Charles A. Quinn Division Vice-President and General Manager, Video Component and Display Division

|                                        | Vol. | REA Engineer<br>29 No. 3 May June 1984                                                                                                  |

|----------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| integrating<br>individual workstations | 4    | VCAD, an engineering productivity strategy<br>J.C. Miller                                                                               |

|                                        | 10   | Personal computers, an engineering productivity tool<br>J.C. Miller   W.T. Kelley                                                       |

|                                        | 15   | CADAM, an engineering productivity tool<br>J.C. Miller   P.J. Kunz                                                                      |

|                                        | 20   | Emerging engineering design tools<br>E.M. Melendez                                                                                      |

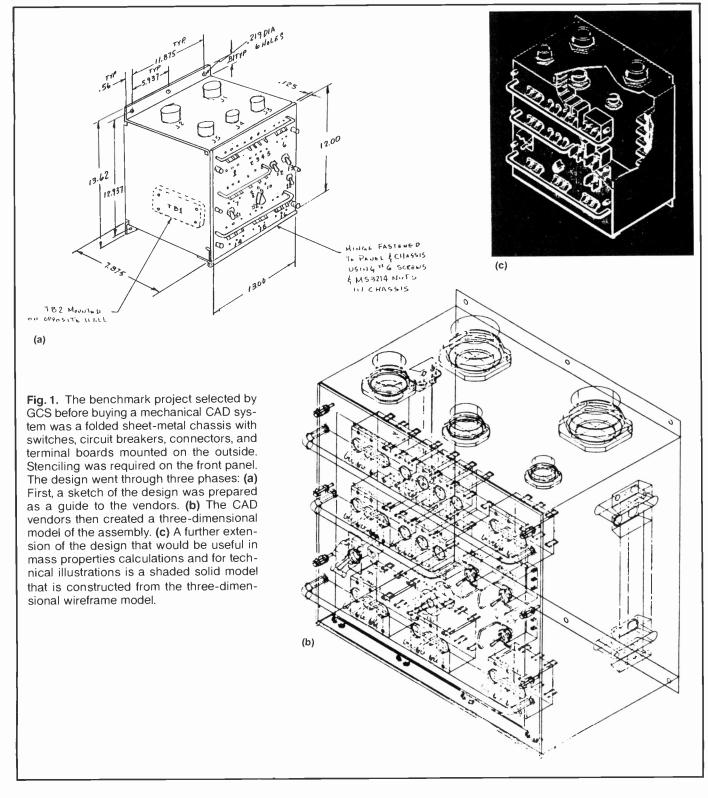

| the buying decision                    | 28   | Choosing a CAD system<br>C.A. Burton                                                                                                    |

|                                        | 35   | The MSR local area network<br>W. Carey                                                                                                  |

| services                               | 39   | An attached processor provides calculation speed<br>and accuracy<br>S.G. Handman                                                        |

|                                        | 43   | Adapting CMS for a varied user community<br>D. Zarodnansky                                                                              |

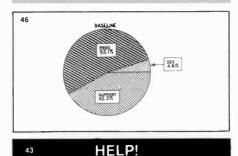

|                                        | 46   | Analyzing design alternatives with the PRICE models<br>A. DeMarco                                                                       |

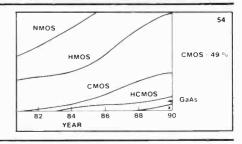

| general interest                       | 54   | CMOS technology moves towards IC leadership<br>H.G. Patterson   J.L. Magos                                                              |

|                                        | 61   | A day in the life of an information-efficient scientist<br>P. Schnitzler                                                                |

| departments                            |      | Pen and Podium, <b>63</b> News and Highlights, <b>66</b> Obituary, <b>72</b><br>Copyright © 1984 RCA Corporation<br>All rights reserved |

#### in this issue ... automating the engineer's workplace

■ Miller: "The VCAD design philosophy has been to provide a locallybased distributed system in a standard environment with a logical and comprehensive communication framework."

■ Miller/Kelley: "The PC was not viewed as some sort of super-design workstation for the elite engineer."

■ Miller/Kunz: "We envisioned a need for a large number of terminals, fast response time, a tight focus on productivity, a common database across all users, and a desire to access a wide set of software tools."

■ Melendez: "Both these subsystems will be linked together onto a network and will share an adaptive design database management system that will behave as the central data-monitoring and control facility."

### **Burton:** "Outlined below are some of the major areas we investigated with each CAD company under consideration."

- **Carey:** "Our hardest task was to decide which of a number of technically excellent replies (to a request for proposal) was the best."

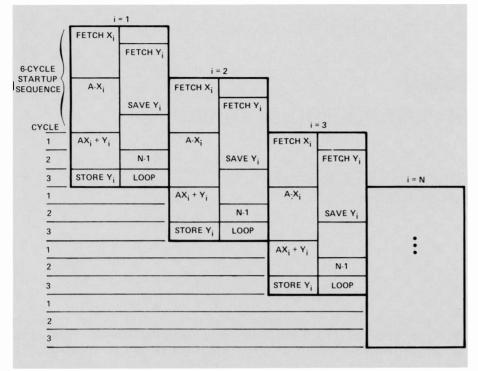

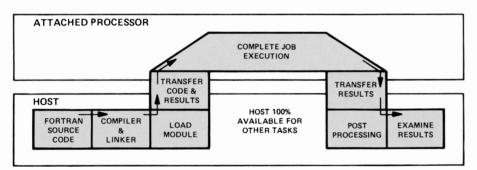

- Handman: "At RCA, the engineering community can take advantage of pipelined calculations in such diverse applications as circuit analysis and structural analysis."

**Zarodnansky:** "Experience has shown that if users can get immediate on-site assistance with a problem, they are more likely to continue to make use of the products provided on the system, and to ask for assistance when they need it."

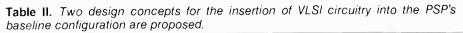

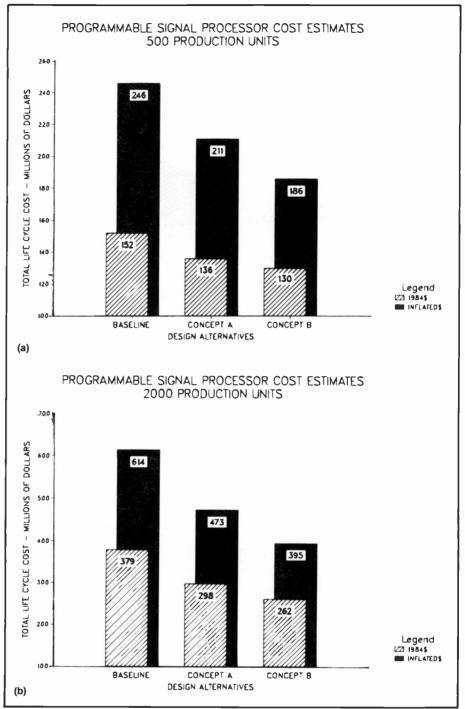

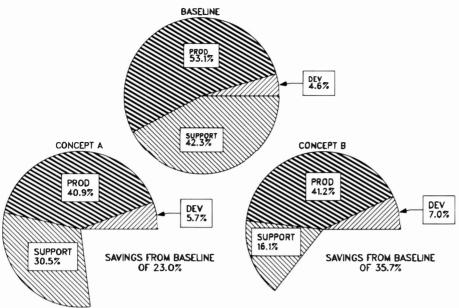

**DeMarco:** "The potential use of the PRICE system throughout the life of a program was illustrated by the Programmable Signal Processor study."

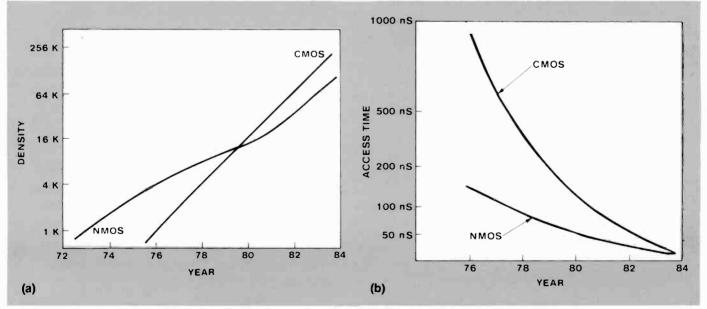

■ Patterson/Magos: "CMOS use is growing in linear circuits such as operational amplifiers and analog-to-digital converters, and it is fast becoming a key technology for the emerging telecommunications and data communications markets."

in future issues... technical excellence, materials science applications, imaging technology, communications.

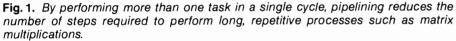

#### ATTACHED PROCESSOR

39

### VCAD, an engineering productivity strategy

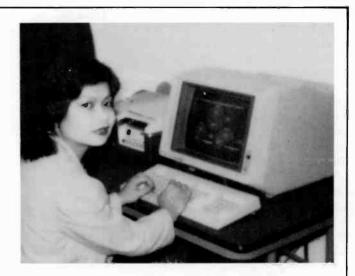

VCAD is an aggressive computer-based engineering productivity strategy. Video—Computer-Aided Design tools are already dramatically changing the work style of engineers, technicians, secretaries, and managers at RCA Video Component and Display Division.

The Video Component and Display Division (VCD) had made modest use of computer technology in previous years; critical design needs had been programmed, but most of the ancillary tasks were fragmented across departmentally based systems. Limited use was made of the Corporate Computing Center due to its cost, features, and remoteness. Lacking a coherent plan, the Division had acquired a number of small computers, each different and incompatible. There were few economies of scale. Many tasks suitable for a computer remained in a manual mode. The dilemma was how to change to a modern sys-

**Abstract:** VCAD is an aggressive computer-based engineering productivity strategy; the initials stand for the Division's name as well as "Video-Computer-Aided Design." This paper describes the VCAD system from concept through implementation and covers the purpose, architecture, major subsystems, training, and early results. VCAD has been a successful program. Even at this early stage the best testimonial is the strong desire from the engineering managers for more VCAD tools. Although VCAD is technically a computer system, from a managerial perspective it is a productivity multiplier. Companion papers in this issue contain expanded treatment of two VCAD subsystems: the CADAM graphics design system and the use of personal computers.

©1984 RCA Corporation Final manuscript received March 22, 1984 Reprint RE-29-3-1 tem without destroying the existing base of applications.

Video—Computer-Aided Design (VCAD) began in early 1983 as a multiyear proposal to increase the productivity of the Engineering Department through a carefully designed and well-integrated computer system. By the end of 1983, Phase I of the VCAD program was complete; a broadly conceived system had been installed and was in productive use.

#### Approach

The VCAD effort began with a recognition of the primary needs of the Engineering Department. We sought increased productivity and concluded that a massive infusion of computer technology was needed, but we lacked the resources to write large amounts of code or to tackle major technological risks in the computer approach. We recognized that our community required assistance in administrative (non-technical) computing, electronic sharing of information, coupling of discrete systems, increased local computer "horsepower," and graphical design aids. Significantly, VCD senior management was willing to back the VCAD project based upon intuitive productivity arguments as opposed to conventional cost/benefit analyses.

The VCAD design philosophy has been to provide a locally-based distributed system in a standard environment with a logical and comprehensive communication framework (see sidebar, facing page). Fortunately, the evolution of the computer art had resulted in technology that was not available in earlier years. An approach was defined based upon several elements.

- Use of the IBM 4341 computer with VM/CMS as the core of the system. This is a low- to mid-range machine with very reliable hardware and a stable operating system. The host can be upgraded as the system load demands. The IBM 4341 runs in an unattended mode 24 hours a day, 7 days a week. All non-IBM computers and terminals link to the host via the communication nework.

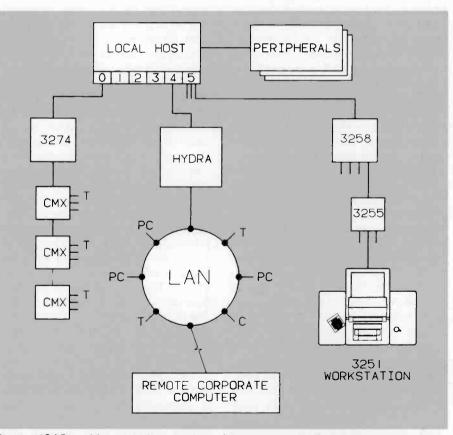

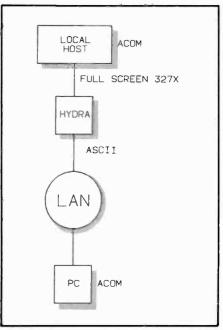

- Construction of a local area network (LAN) to serve as the communication bus joining the host and the many terminals and computers already in place. A LAN is a multi-port communication switch that allows one to logically and simultaneously connect pairs of terminals; it uses translation tables and a network controller to link devices with different protocols, transmission speeds, parity conventions, and so on. Within rather wide limits any two devices can be coupled. The LAN provides the technical means to accommodate the variety of existing terminals and eliminates the need for an additional investment.

- Recognition of the personal computer as the key to putting computer power directly on the desk of the professional. The IBM personal computer (PC and XT) was chosen as our standard. Each PC was attached to the LAN and can operate in either a stand-alone or 3278-terminal mode. The PC provides adequate dis-

#### Video—Computer-Aided Design overview

The goal of VCAD is increased productivity. The VCAD approach is to saturate the entire engineering department with common hardware and software under a comprehensive integrated system design.

Central host computer. A common hub to the overall system, this is currently an IBM 4341 running VM/CMS. It services CADAM, PROFS electronic mail, VSFORTRAN/VSPASCAL programming languages, interactive and batch work. It also holds common databases and core software, and is easy to expand as requirements dictate. The IBM host supports various IBM, and non-IBM terminals via a 3274 controller and local area network. The computer is highly stable and flexible; it runs unattended 24 hours a day, non-stop.

Local area network. The LAN is an "electronic highway" that links various terminals and computers in a standard framework. As a solution to our problem of equipment from many vendors, the LAN handles devices with different protocols, baud rates, parity conventions, and so on. It supports the PC as a 9600-baud full-screen device, and can transfer files between dissimilar terminals or computers. The LAN

tributed computing power on a local (and immediate) basis while retaining the ability to link to the IBM 4341. Each PC has a common configuration and software complement (see companion paper, by Miller and Kelley, for details).

Selection of a turnkey graphics design package CADAM (CADAM Inc.) as the vehicle for converting the core of the manual design process into an integrated system. Centralizing all of the graphics information into a common database eliminates many duplicate manual steps and enhances productivity. A scaled-down variant of CADAM, IBM's FAST-DRAFT, was selected for our remote plants in Marion and Scranton (see companion paper, by Miller and Kunz, for details).

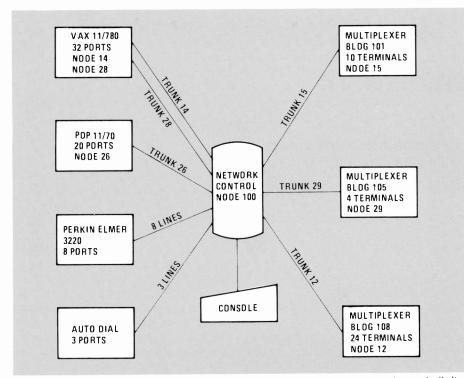

#### Configuration

The initial phase of VCAD hardware (Fig. 1) consisted of a fully implemented LAN covering the entire Engineering Department, an IBM 4341 with four megabytes of memory, three 800-megabyte disks, a tape drive, a 3274 controller for the 3270-class terminals (provision for 32), two 16-port Hydra (JDS Microprocessing) protocol converters, three Displaywriters and seventy-

is linked to the host via a Hydra protocol converter.

Personal computers. These off-load work to a locally-controlled environment. Powerful PC software lets users solve their own problems where possible. PCs support word processing, spreadsheets, planning, databases, analysis, and so on. They can act as 327X-class terminals to the VCAD host when desired. Personal computers are used by all levels of the organization as the basic computer terminal.

CADAM graphics design. CADAM offers a 0.3second response time to user requests, supports a large number of users sharing a divisional database, and will eventually grow to 50-plus CADAM terminals. CADAM's friendly design environment is based upon well-known drafting methodology. Using this system, it's easy to train new users and get rapid productivity gains. It generates high-quality output drawings on the Versatec plotter in 30 to 60 seconds. CADAM comes in modules that extend the system to many application areas. The system drives CAEDS and ANSYS to generate 3D designs and finite-element analysis, and couples to a numerical controlled machining module.

**Fig. 1.** VCAD architecture. An overview of the communication arrangement, showing 3274 controller path, the Hydra link, the local area network, and the CADAM terminal arrangement. The local host serves as the gateway for communications. The LAN connects various terminals, PCs, and non-IBM computers as required.

three IBM PC/XTs—all linked to the LAN, six 3251 graphic design terminals and associated controllers, five printers, and a 36inch Versatec electrostatic plotter. There are now 168 devices (computers, PCs, terminals) attached to the LAN. The 3251s are 19-inch video graphic design terminals used exclusively with the CADAM design software. We chose the NET/1 LAN hardware from Ungermann-Bass and linked it to the IBM host via the Hydra converter. IBM full-screen terminals (3178/3279) were supported by a 3274 driving Ungermann-Bass's CMX multiplexors.

The communication arrangement is nonconventional. From the outset we were faced with the need to support the existing terminals (from many vendors), and the new IBM terminals. The LAN provided a vehicle for linking the existing terminals but the question remained, "How could we best attach the LAN to the host?" The usual solution would have been an IBM 3705 front-end processor. The Hydra offered most of the necessary features at a lower cost, and with a somewhat simpler system interface. The Hydra is a protocol converter that presents asynchronous screenoriented devices to the host as 3278 terminals with cursor control. As a side benefit, the Hydra-supplied PC-3278 terminal emulator (ACOM, Computer Vectors) was found to be superior to the IBM 3101 emulator. We have been very pleased with the full-screen terminal mode of operation for the PC. A suitable emulator was also found for the (existing) Hewlett-Packard terminals, which enables them to communicate with the host via the LAN.

It was desirable to avoid the star architecture associated with the conventional 3274 cabling for the IBM-class terminals. The CMX multiplexor operates in a daisychain mode that makes it possible to greatly reduce the total cable length of the installation. The communication arrangement offers considerable flexibility in installing new devices. On the other hand, the Hydra decision splits the functional responsibility between two vendors in a critical area. Both Hydra and IBM have been responsive in solving communication problems and offering support. On balance, we have been pleased with the design choice.

Most of the engineering managers use a personal computer as their terminal, and the majority of the engineers have reasonable access to some kind of terminal. Our plan is to have an appropriate terminal available for every user.

#### Software

It was our goal from the outset to stay with "plain vanilla" software as provided by the vendor and resist the temptation to modify it. This made it possible to minimize the support effort required and improve the overall system stability. All new application software was purchased and applied to the system without change. Many of the programs developed in the past already ran on the same operating system as the corporate computer at Cherry Hill, N.J., thus eliminating the need for a conversion-but this did require the installation of twelve VM/CMS system patches from Cherry Hill to retain compatibility. Overall, the "plain vanilla" and "buy, don't write" combination were good decisions.

For example, the host software complement includes VM/CMS, VSFOR-TRAN, VSPASCAL, PROFS, CADAM, CAEDS (SDRC Inc.), and ANSYS (Swanson Analysis). By retaining total control of the project, it has been possible to finetune the operating system to achieve the desired response times and performance for the various user groups-this would have been difficult to do under shared circumstances. All engineering applications previously run at Cherry Hill (except for a very large design program) have been brought back to the VCAD system. The PCs run Lotus123, MultiMate (SoftWord Systems), and other purchased software. The PC 3278 emulator (ACOM) is a fullscreen package obtained from Computer Vectors. It also supports file transfer between host-PC and PC-PC.

The Lockheed-developed CADAM system was acquired as the basis for all graphic engineering design. This is a proven modular product capable of running a large number of graphic design terminals on the same system, all sharing a common database. CADAM offers extensive design features coupled with subsecond response to operator inputs. The fast response time is the key to productivity. CADAM is viewed as the most important application on the host. CAEDS and ANSYS support finiteelement modelling.

IBM's PROFS was adopted as the core electronic mail system, but is not the primary tool for word processing. This decision was approached with mixed emotions due to the rather negative observations formed in the RCA Laboratories' experiment. The reasons for the relatively successful installation to date include: VCAD's broad base of installed PROFS users (you have to span the people you normally communicate with), cautious start-up, careful training, follow-up support, but primarily, our nondependence upon the PROFS limited word processing features.

Word processing is supported by a mix between standard PROFS features and MultiMate on the PC. MultiMate relieves the pressure on DCF document preparation, the weakest part of PROFS. Except for three Displaywriters, all Engineering secretaries use MultiMate on their IBM personal computer for their daily work. The ACOM emulator makes it possible to transfer files between MultiMate and PROFS in a straightforward fashion, making it a user decision as to where each task is done.

The PC not only supports useful applications locally, it also off-loads substantial work that would otherwise have "cluttered" the host. In our environment, this reduces the interaction between CADAM and other host-based programs while offering better support to the user. The low cost and wide variety of PC software make it easier to pursue new applications.

#### Training

The VCAD program had high management visibility within the Division. Extensive training was provided for each facet of VCAD. Locally available talent was mobilized to present a wide variety of training courses, lectures, demonstrations, visits, and so on. Much of the success of VCAD may be attributed to the careful planning of the training effort.

A simple but effective "PC College" was established to indoctrinate users into the use of their new tool and the standard software. Participation in the PC College was a prerequisite to receiving the computer. Extensive and highly personalized CADAM/CAEDS/ANSYS training programs were developed ranging from introductory level material to advanced topics. Training was provided for each software package and for all levels and skills. Training is a demanding, expensive, but vital task. Failure to train leads to frustration, inefficiency, and ultimately to lack of results.

The VCAD training program used a top-down philosophy wherever possible. This simple management concept has proven itself to be a powerful one and has removed much of the mystery from the computer. Mr. C.A. Quinn, VCD Vice-President and General Manager, was the first CADAM student, one week after delivery of the VCAD system; the Division Controller and MIS manager also received early training.

Before an individual user could be trained to use a CADAM terminal, every manager in the chain of command up to the Divisional General Manager was required to have CADAM training. This technique required management commitment and paid substantial dividends in the following months. The managers' intimate knowledge of CADAM has greatly facilitated their constructive use of the system. Similarly, in the PC area, the initial terminals were preferentially assigned to managers who took training as a condition for receiving a PC. Their hands-on understanding made it easier to extend the process to their subordinates. Reminiscent of the famous Western Electric Hawthorne study, this active management involvement contributed to the success of the program.

#### Measurement

Since the major purpose of the VCAD investment was to enhance engineering productivity, significant effort was devoted to measurement. Engineering productivity is a particularly elusive quarry. Prior to the delivery of the system, detailed measurements were made of the number of hours required to develop each type of engineering drawing in the various departments. This data was used as a benchmark to measure the progress of the CADAM system. We have used results from General Motors (who has reported a 3.81 productivity improvement with CADAM) as our nominal goal. After only one month of CADAM experience, all operators were exceeding their manual rates and were

pleased with the CADAM system. Monthly and daily data is being gathered and published to track our progress in detail. A CADAM user group was quickly established to reinforce good practices and provide a feedback forum.

The impact of personal computers on productivity had been sampled by a survey of the users shortly after delivery of the machines and will be repeated after a six-month interval. PC user groups have also been established, sponsored by the MIS Information Center.

#### Implementation

A conceptual plan for the VCAD project was submitted in April 1983, approvals were obtained by midyear, and the equipment was installed and made fully operational by December 7, 1983. All project dates and goals were met. Corporate CISS Staff was helpful at all points and cooperated in allowing a flexible approach to the myriad of hardware/software changes that occurred during execution of the plan.

The plan was implemented by two taskforce teams: one interfacing with the vendor (IBM) and another (VCAD) with the user community. Each task force met on a biweekly basis for two hours and represented a collateral duty for its members rather than a full-time assignment. The VCAD task force consisted of a representative from each user department and was particularly useful in hammering out the necessary system-design compromises and communicating with the user community. The smaller IBM task force met with the vendor to deal with the technical details of the project. Excellent support was provided by the vendor. Two full-time professionals were added to the engineering staff to support VCAD.

#### Expansion

At the outset of the VCAD program a Phase II expansion was envisioned for 1984; in fact, this process is well underway and will more than double the system resources by midyear. Phase II will result in additional PCs, 3178 and 3179 terminals, and triple the number of CADAM stations (using the new 5080 color terminals). Moreover, this phase will lead to an upgraded host, doubled disk storage, an A-size Versatec plotter, and new software

modules (CADVUE, TRANSGRAPH, PRANCE/CBDS, SQL, and so on).

The expansion will broaden the CADAM applications beyond the initial mechanical area into electrical designs (schematics, printed circuit board routing and placement, simulations). PROFS usage will go beyond routine electronic mail into mechanizing a number of paper-based subsystems. We intend to merge Engineering Standards into the CADAM database. A new task force has been formed to begin the process of extending CADAM into the numerical controlled machine area. As with Phase I, the expansion will be coupled with an active training program. The project is being planned using the Harvard Project Manager (Harvard Software Inc.) on an IBM XT. MIS has adopted the VCAD architecture as the basis for the new divisional efforts.

#### Acknowledgments

My sincere thanks to M.B. Fisher and C.A. Quinn who authorized VCAD on faith; J. Balling (CISS) who ran interference; T. Hart (MIS) who became an enthusiast; P. Kunz (CADAM), W.T. Kelley (PCs), B. Mangolds (Communication), and K. Walker (System) for their key contributions; and to the remaining members of

James C. Miller is the Manager of Technical Projects and Engineering Administration at VCD in Lancaster, Pa. He earned a BSEE from Rensselaer Polytechnic Institute and an MEng and PhD from Yale University. He received the Honeywell Award from Yale, three RCA Laboratories Achievement Awards, and shared the David Sarnoff Award for Outstanding Technical Achievement, Dr. Miller holds 23 U.S. patents and has published extensively. His current interest is in the application of computer technology to improving organizational productivity. Contact him at: Video Component and Display Division Lancaster, Pa. TACNET: 227-6490

the VCAD Task Force—M. Renfro, H. Hillegass, R. Miller, R. Marsland, C. Lausman, and G. Gadbois—who represented the user community in a professional manner and whose cooperation was essential.

#### Resource guide: VCAD system hardware and software

This set of articles on the VCD Engineering organization's progress toward a network of automated workstations includes numerous references to equipment and software. To help you sort out the options, we have culled this briefly annotated listing complete with company addresses from our own site-specific experiences. If you have any questions, why not call the authors? Or write the manufacturers.

The asterisked items (\*) denote PC hardware and software that are considered "standard" for the VCD Engineering organization; individual machines vary in software/hardware configuration. The double asterisk (\*\*) indicates "under study." We do not necessarily purchase from the source indicated. All of the items have been found to be useful in VCD applications, but this does not constitute a blanket endorsement. All software mentioned will work on our standard hardware configuration.

#### Personal Computer Hardware

**Computer:** IBM PC with Dual Floppy\* or XT System Unit\*, with a memory of 256 Kb (minimum)\*.

Adapter boards: Monochrome/Printer Adapter\* [IBM]; Asynchronous\* [IBM]; Color Graphics [IBM]; Printer Adapter [IBM]. Alternates: STB Graphix Plus\*\*. Monochrome graphics. [STB Systems Inc., 601 N. Glenville Avenue, Suite 125, Richardson, TX 75081]. Hercules. Supports monochrome graphics. [Hercules Computer Technology, 160 Beechnut Drive, Hercules, CA 94547].

*Display/monitor*: Monochrome\* [IBM]; Color [IBM].

Keyboard: IBM\* [IBM]. Alternate: Keytronic KB5151\*\*. Separate numeric and cursor-key clusters. [Key Tronic, P.O. Box 14687, Spokane, WA 99214].

**Printer:** Okidata ML93 with IBM Plug'n Play Kit\*. Our standard PC printer [Okidata Corp., 111 Gaither Drive, Mount Laurel, NJ 08054]. *Alternate:* NEC 3550 with Dual Bin sheet feeder. Letter-quality printer for secretaries. [NEC Home Electronics (U.S.A.), Inc., Personal Computer Division, 1401 Estes Avenue, Elk Grove Village, IL 60007].

#### **Personal Computer Software**

**Operating system:** DOS 2.0\* [IBM] or DOS 2.1 [IBM]

#### Database/file managers:

*Pfs File/Report.* Easy for the novice to use. Suitable for simple filing, reporting, and retrieval applications. [Software Publishing Corp., 1901 Landings Drive, Mountain View, CA 94043].

*TIM IV.* A relational base with good report-writing features, and allows linked files. Rigid input protocol and limited number of fields/record. [Innovative Software, Inc., 9300 West 110th Street, Suite 380, Overland Park, KS 66210].

Data Base Manager II—The Integrator. Convenient means to move information between different application packages. Simple database, easy to use. [Alpha Software Corp., 30 B Street, Burlington, MA 01803].

*R:Base4000.* Powerful relational database system suitable for more complex applications. Good features. Not for the beginner. [Microrim, 1750 112th Avenue, N.E., Bellevue, WA 98004].

*ThinkTank—The Idea Processor.* Unique system for handling outlines, text, concepts, "todo" lists, and so on. Billed as an idea organizer.

Very handy for managers. [Living Video Text, Inc., 1000 Elwell Court, Suite 232, Palo Alto, CA 94303].

**Plotting:** Graphwriter\*\*. A powerful, yet easy to use, package for presentation—quality technical graphs. [Graphic Communications, Inc., 200 Fifth Avenue, Waltham, MA 02254].

**Statistics:** Statgraphics. A sophisticated and powerful statistical package; many features. [Statgraphics Inc., P.O. Box 1558, Princeton, NJ 08540].

**Project Management:** Harvard Project Manager. An excellent CPM planning tool for the PC. Works with monochrome graphics. Practical features. Easy to use. [Harvard Software Inc., 512 Great Road, Littleton, MA 01460].

**Spreadsheet:** Lotus123\*. Justly called "king of the mountain." Excellent spreadsheet, simple but useful database, fine graphics, very limited word processing. Outstanding features. [Lotus Development Corp., 161 First Street, Cambridge, MA 02142).

**Word Processing:** MultiMate\*. An excellent "Wang-clone" product with features usually found only in dedicated word processors. Well-received by secretaries and engineers. [MultiMate International Inc., 52 Oakland Avenue North, East Hartford, CT 06108]. Volkswriter and Volkswriter Deluxe. Not used by VCD. Simple to learn and use. Just what the name implies. [Lifetree Software, Inc., 411 Pacific Street, Suite 315, Monterey, CA 93940].

#### Communications

Local Area Network (LAN): Net/1. Links terminals, and so on, to common electronic data path. Couples to host via Hydra. [Ungermann-Bass, 2560 Mission College Boulevard, Santa Clara, CA 95050].

**Hydra:** Channel-attached protocol converter. Permits PC to look like 327X-class device to host. Supports other devices as well. [JDS Micro-Processing, 25 Mitchell Boulevard, Suite 7, San Rafael, CA 94903].

**Terminal Emulators:** ACOM\*. Used with Hydra. Full-screen 327X emulator with file-transfer capability. [Computer Vectors, Inc., 24871 Pylos Way, Mission Viejo, CA 92691].

**CMX:** Couples to 3274 terminal controller and allows daisy-chain cabling to various IBM devices. This saves cable length. [Ungermann-Bass, 2560 Mission College Boulevard, Santa Clara, CA 95050].

### Personal computers, an engineering productivity tool

The personal computer is a powerful productivity multiplier. As one manager said: "I never really wanted the PC, but now if anyone tries to take it away, I'll break their arm."

When the first personal computer (PC) was brought into the Video Component and Display Division (VCD) only a few years ago, it was a struggle; the authorization system was geared toward remote time sharing and centralized computing. The PC was a somewhat heretical approach to computing, deemed suitable for hobby applications but not for "real" computing. The PC allowed users to do their own computing directly-in an uncontrolled fashion. Where would it all lead if evervone could use a computer? Who would direct it? Wouldn't users just play games? Where is the economy of scale? These were just a few of the objections.

In a short time, personal computers have gone from "persona non grata" to the "engineer's best friend." What caused the transition and why has it occurred with such speed? The PC surge reflects the democ-

Abstract: The personal computer (PC) is a powerful tool for bringing computer power directly to the user. The Video Component and Display Division has made extensive use of the IBM PC as part of an overall engineering productivity strategy (see companion paper, by Miller, on VCAD). This paper describes the approach taken, some of the thinking behind the hardware/software choices (risks and mistakes), system integration, training, and results of an early productivity measurement.

©1984 RCA Corporation Final manuscript received March 22, 1984 Reprint RE-29-3-2 ratization of computing. Plummeting PC costs and explosive varieties of PC software have made it irresistible. Daily ads in the local papers and on TV have extolled the virtues of the PC. Amidst the "hoopla" one can find a large kernel of truth: computers can be used by non-experts.

Well-thought-out software is the key to PC usage. Unlike historical computer users, the PC user views the computer merely as an optional tool to do his real job more effectively. If it is easy, well and good; if not, it won't be used. In fact, the marketplace has generated an amazing range of software directly aimed at the nonprofessional user-these are tools to solve problems. A dynamic cottage industry has been spawned. No longer does the user require the time and skill to craft his own tools. Just as the do-it-yourself carpenter does tasks formerly done by the professional, so now the PC user picks off-the-shelf software to do his work.

The Apple personal computer, with its cost, features, and software, was the trigger to this market avalanche. The now-famous VisiCalc (VisiCorp) spreadsheet was the professional's eye-opener—it provided a generic solution to a wide class of important problems and attracted users exponentially. VisiCalc on the Apple was chic. IBM's later entry into the market put the seal of approval on PCs and, through a strong marketing strategy, rapidly rose to a dominant position. Writers of PC software adopted the IBM PC with its open architecture as the machine of preference and gave it the position of a de facto standard.

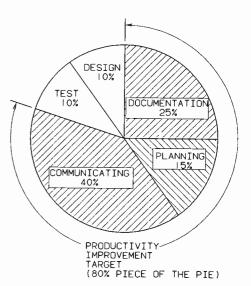

On the average, the professional spends

the bulk of his time communicating, documenting, and planning—as opposed to designing or testing—yet these "administrative" tasks traditionally have the weakest level of support (Fig. 1). In the VCAD approach, we targeted the PC usage directly at the administrative functions (including minor calculations) as opposed to the computer-intensive tasks.

**Fig. 1.** Pie chart breaking out the typical engineer's time profile, based upon data from Hewlett-Packard. Traditional computer support focuses on the test/design segment. The bulk of the engineer's time is spent upon tasks that can benefit from computer assistance, but this is not widely provided. VCAD seeks to service the entire pie through a rounded set of tools.

#### Approach

The VCAD project recognized the PC as a key part of its overall productivity strategy. It provided a means to distribute useful computing power directly to the engineering community, flexibility in selecting software, and the potential to be used in a dual mode—local or terminal. It was clear from the outset that the PC was the means to reach a broad class of users and change their work habits. The PC was not viewed as some sort of super-design workstation for the elite engineer.

The next decision was which vendor and what product? From a hardware perspective, there were many suitable choices and complex tradeoffs to consider. But from the software side, the answer was clear: we chose the IBM PC/XT (the XT is a PC with a Winchester disk) as the standard. While remaining alert to the turmoil in the operating system area, PC-DOS was adopted as the standard operating system. We wanted to avoid the problems that accompany multivendor installations and resisted the temptation to select several PC vendors, each offering some purported advantage. In the VCD engineer ing environment, standardization offered significant advantages over specialization and proliferation.

Standardization is a risky tactic in a volatile market environment; it is easy to pick an Edsel. The VCAD design concept does not depend upon the PC being an IBM one. So far, the choice has stood the test of time although we are constantly on the alert for other trends. There are over one hundred manufacturers of PCs and literally thousands of software offerings. The risk of making a mistake is high. We also learned that there are many subtle errors one can make in meshing PC software to specific hardware configurations. Because the field is relatively new and highly fragmented, it is much more difficult to make good decisions about PCs than about the nominally more complex mainframe options.

Within this conceptual framework, a standard configuration was devised for the PC and the XT. The engineering standard PC/XT was a 256K machine with a monochrome monitor and Okidata 93 printer. A variant configuration was adopted for the secretarial user (different printer). For purposes of investigation, some machines were acquired with minor variations: color monitors, Hercules Graphics cards, more memory, math co-processor, pen plotters, and so on, but these represented variations on a theme rather than radical changes. Each PC/XT was also configured to be attached to the local area network (LAN) so that it could communicate with other devices and computers.

An intuitive judgment was made on the ratio of PCs to XTs, balancing the following factors: cost, ease of use, number of users of the machine, and user sophistication. The XT was felt to be suitable for the more experienced user, the person who could make intelligent use of the larger hard-disk capacity, or the person who had an identified application requiring the disk. The XT user also tended to be someone who would not be sharing the machine with other users. Limited disk-security features made it too easy for someone to inadvertently ruin the disk's contents in a shared environment. The PC was a good entry-level machine. We bought 73 machines in 1983, with PCs to XTs in a 4:1 ratio. All secretarial machines were PCs.

Although there is considerable enthusiasm for the PC as an engineering tool, it is not a cure-all. Many other kinds of PCs and workstations on the market offer more computing power, specialized analytic software, and so on. As the need for higher "horsepower" arises, these terminals can be attached to the LAN without change to the system. For example, experiments with the PC as a laboratory instrumentation computer have shown it to be insufficient for some of the more computation-intensive tasks. In such applications, a 16-bit machine with a faster processor is required. Also, we would characterize the standard configuration as having a weak graphics capability; this can be improved by several relatively minor changes or by use of the host

The broad dilemma was whether to wait for things to settle down and make a safer choice, or to proceed in the face of certain change. We have opted for the latter in the belief that the overall system architecture is sufficiently robust. Downstream, we will acquire PC-type machines with increasing capabilities.

#### Software

Adopting reasonable hardware standards early in the project made it possible to investigate software from a more systematic viewpoint. It was assumed that the primary application for the PC was in simple applications with a high administrative flavor as opposed to computer-intensive or graphics tasks. Early in the process, word processing and spreadsheets were identified as the basic software areas, in addition

**Fig. 2.** The PC connection. The personal computer is attached to the local area network, which in turn is coupled to the host via the Hydra protocol converter. ACOM software in the PC and host cause the PC to be presented to the IBM 4341 as a full-screen 327X-class device with full-function key support. ACOM also supports two-way file transfer. When in the terminal mode, the PC is driven at 9600 baud. Upon request, the PC can be linked to other devices on the LAN, or of course operate in a stand-alone mode.

to ancillary areas such as database managers, statistics, graphics, project planning, and so on. At all times we tried to balance the tradeoff between doing tasks on the VCAD host versus the PC. This is indeed a delicate balance—on the one hand, putting too little on the PC emasculates the original purpose, on the other, each PC tends to become a miniature computer center.

#### Word processing (WP)

Perhaps no area has as many choices and different user opinions as word processing. No one seems to agree on the ideal set of features. In fact there is no one best WP, but a surprising array of specialized offerings, each with strong and weak features. Volkswriter (Lifetree) was selected at the beginning of the VCAD effort (based upon simplicity and ease of learning). Before purchasing it we learned of MultiMate (SoftWord Systems Inc.) and made a decision to change direction. MultiMate, a WP based upon the popular Wang dedicated-

WP system, has an extensive set of features, is well supported by the vendor, and approximates the features of a dedicated WP. From a psychological point of view, it was attractive because there were several Wang WPs already in use in the Division; MIS was asked to concur in the recommendation and they did so. Engineering secretaries who had been trained on the Wang, now prefer the PC with MultiMate.

#### Spreadsheet

Here the decision was easy—Lotus123 (Lotus Development Corp.), perhaps the finest software written. Lotus123 builds on the excellent VisiCalc concept and adds extremely useful capabilities. Lotus123 offers excellent spreadsheet features, useful interactive graphics, modest database capabilities, and very limited word processing. Standard output interfaces make it possible to transfer information between MultiMate and Lotus123 (as well as other packages).

**Fig. 3.** Secretary using the PC and MultiMate for word processing. The general reaction of the secretaries has been highly favorable. Some secretaries are also using packages such as Lotus123 for spreadsheet work. A turnkey Lotus123 template was created to fully automate the business expense report from input to final form ready for signature. Such techniques are improving efficiency.

#### Communications

We made a mistake in this area, initially selecting the IBM 3101 emulator to link the PC to the LAN. After acquiring it, certain deficiencies were found in the software that caused us to look for another solution. Fortunately, the ACOM emulator (Computer Vectors) was found; it supports file transfer as well as PC-3278 emulation.

MultiMate, ACOM, and Lotus123 were installed on virtually all of the PCs acquired. They became the basic software building blocks. It has been a gratifying process to watch users develop their own applications with these tools. Many tasks that would never have reached the level of approval on an MIS Data Processing Request were now being solved quickly and imaginatively, following only a few hours of instruction, often by users with no computer background.

#### PROFS

Although the IBM Professional Office System (PROFS) is not a PC application, each PC owner is coupled to PROFS via the LAN. From a software point of view, it is a package directly available to each user. PROFS serves as the electronic mail link between VCAD users. Using the ACOM emulator, files can be transferred between host and PC; this allows a letter to be composed in MultiMate, sent to another user via PROFS, and so on. Of course the full spectrum of PROFS features are available to each PC user.

A number of packages (database managers, project planning, graphics plotting, statistics) have been reviewed. This is an ongoing effort of the VCAD task force; new software is periodically acquired and studied to determine its utility. Formal reports are generated to document the review. In general, these offerings are specialized and of interest to only a portion of the PC community. Perhaps a dozen different packages are in use within the VCAD community. Authority to purchase PC hardware and software is focussed within engineering to minimize proliferation and encourage synergy among users.

#### Training

Several decisions were key to the PC installation process. Every person assigned to PC had to agree to take training prior to receiving the machine. Secondly, a "PC College" was established as a forum for training. The PC college was not a highly structured school. Students were asked to devote adequate hours to learning DOS, typing skills, and Lotus123 using programmed tutors and selected problems. This combined self-study with hands-on use of a PC and short lectures. MultiMate was

#### Typical comments on the PC investment

6 6 ... Having had little previous exposure to computers, I was slow getting started but I see more and more applications as time goes on. I was not anxious to get the unit, but will now break the arm of anyone who tries to take it away! Every phase of my work has been improved by the use of my PC. Clearer memos, better project planning, and more indepth analysis and documentation of experimental results ...

... The PC is an amazing and powerful tool. The ability to revise documents in MultiMate and have new copy within minutes has been a tremendous time saver ... The system provides an easy access file so that all of the information I need is at my fingertips without going through a lot of paper work ...

...It is easier and less intimidating to write reports using the word processor than using pencil and paper ... The most important application is largescale data manipulation for factory test ... I look forward to retiring my typewriter, supplementing my calculator for engineering calculations, and dispensing with hand tabulation of data and hand plotting on graph paper ...

... A returned Development Tube (DT) sample had a poor focus gun. By looking at a data comparison of all DTs shipped, three other "bad" tubes were found

that were not previously known. The ability to find interesting and important facts in large data fields has been too cumbersome to do in the past. This PC ability will improve this situation

... Lotus123 allows "after thoughts" to be quickly and easily inserted and rapid comparisons made with alternate input variables ... I am now able to keep abreast of time schedules on all important jobs ... The quality of work is improved particularly on design analysis. In cases where formerly features were calculated at a limited number of locations, those same features can be analyzed at an unlimited number of locations....

... We're now able to set up project tracking system for each engineer and designer. The PC will allow each individual to update their project as progress is made ... Project outlining, planning and manpower resources are now possible through worksheet analysis by sorting against projects, group leaders, and so on ...

taught to secretaries in a 4-hour session; others learned it by themselves. Some of the training was devoted to housekeeping tasks such as care of floppy disks, how to run the printer, and so on. Although the time required to train was insignificant, and it varied with the background of the student, it saved many mistakes in actual usage of the machines.

PC user groups have been established to provide a means to share results, tips, problems, and solutions. These user groups are now sustained by the newly-formed MIS Information Center and service the Division rather than just engineering. PROFS training was conducted on a more formal basis in March, using the standard IBM reference material supplemented by an introduction to CMS. During this training, the students also were introduced to ACOM, the means to link to the host and transfer files.

#### Measurement

In February, 1984, a productivity study was undertaken to measure the results of the PC investment. A detailed survey was taken of each PC user querying them about the utility of the machine (see sidebar). Some of the highlights of the study are:

- Almost uniform enthusiasm, good response to the standard software, and a significant increase in computer literacy.

- 73 machines installed. Productivity gains of 25 percent per machine hour after only 1.8 months, and average machine use of 4 hours per day, with 2.6 users/ machine. Faster problem solving. Lotus123 productivity gain 2.6:1, and MultiMate productivity gain 1.5:1.

- Better planning, communications, project tracking. Creation of simple but useful databases in all areas. A myriad of useful analyses reduced to routine.

#### Expansion

Based upon the favorable initial user reactions, we are in the process of defining the Phase II VCAD expansion in the PC area. The current plan is "to reward the rich," that is, to add additional resources preferentially to the groups that have made the best use of the first PCs. Our problem is slightly more complex the second time around as there are additional PC offerings to consider (XT/370, XT/3270, . . .), each of which has certain desirable features. In the laboratory measurement area, we are reviewing the IBM 9000 where higher performance is a requirement.

#### Acknowledgment

Special thanks are due to the enthusiastic engineering community who adopted the new approach while in the midst of major project responsibilities; M. Renfro and H. Hillegass who taught in the "PC College"; B. Mangolds for communications support; and T. Hart who formed the Information Center.

James C. Miller is the Manager of Technical Projects and Engineering Administration at VCD in Lancaster, Pa. (see biography, page 8). William Kelley joined the RCA/EC Microwave activity in 1950. He has held a variety of Manufacturing, Engineering, Program Management, Business Analysis, and Administrative positions during his RCA career. He is currently focusing on optimizing the use of personal computers and PROFS to help improve engineering productivity within VCD. Contact him at: Video Component and Display Division Lancaster, Pa.

TACNET: 227-6443

### CADAM, an engineering productivity tool

We are using CADAM, a computer-graphics system, as the key to upgrading our manual design methods into an integrated modern approach. CADAM is already increasing productivity and design quality at VCD, and changing the way engineers work.

The Video Component and Display Division had made modest use of graphical computer-aided-design tools. Several years ago, an Applicon design system had been acquired and installed in one engineering department. Though a good decision at the time, when viewed in hindsight, certain limitations may be discerned: deficiencies in reliability, number of terminals, ease of

Abstract: CADAM (CADAM Inc.) is the key part of a graphic design system used in the VCAD program. It is an assemblage of powerful computer hardware and software tools. These tools, although internally complex, allow managers, engineers, designers, and drafters to easily perform their normal design functions with greater speed and accuracy. This paper documents the CADAM system from concept to implementation. The rapid success of CADAM is seen by its early use in a broad range of design problems, its easy assimilation into the existing work environment, and the demand for more terminals. Our motivation with CADAM is single-minded: increased engineering productivity. With 2 weeks of training and 8 weeks of production usage, productivity has already reached 2:1 versus manual methods—our goal is 4:1 over the full span of user activity. The CADAM system will eventually be expanded to support approximately 50 terminals.

©1984 RCA Corporation Final manuscript received March 22, 1984 Reprint RE-29-3-3 training, access, and response time made it inappropriate to extend the system to a broader base. The system was primarily dedicated to specific aspects of electrical design. Eventually it evolved into a closedshop service in which dedicated operators did a mix of design, plotter operation, trouble shooting, backup, and programming. The operators were physically and organizationally separated from their parent design groups. As with any service center, work scheduling became an issue. Productivity gains were asserted but difficult to monitor routinely. The formal training program was weak, consisting of either do-ityourself work or a short course at the vendor.

#### Approach

As the VCAD program was planned, we sought a turnkey graphics design system approach that addressed these concerns and that led to an integrated solution. We envisioned a need for a large number of terminals, fast system-response time, a tight focus on productivity, a common database across all users, and a desire to access a wide set of software tools. A balance was sought between speed and advanced design abilities: it is all too easy to incorporate a feature that, while elegant, consumes exorbitant system resource and slows all other users. Because of the need for many terminals, the incremental cost-per-terminal was an important factor.

It was important to integrate the new approach into the existing organizational fabric; therefore, the new system had to be easy to learn, and not require its users to become computer specialists. The graphics system had to assist our communication flow; properly designed and integrated via a good database, it would reduce paper and eliminate duplicate manual steps. Of course, it had to help shorten the overall program design cycle. Different users need to operate the system appropriately; let designers draw and engineers think—not operate a CAD system. Reducing the number of times a part or product is drawn, easy access to current designs, increased quality level, and so on, were other concerns.

Overall, we concluded that a successful and productive solution required a solid host operating system, stable graphics software, and a formal training program. The system was to be imbedded in the existing work culture and organization, yet formed and guided by a standard overall outlook.

The Lockheed-developed Computer-Aided Design and Manufacturing (CADAM) software was selected as the heart of our graphic design approach. This is a comprehensive and stable set of programs that drives a graphics database. The system was augmented by acquiring CAEDS (SDRC Inc.) and ANSYS (Swanson Analysis) to support finite-element modeling as an adjunct to CADAM. These products offer a broad base of engineering tools to use in design from concept and analysis to the final machined part. One man was assigned to implement the system and assumed software, system, and training responsibilities. This is the first CADAM installation within RCA.

CADAM is a widely-used system ca-

pable of supporting large numbers of terminals (one installation has 600+). CADAM provides design and manufacturing advantages such as increased productivity, shorter design cycle, lower costs, better designs, greater accuracy, flexibility to make changes, and the opportunity to have more standardization of design. General Motors has reported 3.81:1 productivity gains via CADAM. Even higher ratios are achieved in specialized tasks. The CADAM system provides a high performance, broad function, design/drafting package together with a number of aids for analysis. It then moves onto completing the job by providing numerical control parts programming abilities. The central database is the system "glue," enhancing communications and reducing manual drawing-retrieval efforts.

#### Configuration

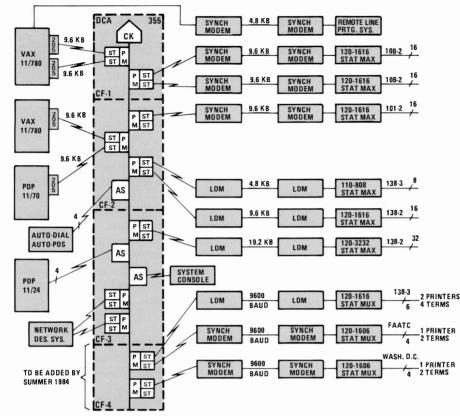

All CADAM hardware is attached to an IBM 4341 (Model 9) computer with 4 megabytes of memory and 2.4 billion bytes of disk storage. The current CADAM workstation consists of the IBM 3251 graphics terminal, which uses a program function keyboard, standard typewriter keyboard, and light pen, to control the program and enter data. Three of the 3251 workstations are attached to a single 3255 terminal controller stationed up to fifty feet away. The 3255 is attached via coaxial cable to a 3258 controller in the computer room; up to four 3255s can be attached to one 3258. The Phase I installation supports six 3251 terminals. The CADAM terminals are placed directly in the user work area rather than in segregated computer spaces. In a very real sense this configuration is a "starter-kit" to prove the concept.

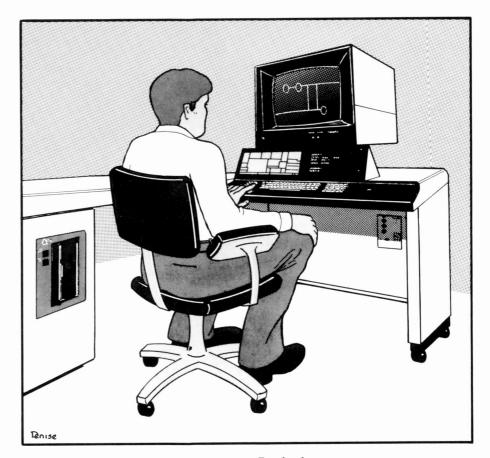

The designer sits at the terminal (Fig. 1) accessing work stored on the large disk in a special CADAM database. He can recall previous work and make changes, start afresh, initiate an analysis, compare drawings, and so on. Each user can access his own reserved portion of the database or, with system authorization, view and copy

designs stored in other work areas. All of the normal graphical commands are supported. The terminal works in a menudriven mode that makes it easier to learn and that always coaches the user as to the next set of steps available. For practical purposes, the size of the database is limitless--all active work is kept on-line. Data is stored in a so-called "21/2D" CADAM database. Every ten interactions the full working drawing is backed up by the system, preventing loss in the event of a crash. Each user designs with a 5K-size working model to instill good practices and avoid waste of resource. Files are protected by a multilevel password scheme and are grouped into sets based upon organizational requirements.

The workhorse of the hardcopy facility is a 36-inch-wide Versatec plotter. The plotter uses an electrostatic process to place elements on the paper or film with a resolution of 200 dots/inch. Through a channel-attached controller, it can produce typical E-size plots in ninety seconds or less. Generally, a plot is completely finished by the time the requester has walked to the plotter. This process saves time formerly lost while searching for a drawing in the manual files. The Versatec Random Element controller and software are used to produce plots with radii that look truly round. Plot quality generally exceeds that of manually drawn tracings.

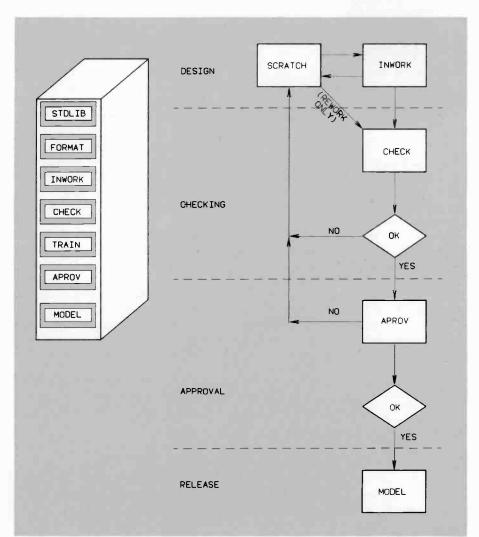

The CADAM database structure is shown in a simplified form in Fig. 2. In our implementation, we have opened the base to most of the CADAM user community to facilitate sharing of work. Elaborate security provisions may be appended as desired.

For tactical reasons an interim approach was chosen for remote graphics in Phase I of VCAD; IBM FASTDRAFT systems were installed in Marion and Scranton. FASTDRAFT is an interactive, two-dimensional, isometric system for computer-aided drafting. It uses the IBM 3251 terminal with a light pen and typewriter keyboard. The program runs on a stand-alone 7361 graphics processing unit. Output is produced on an E-size drum plotter with up to eight colors. Unfortunately, FAST-DRAFT is not directly compatible with CADAM; this complicates efforts to link Lancaster with the manufacturing sites. In

**Fig. 1.** Designer working at CADAM terminal. The workstation consists of the IBM 3251 graphic display, light pen, function keyboard, and conventional keyboard. The system provides a 0.3-second response to most requests. The 3251 operates in a mode that shows the menu at the bottom of the screen and the required response options for a selection at the top. The VCAD visor is part of the VCAD training publicity effort.

the short run, software links between CADAM and FASTDRAFT via IGES (a graphics interchange facility) are being investigated, but a longer-range solution may be satellite CADAM stations.

#### Software

The turnkey CADAM software has the ability to set various performance parameters and options that are installation dependent. The primary workhorse is the graphics design package CADAM (release 19.1). CADAM is an interactive graphics system for computer-aided design, developed by Lockheed Corporation for over 15 years. CADAM is divided into modules and we are currently running the following: CAD/CAM, Data Management, Hardcopy, Statistical Data, Accounting, 3-D Surface, Geometry Interface, CADGRAM, CADEX, and 3-D Mesh Geometry. CADAM was installed without incident and has proven to be very stable.

CADAM is a complex piece of software that can be tuned in a myriad of ways internally and with respect to the VM/CMS host operating system. This is a complex process and must be done carefully to properly balance the system resources. The users are not involved in tuning, database management, or backup-they concentrate on their work. In our view, system tuning in an engineering environment is sufficiently subtle and dynamic as to require local skills. In the VCAD system, priorities have been arranged such that CADAM is the most important task on the system. Each CADAM user normally sees system response to a light pen "hit" within 0.3 seconds. This extremely rapid response time-even with a large number of terminals and considerable background work-is the key to productivity. A skilled operator can stack up commands even at this fast rate. The machine does not normally limit the thinking process.

CAEDS and ANSYS are used in combination for finite-element modeling. CAEDS is an integrated program that addresses the functions and applications of mechanical product development. CAEDS emphasizes the use of analytical modeling and analysis of a design in the conceptual phase. It interfaces with the CADAM database and will extract 3-D data from a model for mesh generation. Our configuration uses the modules FRAME and

**Fig. 2.** CADAM database structure. A design is initiated and stored in the user's work space. When complete, it is advanced through several levels for checking and approval. The user work space is deliberately kept small to force passing work on for approval and release. Each level in the hierarchy blocks the subordinate users from making changes. Final released drawings cannot be altered by any of the users; but they can be copied and used as the basis for starting a new design. While signed file copies are maintained for archival and legal purposes, the "real" design rests in the CADAM database. All drawings are maintained on-line and can be accessed in a matter of seconds by any authorized CADAM user. This facilitates sharing and reduces redundant effort.

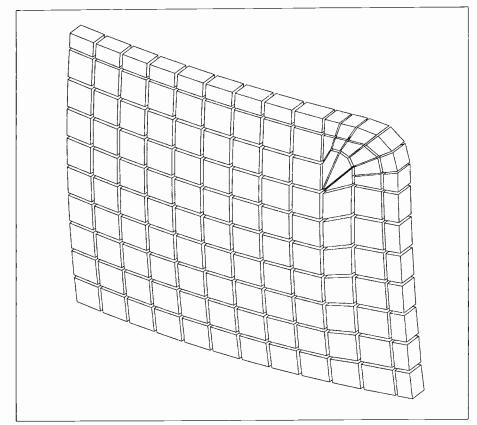

GRAPHICS and then interfaces to the nonlinear solver of ANSYS to analyze the model. ANSYS is a large-scale, generalpurpose program for the solution of engineering analyses. Figure 3 shows a typical ANSYS output generated on the Versatec plotter.

The combination of the two products, along with CADAM, provides a powerful tool to build analytic models interactively and solve them for any conditions that we presently encounter.

#### Training

Training is an extremely important aspect of the entire operation. It is an investment in future results yielding return as increased output at a higher quality level. Extensive training is needed to fully use the options available—this not only applies to the everyday users but most importantly to the managers who will have control over the jobs on the terminal.

We have followed a top-down training philosophy in order to imbed CADAM

into the working culture as quickly as possible. The first CADAM trainee was Mr. C.A. Quinn, the Division Vice-President and General Manager. All managers in the command chain between him and the ultimate user were trained prior to training the user. The benefits of this approach cannot be overestimated. Excellent standardized training is available at the vendor but we opted for a local approach. One of the authors (P.J.K.) took specialized training at the vendor's site prior to installation of the equipment; he then served as the local trainer. This technique allows the training to be conducted in a fashion that best matches the norms and work system of the location with minimum disruption to the normal job assignments, and has proven to be extremely effective.

A broad range of courses are presented: CADAM BASIC, On-the-Job Training, BASIC II, BASIC NC, Advanced NC, FEM, ANSYS, 3-D Surface. The basic course includes 40 hours of terminal time and a second 40 hours of on-the-job training doing productive work. Thirty-two people have been trained in 2.5 months, representing over 2000 hours of class time. All have finished the courses and are at least 1:1 with manual techniques at the end of training. Refresher courses are held to maintain skill levels or review new system features. Demonstrations are given to acquaint untrained persons with the CADAM potential. Close follow-up is maintained with each user to review performance and skill level. All graduates of training receive cer-

**Fig. 3.** Typical ANSYS plot. Finite-element models can be created directly through ANSYS procedures (the slowest method) or through the CAEDS/CADAM techniques starting with a CADAM drawing. VCAD offers good turnaround and excellent plotting through the Versatec graphic plotter. A drawing takes 45 seconds to generate from the ANSYS output run.

tificates; buttons, hats, and so on, are issued to gain attention.

#### Measurement

A major effort was invested to establish an effective productivity measurement scheme. At a very early date, benchmark data and work statements were received from the managers of the groups that were targeted to receive CADAM. Benchmark data was also received from the Scranton and Marion plants before using FASTDRAFT. It was not simple to obtain meaningful data and a certain element of subjectivity was involved. Each group is being monitored against their individual measurement standards.

The CADAM system has been well received and is meeting our expectations. Evidence of this is seen in the progression of events. Prior to receiving the system, the managers did not believe 1:1 productivity would be reached for eight to twelve months. After they were trained, their figure was revised to six months, and currently, after 8 weeks of production use, the same managers will affirm that the operators are at a level of 2:1 productivity or better. A further sign of acceptance appeared in February, when terminal utilization jumped to better than 90 percent during normal working hours. By March, we were experiencing 90 percent usage over a 12-hour day plus some weekend time. One engineer, after only 3 weeks of production experience, solved a knotty design problem with CADAM and avoided an estimated \$100K loss that would otherwise have occurred with a manual design. That single effort "paid" for the CPU.

Our goal is to move up the productivity curve to a level of 4:1 or better. Managerial attention is focused on this factor. Over the period ahead, the productivity monitoring effort will be automated in order to highlight performance and possible retraining needs.

We have reached a point where new training has essentially stopped because each person cannot schedule adequate terminal time. New designs and some rework are being done on the system, which is currently being used primarily for mechanical, as opposed to electrical, design. Users have embraced the new technique and voiced no desire to return to the older ways. It is too early to determine the number of draw-

ing boards replaced by a terminal.

The system has been available for use around the clock since December 7, 1983. The host 4341 runs unattended and has been solid (one unscheduled IPL since November) since installation. This type of performance is crucial to a centralized system. During the first 45 days of operation (6 terminals, 10-hour CADAM day), we logged 1688 production terminal hours from an available 2700 hours (62 percent usage), and lost 21 terminal hours to an in-plant power failure.

Regular CADAM Users Group meetings have resulted in excellent feedback. All trained personnel have agreed that the system is stable, fast, and easy to learn. They are beginning to develop their own techniques to improve their new-found skill. Several user areas have developed new ways to perform their design problems including applications where they had previously been unable to get satisfactory answers. The Drafting Standards Committee has started to integrate CADAM into the work standards.

#### Expansion

The enthusiastic reaction to CADAM and its auxiliary tools has justified an early expansion of the system. By midyear, the host computer will have been upgraded and a dozen additional CADAM terminals will be arriving. The present projection calls for an ultimate need for more than fifty CADAM terminals and will require further expansion.

The new CADAM terminals will be of the IBM 5080 family, featuring color, raster refresh, and tablet input. The 5080 architecture has one controller per terminal, allowing them to be sited individually as desired. In future CADAM releases, more function will be downloaded to the 5080 terminal, thus allowing more terminals per unit of CPU resource.

At the same time, we are broadening our scope to consider the extension of CADAM into numerical controlled machining. A numerical control task force has been established to do the preliminary planning, and experiments are being conducted with the existing CADAM numerical control modules to determine its viability. Links have been established between VCAD and the existing NC equipment at Lancaster. We had acquired CADGRAM and CADEX, two electrical-design-oriented CADAM modules as a part of Phase I. As the new terminals arrive, these will allow us to extend the scope of CADAM into the electrical design area. CADAM is also being studied as a mechanism to put our Engineering Standards on-line for the technical community; it would be accessed by relatively inexpensive 3179 color terminals using CADVUE. The list of potential improvements is greater than our capacity to address them.

#### Acknowledgment

Sincere thanks to K. Walker for his contributions in the system area.

James C. Miller is the Manager of Technical Projects and Engineering Administration at VCD in Lancaster, Pa. (see biography, page 8).

Peter Kunz received the BSME with a minor in Materials Science from the University of Connecticut in 1979. He joined RCA in 1979 and his initial work centered on machine design of production equipment for the electron gun, including cathode problems and the quick-heat bimetal cathode process. He received his first patent in 1983 and has several patents pending. In 1983, Mr. Kunz was promoted to Member Technical Staff and joined the VCAD project. In his current capacity, he is responsible for implementation and support of the CADAM computer-aided design system including training, database management, finite-element modeling, productivity measurement, and systems support.

Contact him at: Video Component and Display Division Lancaster, Pa. TACNET: 227-6492

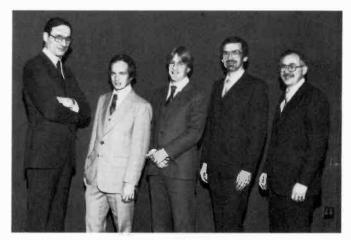

Authors Miller (left) and Kunz.

### Emerging engineering design tools

Future workstations will allow flexibility, integration, ease of use, and prospects for creating proprietary sets of design tools. The tools will paradoxically and powerfully integrate broad individual design freedom within highly organized and synergistic group efforts.

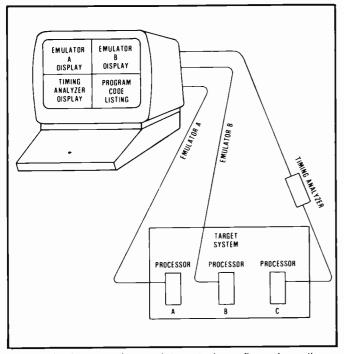

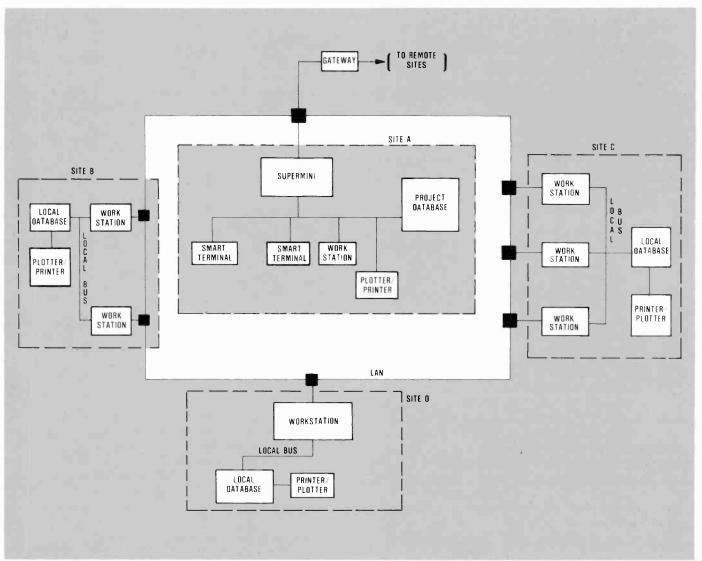

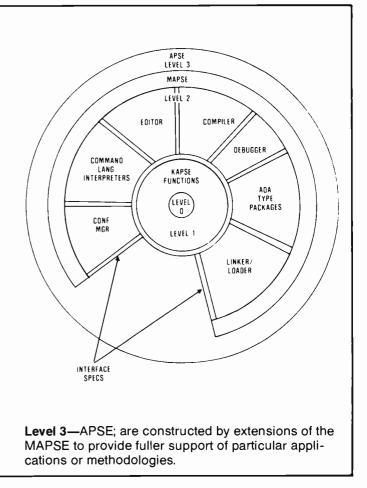

During this decade and into the 1990s the design of embedded microcomputer systems will require a new set of design tools. The design environment for the logic and system (hardware and software) engineers will consist of highly intelligent design/development workstations containing highly integrated automated software tools on one hand and an automated software-support environment residing on a superminicomputer on the other. Both these subsystems will be linked together onto a network and will share an adaptive design database management system that will behave as the central data-monitoring and control facility for the multi-engineer team. This design system will increase productivity, shorten the design cycle, and will allow management to better monitor and control the design cycle. Creativity and innovative use of these automated design tools by the design team will ensure a competitive edge in the marketplace.

In pursuing research on what type of tools an engineer will need and use in the future, an interesting cause-effect relationship was discovered. Today, most engineers are team players, relying on each other to perform project-related tasks in taking a product from concept to completion. The size of most engineering-related undertakings dictates that an engineer interface and work in cooperation with an integrated design team. However, in past

**Abstract:** This article addresses today's engineering design problems and how they may be solved using technology together with recent and future software applications. Aspects of managing design projects in present and future environments will be covered, including system tools, IC design tools, PC-board design tools and hardware/software integration tools. The distributed database environment is a key to achieving teamwork within a highly individualized working environment. Other aspects of future systems will be artificial intelligence, rigorous project management tools, superminicomputers, and powerful user interfaces.

©1984 RCA Corporation

Final manuscript received March 29, 1984. Reprint RE-29-3-4

Melendez: Emerging engineering design tools

years engineering as a profession was thought of as an individual pursuit that demanded creativity and a working knowledge of most all of the engineering disciplines. If the recent and continuing evolution to low-cost memory becomes married to the emerging revolution on artificial intelligence, the engineer may move from a team player environment back to an individual, less specialized way of working.

It is important for the reader to realize that the projections of what future engineering tools for the engineering profession will be is an opinion of the author and not a stated policy of RCA. In Burlington, Massachusetts, RCA Automated Systems has been and continues to pursue many of the areas discussed in this article. For example, Automated Systems has under development an artificial intelligence program for microprocessorbased test systems, a plant-wide local area network (LAN) for development activities that is married to today's most advanced engineering tools. Many of the projections made in this article reflect the baseline Automated Systems has established in its drive to provide engineers with the best available engineering tools that will meet not only today's but tomorrow's technical challenges.

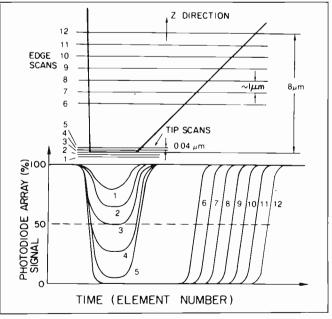

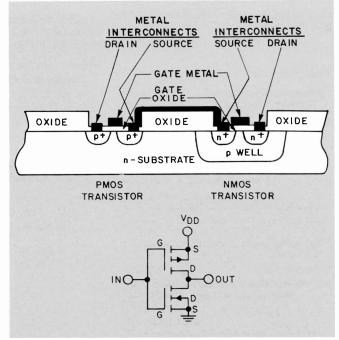

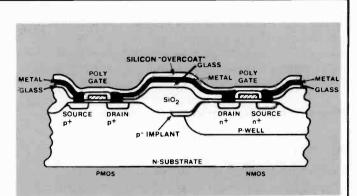

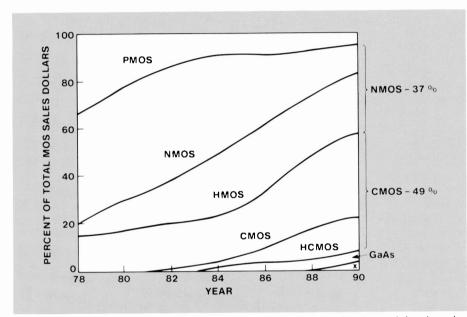

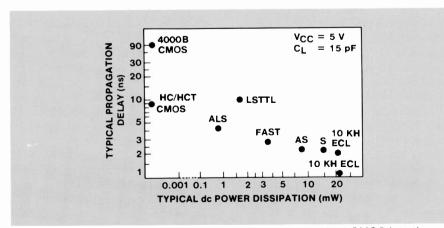

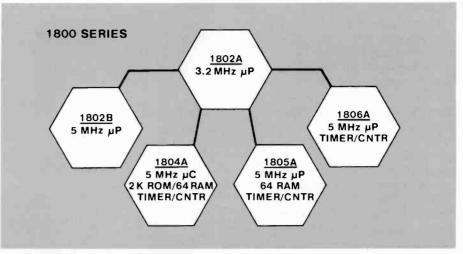

#### Managing design projects