## a technical journal

## RADIO AND ELECTRONICS RESEARCH • ENGINEERING

Published quarterly by RCA LABORATORIES in cooperation with all subsidiaries and divisions of

RADIO CORPORATION OF AMERICA

VOLUME XXIV

DECEMBER 1963

NUMBER 4

PAGE

## CONTENTS

| Foreword                                                                                                         | 471          |

|------------------------------------------------------------------------------------------------------------------|--------------|

| H. W. LEVERENZ                                                                                                   |              |

| The Etching of Germanium Substrates in Gaseous Hydrogen Chloride<br>J. A. AMICK, E. A. ROTH, AND H. GOSSENBERGER | 473          |

| Chemical Polishing of Silicon with Anhydrous Hydrogen Chloride<br>G. A. LANG AND T. STAVISII                     | 488          |

| The Growth of Germanium Epitaxial Layers by the Pyrolysis of<br>Germane                                          | 499          |

| Epitaxial Deposition of Silicon by Thermal Decomposition of Silane<br>S. R. BHOLA AND A. MAYER                   | 511          |

| Epitaxial Deposition of Silicon and Germanium Layers by Chloride<br>Reduction                                    | 523          |

| Vapor-Phase Synthesis and Epitaxial Growth of Gallium Arsenide<br>N. GOLDSMITH AND W. OSHINSKY                   | 546          |

| The Growth of Single-Crystal Gallium Arsenide Layers on Germa-<br>nium and Metallic SubstratesJ. A. AMICK        | 555          |

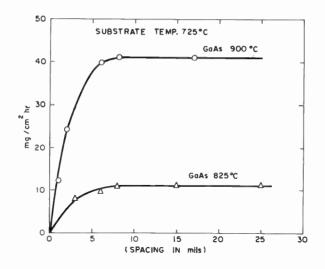

| Transport of Gallium Arsenide by a Close-Spaced Technique<br>P. H. ROBINSON                                      | 574          |

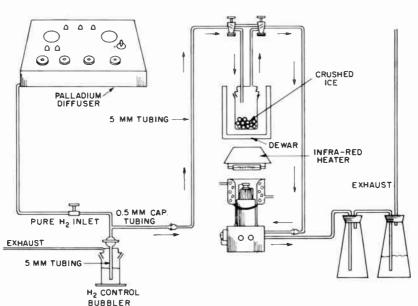

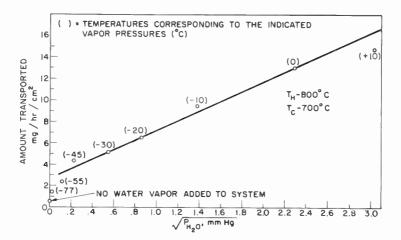

| Epitaxial Growth of GaAs Using Water Vapor<br>G. E. GOTTLIEB AND J. F. CORBOY                                    | 5 <b>8</b> 5 |

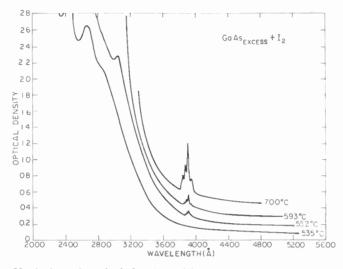

| Gas Phase Equilibria in the System GaAs-I <sub>2</sub><br>D. RICHMAN                                             | 596          |

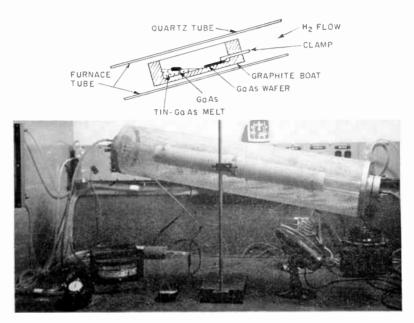

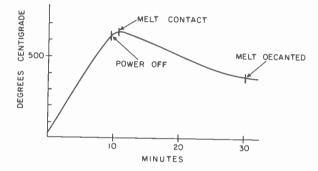

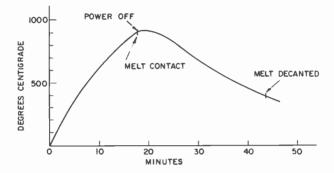

| Epitaxial Growth from the Liquid State and Its Application to the<br>Fabrication of Tunnel and Laser Diodes      | 603          |

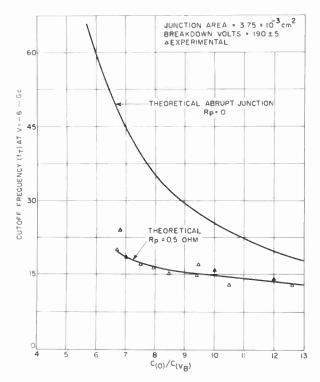

| lligh-Power Epitaxial Silicon Varactor Diodes<br>H. KRESSEL AND M. A. KLEIN                                      | 616          |

(continued on next page)

## CONTENTS (continued)

\*

ø

| ••••••••                                                                                                 |      |

|----------------------------------------------------------------------------------------------------------|------|

|                                                                                                          | PAGE |

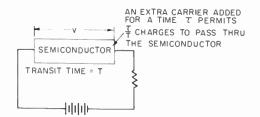

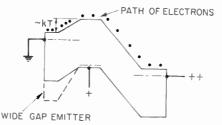

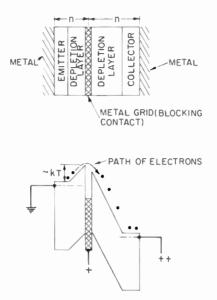

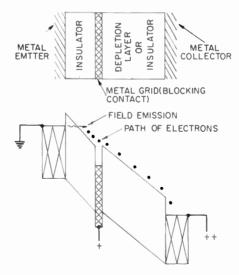

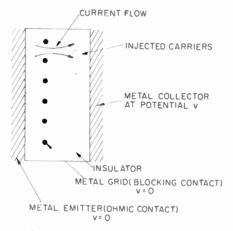

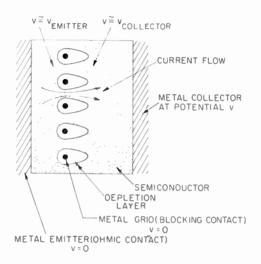

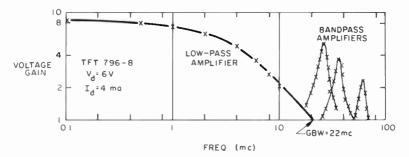

| An Analysis of the Gain-Bandwidth Limitations of Solid-State Triodes<br>A. ROSE                          | 627  |

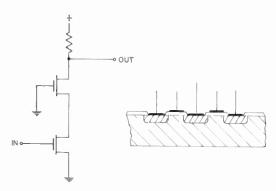

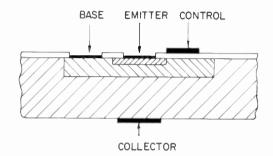

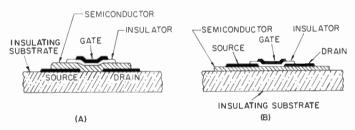

| The Field-Effect Transistor—A Review<br>J. T. WALLMARK                                                   | 641  |

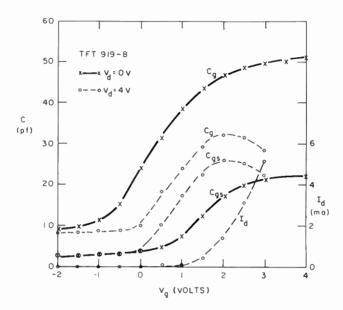

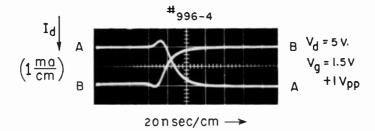

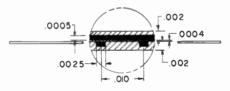

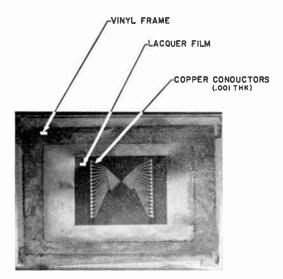

| Coplanar-Electrode Insulated-Gate Thin-Film Transistors<br>P. K. WEIMER, F. V. SHALLCROSS, AND H. BORKAN | 661  |

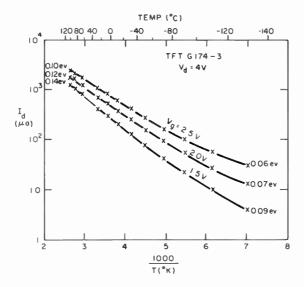

| Evaluation of Cadmium Selenide Films for Use in Thin-Film Tran-                                          |      |

| sistors                                                                                                  | 676  |

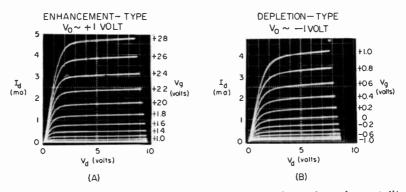

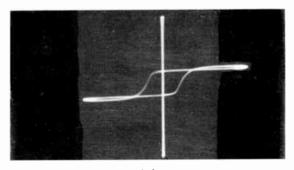

| Transfer Characteristics of Field-Effect Transistors<br>W. A. BÖSENBERG                                  | 688  |

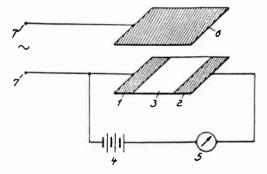

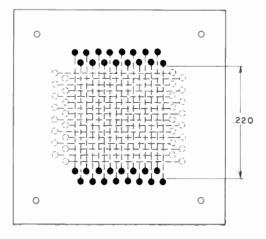

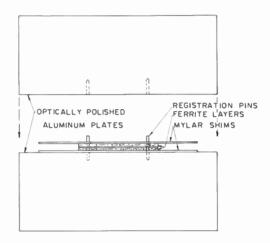

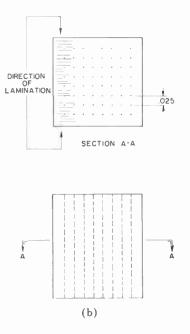

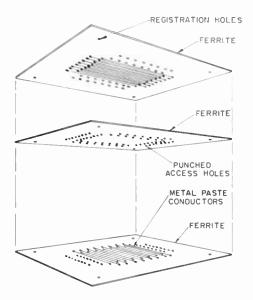

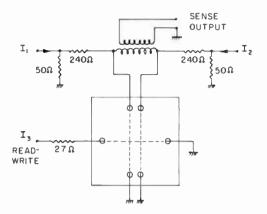

| Laminated Ferrite Memory<br>R. Shahbender, K. Li, C. Wentworth, S. Hotchkiss, and<br>J. A. Rajchman      | 705  |

| RCA TECHNICAL PAPERS                                                                                     | 730  |

| Authors                                                                                                  | 734  |

| INDEX, VOLUME XXIV (1963)                                                                                | 743  |

© 1963 by Radio Corporation of America All rights reserved

RCA REVIEW is regularly abstracted and indexed by Abstracts of Photographic Science and Engineering Literature, Applied Science and Technology Index, Bulletin Signalétique des Télécommunications, Chemical Abstracts, Electronic and Radio Engineer, Mathematical Reviews, and Science Abstracts (I.E.E.-Brit.).

## BOARD OF EDITORS

Chairman R. S. Holmes RCA Laboratories

E. I. ANDERSON Home Instruments Division

> A. A. BARCO RCA Laboratorics

G. L. BEERS Radio Corporation of America

G. H. BROWN Radio Corporation of America

A. L. CONRAD RCA Service Company

E. W. ENGSTROM Radio Corporation of America

D. H. EWING Radio Corporation of America

A. N. GOLDSMITH Honorary Vice President, RCA

> J. HILLIER RCA Laboratorics

E. C. HUGHES Electronic Components and Devices

E. A. LAPORT Radio Corporation of America H. W. LEVERENZ RCA Laboratories

G. F. MAEDEL RCA Institutes, Inc.

W. C. MORRISON Broadcast and Communications Products Division

> L. S. NERGAARD RCA Laboratories

H. F. Olson KCA Laboratories

J. A. RAJCHMAN RCA Laboratories

D. S. RAU RCA Communications, Inc.

D. F. SCHMIT Radio Corporation of America

L. A. SHOILIFF RCA International Division

> W. M. WEBSTER RCA Laboratorics

Secretary C. C. Foster RCA Laboratories

#### REPUBLICATION AND TRANSLATION

Original papers published herein may be referenced or abstracted without further authorization provided proper notation concerning authors and source is included. All rights of republication, including translation into foreign languages, are reserved by RCA Review. Requests for republication and translation privileges should be addressed to *The Manager*.

## FOREWORD

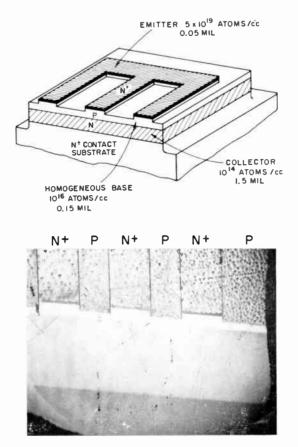

PITAXIAL GROWTH, a new and useful technique employed in preparing novel, intricate, and precisely controlled semiconductor devices, is the subject of the first twelve papers presented in this issue of RCA REVIEW.

The term "epitaxy," coined from the Greek roots epi = upon and taxis = arrangement, is used to describe crystal growth of a special kind: When atoms from a fluid phase condense on a crystalline substrate to form a crystalline layer whose *orientation* is controlled by the substrate, the layer is said to be "epitaxial."

Of the many techniques for achieving epitaxial growth, various methods for deposition from the vapor phase are the most popular, and some of these are described in the majority of the papers in this issue. This popularity can be ascribed to the relatively low temperatures at which epitaxial growth can be obtained from vapor-phase systems, and to a consequent improvement in the purity of the deposited layers.

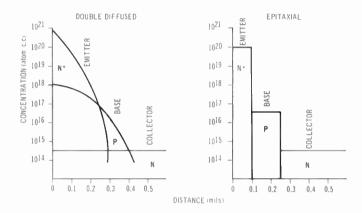

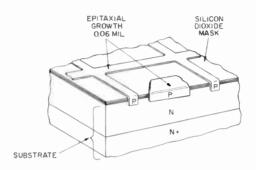

Epitaxy adds new dimensions of freedom in the design and fabrication of semiconductor devices. Epitaxial layers can be given desired electrical properties by introducing small amounts of doping agents during the growth. Hence, the relatively thin active volumes and interfaces of transistors and other solid-state devices can be custom made, with abrupt or graded changes in electronic properties and with controlled thicknesses, as required. Furthermore, large numbers of devices having uniform electrical characteristics can be made simultaneously using masking coupled with epitaxy. In many instances, epitaxial growth of one semiconductor on another can be achieved; with some semiconductors the composition, as well as the doping, of the growing layer can be altered during growth to permit the fabrication of new kinds of semiconductor crystals and junctions. The versatility and power of the epitaxial growth process is, perhaps, revealed to best advantage in the preparation of integrated circuits where many active and passive devices are formed and interconnected on the same small-area substrate.

This collection of papers signals more than the advent of new and useful epitaxial growth techniques. It demonstrates, in addition, the

December 1963

need for interdisciplinary effort in developing the techniques required for the fabrication of full-fledged integrated circuitry. Thus, the accomplishments described in this issue are a testimony to the fruitfulness of the coordinated teamwork of persons versed in several scientific disciplines—chemistry, metallurgy, physics, and electronics when directed toward a common objective.

> H. W. LEVERENZ Associate Director RCA Laboratories

Princeton, N. J.

## THE ETCHING OF GERMANIUM SUBSTRATES IN GASEOUS HYDROGEN CHLORIDE\*†

Вγ

J. A. AMICK, E. A. ROTH,\*\* AND H. GOSSENBERGER

RCA Laboratories, Princeton, N. J.

Summary—A technique for preparing chemically etched, mirror-smooth surfaces on (111) oriented germanium wafers is described. These surfaces, which are essentially structureless, appear to be ideal for use in epitaxial growth. The influence of etching gas composition, temperature and etching time on the etching rate are reported.

#### INTRODUCTION

HE substrate surface is of critical importance for the preparation of epitaxial deposits since this surface plays a major role in the nucleation process taking place during the initial stages of growth. Ideally, this surface should be free of major crystalline defects such as the work damage left by mechanical polishing. It should be free of chemical impurities such as oxide layers. It is also desirable that the surface be extremely flat, smooth, and structureless. The techniques used in preparing the substrate surface for epitaxial growth should be highly reproducible and should eliminate any contamination of the substrate caused, for instance, by exposing it to the atmosphere during the interval between etching and epitaxial growth.

It has been found that all of these requirements can be met for (111) oriented germanium substrates by etching them in flowing gaseous HCl at temperatures above  $800^{\circ}$ C in the same apparatus in

<sup>\*</sup> A portion of this paper was presented at a conference on Single Crystal Thin Films held at the Philco Scientific Laboratory, Bluebell, Pa., May 13-14, 1963, and will appear in the proceedings of this conference.

<sup>&</sup>lt;sup>†</sup> Note added in proof: A kinetic study of the HCl etching of germanium substrates was presented as a "Recent News Paper" at the semiconductor session of the Electrochemical Society Meeting, Sept. 29 to Oct. 3, 1963, by K. J. Miller and M. J. Grieco.

$<sup>^{\</sup>ast\ast}$  Presently a member of the Science Department, Ryder College, Trenton, N. J.

which growth is to take place.<sup>††</sup> The reaction is easily controlled, and thicknesses of 1 mil or more can be rapidly removed from the substrate leaving a bright, mirror smooth, structureless surface. HCl reacts with germanium oxide to form germanium chloride and water which are removed from the apparatus. Chlorine, the major impurity present on the etched germanium surface, causes no serious problem since epitaxial growth is often carried out by the reduction of chlorides.

Germanium (111) oriented wafers, prepared in this manner, have been used as substrates for the epitaxial growth of germanium<sup>3</sup> and of gallium arsenide.<sup>4</sup> The preparation of these layers is described in other papers.

#### APPARATUS

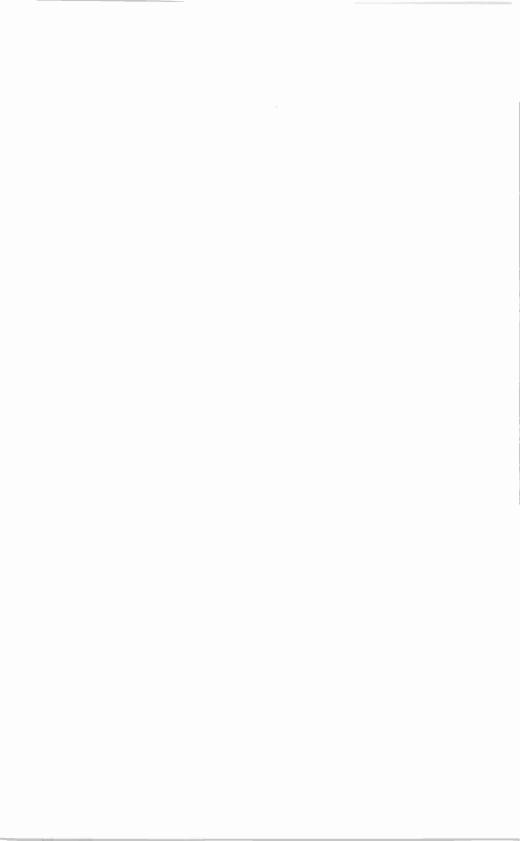

Two different types of apparatus have been used for etching germanium substrate wafers in gaseous HCl. In one of these the wafer is mounted on a susceptor block and heated by r-f induction,<sup>3</sup> the walls being kept relatively cool. In the other, the wafers are mounted on a quartz support rod and heated by a furnace surrounding the quartz etching chamber.<sup>4</sup> Results obtained with both types of apparatus are equivalent. Since the greater portion of the etching information was obtained with the first of these two systems, it will be described in more detail.

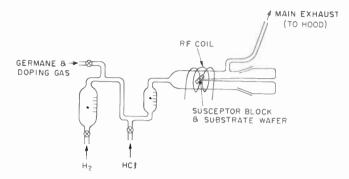

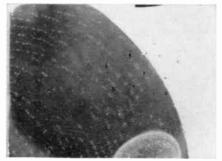

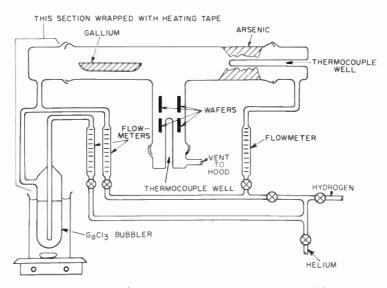

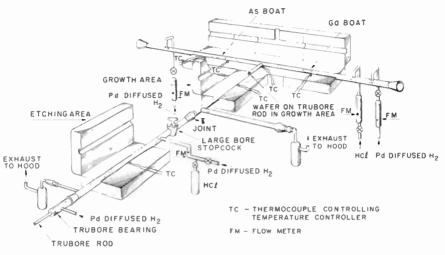

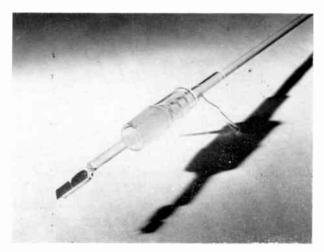

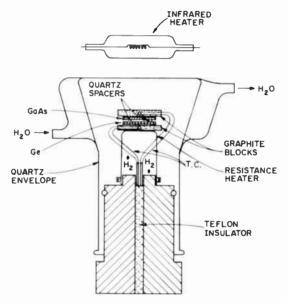

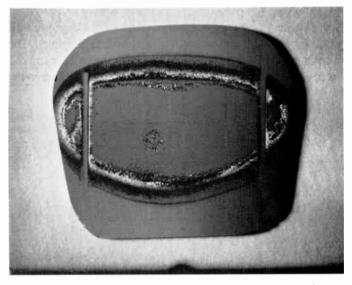

Figure 1 shows the apparatus in which the etching of germanium substrates was carried out prior to the growth of germanium layers.<sup>3</sup> The manner in which the germanium substrate and the susceptor block are mounted is seen in Figure 2. The etching chamber and the susceptor support are of quartz while the remainder of the system is Pyrex. Palladium-diffused hydrogen or tank helium are admitted to the system by way of a 1/4-20 flowmeter.<sup>\*</sup> HCl is introduced directly into the

<sup>2</sup> K. O. Seiler, U. S. Patent No. 2,744,000, May 1, 1956.

<sup>3</sup> E. A. Roth, H. Gossenberger, and J. A. Amick, "The Growth of Germanium Epitaxial Layers by the Pyrolysis of Germane," *RCA Review*, Vol. 24, p. 499, Sept. 1963.

<sup>&</sup>lt;sup>††</sup> Etching of germanium and silicon in HCl, chlorine and mixtures of these gases has been mentioned in several publications.<sup>1,2</sup> The nature of the surface so prepared and the conditions under which the etching is carried out have not previously been described, however.

<sup>&</sup>lt;sup>1</sup>G. W. Cullen, J. A. Amick and D. Gerlich, "The Stabilization of Germanium Surfaces by Ethylation," *Jour. Electrochem. Soc.*, Vol. 109, p. 124, Feb. 1962.

<sup>&</sup>lt;sup>4</sup> J. A. Amick, "The Growth of Single-Crystal Gallium Arsenide Layers on Germanium and Metallic Substrates," *RCA Review*, Vol. 24, p. 555, Sept. 1963.

<sup>\*</sup> Fischer and Porter Co., Hatboro, Pennsylvania.

Fig. 1—Diagram of apparatus for etching of Ge substrate wafers prior to epitaxial growth.

hydrogen stream from a lecture cylinder and monitored by passing the mixture through a second 1/4-20 flowmeter. In this manner the HCl present in the short link between the tank valve and the apparatus is rapidly removed from the system once the valve is shut off. Furthermore, the second flowmeter introduces turbulence into the gas stream which helps to ensure thorough mixing of the gases. The exhaust gases pass through a three-foot length of 1/2-inch outside diameter Pyrex tubing and are then burned in a hood. As etching proceeds, the smoothness of the surface can be followed visually through the optical flat sealed into one end of the etching chamber.

The temperature of the substrate is determined with an optical

Fig. 2—Close-up view of susceptor block, with mounted substrate wafer and quartz support rod.

pyrometer so placed that the hot substrate can be observed reflected in a mirror mounted in front of the optical flat. To provide a fixed reference point for the temperature measurement, the melting point of an old susceptor block was determined. The temperature read on the pyrometer was  $840^{\circ}$ C when the instrument was focussed on a molten area of the block. Since the accepted melting point of germanium is  $936^{\circ}$ C a temperature correction of  $96^{\circ}$  was added to each pyrometer reading.

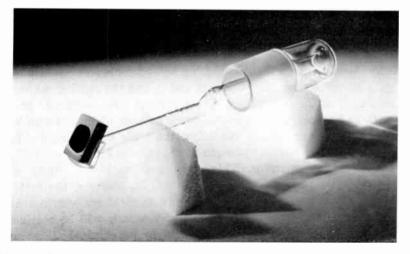

The etching zone of the second apparatus, that used for depositing gallium arsenide layers on germanium substrates,<sup>4</sup> is shown schemati-

Fig. 3-Diagram of HCl etching apparatus using external furnaces.

cally in Figure 3. The etching chamber and wafer support are constructed of quartz, and the gas-inlet system is similar in design to that of the first apparatus described above. Exhaust gases leave the system by way of a bubbler containing fluorocarbon oil.

It has been observed that the etching will be nonreproducible unless the walls of the system, the substrate wafer, and the etching reagents are extremely clean. The walls of the apparatus must be free of products such as hydrocarbon oils and stopcock greases which are attacked by the HCl. To ensure this condition, the walls of the system are normally flamed out with a hydrogen torch, prior to etching, while HCl flows through the apparatus. This step is not required if the system is used two or three times during one day. If, however, the system stands over a weekend, or if stopcock grease is accidentally introduced into the system, cloudy nonuniform surfaces usually will be obtained. Flaming the walls will return the system to its original state, and smooth structureless germanium surfaces will again be obtained following etching.

#### MATERIALS

The (111) germanium substrates used in this work were approximately 10 mils thick, and mechanically polished on one surface to an optical finish. Most of the etching experiments were carried out on  $p^+$  material gallium doped to about  $7 \times 10^{-4}$  ohm-cm, as these were to be employed subsequently in the epitaxial growth studies; p and n type wafers of both high and low doping concentration were also etched and their surfaces were found to be comparable to those of the etched  $p^+$  germanium substrates.

The germanium susceptor blocks (Figure 2) were prepared from intrinsic germanium according to a design suggested by N. Ciampa. A square bar of heavily doped germanium at the upper right of the block serves as an "igniter."

The hydrogen used in this work was obtained from standard tank hydrogen by passing it through a palladium diffusion apparatus.<sup>\*</sup> The purity of this reagent is higher than can be obtained by any other standard technique. The helium used in this work was taken directly from a standard cylinder. Since this reagent is used only for the initial displacement of air from the system and is not present during etching, it was not purified prior to use.

The hydrogen chloride was originally obtained from Matheson<sup>†</sup> lecture cylinders. No reduction valve was used and all connections were of Teflon or Pyrex except the cylinder valve which was Monel. Analyses have shown that this reagent contains impurities in variable amounts.<sup>5</sup> These were found to give nonreproducible results, especially when an exhausted cylinder was replaced with a fresh one. Recently, HCl has been obtained from the Stauffer Chemical Co.<sup>‡</sup> in much higher purity; infrared absorption analyses showed no detectable carbon dioxide and no acetylene.<sup>5</sup> This HCl has given consistently excellent surfaces.

#### PRECLEANING STEPS

Precleaning of the substrate wafer, susceptor block, and quartz support was found to be essential. It is especially important to remove any traces of the wax used to mount the germanium single-crystal boule during the slicing operation. If this wax is not removed, the surface

<sup>\*</sup> Engelhard Industries, Inc., Newark, New Jersey.

<sup>&</sup>lt;sup>†</sup> Matheson Co., Inc., East Rutherford, New Jersey.

<sup>&</sup>lt;sup>5</sup> G. A. Lang and T. Stavish, "Chemical Polishing of Silicon with Anhydrous HCl," RCA Review, Vol. 24, p. 488, Sept. 1963.

<sup>&</sup>lt;sup>‡</sup> Textile Chemical Co., Reading, Pa.

of the etched wafer will be hazy and nonuniform, and a carbonized residue of the wax will be present at the edge of the wafer. The wax used to mount the single-crystal boules was soluble in chlorinated hydrocarbons and could be removed by immersing a wafer in boiling trichloroethylene for a few minutes, then rinsing in fresh hot trichloroethylene. The germanium wafer was then washed in an aqueous detergent solution, rinsed in deionized water, then in absolute methanol and finally in carbon tetrachloride. Following the carbon tetrachloride rinse, the wafer was placed in a flowing stream of filtered tank helium and allowed to dry.<sup>†</sup>

The susceptor block, after use, was cleaned and made planar by grinding its surface against a plate glass flat using silicon carbide 305 abrasive.<sup>‡</sup> It was then washed in aqueous detergent, rinsed in deionized water, methanol and carbon tetrachloride and dried in filtered helium, as described for the substrate wafers.

The quartz support rod was cleaned either by heating it in a hydrogen-oxygen flame or, if necessary, by first etching it in a mixture of HF and hydrogen peroxide to remove any germanium deposit, then rinsing it in deionized water and finally heating it in a hydrogenoxygen flame.

Prior to beginning an etching or growth run, the standard taper joint was carefully cleaned with trichloroethylene to remove all traces of stopcock grease. The inner member (on the support rod) was then greased with silicone stopcock grease, the susceptor block and the substrate were mounted on the support, and the assembly was inserted into the apparatus. In this way, contact of the substrate and susceptor block with stopcock grease could be avoided during insertion of the assembly into the apparatus.

#### ETCHING OF THE SUBSTRATE WAFERS

The air initially present in the etching apparatus is first displaced by helium which, in turn, is displaced by hydrogen flowing at about 10.8 liters per minute. After a few minutes, the r-f generator is turned on and the susceptor block and substrate wafer brought up to the desired temperature, as determined with the pyrometer. Generally this temperature is about  $830^{\circ}$ C (corrected). A few minutes is allowed

<sup>&</sup>lt;sup>†</sup> This sequence is based partly on suggestions by W. Kern and was designed to minimize contaminants on the surface prior to beginning the HCl etching.

<sup>&</sup>lt;sup>‡</sup> Centriforce 305, American Optical Co.

for the block, the wafer, and the reaction zone to reach a thermal steady state.

To begin the etching, the HCl valve is opened and HCl is introduced into the system at a rate of about 2.2 liters per minute to give an etching gas composition of approximately 85% H<sub>2</sub>, 15% HCl. Etching is allowed to continue for as long as necessary to remove a desired amount of material from the substrate surface. Under these conditions, approximately 135 seconds of etching are needed to remove 1 mil from the substrate wafer. The HCl valve is then shut off and the etching gas is displaced by the pure hydrogen which continues to flow. After three to five minutes, the r-f generator is turned off if no deposition is to take place. Approximately 20 minutes is required for the block and the substrate wafer to cool to room temperature. The hydrogen is then displaced with helium and the block, wafer, and support rod are removed from the system. The standard taper joint is immediately cleaned to prepare the system for the next run.

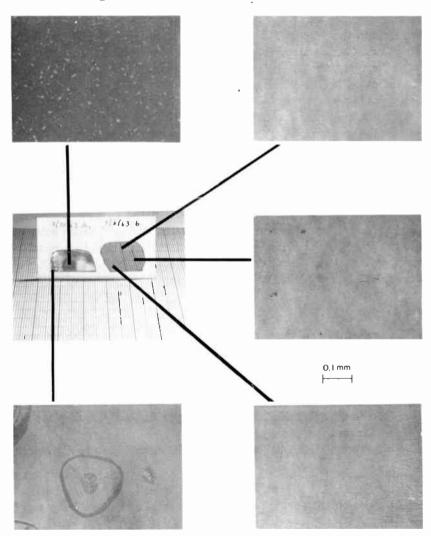

#### NATURE OF THE ETCHED SURFACES

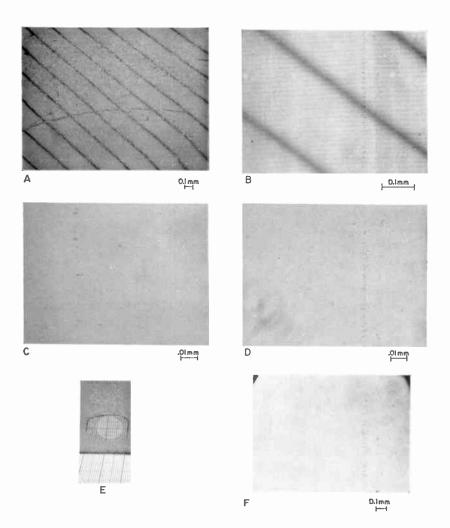

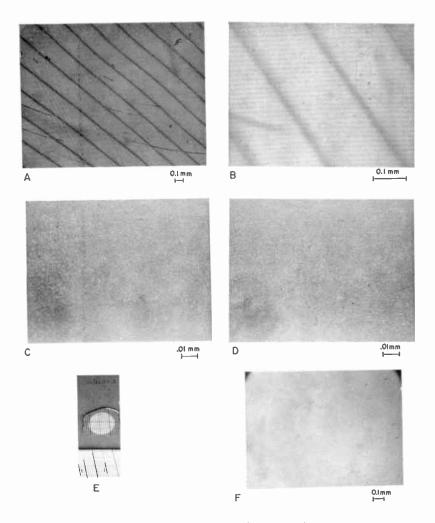

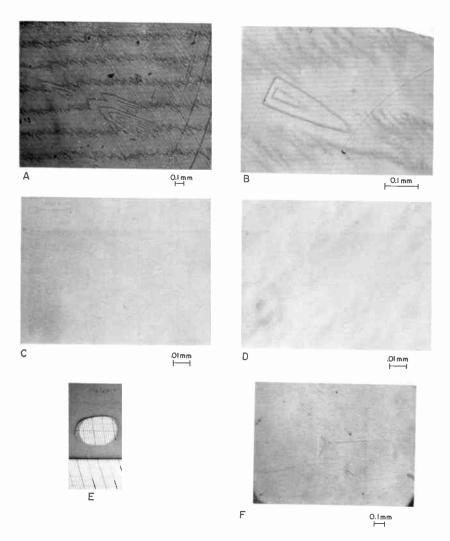

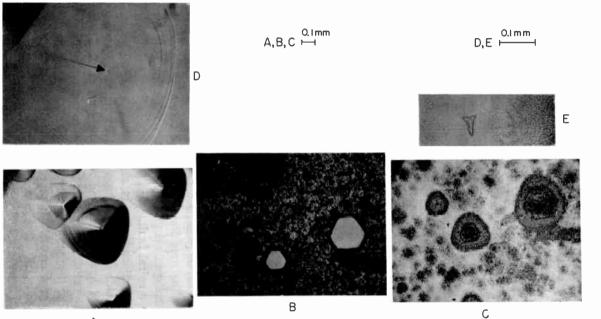

Two typical germanium wafers etched in this manner are shown in Figures 4 and 5. In each figure, a low-magnification photograph of the wafer is shown. Although it is difficult to convey an impression of the surface finish which is achieved with this etching technique, these photographs were taken with the wafers mounted on a piece of graph paper so that the mirror reflection of the graph paper in the substrate surface could be seen. The central bright area, which is actually circular, appears elliptical in the photograph. In this area a 1000 Å silver film has been deposited by evaporation so that the surface could be examined by the multiple-beam interference technique.<sup>6</sup>

Also included in each figure are five micrographs; at the top are the micrographs obtained by the multiple-beam interference technique. In the center are micrographs obtained on a Leitz metallograph using incident vertical illumination. To the left is a bright-field micrograph, to the right is a micrograph obtained under phase-contrast conditions, each at  $1000 \times$  magnification. For comparison, a bright-field micrograph obtained at  $65 \times$  magnification is included at the lower right.

From these micrographs it is seen that the surface is essentially structureless even at  $1000 \times$  magnification and is flat to within a few hundred Å over areas of about 1/10 inch on a side. Over larger areas, a gentle slope is observed in the interference fringes but no fine struc-

<sup>&</sup>lt;sup>6</sup> A. Tolansky, Surface Microtopography, Interscience (Wiley), New York, 1960.

Fig. 4—Micrographs of a mirror smooth Ge surface produced by etching in HCl: (A,B) multiple beam interference micrographs; (C,D) micrographs of surface (left—bright field, right—phase contrast); (F) 65 × bright-field micrograph; (E) photographs of graph paper reflected in wafer surface. wafer: 11/21/62-2, Ge doped with Ga to 7 × 10<sup>-4</sup> ohm cm (S-7 wafer)

gas composition: 19.3% HCl, 80.7% H<sub>2</sub>

gas flow rate: 12.89 liters/min substrate temperature. 850°C (convected)

substrate temperature: 850°C (corrected) etching time: 110 sec thickness removed: 17.2 microns

#### ETCHING OF GERMANIUM SUBSTRATES

ture can be detected. These surfaces, which are representative of those obtained routinely, are about as optically flat as finely mechanically polished germanium specimens except at the outer edge of the wafer.

Figure 6 shows a surface which was etched at too low a temperature. The structure on the surface is apparent in all micrographs but is especially noticeable in the multiple-beam interference micrographs.

Fig. 5—Micrographs of Ge surface of wafer, 12/26/62-2, produced in the same manner as that shown in Figure 4, except that substrate temperature was 815°C (corrected) and the thickness removed was 19.2 microns.

December 1963

At these temperatures the etch becomes selective, and pronounced pitting and haziness can be observed. Increasing the HCl concentration for a given etching temperature can also lead to selective etching, especially for the leading edge of a germanium wafer. as shown in Figure 7.

Fig. 6—Micrographs of mirror-smooth Ge surface of wafer, 1/16/63-1, produced in the same manner as those shown in Figures 4 and 5 except that substrate temperature was 790°C (corrected) and the thickness removed was 11.5 microns.

Fig. 7—Effect of increasing HCl concentration (for a given etching temperature).

COMPARISON OF HCl ETCHING WITH OTHER CHEMICAL ETCHES

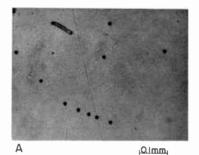

A marked smoothing action has been noted for the gaseous etching of germanium wafers in HCl, as illustrated in Figure 8. A (111) oriented,  $p^+$  germanium substrate wafer was divided into halves; one half was etched in the gaseous HCl, the other in a reagent composed of

Fig. 8—Comparison of the surfaces left on a Ge wafer by etching: (A) one half of Ge wafer in 95  $\rm HNO_{3}$ -5 HF; (B) second half etched in HCl gas; (C) second half subsequently etched in 95  $\rm HNO_{3}$ -5 HF. (Wafer 1/30/63-1, Ge doped with Ga to 7  $\times$  10<sup>-4</sup> ohm cm (S-6 wafer); etching conditions standard; thickness removed during HCl etch not measured directly, estimated 15-20  $\mu$ ; thickness removed during 95/5 etch not measured directly, estimated at 5-10  $\mu$ .)

95 parts by volume of concentrated HNO<sub>3</sub>, 5 parts 49% HF (95/5 etch). Etching in this reagent was carried out because a treatment of this type is commonly used to prepare germanium substrate surfaces for subsequent epitaxial growth. After etching for a total time of 3 minutes, the wafer was rinsed and dried. This etch usually reveals scratches and pits in the substrate surface (Figure 8A). Close examination of the wafer etched in gaseous HCl reveals that almost no structure is present. (Figure 8B). The HCl etched surface was subsequently etched in the 95/5 reagent (Figure 8C) and it can be seen that the scratch marks are less pronounced than in Figure 8A, but the deep pits are again visible.

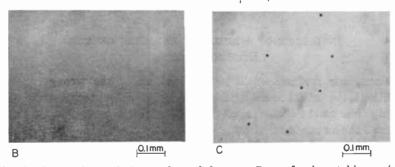

Fig. 9-Germanium removed during HCl etching versus etching time.

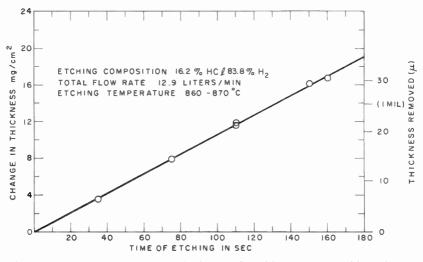

## INFLUENCE OF ETCHING PARAMETERS ON THE ETCHING PROCESS

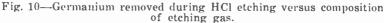

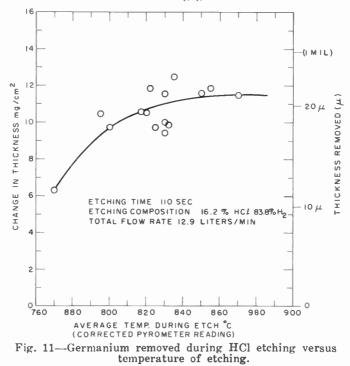

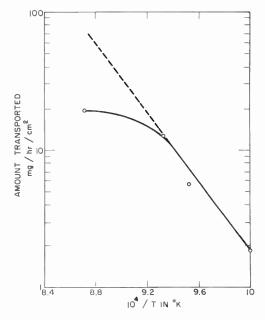

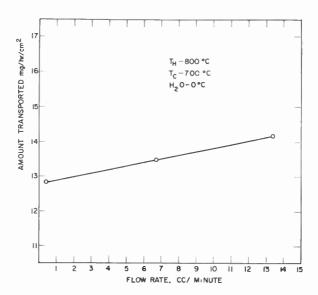

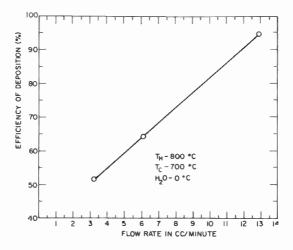

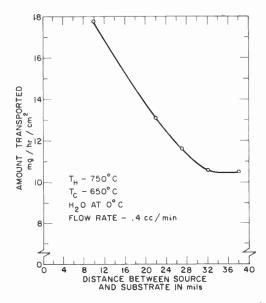

Since poor surfaces could be obtained under the wrong etching conditions, the influence of gas flow rate, composition, temperature and etching time on the character of the etched surface were examined. In Figure 9 the amount of material removed from the surface as a function of etching time is plotted for a given temperature of etching and a particular composition of the etching gas. In Figure 10 the influence of etching-gas composition on the rate of removal of germanium is given. Finally, the amount of germanium removed from the surface as a function of temperature is plotted in Figure 11. These experiments show that the amount of germanium removed from the surface is

December 1963

linearly proportional to the time of etching and to the concentration of HCl in the etching gas, so long as the total gas flow is approximately constant. Furthermore, the amount of germanium removed from the surface is independent of the temperature of the etching, so long as the (corrected) temperature is above about 800°C. Reproducibility in the amount of the material removed during a given etch is observed to be about 10%.

Fig. 12—Optical micrographs of a (100) germanium wafer etched in HCl under the same conditions as in Figure 4. (Wafer 1/15/63-1, Ge doped with As to 0.05 ohm cm (UW-6); thickness removed 16.1 microns.)

For all of the points plotted in Figures 9, 10, and 11 the surfaces from the etching were equivalent, having a mirror bright, optically flat finish similar to those shown in Figure 4 and 5, except for the surfaces prepared at too low a temperature which gave results similar to those of Figure 6. To obtain the best structureless surfaces at etching rates of about 1/2 mil per minute, the temperature must be above 800°C. Below this temperature the etch becomes selective and pits appear.

Surfaces obtained under the conditions described above but on germanium substrate wafers having different doping concentrations and different orientations, are not all alike. In every case the surface was shiny, but for some wafers surface structure was visible micro-

## ETCHING OF GERMANIUM SUBSTRATES

scopically and to the naked eye. 25-mil-thick phosphorus-doped germanium wafers having a resistivity of about 0.01 ohm-cm and 25-milthick wafers doped with gallium to about 1 ohm cm yielded excellent, mirror-finish surfaces. Wafers doped with arsenic to 0.06 ohm-cm, however, showed a distinct waviness similar to orange peel, apparent to the naked eye and visible under the microscope at low magnification. The surfaces did not have fine structure, however, and appeared quite bright and smooth over a short range.

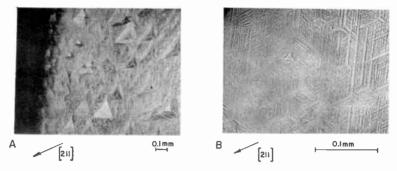

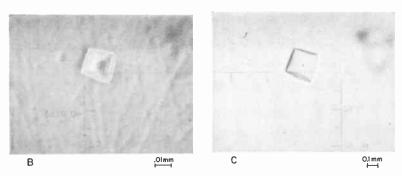

When a (100) orientation wafer is used, square etch pits and marked background structure becomes visible, as seen in Figure 12. Other orientations have not yet been examined, but it is inferred that they will not etch as satisfactorily as the (111) oriented wafers.

#### ACKNOWLEDGMENTS

We would like to express our appreciation to B. R. Czorny, E. Cave, A. F. Mayer and N. Ciampa of RCA Electronic Components and Devices, Somerville, for their helpful discussion and suggestions, to A. Revesz, H. Hook, R. Evans and D. Kupper of RCA Laboratories who aided us in obtaining the multiple beam interference micrographs, and to G. W. Neighbor of RCA Laboratories for his help in setting up and using the Leitz Metallograph.

## CHEMICAL POLISHING OF SILICON WITH ANHYDROUS HYDROGEN CHLORIDE\*

#### Βч

## G. A. LANG AND T. STAVISH

#### RCA Electronic Components and Devices, Somerville, N. J.

Summary—Clean, structurcless surfaces have been prepared on silicon (111) wafers by means of etching in anhydrous HCl. The influence of temperature and gas composition on the etching rate has been determined. Commercially available cylinders of HCl have been analyzed to correlate the etching results with the purity of the HCl reagent used. The precautions necessary for obtaining smooth, structurcless surfaces are described.

#### INTRODUCTION

THE PREPARATION of clean, structureless silicon surfaces is HE PREPARATION of clean, structureless silicon surfaces is of great importance when these surfaces **a**re to be used as substrates for the epitaxial deposition of silicon layers. To minimize defects in the epitaxial layers, it is essential to remove any oxide deposit as well as any mechanically worked region resulting from polishing of the substrates. Aqueous etches of hydrogen fluoride are normally used for this purpose, but the resulting surfaces are not structureless. Both fine pits and "orange peel" can usually be observed on such chemically polished silicon wafers, even when the rotatingbeaker technique<sup>1</sup> of polishing is employed. Cave and Czorny have found that extremely smooth, structureless surfaces can be obtained on silicon substrates if anhydrous hydrogen chloride is used as the etching agent.<sup>2</sup> An investigation of the parameters influencing the etching has been undertaken, therefore, to determine the optimum values for these parameters and to devise better methods of controlling the polishing rate and the smoothness of the surface finish.

<sup>\*</sup> The etching of silicon wafers in SiCl, and in HCl/SiCl, mixtures was described in a "Recent News Paper" by K. Bean and P. Gleim, at the Electrochemical Society meeting September 30-October 3, 1963, in New York City. Their results, obtained in a different type of apparatus, are qualitatively similar to those reported here.

<sup>&</sup>lt;sup>1</sup>D. L. Klein, G. A. Kolb, L. A. Pompliano, and M. V. Sullivan, "Electropolishing of n-Type Germanium and p- and n-Type Silicon," Abstract No. 46, Spring meeting of Electrochemical Society, May 1961.

<sup>&</sup>lt;sup>2</sup> E. F. Cave and B. R. Czorny, "Epitaxial Deposition of Silicon and Germanium Layers by Chloride Reduction," *RCA Review*, Vol. 24, No. 4, p. 523, Dec. 1963.

#### Apparatus

The etching experiments described in this paper were performed in a quartz tube that had an inner diameter of 1% inches and was 30 inches long. This tube was centrally located in a 16-inch resistanceheated furnace. Over the central 2 inches of this furnace the temperature was constant within 5°C of the furnace-temperature setting of 1217°C. The inlet side of the quartz tube was joined to a Pyrex manifold that permitted the introduction of nitrogen, used as a purging gas, or of the hydrogen chloride in a hydrogen diluent, used for the etching. Gas flows were monitored with flowmeters and regulated by needle-bore stopcocks. All connections to the manifold were made of Monel,\* Teflon,\* or Pyrex\* to reduce the probability of any chemical reaction between the apparatus and the hydrogen chloride. The outlet side of the quartz tube was open to the atmosphere, and the effluent gases were burned as they emerged from the tube. The spent gases were then carried away by a small exhaust hood placed over the outlet end of the tube.

A simple technique was used to properly position the silicon wafers inside the polishing apparatus. First, the substrate wafers were placed face down on a quartz flat attached to a hollow quartz push-rod. The assembly was then inserted into the etching tube through the open (exhaust) end and located within the furnace by means of the pushrod. A thermocouple inserted through the center of the hollow pushrod was used to monitor the temperature near the location of the wafers.

#### MATERIALS

The silicon used in this work was obtained in the form of (111) oriented slices about 10 mils thick. Their surfaces were either mechanically polished, using a 0.3-micron abrasive, or were lapped, using a 12- to 14-micron abrasive.

The anhydrous hydrogen chloride was obtained from two main sources. Initially, nine different samples were obtained from one supplier in lecture cylinders. These samples were analyzed by infrared absorption measurements, as described by Pierson.<sup>3</sup> Four of the samples were found to contain acetylene as a major impurity in concentrations of 0.1 to 0.2 per cent; four others were found to contain

<sup>\*</sup> Trade mark.

<sup>&</sup>lt;sup>3</sup> R. H. Pierson, A. N. Fletcher, and E. St. Clair Gantz, "Catalog of Infrared Spectra for Qualitative Analysis of Gases," *Anal. Chem.*, Vol. 28, p. 1218, 1956.

carbon dioxide as the major impurity in concentrations of 0.3 per cent; and the ninth sample was found to contain no impurity in concentrations greater than 0.01 per cent. Acetylene proved to be particularly undesirable in the hydrogen chloride samples because discolored or matte surfaces were obtained when the samples containing this impurity were used for the chemical polishing. All the data on etching rate and surface finish reported in this paper were obtained with a tank of hydrogen chloride containing 0.3 per cent carbon dioxide, but no detectable acetylene.

More recently, samples of Stauffer Chemical Company's anhydrous hydrogen chloride have been obtained. This material has been found to contain less than 0.01 per cent each of acetylene and carbon dioxide, and excellent results are obtained when it is used to polish silicon wafers.

#### PROCEDURE

In the first step of the anhydrous hydrogen chloride method of polishing silicon wafers, the furnace and the quartz reaction tube are brought up to the desired etching temperature while a flow of nitrogen is passed through the apparatus. When the desired temperature has been reached and the apparatus has come to thermal equilibrium, a flow of about 8 liters of hydrogen per minute is established (this value provides a flow rate past the wafer of 14 centimeters per second) and the nitrogen flow is shut off. The silicon wafer on its quartz support is then introduced into the etching chamber and allowed to come to thermal equilibrium. An interval of about 5 minutes is sufficient for this purpose. The valve on the cylinder of hydrogen chloride is then opened, and the desired flow of this reagent is established. Etching usually proceeds for about ten minutes, after which time the hydrogen chloride valve is closed. The wafers are withdrawn from the furnace into the cooler region of the quartz tube, and after they have cooled to about 100°C, they are withdrawn from the apparatus.

#### RESULTS

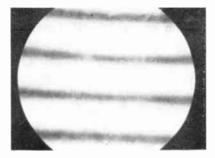

An impression of the types of surfaces obtained by mechanical polishing, by aqueous chemical etching and by anhydrous hydrogen chloride etching of silicon wafers is given by the series of interference micrographs shown in Figures 1-3. All the interference micrographs were obtained at  $250 \times$  original magnification on a Zeiss interference microscope. Figure 1a shows the interference pattern obtained on a mechanically polished silicon wafer, Figure 1b shows the same wafer after 0.3 mil has been removed by etching in anhydrous 0.45%

CHEMICAL POLISHING OF SILICON

(a)

(b)

Fig. 1-Interference micrographs of a mechanically polished silicon surface before and after two degrees of hydrogen-chloride polishing: (a) mechanically polished wafer, (b) same wafer after 0.3 mil of hydrogen chloride polishing, and (c) same wafer after a total of 1 mil of hydrogen chloride polishing.

(a)

(b)

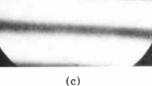

Fig. 2-Interference micrographs showing the combined effects of an aqueous chemical etch and anhydrous hydrogen chloride on a lapped silicon surface: (a) lapped silicon wafer after 4 mils of chemical polishing and (b) same wafer after 2.4 mils of hydrogen chloride polishing.

December 1963

hydrogen chloride at  $1275^{\circ}$ C, and Figure 1c shows the wafer after a total of 1.0 mil has been removed by HCl etching. This amount (1 mil) of material is generally removed from a silicon wafer to ensure that all mechanical damage has been removed. Surfaces equivalent to those described above were obtained for silicon wafers etched at  $1175^{\circ}$ C at the same HCl concentration and for wafers etched at  $1275^{\circ}$ C in 3.0% hydrogen chloride. Thus, there is a range of parameters in which excellent surface finishes can be obtained from the anhydrous hydrogen chloride etching of mechanically polished substrates.

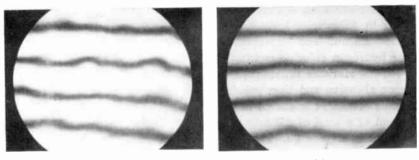

Fig. 3—Interference micrographs showing two degrees of hydrogen chloride polishing of a lapped silicon surface: (a) 2.8 mils removed from the lapped surface and (b) 4.2 mils removed from the lapped surface.

An interference micrograph of a silicon wafer lapped with a 12to 14-micron abrasive and then chemically polished for forty minutes with an iodine polishing etch is shown in Figure 2a. This procedure removed more than 4 mils of material. The same wafer was then etched in anhydrous hydrogen chloride to remove an additional 2.5 mils of silicon. The improvement in the smoothness of the surface after hydrogen chloride etching is apparent from Figure 2b.

An interference micrograph of a wafer lapped with a 12- to 14micron abrasive and then polished with hydrogen chloride to remove 2.8 mils of silicon is shown in Figure 3a. The same wafer, after the removal of a total of 4.2 mils of silicon by hydrogen chloride etching, is shown in Figure 3b. The surface smoothness is much superior to that obtained by aqueous chemical polishing of the same type of lapped surface (cf. Figure 2a).

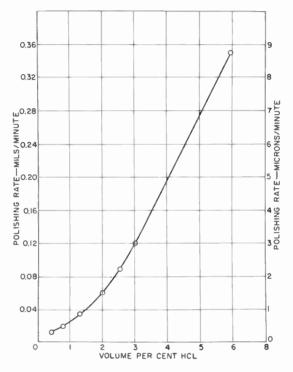

Figure 4 shows the etching rate of mechanically polished silicon wafers as a function of the concentration of hydrogen chloride present in the etching gas. These rates were derived from observed weight

losses during etching and are normalized to unit area. This graph shows that, except for very low concentrations of hydrogen chloride where the conditions probably approach true thermodynamic equilibrium, the etching rate is a linear function of the concentration over the range of concentrations studied.

Fig. 4—Polishing rate as a function of the per cent (by volume) of hydrogen chloride in the etching gas at 1275°C.

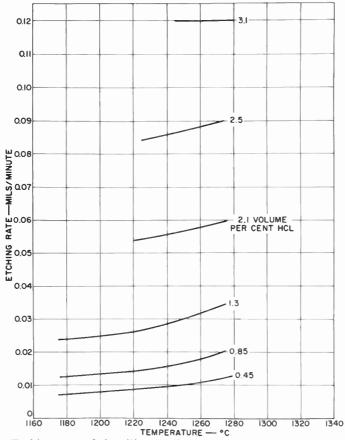

The etching rate for mechanically polished silicon wafers as a function of temperature, for several different compositions of etching gas, is shown in Figure 5. These curves show that the etching rate is not strongly influenced by temperature. No influence on the etching rate was observed for different resistivity types or different resistivity levels, or different initial surface finishes. The mechanically polished wafers and the lapped wafers behaved identically at both high and low etching rates. For these experiments, a temperature of 1275°C and a hydrogen chloride concentration of 0.6 per cent were used.

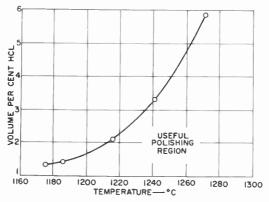

Figure 6 shows the useful polishing region for the system investigated. The maximum polishing rate is defined by the upper boundary

Fig. 5—Etching rate of the silicon wafers as a function of temperature for various concentrations of hydrogen chloride.

Fig. 6—Maximum per cent (by volume) of hydrogen chloride in the etching gas as a function of temperature.

#### CHEMICAL POLISHING OF SILICON

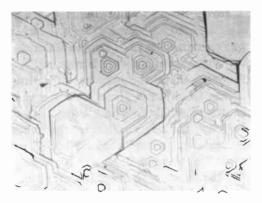

of the useful polishing region and is found to be a function of temperature. If this rate is exceeded by increasing the flow rate of the hydrogen chloride (increasing the concentration of hydrogen chloride in the etching gas), the gas will selectively etch the silicon, and the polished surfaces become pitted, as shown in Figure 7. The hexagonal pits shown in this figure are similar to the ones that, as described below, are formed when the warm-up time of the wafers prior to etching is too short. Thus, for 8 liters per minute of hydrogen flow, any hydrogen chloride flow rate up to and including the maximum flow

Fig. 7—Pitting of the silicon wafers that results from an excessive flow of hydrogen chloride.

will produce a polished surface at any given temperature. It is the limitations on the hydrogen chloride flow rate that form the area termed "useful polishing region" in Figure 6.

The maximum polishing rate, although primarily limited by temperature, is also influenced by the following factors.

(1) Moisture Content of the Etching Mixture—Any leak in the apparatus effectively introduces moisture into the system and limits the maximum useful polishing rate. The maximum polishing rate could be increased at low etching temperatures by inserting a methanol dry-ice trap (at  $-60^{\circ}$ C to  $-70^{\circ}$ C) into the hydrogen chloride gas line. The increase in maximum polishing rate apparently results from a reduction in the moisture content of the hydrogen chloride.

(2) Purity of the Hydrogen Chloride—As described earlier, the purity of hydrogen chloride varies from cylinder to cylinder and from vendor to vendor. The variation in the purity of hydrogen chloride affects the values of the maximum polishing rate given in Figure 6.

Thus, when different cylinders of hydrogen chloride are used, the useful polishing regions will generally be somewhat different from that shown in Figure 6. For example, at 1217°C, a variation in the maximum polishing rate by a factor of 2 was observed among several different cylinders of hydrogen chloride. These differences depended to a large extent on the carbon dioxide content of the gas—the higher the carbon dioxide content, the lower the maximum useful polishing rate. The carbon dioxide probably reacts with hydrogen in the furnace to form water, which has already been shown to be undesirable.

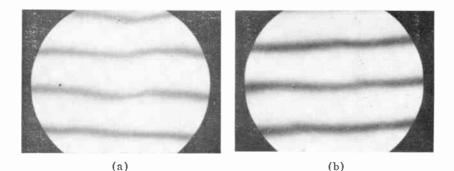

(3) Warm-up Time of the Wafers—If the silicon wafers are introduced into the furnace while the hydrogen chloride gas is flowing, their surfaces are found to be pitted after the etching operation is completed. If the concentration of hydrogen chloride in the etchant gas is increased, a longer warm-up time is required before the etching can be begun. Figure 8 shows the influence of warm-up time on the quality of the surface finish for a given hydrogen chloride concentration and temperature of etching. The pitting that occurs when the warm-up time is insufficient is similar to that obtained when the etching rates are excessive, as mentioned earlier. Figure 8 shows that as the warm-up period increases and the wafer more closely approaches the temperature of the furnace, the pitting decreases. Similar pitting can occur if the wafer is withdrawn from the furnace while the hydrogen chloride is flowing.

## LIMITATIONS OF THE ANHYDROUS HCl POLISHING METHOD

Two factors tend to limit the use of anhydrous HCl for polishing silicon wafers. First, when this polishing technique is employed, the leading edge of the wafer (the one nearest the HCl source) is etched more rapidly than the trailing edge. However, if a turbulence is introduced into the gas stream, this difference in etching rate can probably be eliminated.

Second, because of the high temperature required to obtain smoothly etched surfaces, the application of the anhydrous HCl polishing technique is restricted primarily to undiffused substrate wafers. This restriction results from the fact that when a diffusion step has been performed on the wafer prior to etching, the etching cycle must be substantially shortened to ensure that further diffusion of the wafer is held to a minimum.

In an attempt to overcome the limitation imposed by the hightemperature requirement of hydrogen chloride polishing, a chlorine etchant was tested as a substitute for the hydrogen chloride. Although chlorine attacks silicon at lower temperatures than hydrogen chloride, the surfaces were always found to be attacked preferentially, as reported by Gualtieri.<sup>4</sup> This behavior was also observed for etching mixtures of chlorine and nitrogen over the entire composition range at temperatures from 500 °C to 900 °C.

30 sec. warm-up

ŝ

60 sec. warm-up

DIRECTION OF GAS FLOW-++ (ALL WAFERS)

90 sec. warm-up

120 sec. warm-up

Fig. 8—Pitting of the silicon wafers that occurs when the flow of hydrogen chloride is begun before the wafers have been allowed a sufficient warm-up period.

#### CONCLUSIONS

The polishing of silicon wafers in anhydrous HCl has been found very satisfactory for several reasons:

(1) The polishing rate can be accurately controlled, and the

<sup>&</sup>lt;sup>4</sup> J. G. Gualtieri, M. J. Katz and G. A. Wolff, "Gas Etching and Its Effect on Semiconductor Surfaces," *Zeitschrift für Krist.*, Vol. 114, p. 11, 1960.

ł

polycrystalline p-type germanium layers having an average crystallite diameter of 0.3 to 0.5 micron, a resistivity of about 0.02 to 0.05 ohm-cm and a mobility of 20 to 140 cm<sup>2</sup>/volt-sec. By adding arsine to their germane, they obtained n-type deposits. The surfaces of their films appeared reasonably smooth at 15,000× magnification.

In an attempt to deposit smooth, single-crystal layers of germanium epitaxially on germanium substrates, Davis and Lever<sup>2</sup> employed the pyrolysis of germane. Although they were unsuccessful in preparing smooth surfaces, they did obtain single-crystal deposits when the substrate was held at a temperature of approximately 900°C. Their depositions were carried out at reduced pressures in a vacuum system whose ultimate vacuum was stated to be  $10^{-6}$  mm Hg. Their substrates were cleaned by chemical etching followed by baking in hydrogen at about 900°C. No electrical measurements were reported for these layers, nor was the purity of their germane given.

With the recent improvement in the synthesis of germane in high yields reported by Macklen,<sup>3</sup> and by Griffiths<sup>4</sup> and with the newly developed technique of etching germanium substrates in gaseous HCl at high temperatures,<sup>5</sup> a reinvestigation of the preparation of germanium layers by pyrolysis of germane seemed warranted. Additional information which has been published by Boudart et al.<sup>6,7</sup> on the kinetics of the pyrolysis of germane was also very encouraging. They found that decomposition on the surface proceeds an order of magnitude faster than the homogeneous gas-phase reaction. They also postulated that during the decomposition, GeH<sub>x</sub> radicals migrate freely on the germanium surface, a situation which should be favorable for the deposition of layers having smooth surfaces and high crystalline perfection.

<sup>&</sup>lt;sup>2</sup> M. Davis and R. F. Lever, "Vapor Phase Crystal Growth of Germanium from Thermally Decomposed Germane," *Jour. Appl. Phys.*, Vol. 27, No. 7, p. 835, July 1956.

<sup>&</sup>lt;sup>3</sup> E. D. Macklen, "Preparation of Germane. Part I. Reaction between Lithium Aluminium Hydride and Germanium Tetrachloride," *Jour. Chem. Soc.* (London), p. 1984, April-Aug. 1959; "Preparation of Germane. Part II. Reaction between Sodium Borohydride and Germanium Tetrachloride," p. 1989.

<sup>&</sup>lt;sup>4</sup> J. E. Griffiths, "Mongermanes-Their Synthesis and Properties," Inorganic Chemistry, Vol. 2, p. 375, April 1963.

<sup>&</sup>lt;sup>5</sup> J. A. Amick, E. A. Roth, and H. Gossenberger, "The Etching of Germanium Substrates in Gaseous Hydrogen Chloride," *RCA Review*, Vol. 24, No. 3, p. 473, Sept. 1963.

<sup>&</sup>lt;sup>6</sup> K. Tamaru, M. Boudart, and H. Taylor, "The Thermal Decomposition of Germane. I. Kinetics," *Jour. Phys. Chem.*, Vol. 59, No. 9, p. 801, Sept. 20, 1955.

<sup>&</sup>lt;sup>7</sup> P. J. Fensham, K. Tamaru, M. Boudart, and H. Taylor, "The Thermal Decomposition of Germane. II. Mechanism," *Jour. Phys. Chem.*, Vol. 59, No. 9, p. 806, Sept. 20, 1955.

## THE SYNTHESIS OF GERMANE

Until 1957, the production of germane was severely limited because it was obtainable only in low yields from starting materials which were themselves difficult to prepare. With the availability of the powerful reducing agent lithium aluminum hydride, it was expected that larger yields of germane could be obtained. However, the reducing power of this mixed hydride is so great that the reduction product consists mostly of elemental germanium. In 1957 Piper and Wilson<sup>8</sup> showed that sodium borohydride is a more-satisfactory reducing agent for this synthesis, being much milder than lithium aluminum hydride. Using germanium dioxide as the starting material, they obtained yields of germane in excess of 50%.

In the preparation of reagent germane used here, germanium dioxide was again employed as the starting material. When the oxide is added to concentrated aqueous HCl,\* conversion of some of the oxide to chloride takes place. Addition of aqueous sodium borohydride dropwise to this combination results in the liberation of a germane-hydrogen mixture.

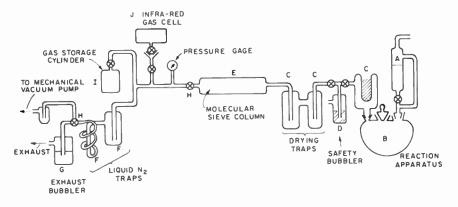

Figure 1 shows a schematic of the reaction apparatus used in the preparation of germane. A solution of about 110 grams of sodium borohydride<sup>†</sup> in 450 ml of water is filtered into the dropping funnel. (A). This solution is then added dropwise to a slurry consisting of 104 grams of  $\text{GeO}_2^{\#}$  in a solution of 365 grams of constant boiling (20.24 wt.%) HCl in 300 ml of water. The concentration of HCl is not critical but at higher concentrations the formation of hydrogen is favored over the formation of germane and at lower concentrations the conversion of germanium dioxide to germanium tetrachloride becomes inefficient, especially after most of the HCl has been consumed in the reaction. During addition of the borohydride, the slurry is constantly stirred with a magnetic stirrer in the flask (B). The resulting gaseous products, mostly hydrogen and germane, are dried by

<sup>†</sup> Sodium Borohydride, 98%+ from Metal Hydrides, Inc., Beverly, Mass. <sup>#</sup> Eagle-Picher Company, Miami, Oklahoma.

<sup>&</sup>lt;sup>8</sup> T. S. Piper and M. K. Wilson, "The Preparation of Germane," Jour. Inorganic and Nuclear Chem., Vol. 4, p. 22, 1957.

<sup>\*</sup> In 1961, Drake<sup>9</sup> published a modification of Macklen's method in which acetic acid was substituted for the HCl. With this substitution, the reaction becomes more efficient in terms of the borohydride required.

<sup>&</sup>lt;sup>9</sup> J. E. Drake, "The Preparation of Some Germanium Hydrides," U. S. Atomic Energy Comm., Univ. of California Radiation Lab, UCRL 9709, May 18, 1961; J. E. Drake and W. L. Jolly, "Hydrides of Germanium," Jour. Chem. Soc. (London), p. 2807, Part III, 1962.

passing them through the dry-ice traps (C). A silicone oil bubbler (D) is provided as a safety value in the event that a block occurs in the purification train during operation. The gas mixture is next passed through a 36-inch column of molecular sieve (E),<sup>\*</sup> which serves to dry the gases still further and to remove any hydrogen chloride from the gas stream. Before beginning a run, this column is heated to 350°C and purged with flowing helium for 24 hours and then cooled to room temperature. Germane condenses in the liquid nitrogen traps (F) and by-product hydrogen leaves the system through bubbler (G) filled with silicone oil.

Fig. 1-Apparatus for the preparation and purification of germane.

At the conclusion of the reaction, the germane retained in the molecular sieve column is displaced with flowing helium and condensed in the liquid nitrogen traps (F). The system between the stopcocks (H) is then evacuated and sealed off while the germane is held at liquid-nitrogen temperature. Finally the germane is transferred into the gas cylinder (I) which has previously been evacuated and cooled to liquid-nitrogen temperature. An infrared sampling cell (J) is used to collect samples for analysis. After all of the germane has been transferred to the gas cylinder, the system is again pumped down to a pressure of less than 1.0 micron to remove any noncondensable gases, primarily hydrogen. The cylinder is then closed off and allowed to warm to room temperature. It is then cooled again to liquid nitrogen temperature and again pumped down. After two or three cycles, the pressure in the system no longer rises when the valve between the

<sup>\* 5</sup>A Molecular Sieve, Linde Co. Division, Union Carbide Corp.

## GROWTH OF GERMANIUM EPITAXIAL LAYERS

cylinder and the system is opened, the cylinder being at liquid nitrogen temperature. The relative concentration of noncondensable gases in the cylinder at room temperature should then be well below 1 part per million.

The germane which collects in the liquid nitrogen traps is a white solid which melts, on warming, to a colorless liquid. The yield for the synthesis reaction described above is generally about 35% calculated on the germanium oxide used. A large quantity of a reddish brown solid usually forms in the flask (B) as the reaction proceeds. This is presumed to be the polymeric germanium hydride  $(GeH_2)_x$  which has been reported by earlier workers.<sup>3</sup> This by-product is probably the cause of the low yields obtained.

#### ANALYSIS OF THE GERMANE

The germane was analyzed by three techniques: gas chromatography, infrared spectroscopy, and mass spectrometry. The gas chromatograms were obtained with a Perkin-Elmer 154 C Vapor Fractometer using a silica-gel column. This analysis showed that the germane had less than 1% hydrogen and no trace of water. Because air is invariably introduced into the Fractometer during sampling, it can only be stated from this analysis that its concentration is less than 1%. No peaks were observed which could not be interpreted. The infrared analyses were obtained using a Perkin-Elmer 221 infrared spectrophotometer and a 10-cm gas cell. The only absorption peaks observed were those previously reported for germane.<sup>10,11</sup> No water or HCl absorption peaks were detected. Neither oxygen nor nitrogen have characteristic absorption bands in the infrared.

Mass spectrometric analyses were obtained using a Consolidated 21-620 mass spectrometer. These spectra showed that the concentration of air in the germane was less than 0.02%. Small peaks characteristic of hydrocarbons, water and carbon dioxide were present as background in the instrument. If any of these were present in the germane, their concentration was well below the level of 0.02%.

Results from these three analytical techniques thus confirm the purity of the germane. The contaminant present in the greatest amount is probably hydrogen. Since the depositions were to be carried out in hydrogen, this was not troublesome. Other than hydrogen, the con-

<sup>&</sup>lt;sup>10</sup> W. B. Steward and H. H. Nielsen, "The Infrared Absorption Spectrum of Germane," *Phys. Rev.*, Vol. 48, No. 11, p. 861, 1935.

<sup>&</sup>lt;sup>11</sup> J. W. Straley, C. H. Tindal and H. H. Nielsen, "The Vibration-Rotation Spectrum of GeH<sub>4</sub>," *Phys. Rev.*, Vol. 62, p. 161, 1942.

tamination level is below 2 parts in 10,000. Water and oxygen are below this level by at least one order of magnitude. No diborane (from the decomposition of sodium borohydride) or HCl are present in detectable amounts.

#### DEPOSITION OF GERMANIUM LAYERS

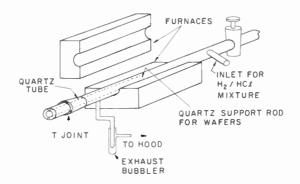

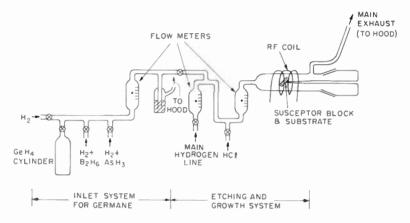

The apparatus in which the germanium layers were deposited is shown in Figure 2. In this apparatus, provision is made for etching the substrate surface in gaseous HCl just prior to growth. Following

Fig. 2—Diagram of apparatus for the growth of germanium layers by the pyrolysis of germane.

the HCl etch, the substrate has a clean, brightly polished surface which is ideal for epitaxial growth. The manner of preparing these germanium substrates and the characteristics of the HCl etched surfaces prepared in this apparatus have already been described.<sup>5</sup>

The reagents employed in the growth include germane, synthesized as described above, and palladium-diffused hydrogen." When it was desired to produce doped layers, either arsine diluted in hydrogen to 50 ppm or diborane diluted in hydrogen to the same concentration were employed.<sup>†</sup> Substrates were (111) oriented single-crystal slices of germanium doped to a resistivity of about  $7 \times 10^{-4}$  ohm-cm with gallium or to about 0.05 ohm-cm with arsenic. The susceptor block on which the substrates were heated was described earlier.<sup>6</sup>

<sup>\*</sup> Palladium diffuser from Engelhard Industries, Newark, N. J.

<sup>&</sup>lt;sup>†</sup> Air Reduction Company, Jersey City, N. J.

#### GROWTH OF GERMANIUM EPITAXIAL LAYERS

The concentration of germane in the entrant gas was kept low, typically about 0.005% by volume, so that the same gas flows could be used for the growth of single-crystal germanium layers over a wide temperature range. For growth in the neighborhood of 800°C, this concentration could be increased by a factor of at least 10 without affecting the crystalline nature of the deposit perceptibly.

The best growth conditions required rapid flows of hydrogen to minimize decomposition of the germane in the gas phase. If gas phase (homogeneous) nucleation takes place upstream from the substrates, randomly oriented crystallites may settle onto the substrate surface and polycrystalline layers usually result. With sufficiently high hydrogen flow, pyrolysis of the germane is minimized until the reagent impinges on the substrate surface. Hydrogen flows were typically about 10 liters per minute which, in this apparatus, corresponds to a linear velocity of about 8 cm per sec.

Before growth of a germanium layer on a freshly etched substrate, the r-f generator is adjusted, while the hydrogen stream is flowing, so as to bring the temperature of the substrate from that used in the etching to that desired for growth. A few minutes are then allowed for the substrate to come to a steady-state temperature. During this interval, a flow of germane and, if desired, dopant gas is established in the inlet system. The flow rate of each of these gases is adjusted to desired values with the help of the flow meter, and the effluent is allowed to pass out through the inlet bubbler (cf. Figure 2). About 50 cc/min of hydrogen is added to this gas stream to ensure thorough mixing of the gases and rapid attainment of a constant composition.

To begin growth, the stopcock separating the inlet apparatus from the growth apparatus is opened. At this time, the column of liquid in the bubbler provides sufficient back pressure so that all of the gas now enters the main hydrogen-gas stream and passes through the deposition chamber. The presence of germane in the deposition chamber can readily be detected by the appearance of the flame of the exhaust gases. The flame, upon addition of the germane, acquires a yellow inner cone similar to that obtained with methane.

A run typically lasts about one hour with approximately 1/4 mil of germanium being deposited in that interval. At the conclusion of a run, the stopcock connecting the inlet system with the main hydrogen flow is turned off. The disappearance of germane from the system can be observed by watching the flame of the effluent gases and, about 5 minutes later, the r-f generator is turned off and the substrate is allowed to cool to room temperature in flowing hydrogen.

505

## CHARACTERISTICS OF DEPOSITED GERMANIUM LAYERS

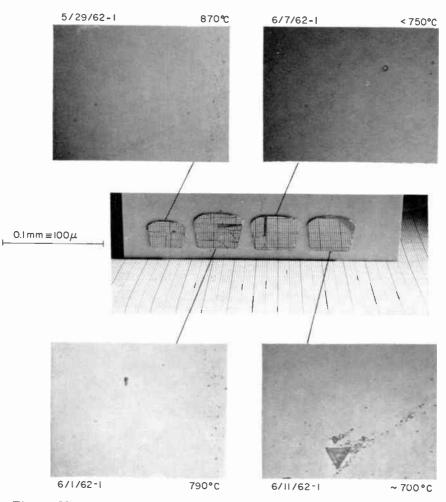

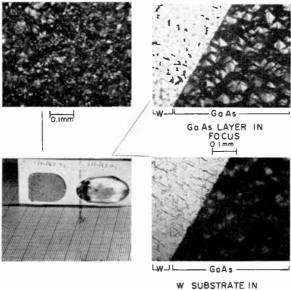

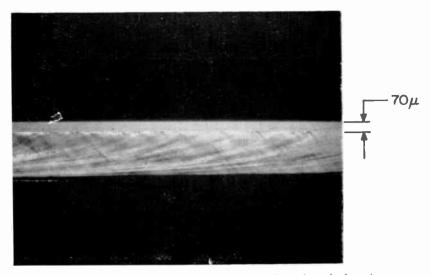

Initially, approximately 1/4-mil thick layers were prepared from the pyrolysis of germane without introducing any additional doping agent. Over the temperature range  $\sim 700$  °C to 900 °C, (corrected) bright, mirror smooth deposits were obtained, as shown in Figure 3. The pyrometer used in this work cannot be read precisely for true temperatures below 750 °C. Therefore, the lower temperature limit at which smooth deposits are obtained was not estimated accurately.

Fig. 3—Micrographs and photograph of the "as grown" surfaces of germanium epitaxial layers prepared by pyrolysis of germane at different temperatures (corrected) (original magnification ×650; thickness of layers about 6 microns).

Defects begin to appear in the grown layers at temperatures estimated as in the neighborhood of 700°C (corrected).

In order to give an impression of the surface finish of the grown layers, a photograph of the wafers is included in Figure 3. Prior to obtaining this photograph, several of the wafers were cut apart and angle lapped. The cracks where the pieces have been rejoined can readily be seen. The surrounding micrographs, obtained at an original magnification of  $650\times$  show that the surfaces of the layers have very little structure. The characteristic triangular defects seen by Davis and Lever<sup>2</sup> are absent in these micrographs except for a few scattered defects seen in the deposits prepared at the lowest temperature.

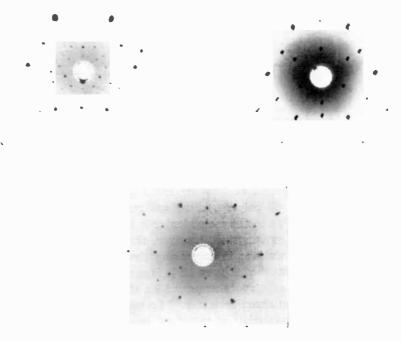

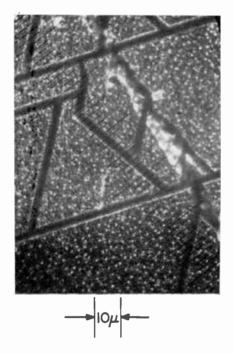

The crystallinity of the layers was evaluated by two techniques. Laue back-reflection patterns were obtained which give information about the crystallinity to a depth of approximately 1 mil. Selective chemical etches were also used to reveal etch pits in the deposited layers. Both of these techniques show that the layers are highly crystalline and oriented in the same sense as the substrate. Electron diffraction has also been attempted with these layers but the results have been ambiguous. The layers are apparently so smooth that the patterns originate from small projections on the surface, possibly oxide particles.

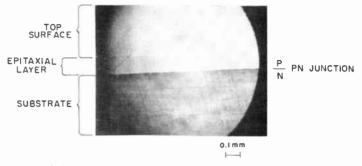

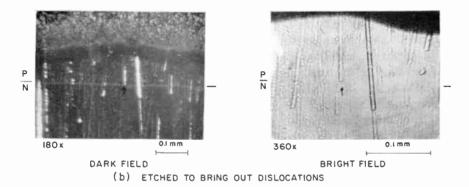

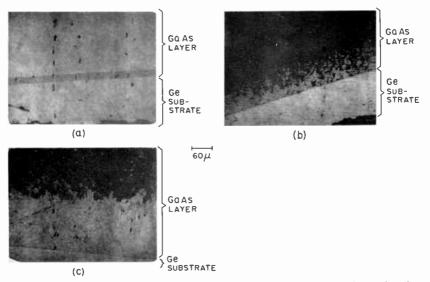

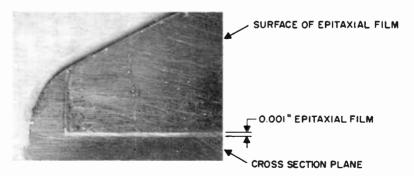

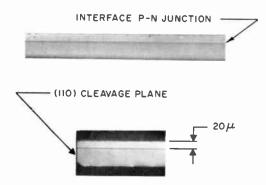

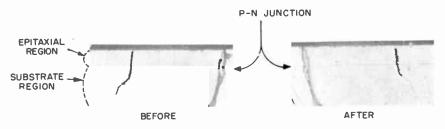

The interface region between the substrate and the grown layer is shown in Figure 4 for a p-type layer grown on an n-type substrate. In Figure 4a, the junction is delineated by angle lapping the wafer at 2° followed by copper staining the junction region. In Figure 4b the same wafer has been etched to reveal dislocations. The etch pits are seen to be triangular, of the same orientation and approximately the same concentration on both sides of the junction.

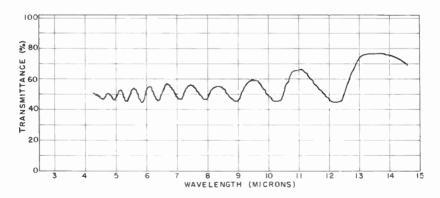

The thickness of the deposited layers was determined both by angle lapping/staining (Figure 4a) and by infrared interference (Figure 5). The maxima and minima in the infrared interference pattern are quite pronounced, indicating that the layer is uniform in thickness and that the surfaces are essentially plane parallel.

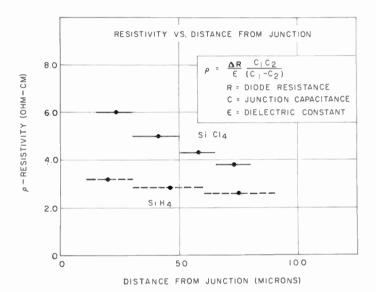

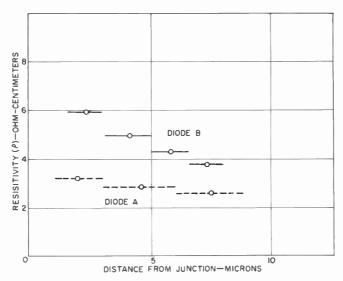

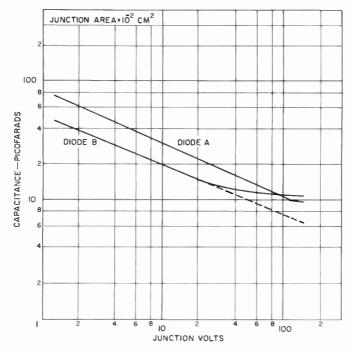

Resistivities of the germanium layers prepared by pyrolysis of germane without deliberate addition of doping agents were about 1 ohm cm p-type and were measured by two methods. For the deposits on n-type substrates, a four-point probe was used to estimate the resistivity. For deposits prepared at about 850°C (corrected) on heavily doped p-type substrates, a different technique was used. A junction was prepared within the epitaxial layer by in-diffusion of arsenic. Mesas were then etched in the layers to give diodes. The capacitance-voltage characteristics of these diodes were determined

507

(a) ANGLE LAPPED(2°) AND STAINED WITH COPPER

Fig. 4—Typical epitaxially grown layer of germanium prepared by pyrolysis of germane (growth temperature 860°C (corrected); thickness about 6 microns).

Fig. 5—Typical infrared interference pattern from an epitaxially deposited germanium layer prepared by pyrolysis of germane.

### GROWTH OF GERMANIUM EPITAXIAL LAYERS

509

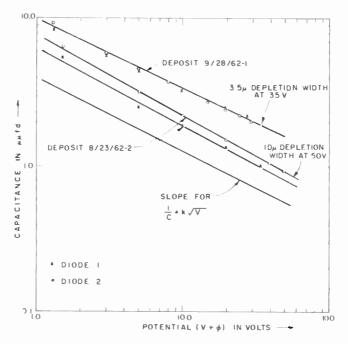

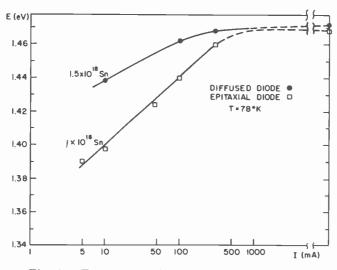

(Figure 6) and, knowing the area of the junction, the resistivities were calculated.<sup>12</sup> The agreement between these two types of measurement suggests that very little dopant is transferred from the substrate or susceptor into the growing layer during deposition. The capacitance-voltage characterisics of Figure 6 all show excellent square-root-law

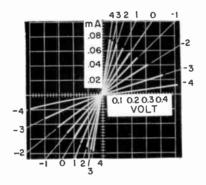

Fig. 6—Capacitance versus voltage characteristics for diodes prepared in epitaxial germanium deposits. Deposit 8/23/62-2: growth temperature 860°C (corrected); thickness 20 microns (infrared interference). Deposit 9/28/62-1: growth temperature 845°C (corrected); thickness 7 microns (infrared interference).

curves, demonstrating that the doping concentration is uniform throughout the region in which the space-charge depletion layer forms.

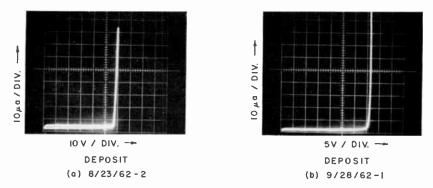

The current-voltage characteristics of these junctions formed within the epitaxial layer were also determined, as shown in Figure 7. Reverse breakdowns are observed to be very sharp, and the breakdown potential is in good agreement with that calculated for avalanche breakdown in the epitaxial layer. Saturation currents are low and uniform from diode to diode.

<sup>&</sup>lt;sup>12</sup> J. Hilibrand and R. D. Gold, "Determination of the Impurity Distribution in Junction Diodes from Capacitance-Voltage Measurements," *RCA Review*, Vol. 21, No. 2, p. 245, June 1960.

Fig. 7-Reverse-bias characteristics of diodes formed in germanium epitaxial layers prepared by pyrolysis of germane (cf. Figure 6). (Courtesy of B. R. Czorny).

These diode characteristics are reported to be as good as for diodes prepared in the best germanium epitaxial layers produced by reduction of germanium chloride with hydrogen. It is therefore concluded that germanium epitaxial layers equivalent in a crystallographic and electrical sense to layers prepared by reduction of germanium chloride can be prepared by the pyrolysis of germane. A discussion of the properties of the doped layers and the relationship between the concentration of dopant in the gas stream and the doping concentration in the deposited layers is planned for a future paper.

#### ACKNOWLEDGMENT

For the fabrication of diodes and the measurement of their capacitance-voltage and current-voltage characteristics, we are indebted to B. R. Czorny of RCA Electronic Components and Devices. The mass spectrometric analyses of the germane were carried out by I. Stacy, and the gas chromatograph was kindly made available by H. Hyman and P. A. Hoss, also of RCA Components and Devices. We would also like to thank A. F. Mayer and W. Kern for their many helpful comments and suggestions, and M. Coutts, G. W. Neighbor, and W. Roth for their aid in obtaining x-ray and electron-diffraction patterns.

## EPITAXIAL DEPOSITION OF SILICON BY THERMAL DECOMPOSITION OF SILANE

#### Βy

## S. R. BHOLA AND A. MAYER

#### RCA Electronic Components and Devices, Somerville, N. J.

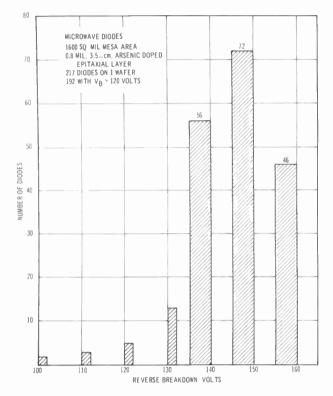

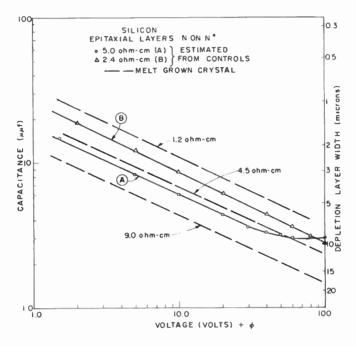

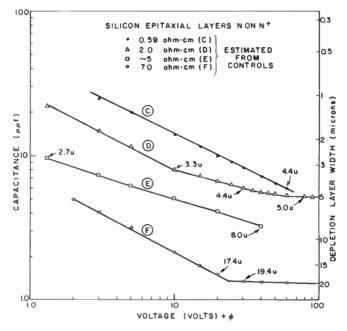

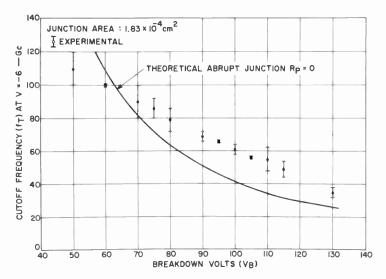

Summary—Pyrolysis of silanc diluted with hydrogen is shown to be a safe, simple, and convenient method for the epitaxial deposition of silicon. Large-area microwave diodes made by this process have excellent electrical properties. Almost abrupt high-low and p-n junctions can be grown at rates of 0.02 to 1 micron per minute at 1080 to 1130°C. Gas-phase doping with diborane, phosphine, and arsine permits close resistivity control in the range 0.001 to 30 ohm-centimeters.\*

#### INTRODUCTION

HE EPITAXIAL DEPOSITION of single-crystal silicon layers on silicon substrates has become an established step in the routine production of various semiconductor devices. Common practice is to use a vapor-phase reaction, at 1150 to 1250°C, between silicon tetrachloride (SiCl<sub>4</sub>) and hydrogen to form the elemental silicon which deposits on the substrate wafer; the other reaction products are mainly hydrogen chloride and lower silicon chlorides. Other silicon halides (SiHCl<sub>3</sub>, SiBr<sub>4</sub>, SiI<sub>4</sub>, etc.) may be used in place of the tetrachloride. The process is well suited for the routine production of many types of transistors, diodes, and rectifiers.

However, at the relatively high concentration required for the deposition reaction, halide ions can transport and deposit unwanted impurities at the growing face. In some semiconductor devices, abrupt changes in dopant concentration and in the type of conductivity are desirable, and it was thought probable that such structures could be prepared more advantageously by the thermal decomposition of silane  $(SiH_4)$ .

Silane can be obtained from the hydrolysis of calcium or magnesium silicide or from the reaction of silicon tetrachloride with

<sup>\*</sup> The silane process was described brieby in a "Recent News Paper" entitled "Silane Epitaxial Silicon for Microwave Diodes," by M. A. Klein, H. Kressel, and A. Mayer at the Electrochemical Society Meeting, Pittsburgh, April 1963.

lithium aluminum hydride.<sup>1,2</sup> It is a colorless gas which ignites spontaneously when released into the atmosphere. (It has a boiling point of 112°C, a freezing point of -185°C, a critical temperature of -3.5°C, and a critical pressure of 47.8 atmospheres.) Mixtures of silane and air are explosive over a wide range of composition. When prepared by either of the methods mentioned above, the silane usually contains traces of other hydrides, such as arsine, borane, phosphine, and the like. It can be purified by chemical absorption, by condensation and distillation, by the use of suitable cold traps, or by the selective adsorption of impurities on active carbon or a molecular sieve;<sup>3-5</sup> borane impurities can also be removed catalytically by contact with platinum or Raney nickel.<sup>6</sup>

Silane has a positive free heat of formation,  $\Delta Hf_{298}$ , which is about +7.5 kilocalories per mole.<sup>7-9</sup> The pyrolytic reaction,  $SiH_4 \rightarrow Si + 2H_2$ , is appreciable at temperatures above 600°C and is probably accompanied by the formation of small amounts of polymers, such as disilane  $(Si_2H_6)$ , trisilane  $(Si_3H_8)$ , etc.<sup>10</sup> The standard free energy of decomposition for this reaction is -12 kilocalories per mole at 300°K and -40 kilocalories per mole at 1400°K.

The decomposition of pure silane at reduced pressure has been the basis for the production of bulk silicon for many years,<sup>11</sup> but because the process is hazardous and necessitates burdensome safety precau-

<sup>3</sup> H. C. Kelly, T. J. Flynn, C. W. Davis, and S. Johnson, AFCRC-TR-57-198; AD 133701, 1957; C. W. Lewis, M. B. Giusto, and S. Johnson, AFCRC-TR-58-354; AD 228538, 1959.

<sup>4</sup> E. G. Caswell and R. A. Lefever, U.S. Patent 2,971,607 (1961).

<sup>5</sup> R. G. Beckenridge, U.S. Signal Corps Contract DA 36-039-SC-90734, Quarterly Reports June 1962 onward.

<sup>6</sup> T. A. Jacob and N. R. Trenner, U.S. Patent 3,019,087 (1962).

<sup>7</sup> T. R. Hogness, T. L. Wilson, and W. C. Johnson, "Thermal Decomposition of Silane," *Jour. Amer. Chem. Soc.*, Vol. 58, p. 108, Jan. 1936.

<sup>8</sup> E. O. Brimm and H. M. Humphreys, "The Heat of Formation of Silane," Jour. Phys. Chem., Vol. 61, p. 829, June 1957.

<sup>9</sup> S. R. Gunn and L. G. Green, "The Heats of Formation of Some Unstable Gaseous Hydrides," *Jour. Phys. Chem.*, Vol. 65, p. 779, May 1961.

<sup>10</sup> K. Stokland, "The Thermal Decomposition of Disilane and Trisilane," Trans. Faraday Soc., Vol. 44, p. 545, Aug. 1948.

<sup>11</sup> H. F. Sterling and F. J. Raymond, Brit. Patent 745,383; U.S. Patent 3,044,967; see also 2,841,860; 2,871,533.

<sup>&</sup>lt;sup>1</sup> J. M. Wilson, "Large-Scale Preparation of Ultrapure Silicon," *Research*, Vol. 12, p. 91, March 1959.

<sup>&</sup>lt;sup>2</sup> C. H. Lewis, H. C. Kelly, M. B. Giusto, and S. Johnson, "Preparation of High-Purity Silicon from Silane," *Jour. Electrochem. Soc.*, Vol. 108, p. 1114, Dec. 1961.

## EPITAXIAL DEPOSITION OF SILICON

tions, most producers have turned to other methods. It has been found, however, that silane diluted with hydrogen or a rare gas to a concentration of less than 5% by volume is not pyrophoric and can be stored at a pressure of 1000 psi in a standard gas cylinder. It is now available commercially in this form. The silane epitaxial system described

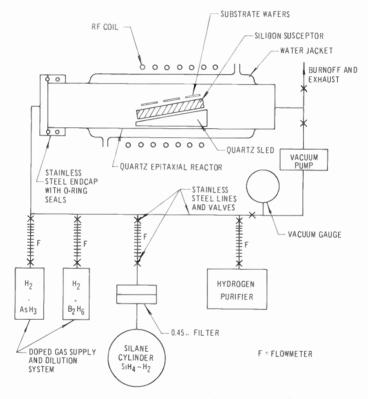

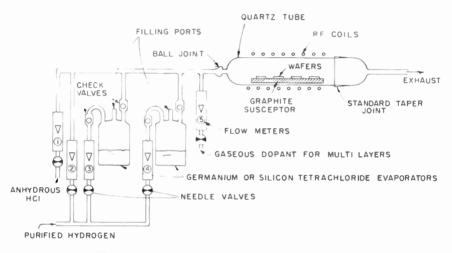

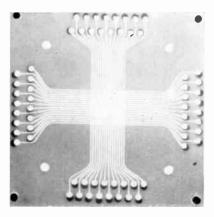

Fig. 1-Schematic diagram of silane epitaxial system.

in this paper has been operated daily for 18 months without accident, using the same safety precautions as those recommended for hydrogen.

#### APPARATUS

The apparatus used to achieve the epitaxial deposition of silicon from the pyrolysis of silane is shown schematically in Figure 1. All lines and valves of this apparatus are made of stainless steel and are connected by Teflon compression and Viton "O" ring fittings. The

513

reactor tube is made of quartz. The water jacket is used to keep the temperature of the wall of the reactor tube low enough so that the pyrolysis of the silane is confined to the r-f heated silicon susceptor block upon which the substrate wafers are placed. The block is supported on a quartz sled in an inclined position which helps to assure over-all uniformity of the silicon deposition.

The system is checked for leaks with a helium mass spectrometer detector and, on a more routine basis, by evacuating the system with the rotary vacuum pump attached to it and observing the vacuum gauge after the pump has been isolated. It is important that oxygen, in particular, be eliminated from the system, because traces of oxygen interfere with the doping and react with silicon to form silicon monoxide particles which can become embedded in the deposit. Silicon monoxide deposits also form on the apparatus wall, obscuring vision and interfering with the optical pyrometer readings used for temperature control.

The hydrogen diluent for the silane and doping gases is used in relatively large volumes to ensure uniformity in the thickness and in the doping of the deposit. A palladium diffuser can be employed to obtain a reliable source of oxygen-free and dust-free hydrogen, although its use is not mandatory.

A submicron filter is used to remove any dust that comes from the compressed-gas cylinders that supply the diluted silane and dopants. Diborane and arsine or phosphine at concentrations of 200 to 500 parts per million in hydrogen are used as the dopants. The required dilution of the dopants with hydrogen is accomplished by expansion of a known quantity of the doping gases into evacuated stainless-steel tanks and addition of hydrogen until the pressure in the tanks rises to a predetermined level (3 to 6 atmospheres). The diluted dopant gases are then allowed to flow from their respective reservoirs through flowmeters to the main gas feed. This dilution system can provide a wide range of dopant concentrations and yet uses only one flowmeter for each dopant gas, so that automatic and programmed flow control becomes feasible.

### **OPERATION**

The prepared silicon wafers are inserted into the reactor on a high-resistivity silicon block as shown in Figure 1. A small piece of low-resistivity silicon is placed in contact with the susceptor block to act as a starter for r-f coupling. The apparatus is evacuated to remove air and the last traces of moisture, and hydrogen is admitted until atmospheric pressure is reached. The exit valve is then opened and the hydrogen flow is adjusted to 10 to 30 liters per minute. The susceptor is heated to  $1200^{\circ}$ C<sup>\*</sup> for 10 to 15 minutes to remove the natural oxide film on the substrate wafer. The temperature is reduced to  $1100^{\circ}$ C and, when thermal equilibrium is reached, the silane flow (and dopant flow) is started. After the deposition process has proceeded for the time necessary to produce the desired thickness, the silane flow is stopped, and the wafers are cooled in hydrogen.

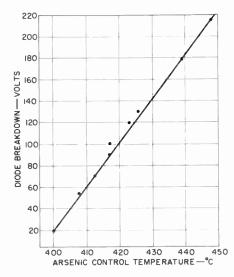

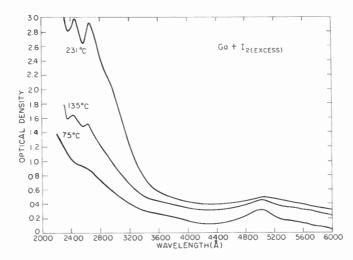

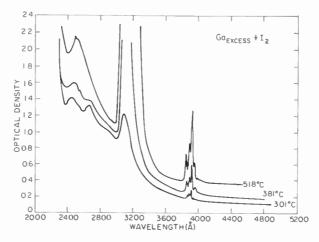

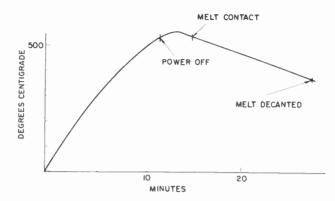

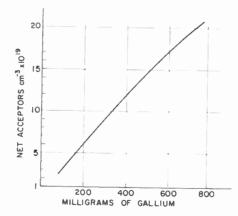

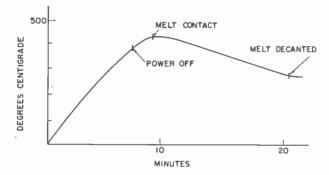

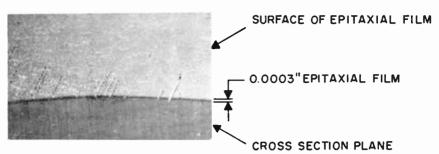

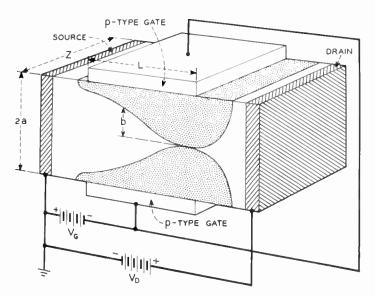

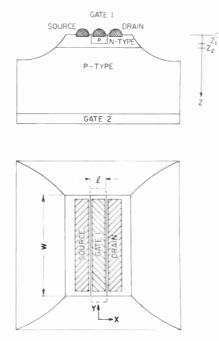

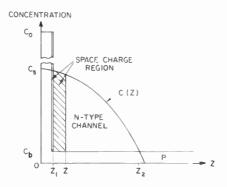

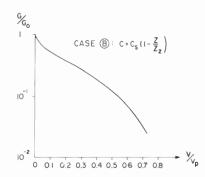

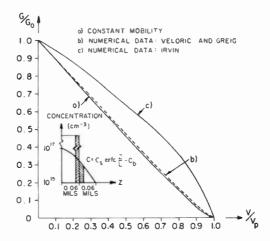

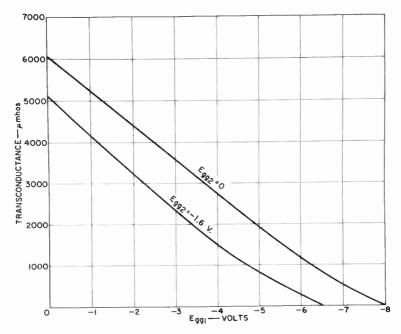

## SURFACE PREPARATION