# THE BELL SYSTEM TECHNICAL JOURNAL

DEVOTED TO THE SCIENTIFIC AND ENGINEERING

ASPECTS OF ELECTRICAL COMMUNICATION

Volume 54

December 1975

Number 10

Copyright @ 1975, American Telephone and Telegraph Company. Printed in U.S.A.

## Quasi-Optical Polarization Diplexing of Microwaves

By T. S. CHU, M. J. GANS, and W. E. LEGG (Manuscript received July 17, 1975)

The feasibility of a microwave quasi-optical polarization diplexer has been demonstrated using photo-etched copper strips with thin mylar backing as a practical example. The insertion losses of the principal polarization and the cross polarization have been calculated and measured. The conducting strips must be aligned in a preferred direction, namely, perpendicular to the plane of incidence, to minimize cross-polarized radiation, whereas orientation of the plane of the grid with respect to the beam direction is not restricted. The measured cross-polarized radiation agrees with predictions from simple theoretical models of a magnetic current sheet for the transmission mode and an electric current sheet for the reflection mode. This type of diplexer has been successfully employed in studying the polarization properties of the 20-GHz signal from the ATS-6 satellite.

### I. INTRODUCTION

To achieve frequency reuse by employing orthogonal polarizations in a radio communication system, it is essential to avoid cross polarization in the feed patterns that illuminate the antennas; this relies upon the diplexing of two orthogonal polarizations with high isolation. Waveguide-type polarization couplers perform diplexing well where a carrier with an associated bandwidth of about 10 percent is involved. However, it is difficult to provide a low-loss ( $\lesssim 0.1~\mathrm{dB}$ ) waveguide diplexer to separate effectively and simultaneously the two polarizations in each of two widely separated common carrier bands, such as 18 and 30 GHz. The difficulty stems from the vulnerability of an oversized

waveguide to higher-order modes in the higher-frequency band. Contamination by only 1 percent of the power in higher-order modes may cause unacceptable cross-polarized radiation in the feed.

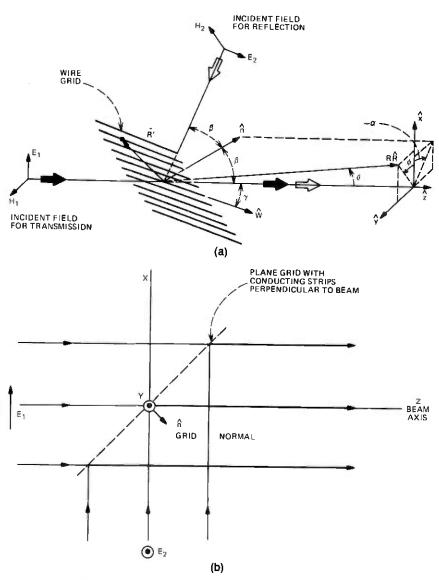

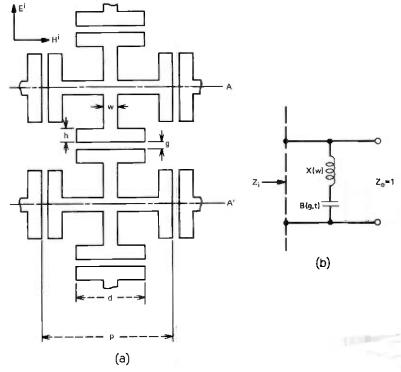

The necessity for overcoming this problem has led to the suggestion of using a closely spaced wire grid as a quasi-optical polarization diplexer. The purpose of this paper is to describe feasibility studies of this quasi-optical approach. Not only should the insertion loss be small and the feed pattern distortion slight in the principal polarization, but minimization of the cross-polarized radiation should also be achieved. Our measurements have shown that the wires must be oriented in a preferred direction to minimize the cross-polarized radiation. This property is explained theoretically by utilizing a magnetic current sheet for transmission through the grid and an electric current sheet for reflection from the grid. This preferred direction requires that the wires be perpendicular to the plane of incidence determined by the beam axis and the grid normal, as shown in Fig. 1b. One notes that the classical application of a polarizer, which consists of a wire grid parallel to an aperture plane, always satisfies this condition.

In Section II we calculate the insertion loss and cross-polarized radiation using simple theoretical models. Section III describes the measurements and the comparison between the calculated and measured cross-polarized radiation of wire grids in various configurations. Section IV discusses applications and includes concluding remarks.

To avoid confusion about the definition of cross polarization, the following two explicit expressions

$$\hat{p}_1 = \hat{\theta}\cos\phi - \hat{\phi}\sin\phi \tag{1}$$

$$\hat{p}_2 = \hat{\theta} \sin \phi + \hat{\phi} \cos \phi \tag{2}$$

are defined as the two orthogonal polarization vectors which are the cross polarization of each other. The carat " indicates unit vector, and  $(\theta, \phi)$  are spherical coordinates as shown in Fig. 1a;  $\hat{p}_1$  and  $\hat{p}_2$  within the immediate vicinity of the Z axis are in the nominal X and Y directions, respectively. The usual antenna pattern measurements yield directly the patterns for the two polarization components under this definition. If a feed pattern with the polarization vector (1) or (2) (often called a balanced-feed radiation<sup>2</sup>) illuminates a paraboloid with its axis oriented in the Z direction, the reflected field in the aperture of the paraboloid is free of cross polarization.

### II, THEORETICAL CALCULATIONS

### 2.1 Insertion losses

Implementation of quasi-optical polarization diplexers requires prediction of the insertion losses for both the principal and the unwanted

Fig. 1—(a) Geometry of a quasi-optical polarization diplexer. (b) Preferred configuration of quasi-optical polarization diplexing.

cross polarization. If the polarization grid is made of uniformly spaced copper strips with a thin mylar backing, the calculation is facilitated by the equivalence between the periodic grating and the capacitive diaphragm in a parallel-plate waveguide. Neglecting the effect of the thin mylar layer, the power reflection coefficient for an incident wave

polarized perpendicular to the strips is approximately given by<sup>3,4</sup>

$$R_{\perp} = \frac{B^2 \cos^2 \theta}{4 + B^2 \cos^2 \theta},\tag{3}$$

where

$$B = \frac{4b}{\lambda} \ln \sec \left( \frac{\pi d}{2b} \right)$$

is the shunt susceptance, b the grating period, d the width of the conducting strip,  $\lambda$  the wavelength, and  $\theta$  the angle of incidence between the direction of propagation and the normal to the grating plane. Equation (3)\* is based upon the low-frequency approximation  $(b \ll \lambda)$  for a grating of infinitely thin perfectly conducting strips. Using Babinet's principle, the power transmission coefficient " $T_{11}$ " for an incident wave, polarized parallel to the plane determined by the strip and the propagation direction, is also approximately given by eq. (3) provided the strip width d in the expression for B is replaced by the spacing (b-d).

If we employ the numerical value, b = 0.5 mm, d = 0.2 mm,  $\lambda = 1.05$  cm, and  $\theta = 45^{\circ}$ , as used in the experiment later, substitution into eq. (3) yields the insertion loss of the cross polarization

$$-10 \log_{10} R_1 = 36.8 \text{ dB}$$

$-10 \log_{10} T_{11} = 28.8 \text{ dB},$

which is equivalent to an insertion loss of only 0.001 dB and 0.006 dB for the transmitting and reflecting principal polarizations, respectively. Typically, the cross polarization in a Cassegrain feed aperture that illuminates a polarization diplexer is of the order of -20 dB or less; thus, the improvement provided by use of a quasi-optical polarization diplexer reduces the residual cross-polarized components in the grid aperture to negligible values.

However, the residual cross polarization discussed above is only part of the possible cross-polarized radiation; the following calculations show that the co-polarized field in the grid aperture may also give rise to off-axis cross-polarized radiation if the strips are not oriented in a preferred direction.

\*Equation (3) is known to be accurate when the strips are parallel to the plane of incidence for all strip widths. However, to the authors' knowledge, the rigorous

demonstration, in the literature, of its accuracy for other strip directions is restricted to the cases  $(b-d)/b \ll 1$ , or  $d/b \ll 1$ .

Tograms the cases  $(b-d)/b \ll 1$ , or  $d/b \ll 1$ .

Tograms the cases  $(b-d)/b \ll 1$ , or  $d/b \ll 1$ .

Therefore, the grid was designed to have both copper strip width and gap spacing equal to 0.25 mm. However, this specification was close to the resolution limit of the fabrication process in use at the time, which resulted in a grid with the above massured dimensions. sulted in a grid with the above measured dimensions.

### 2.2 Magnetic current sheet

For the case of transmission through an arbitrarily oriented wire grid, a magnetic-current-sheet model is used to calculate the radiation.

If a wire grid is placed in front of a radiating aperture that produces a wave collimated in the Z direction, the on-axis radiation is linearly polarized perpendicular to the conducting direction of the wire grid. We shall find the polarization properties of the off-axis radiation.

Let the plane of the wire grid be oriented in an arbitrary direction, as shown in Fig. 1a, with the following unit normal

$$\hat{n} = \hat{x} \sin \beta \cos \alpha + \hat{y} \sin \beta \sin \alpha + \hat{z} \cos \beta. \tag{4}$$

In order that an incident electric field,  $E_1 = E_1 \hat{x}$ , may pass freely through the wire grid, the direction of the conducting wires

$$\hat{w} = \sin \gamma \, \hat{y} + \cos \gamma \, \hat{z} \tag{5}$$

must be the same as that of the equivalent magnetic current density  $2\hat{n} \times E_1$  (see the appendix):

$$\hat{n} \times \mathbf{E}_{1} = E_{1} \sqrt{\cos^{2} \beta + \sin^{2} \beta \sin^{2} \alpha} \left[ \frac{\cos \beta \hat{y}}{\sqrt{\cos^{2} \beta + \sin^{2} \beta \sin^{2} \alpha}} - \frac{\sin \beta \sin \alpha \hat{z}}{\sqrt{\cos^{2} \beta + \sin^{2} \beta \sin^{2} \alpha}} \right], \quad (6)$$

i.e.,

$$\sin \gamma = \frac{\cos \beta}{\sqrt{\cos^2 \beta + \sin^2 \beta \sin^2 \alpha}}$$

and

$$\cos \gamma = \frac{-\sin \beta \sin \alpha}{\sqrt{\cos^2 \beta + \sin^2 \beta \sin^2 \alpha}}.$$

The far-zone electric-field radiation of a magnetic current sheet can be written

$$\mathbf{E}_{1} = -\frac{jk}{2\pi R} e^{-jkR} \int \left[ \hat{R} \times (\hat{n} \times \mathbf{E}_{1}) \right] e^{jk\mathbf{R}' \cdot \hat{R}} dA, \qquad (7)$$

where k is the free-space phase constant, and R and  $\hat{R}$  are the distance to the far-field point and the corresponding unit direction vector. The points on the magnetic current sheet are defined by R'. The polarization is determined by the bracketed vector product in eq. (7),

$$\mathbf{P}_{1} = \hat{R} \times (\hat{n} \times \mathbf{E}_{1}) = E_{1} \sqrt{\cos^{2} \beta + \sin^{2} \beta \sin^{2} \alpha} \left[ \hat{\theta} (-\cos \phi \sin \gamma) + \hat{\phi} (-\sin \theta \cos \gamma + \cos \theta \sin \phi \sin \gamma) \right].$$

(8)

The dot product of eqs. (1) and (8) gives the principal polarization component

$$\mathbf{P}_1 \cdot \hat{\mathbf{p}}_1 = -E_1 \cos \beta [1 - \sin^2 \phi (1 - \cos \theta) - \sin \theta \sin \phi \cot \gamma]. \quad (9)$$

If we substitute the above product for the bracket in eq. (7), it is seen that the on-axis radiation is the same as that without the wire grid, while the off-axis radiation is only slightly perturbed. Here the factor  $\cos \beta$  accounts for the larger slanted area of the grid.

Now the dot product of eqs. (2) and (8) gives the cross-polarization component

$$\mathbf{P}_1 \cdot \hat{\mathbf{p}}_2 = -E_1 \cos \beta [\sin \phi \cos \phi (1 - \cos \theta) + \sin \theta \cos \phi \cot \gamma]. \tag{10}$$

The cross polarization on axis vanishes, as expected. When the direction of the conducting wire is perpendicular to the beam axis, i.e.,  $\gamma = 90^{\circ}$ , only second-order cross polarization, as represented by the first term in eq. (10), is present with maxima in the  $\phi = 45^{\circ}$  planes. This second-order cross polarization is negligibly small for narrow feed patterns. However, this residue can become a considerable item for broad feed patterns, as will be demonstrated by an experiment described later.

When the direction of the conducting wire is not perpendicular to the beam axis, i.e.,  $\gamma \neq 90^{\circ}$ , the second term in eq. (10) represents first-order cross-polarization lobes with maxima in the  $\phi = 0$  plane. This term is kept small if both  $\theta$  and  $(90^{\circ} - \gamma)$  are small. Therefore, fine adjustment to reduce the residual cross polarization can be accomplished by rotation of the grid in its own plane in the case of a narrow feed pattern.

### 2.3 Electric current sheet

Next, consider the case of reflection from the wire grid. The reflected field is entirely due to the fields radiated by electric currents flowing in the wires. If the grid is fine enough, these currents will flow only in the direction of the wires. Thus, we may use an electric current sheet model to compute the field reflected from the wire grid. To obtain perfect reflection from the grid, the direction of the conducting wires must be the same as the induced electric current direction  $\hat{n} \times H_2$ , where  $H_2$  is the incident magnetic field for this case. The far-zone electric field of an electric current sheet can be written

$$\mathbf{E}_{2} = \frac{jkZ_{0}}{2\pi R} e^{-jkR} \int \{\hat{R} \times [\hat{R} \times (\hat{n} \times \mathbf{H}_{2})]\} e^{jk\mathbf{R}' \cdot \hat{R}} dA, \qquad (11)$$

where  $Z_0$  is the free-space impedance. The polarization is determined

1670 THE BELL SYSTEM TECHNICAL JOURNAL, DECEMBER 1975

by the vector product inside the bracket in eq. (11):

$$\mathbf{P}_{2} = \hat{R} \times \{\hat{R} \times (\hat{n} \times \mathbf{H}_{2})\} = |\hat{n} \times \mathbf{H}_{2}| [\hat{\theta}(\sin \theta \cos \gamma - \cos \theta \sin \phi \sin \gamma) + \hat{\phi}(-\cos \phi \sin \gamma)]. \quad (12)$$

The above polarization is orthogonal to that of eq. (8). The principal and cross-polarization components are obtained by the dot products of eq. (12) with eqs. (2) and (1), respectively.

$$\mathbf{P}_2 \cdot \hat{p}_2 = -H_2 \cos \beta [1 - \sin^2 \phi (1 - \cos \theta) - \sin \theta \sin \phi \cot \gamma]$$

(13)

$$\mathbf{P}_2 \cdot \hat{p}_1 = H_2 \cos \beta [\sin \phi \cos \phi (1 - \cos \theta) + \sin \theta \cos \phi \cot \gamma]. \tag{14}$$

Here the relation  $|\hat{n} \times \mathbf{H}_2| \sin \gamma = H_2 \cos \beta$  follows the symmetry with respect to  $\hat{n}$  between the incident wave and reflected wave of which the magnetic field is equal to  $H_2\hat{x}$ .

Since eqs. (13) and (14) are identical to eqs. (9) and (10) except for a proportionality constant, the properties of the off-axis cross-polarized radiation described in the previous case are also valid for this orthogonal case in reflection.

### III. EXPERIMENT

### 3.1 Insertion loss

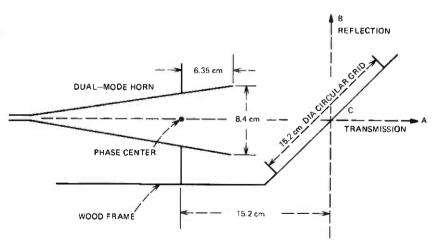

The insertion loss of the combinations of a dual-mode horn and a wire grid were measured at 28.5 GHz and 19 GHz in both transmission and reflection. Figure 2 shows the sketch of the 28.5-GHz experimental model. The dual-mode horn has been described elsewhere. The wire grid was made by photo-etching a copper-covered mylar sheet; copper

Fig. 2-Schematic of experimental assembly for 28.5 GHz.

strips 0.2 mm wide and 0.018 mm thick are spaced 0.3 mm apart on a mylar sheet 0.013 mm thick. The grid, mounted in a circular wooden rim, can be rotated in its own plane, which is oriented at 45° with respect to the horn aperture. The 19-GHz experiment uses a scaled dual-mode horn and 24.7-cm-diameter circular grid with the same copper strips and the same mylar sheet described earlier.

The measured minimum insertion loss on axis, for both transmission and reflection, was found to be only about 0.1 dB for the principal polarization; the discrepancy with the calculated 0.001 and 0.006 dB can be explained by measuring error and slight pattern distortion due

to diffraction around the grid.

The maximum insertion loss of the cross-polarized field, on axis, at 19 and 28.5 GHz for both transmission and reflection is shown in Table I. The symbols  $\parallel$  and  $\perp$  indicate that the grid wires are parallel and perpendicular, respectively, to the plane of incidence.

The measured data are only in qualitative agreement with the approximate prediction from eq. (3). However, the effect of the mylar sheet (0.013 mm thick with a dielectric constant of 3), imperfect polarization of the horn radiation, and diffraction around the grid have been neglected in the approximate calculation. It was observed that the measured insertion loss of the cross polarization depends somewhat upon the spacing between the horn and the grid.

### 3.2 Radiation patterns at 28.5 GHz

The measured cross polarization in the radiation patterns is found to be negligible if the conducting strips are aligned in the preferred direction normal to the beam. But for the conducting strips in non-preferred directions, such as those parallel to the plane of incidence, maximum cross-polarized radiation is obtained in the transverse planes—AC for transmission and BC for reflection—both perpendicular to the plane of Fig. 2. To illustrate the predictions of the theoretical models in the preceding section, we present the measured

Table 1 — Measured insertion loss of cross-polarized fields

| Grid-Wire<br>Position | 28.5 GHz               |                  | 19 GHz             |                  |

|-----------------------|------------------------|------------------|--------------------|------------------|

|                       | Transmission           | Reflection       | Transmission       | Reflection       |

| *<br>                 | 24 dB<br>28 dB<br>28.8 | 25<br>30<br>36.8 | 32.5<br>38<br>32.3 | 30<br>34<br>40.3 |

<sup>\*</sup> Conducting strips are parallel to the plane of incidence.

† Conducting strips are perpendicular to the plane of incidence.

transverse plane patterns at 28.5 GHz for four combinations of horn polarization and conducting strip directions.

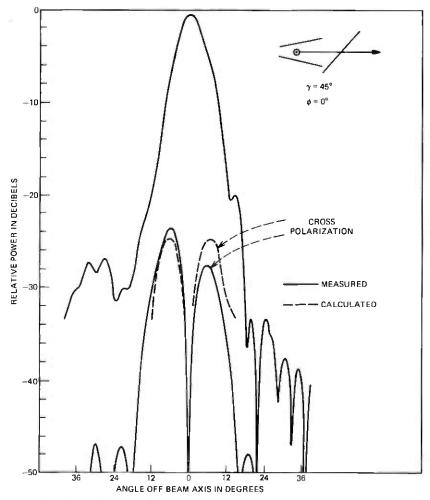

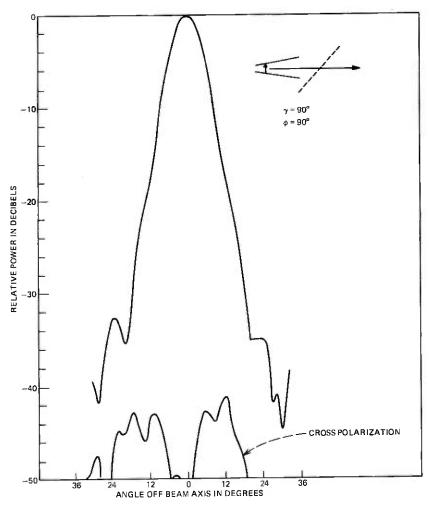

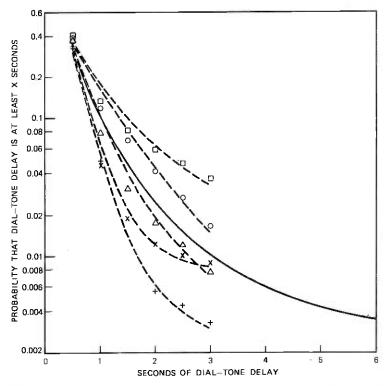

The transverse plane patterns in Figs. 3 and 4 were measured with the radiation transmitted through the grid. In Fig. 3 the horn polarization is perpendicular to, and the conducting strips parallel to, the plane of Fig. 2. The average of the cross-polarization lobe maxima is about 20 dB below that of the principal polarization in the same direction ( $\theta = 6^{\circ}$ ), and agrees well with the prediction of eq. (10) [relative to eq. (9) with  $\gamma = 45^{\circ}$ ] as shown by the dotted curves. In Fig. 4,

Fig. 3—Radiation patterns of a transmitting grid at 28.5 GHz with conducting strips parallel to the plane of incidence.

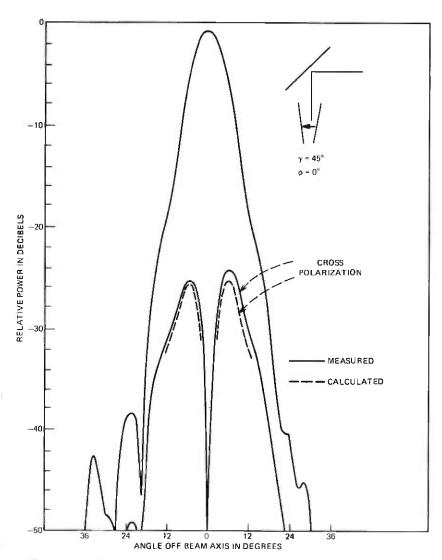

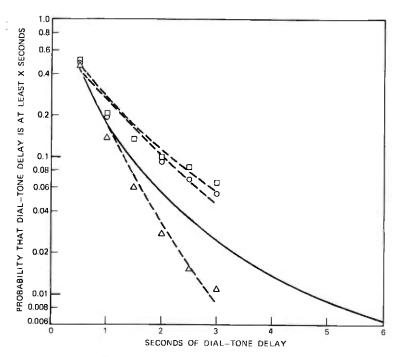

Fig. 4—Measured radiation patterns of a transmitting grid at 28.5 GHz with conducting strips perpendicular to the plane of incidence.

the horn polarization is parallel to, and the conducting strips perpendicular to, the plane of Fig. 2. The measured cross polarization of less than -40 dB essentially confirms the theoretical prediction of negligible cross polarization from eq. (10) ( $\gamma = 90^{\circ}$ ), since the measuring accuracy of the cross-polarization level is reliable down to about -40 dB.

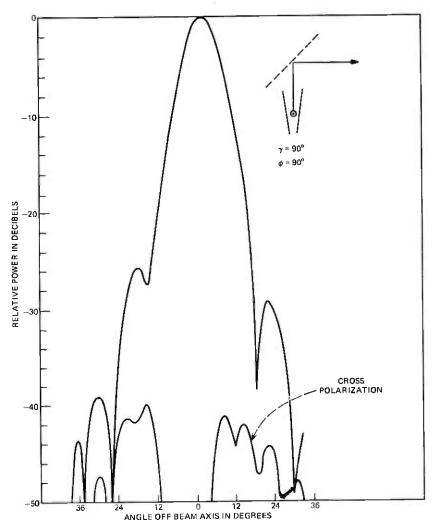

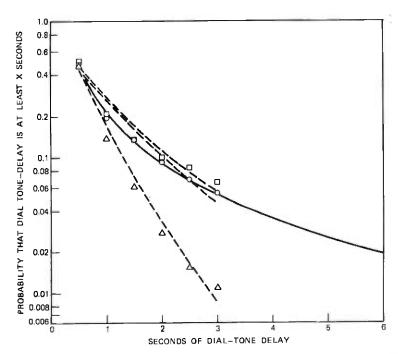

The transverse plane patterns in Figs. 5 and 6 were measured with the radiation reflected from the grid. In Fig. 5 both the horn polarization and the conducting strips are parallel to the plane of Fig. 2,

Fig. 5—Radiation patterns of a reflecting grid at 28.5 GHz with conducting strips parallel to the plane of incidence.

and the measured cross polarization is essentially the same as that of the transmitting case in Fig. 3. In Fig. 6, both the horn polarization and the conducting strips are perpendicular to the plane of Fig. 2, and the measured cross polarization of less than -40 dB is similar to that of Fig. 4. Thus, the results show that in employing quasi-optical polarization diplexers the off-axis cross-polarized radiation

Fig. 6—Measured radiation patterns of a reflecting grid at 28.5 GHz with conducting strips perpendicular to the plane of incidence.

can be suppressed only if the conducting wires are perpendicular to the beam (i.e., perpendicular to the plane of incidence).

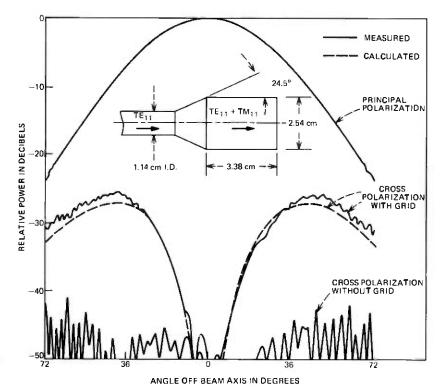

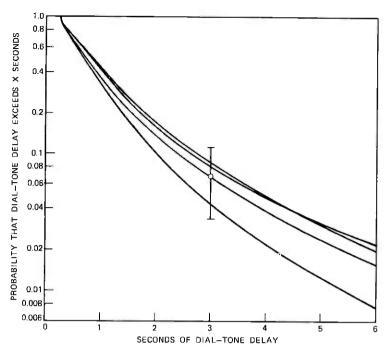

Owing to limitation of the measuring accuracy, it is difficult to measure the second-order cross polarization, the  $(1-\cos\theta)$  term in eqs. (10) and (14), of the wire grid for narrow feed patterns. Therefore, we conducted an experiment with a broad feed pattern to check this term, which grows rapidly when  $\theta$  increases. The radiation patterns

Fig. 7—Radiation patterns of a small dual-mode circular aperture feed  $(D/\lambda=1.39$  at 16.5 GHz).

of a small dual-mode horn<sup>6</sup> (see inset in Fig. 7) were measured with and without the wire grid.

In the absence of the grid, the measured 45° plane patterns of principal and cross polarization are as shown in Fig. 7. The measured patterns in other planes (not shown) exhibited circular symmetry in the co-polarized radiation pattern, and less than -40 dB in cross polarization everywhere. When the small dual-mode aperture was covered by a wire grid, the measured pattern in co-polarization remains essentially the same as without the grid; however, the cross polarization in the  $\phi = 45$ ° plane rises to -26 dB as shown in Fig. 7. The calculated cross polarization, which is plotted as a dotted curve, shows good agreement with the measured pattern. The cross-polarized radiation of a small grid-covered aperture is similar to that of a dipole.

Thus, the above results demonstrate that the wire grid is a good polarizer for large apertures, whereas improper use of the wire grid can even enhance the cross-polarized radiation of a small aperture.

### IV. DISCUSSION

It has been observed<sup>2</sup> that there will be no cross polarization in the main reflector aperture of an offset near-field Cassegrainian antenna provided no cross polarization illuminates the subreflector. This ideal condition can be approximately realized by application of a quasi-optical polarization diplexer to the feed of an offset Cassegrainian antenna with large effective F/D ratio. The quasi-optical polarization diplexer can also be used on a symmetrical Cassegrainian antenna as demonstrated by its application in an earth-station receiver<sup>7,8</sup> for the 20-GHz ATS-6 signal.

The basic philosophy of the quasi-optical polarization diplexer can be simply stated as a cleaning up of the two orthogonal polarizations simultaneously just before illuminating the subreflector. This cleaning process is especially desirable if the feed is an offset reflector with relatively small F/D ratio. But the conducting wires must be oriented in a preferred direction, perpendicular to the plane of incidence, to avoid the off-axis cross-polarized radiation. For the broad feed pattern of a small dual-mode aperture, the second-order cross-polarized radiation from a classical polarizer may exceed that of the dual-mode aperture without the polarizer. The accuracy of the theoretical predictions demonstrates the utility of equivalent current sources for such analyses.

To avoid excessive spill-over loss and pattern distortion, the quasi-optical diplexer should be made conservatively large, typically with edge illumination less than -20 dB. The main disadvantages of quasi-optical feed systems appear to be bulkier volume and heavier weight compared with conventional waveguide diplexing feed systems, especially when both polarization and frequency diplexing are performed by quasi-optical components. But these components have an advantage in handling high power without difficulty. Equation (10) indicates that fine tuning ( $\gamma \approx 90^{\circ}$ ) of the residual polarization response may be accomplished by rotation of the grid in its own plane.

### **APPENDIX**

To calculate the field transmitted through the wire grid, a magnetic current equivalent source is chosen, the choice being governed by the following considerations.

Given the tangential electric and/or magnetic field on the bounding surface of a source-free region, we may place equivalent sources on the bounding surface to correctly reproduce the original field in the source-free region:<sup>9</sup>

(i) Magnetic current:  $K = E_t \times \hat{n}$ , backed by a perfect electric conductor on the bounding surface.

(ii) Electric current:  $J = \hat{n} \times H_i$ , backed by a perfect magnetic conductor on the bounding surface.

(iii) Combination:

$$\begin{cases} \mathbf{K} = \mathbf{E}_t \times \hat{n}, \text{ magnetic current} \\ \mathbf{J} = \hat{n} \times \mathbf{H}_t, \text{ electric current} \end{cases}$$

operating in free space.

All three equivalent sources give identical results if they are based on the true fields,  $\mathbf{E}_t$  and  $\mathbf{H}_t$ . However, in the case of transmission through a grid, we do not know the true magnetic field  $\mathbf{H}_t$  on the source-free side of the grid. If the polarizer is fine enough, one can be sure, though, that the tangential electric field is perpendicular to the wires. Thus, the field transmitted through the grid can be predicted most accurately by the magnetic current equivalent source backed by an electric conducting plane on the grid. Since a tangential magnetic current imaged in an electric conducting plane is equal to itself, we may include the effect of the electric conducting plane by using twice the magnetic current,  $2\mathbf{K}$ , operating in free space.

The far field radiated by the magnetic current density, 2K, in free space is

$$\mathbf{E}_{1} = -\frac{jk}{4\pi R} e^{-jkR} \int_{\substack{\text{grid}\\\text{gaps}}} \left[ (2\mathbf{K}) \times \hat{R} \right] e^{jk\mathbf{R}' \cdot \hat{R}} dA. \tag{15}$$

If the grid spacing is very small compared with wavelength, then, as the magnetic current  $2\mathbf{K} = 2\mathbf{E}_t \times \hat{n}$  varies from zero on the grid wires to maximum in the space between, the other terms in the integrand of eq. (15) are essentially constant. Thus, we may replace the fluctuating  $\mathbf{K}$  with its average value,  $\mathbf{K}_{avg}$ ,

$$\mathbf{E}_{1} = -\frac{jk}{4\pi R} e^{-jkR} \int \left[ (2\mathbf{K}_{avg}) \times \hat{R} \right] e^{jkR' \cdot \hat{R}} dA.$$

(16)

Although we know the direction of K, we do not know its magnitude unless the reflection coefficient of the grid is known. In the usual case, the grid is designed to introduce negligible insertion loss for the desired polarization, whence  $E_1$  on axis should equal that present when no grid is used. In this case, the magnitude of  $2K_{avg}$  would have to be such that

$$2\mathbf{K}_{\text{avg}} = 2\mathbf{E}_1 \times \hat{n} \text{ (negligible insertion loss)}$$

(17)

in order that eq. (16) will result in the correct on-axis value for  $E_1$ . By substituting eq. (17) into eq. (16), we arrive at eq. (7), the desired equation for computing the field transmitted through the wire grid.

### REFERENCES

A. C. Ludwig, "The Definition of Cross Polarization," IEEE Trans., AP-21 (January 1973), pp. 116-119.

T. S. Chu and R. H. Turrin, "Depolarization Properties of Off-Set Reflector Antennas," IEEE Transactions, AP-21 (May 1973), pp. 339-345.

R. E. Collin, Field Theory of Guided Waves, New York: McGraw-Hill, 1960, p. 366.

J. R. Wait, "Reflection at Arbitrary Incidence from a Parallel Wire Grid," Appl. Sci. Res., Sec. B, 4, No. 6, 1954-1955, pp. 393-400.

M. J. Gans and R. A. Semplak, "Some Far-Field Studies of an Offset Launcher," B.S.T.J., 54, No. 9 (September 1975), pp. 1319-1340.

R. H. Turrin, "Dual Mode Small-Aperture Antennas," IEEE Trans. Antennas and Propagation, AP-15 (March 1967), pp. 307-308.

D. A. Gray, "Depolarization of ATS-6 Satellite 20 GHz Beacon Transmitted Through Rain," presented at the 1975 USNC-URSI Spring Meeting, June 3-5, Urbana, Illinois.

R. H. Turrin, personal communication.

V. H. Rumsey, "Some New Forms of Huygens' Principle," IRE Transactions, AP-7 (Suppl.) (December 1959), p. S103.

### Material Structure of Germanium-Doped Optical Fibers and Preforms

By H. M. PRESBY, R. D. STANDLEY, J. B. MacCHESNEY, and P. B. O'CONNOR

(Manuscript received July 8, 1975)

The structural characteristics of preforms and optical fibers fabricated by modified chemical vapor deposition were studied by optical, interference, and scanning electron microscopy. It was observed that the structural features resulting from the deposition process are preserved through subsequent processing and appear in the fiber with the exception of a region at the center of the fiber. Here, selective evaporation of dopant material from the inner surface of the deposit results in a refractive index depression on the axis of the optical waveguide.

#### I. INTRODUCTION

The chemical vapor deposition process, in which oxides are deposited and simultaneously fused on the inner surface of a fused silica tube, has become a valuable technique for fabricating low-loss<sup>1,2</sup> and graded-index optical fibers.<sup>3</sup> In modifications and refinements of this technique, higher depositional rates and very low-loss single-mode fibers<sup>4</sup> have also been achieved.

An important question that arises in utilizing this process concerns the correlation of the deposited material structure in the preform to that in the resulting optical fiber. Can one be confident, for example, that the same distribution of refractive index that is introduced into the preform by changing the material composition of the deposited layers exists in the fiber pulled from this preform? This determination is necessary if one is to reliably fabricate those graded-index profiles required to achieve a minimum of pulse dispersion. This is due to the fact that the shaping of the index profile is quite critical because the reduction-in-pulse-dispersion-vs-profile curves exhibit a singularity-like behavior in the region of the optimum index distribution.

Evidence for the preservation of the deposited profile has recently been reported, based on the observation of a linear increase in refractive index in a fiber which was pulled from a preform in which the dopant concentration was increased in the same manner.<sup>7</sup> In this paper, we present results of optical, interference, and scanning electron microscope studies<sup>8</sup> of a graded, near-parabolic, index fiber and preform as further aid in understanding the transition of material from the preform to the fiber state. A main conclusion of this study is that the structural features resulting from the preform deposition process are preserved and, after suitable scale transformation, appear in the fiber. Due consideration should therefore be given to depositional characteristics that may ultimately affect transmission behavior.

### II. OBSERVATIONS

The preform originates from an approximately  $\frac{1}{2}$ -m-long 12 × 14mm fused-quartz tube which is collapsed into a rod after the deposition process. In the structure studied here, the deposition started with an initial layer of borosilicate to prevent impurity diffusion into the core. This layer was deposited with 41 traversals of a oxyhydrogen burner which provides the heat to react the BCl3, SiCl4, and O2 starting materials. The core deposition process consists of systematically increasing the flow of GeCl4 while holding the flows of SiCl4 and BCl3 constant, thus producing an increasing GeO2 content and associated increased refractive index with increasing deposit thickness. The GeCl<sub>4</sub> flow was increased 11 times, in such a manner as to produce a near-parabolic index variation from the cladding interface to the center of the core. The number of torch traversals during each of the 11 steps was controlled to make the thickness of each step approximately equal. After collapse, a length of preform was pulled into a fiber with an overall diameter of ~100 µm by the use of an electric furnace.

A slice transverse to the axis of the remaining length of preform was made and then polished to a thickness of approximately 10 mills for interference and optical microscopic observations. Transverse samples of the fiber were also prepared for interference-microscope and scanning-electron-microscope studies. In the latter case, after a short length of fiber is scored and broken to ensure a flat end, it is etched in a 25-percent solution of hydrofluoric acid for several minutes and then flash-coated. The last step is performed to prevent charge build-up on the sample during scanning-electron microscope observations.

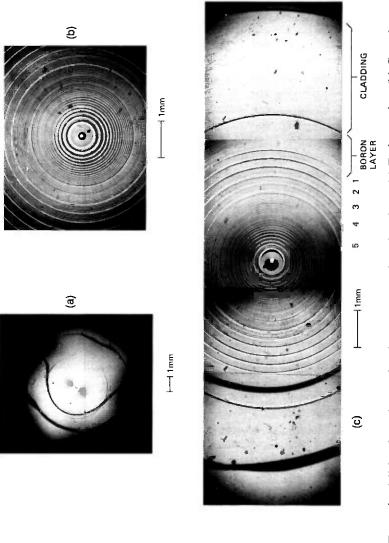

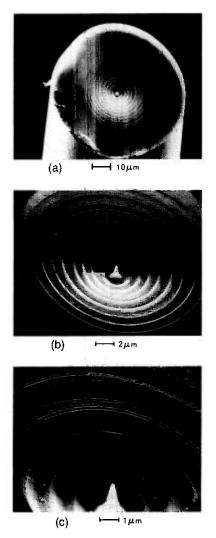

An overall view of the preform sample observed with conventional optical microscopy is shown in Fig. 1a. The sample is  $\sim$ 7.2 mm in diameter with a core diameter of 4 mm. The irregular shape is due to pieces of the cladding which broke off during the cutting and polishing procedure. It should be noted that the preform is under considerable stress because of the difference in the expansion coefficients of the

Fig. 1—Transmitted light photomicrographs of transverse section of preform. (a) Entire section. (b) Central core region. (c) Entire section at higher magnification.

core and the cladding. If this stress is not to be relieved by shattering upon cutting, extreme care must be used. In this case, the preform was cut with a diamond wire saw with controlled lubrication. Even so, the preform did crack, as seen by the dark curved line in the left-hand section of the sample.

Figures 1b and 1c obtained by optical microscopy show expanded views of the central region and of a portion of the entire cross section. The cladding, the borosilicate layer, and the first five germania-borosilicate steps are labeled. The regions between the steps are quite distinct, as are the individual layers within each step. Each of these layers, as noted, corresponds to a traversal of the oxyhydrogen burner along the tube. During step 3, for example, the GeCl<sub>4</sub> flow was maintained constant for nine traversals of the burner, producing the nine layers observed in Fig. 1c.

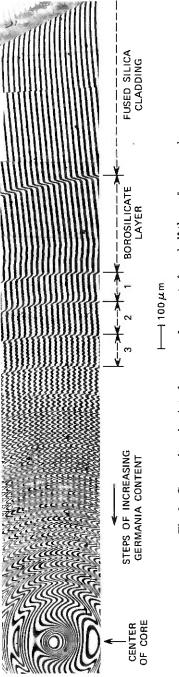

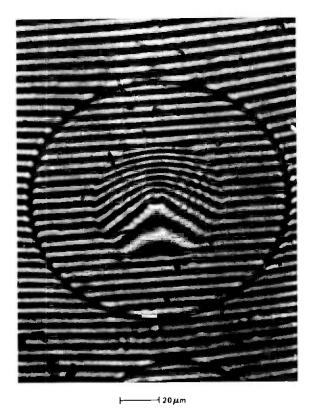

An expanded view of one-half the preform sample as observed by interference microscopy is shown in Fig. 2. The refractive-index difference between the cladding and a point in the core of the preform is given by the fringe displacement at that point times the wavelength of observation and divided by the thickness of the sample. One observes the straight parallel fringes in the fused silica cladding on the right indicating the uniform composition of this region, as expected. The drop in the level of the fringes indicates the termination of the cladding and the start of the borosilicate step that has a lower index of refraction than pure fused silica. Again, in this region, which extends for about 375 µm, the composition is relatively uniform and no evidence is seen of the 41 layers which comprise this step. This tends to indicate that some boron diffusion occurs, smoothing out the individual layers. It does not appear, however, that boron diffuses into the cladding, as evidenced by the relatively sharp transition occurring  $\sim 10 \ \mu \text{m}$  between the cladding and this step.

At the termination of the pure borosilicate layer, germania deposition commences. The first three of these steps are labeled. Note, in particular, that step 3 exhibits nine sinusoid-like variations which, as discussed previously, correspond to nine torch traversals used in depositing this step. The reason for this index variation within each layer may be due either to a difference in composition of the particles reacting homogeneously (i.e., in the gas phase) and heterogeneously (i.e., on the surface of the tube), or to temperature variation effects, depositing different concentrations as the torch passes. These compositional variations become quite sizable as the number of layers in each step decreases towards the center of the core. Note that in all steps the integrity of these layers is maintained and that relatively sharp boundaries exist between the steps. The transitions are most

Fig. 2—Composite microinterferrogram of segment of one-half the preform sample.

clearly seen between the first few steps in which the change in germanium content is largest. These observations indicate that little, if any, germanium diffusion occurs between adjacent steps or within a given step itself.

The situation is quite different at the center of the core. Despite the fact that the germanium concentration was varied in a smoothly increasing manner in the last several steps, a large disturbance in the center is observed, with a corresponding dip in the refractive index. We believe this is due to the evaporation of germania at the inner surface of the deposit during the elevated temperatures experienced in the collapse process. The fact that the last two or three layers appear to broaden towards the center also indicates the existence of some germanium flow extending beyond the immediate central segment. It may be possible to compensate for this effect by a germanium overdoping in this region.

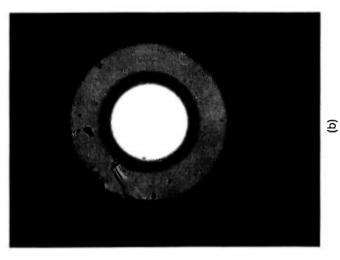

Quantitative index measurements indicate a maximum index difference between core and cladding of approximately  $\Delta n_m = 0.016$  and an index difference between the cladding and the borosilicate layer of  $\Delta n = 0.004$ . Both values are in very good agreement with the corresponding measurements made from the microinterferrogram of the fiber, which is shown in Fig. 3a, and indicate a preservation, for the most part of the material composition through the pulling process.

Note in Fig. 3a the uniform cladding containing straight parallel fringes, the subsequent drop owing to the borosilicate layer, and the gradual grading of the index profile to a maximum near the axis. The grading was near-parabolic and has been related to a reduction in pulse dispersion for this fiber. These regions are again shown in the transmitted-light photomicrograph of Fig. 3b. The core which appears as the bright central area is surrounded by the relatively dark borosilicate layer. Beyond that is the grayish cladding with an overall diameter of  $96~\mu m$ .

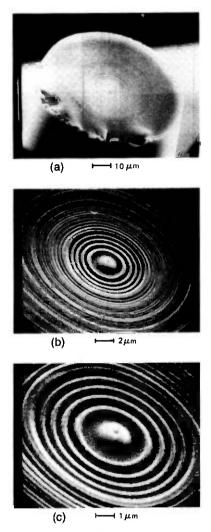

The resolution of the interference microscope is not sufficient to resolve any layer or step structure in the fiber. To obtain greater resolution, we made use of scanning electron microscopy. Preparation of the fiber samples was described previously, and results of observations are shown in Figs. 4 and 5.

Figure 4 presents three micrographs taken at increasing magnifications centered on the axis, and Fig. 5 is a composite photograph of a section of one-half the fiber at somewhat greater magnification. The main points to be noted are the preservation of the step and layer structure in the fiber and the appearance of the elevated region near the axis. This feature is a region that did not etch as rapidly as the surrounding area, because of a lack of contained dopant and agrees

I 10 km

<u>a</u>

Fig. 3—(a) Microinterferrogram. (b) Photomicrograph of fiber.

Fig. 4—Scanning-electron-beam-microscope photographs of fiber at increasing magnification.

with the preform observation of germanium departure during collapse. The appearance of the distinct step and layer structure displays the further lack of germanium diffusion even during the pulling process and indicates the maintenance of compositional and structural integrity from the deposition through the pulling process, with the exception of the central region.

We further investigated this latter region in another fiber prepared in the same manner by chemical vapor deposition. In this fiber, the

Fig. 5—Composite scanning-electron-beam-microscope photograph of segment of one-half fiber. I #

GeCl<sub>4</sub> flow was increased at each of ten steps to produce a linear variation in concentration. The number of layers in each step varied somewhat from the fiber considered above. Scanning-electron-microscope photographs of etched fiber samples are shown at increasing magnification in Fig. 6.

The depression of the index on the axis because of the loss of dopant is quite pronounced in this fiber and appears as the micron-or-so in

Fig. 6—Scanning-electron-beam-microscope photograph of fiber having linear refractive-index profile.

diameter, raised, tapered pip in the center. Note also the preservation of the distinct step and layer structure. The refractive index depression is also observed in this case in the microinterferrogram of the fiber shown in Fig. 7. It is seen as a dip in the fringe normally passing through the center of the fiber. Slight modulations of the refractive index can also be observed at each of the ten steps in this case owing to the relatively large change in germanium concentration between the steps.

It is important to note that, despite the structural features that exist on such a small scale, the losses of these fibers were less than 5 dB/km in the region of  $1.0\,\mu\text{m}$ . This is presumably due to the fact that these features are very uniform in the direction parallel to the axis of the fiber and hence do not contribute in a large way to scattering losses. Small-scale variations of such features if existing, however, could form a lower limit on losses achievable with fibers fabricated by this technique.

Fig. 7—Microinterferrogram of linear refractive-index profile fiber showing index depression in center.

In summary, structural features resulting from the preparation of both the preforms and graded-index optical fiber by the chemical vapor deposition process have been observed by optical, interference, and scanning electron microscopy. These features can be directly related to steps in the fiber fabrication. It was observed that structures present in the preform were preserved through the drawing and were present in the fiber. For instance, optical and interference observations indicated that germania concentrations varied within each deposited layer, and this variation was not substantially altered by subsequent processing steps except in the centermost layers. Here, flow of the deposit during collapse and vaporization of germania, probably as GeO, led to a depleted region of lower refractive index at the fiber center.

### REFERENCES

J. B. MacChesney, P. B. O'Connor, F. V. DiMarcello, J. R. Simpson, and P. D. Lazay, Proceedings of Xth International Congress on Glass, Kyoto, Japan, July 6, 1974, pp. 40-45.

W. G. French, J. B. MacChesney, P. B. O'Connor, and G. W. Tasker, "Optical Waveguides with Very Low Losses," B.S.T.J., 63, No. 5 (May-June 1974),

Waveguides with Very Low Losses, B.S.T.J., 83, No. 5 (May-June 1974), pp. 951-954.

J. B. MacChesney, P. B. O'Connor, and H. M. Presby, "A New Technique for the Preparation of Low-Loss and Graded-Index Optical Fibers," Proc. IEEE, 62, No. 9 (September 1974), pp. 1280-1281.

W. G. French and G. W. Tasker, "Fabrication of Graded Index and Single Mode Fibers with Silica Cores," Digest of Papers Presented at Topical Meeting on Optical Fiber Transmission, Williamsburg, Virginia, January, 1975, pp. TuA2-1 TuA2-3.

D. Gloge and E. A. J. Marcatili, "Multimode Theory of Graded-Core Fibers," B.S.T.J., 52, No. 9 (November 1973), pp. 1563-1578.

E. A. J. Marcatili, "Theory and Design of Fibers for Transmission," Digest of Papers Presented at Topical Meeting on Optical Fiber Transmission, Williamsburg, Virginia, January, 1975, pp. TuC4-1—TuC4-4.

P. B. O'Connor, H. M. Presby, J. B. MacChesney, and L. G. Cohen, to be published by J. Am. Ceram. Soc.

C. A. Burrus and R. D. Standley, "Viewing Refractive-Index Profiles and Small-Scale Inhomogeneities in Glass Optical Fibers: Some Techniques," Applied Optics, 13, No. 10 (October 1974), pp. 2365-2369.

L. G. Cohen, P. Kaiser, J. B. MacChesney, P. B. O'Connor, and H. M. Presby, "Transmission Properties of a Low-Loss Near-Parabolic-Index Fiber," Appl. Phys. Lett., 26, No. 8 (April 1975), pp. 472-474.

### An Efficient Linear-Prediction Vocoder

### By M. R. SAMBUR

(Manuscript received April 29, 1975)

A primary interest in any method for producing synthetic speech is to minimize the number of bits per second required to generate acceptable quality speech. An efficient method for transmitting the linear-prediction parameters has been found by using the techniques of differential PCM. Using this technique, speech transmission is achieved employing fewer than 1500 bits/s. Further reductions in the linear-prediction storage requirements can be realized at a cost of higher system complexity by transmission of the most significant eigenvectors of the parameters. This technique in combination with differential PCM can lower the storage to 1000 bits/s.

### I. INTRODUCTION

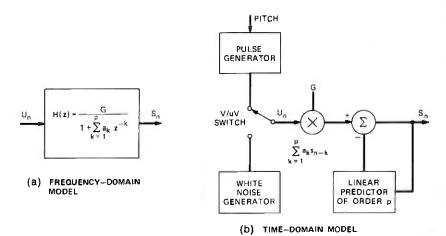

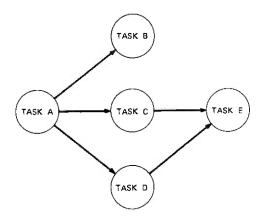

The method of linear prediction has proved quite popular and successful for use in speech compression systems.<sup>1-4</sup> In this method, speech is modeled as the output of an all-pole filter H(z) that is excited by a sequence of pulses separated by the pitch period for voiced sounds, or pseudo-random noise for unvoiced sounds. These assumptions imply that within a frame of speech the output speech sequence is given by

$$s(n) = \sum_{k=1}^{p} a_k s(n-k) + u_n,$$

where p is the number of modeled poles,  $u_n$  is the appropriate input excitation, and the  $a_k$ 's are the coefficients characterizing the filter (linear prediction coefficients). Figure 1 illustrates the frequency-domain, as well as the equivalent time-domain, model of linear-prediction speech production. To account for the nonstationary character of the speech waveform, the parameters  $a_k$  of the modeled filter are periodically updated during successive speech frames. Generation of speech in this method requires a knowledge of the pitch, the filter

<sup>\*</sup>A frame is a segment of speech thought adequate to assume stationarity of the speech process. Typical frame lengths employed range from 10 to 30 ms.

Fig. 1-Discrete model of speech production as employed in linear prediction.

parameters, and the gain of the filter (amplitude of input excitation) in each speech frame.

A primary interest in any method for producing synthetic speech is to minimize the number of bits per second needed to generate acceptable quality speech. The smaller the information storage requirements (bits per second), the more attractive the system becomes for the important applications of voice answer-back and speech transmission. To achieve the minimum storage requirement for a given system, an efficient means of quantizing the generating parameters must be determined. Using conventional pulse code modulation (PCM) techniques in which the amplitude of each parameter is uniformly quantized into  $2^B$  levels, it has been found necessary to allot at least five bits (B=5) of information for both pitch and gain and at least 11 bits for each  $a_k$ . The corresponding storage requirements for this method of quantization of the linear-prediction (LPC) parameters is unacceptable for many applications, and an improved scheme for quantizing the parameters is needed.

For the usual 12-pole linear-prediction representation, the dominant portion of storage is allotted to the filter coefficients (132 bits per frame in the PCM method of information transmission). The extremely fine quantization of the  $a_k$ 's is necessary because small perturbations in the coefficients can sometimes cause radical changes in the important pole frequencies of the modeled filter H(z) and may even cause the filter to become unstable (poles outside the unit circle). To overcome the limitations of quantizing the predictor (filter) coefficients, it has been found quite profitable to transmit different but informationally equivalent sets of parameters. <sup>4,6</sup> The most suitable parameters have

been experimentally determined to be the log-area ratio coefficients  $g_i$ . These coefficients are nonlinearly related to the filter coefficients by

$$g_i = \log \frac{1 + k_i}{1 - k_i},\tag{1}$$

where the  $k_i$ 's are termed the parcor coefficients.<sup>1,2,4,6</sup> If we denote  $a_i^{(j)}$  as the *i*th linear prediction coefficient for a *j*th-pole linear-prediction model, then

$$k_i = a_i^{(i)}. (2)$$

The parcor coefficients have the very important property that if

$$|k_i| < 1, \qquad i = 1, \cdots, p, \tag{3}$$

then it is guaranteed that the linear-prediction filter is stable.<sup>4</sup> Thus, small perturbations in the parcor coefficients or log-area coefficients will not affect the stability of the modeled filter.

Since the log-area coefficients are nonlinearly related to the filter coefficients, transmission of the log-area parameters is equivalent to a nonuniform quantization of the linear-prediction coefficients. By transmitting the log-area parameters, the number of bits allotted to the filter parameters can be effectively reduced by nearly  $\frac{1}{2}$ . In this paper, we offer two additional methods of quantization of the necessary synthesis parameters (pitch, gain, and filter coefficients) that can even further reduce the storage requirements of a linear-prediction vocoder. One proposed method of quantization uses the technique of differential PCM (DPCM) to transmit the linear-prediction parameters. This scheme exploits the fact that the LPC parameters are themselves predictable from previous samples. Using this method, speech transmission that is practically equivalent to the unquantized synthesis can be achieved using fewer than 2000 bits/s.

The second method of transmission exploits the redundancy between the linear-prediction parameters. The LPC parameters can be predicted not only from the given parameter's past values, but also in some sense from values of the other parameters. The suggested scheme involves the transmission (using DPCM techniques) of the most significant eigenvectors of the log-area parameters. For the typical speech utterance, the space of the 12 log-area coefficients can be effectively represented by only the first five or six eigenvectors. The transmission requirement for this method is fewer than 1200 bits/s.

The organization of this paper is as follows. In Section II, we briefly discuss the concept of DPCM coding. In Section III, we show that DPCM coding offers a significant improvement over PCM coding for transmission of the linear-prediction parameters. In Section IV, the results

are presented of a synthetic speech experiment using the proposed december of December of

### II. DIFFERENTIAL PULSE CODE MODULATION

The idea of differential PCM is similar in philosophy to the concept employed in linear-prediction speech analysis. In DPCM, we assume that the transmitted parameter in a given frame of interest can be estimated by a linear combination of the parameter in previous frames. If we let x, denote the value of the transmission parameter x in the rth frame (where x can represent pitch, gain, log-area coefficients, or whatever), then this assumption implies

$$x_{\tau} \approx \hat{x}_{\tau} = \sum_{i=1}^{n} b_i x_{\tau-i}, \tag{4}$$

where n is the order of the DPCM prediction analysis. The DPCM technique calls for the transmission of the difference between the predicted value  $\hat{x}_r$  and the true value  $x_r$ .

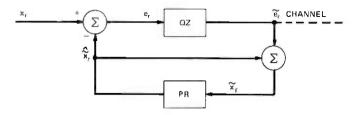

Figure 2 illustrates the structure of the DPCM coding system. In the implementation of a DPCM scheme, a feedback path around the quantizer is used to ensure that the error in the reconstructed (quantized) signal  $x_r$  is precisely the quantization error for the difference signal  $e_r = x_r - \hat{x}_r$ , where  $\hat{x}$  is the predicted value based upon the quantized signal  $x_r$ . The predictor coefficients  $b_i$  are chosen to minimize the power of the difference signal  $e_r$ . The mathematical analysis required for the solution of the optimum set of  $b_i$ 's is exactly the same as the analysis for the calculation of the linear-prediction coefficients,  $a_i$ ,  $i = 1, \dots, p$ . The determination of the  $b_i$ 's is made by solving the familiar correlation equations:

$$\sum_{i=1}^{n} b_{i} \sum_{\tau=n}^{N} x_{\tau-i} x_{\tau-k} = -\sum_{\tau=n}^{N} x_{\tau} x_{\tau-k}, \qquad 1 \leq k \leq n,$$

(5)

where N is the number of frames in the utterance.

The advantage of DPCM coding is obvious when one realizes that, if  $x_{\tau}$  can be accurately estimated from previous samples, the information necessary for transmission (as expressed by the difference signal  $x_{\tau} - \hat{x}$ ) is necessarily less than the information required for coding the signal without exploiting its predictability. The advantage of

Fig. 2—Differential PCM (Qz = quantizer; PR = predictor; =  $\hat{\bar{x}}_r = \sum_{j=1}^r b_j x_{r-j}$ ).

DPCM coding can be precisely specified by noting that, for a given fineness of quantization, the quantization error is proportional to the variance of the signal present at the quantizer. Thus, the improvement in performance (as measured by the frequently used standard of signal-to-quantization-error ratio) using DPCM strategy over straight PCM coding is given by the ratio of the variance (power) of x, to that of the difference signal

$$G = \frac{\langle x_{\tau}^2 \rangle}{\langle (x_{\tau} - \hat{x})^2 \rangle}.$$

(6)

Using the optimum predictors  $b_i$ , the resulting gain over PCM is approximately given by

$$G_{\text{opt}} = \left(1 - \sum_{k=1}^{n} \frac{b_i C_i}{C_0}\right)^{-1} = \frac{\langle x_r^2 \rangle}{\langle (x_r - \hat{x}_r)^2 \rangle}, \tag{7}$$

where

$$C_i = \sum_{r=n}^{N} x_r x_{r-i}. \tag{8}$$

For equal standards of synthetic speech quality, the gain obtained by using a draw strategy over that of PCM coding can be traded off to reduce the rate of information transmission. Of course, for G < 1, it is disadvantageous to use draw coding. However, for the transmission of parameters that are reasonably smooth in their variation from one transmission frame to the next, it is guaranteed that draw coding is superior to PCM coding. In the next section, we demonstrate the efficiency of draw techniques for the coding of the linear-prediction speech parameters.

### III. DPCM IMPROVEMENT IN CODING LPC PARAMETER

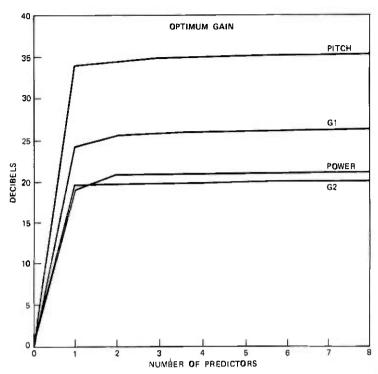

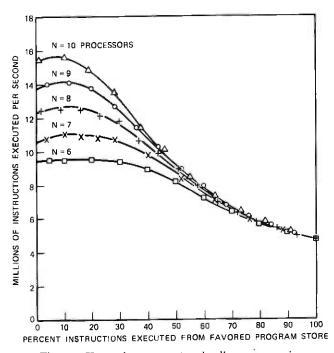

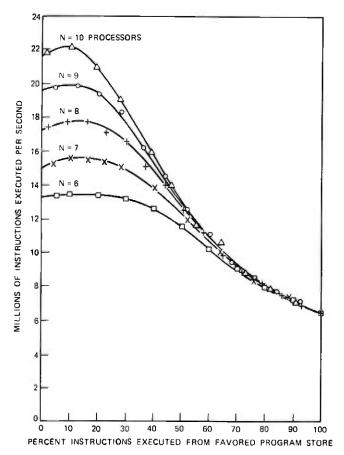

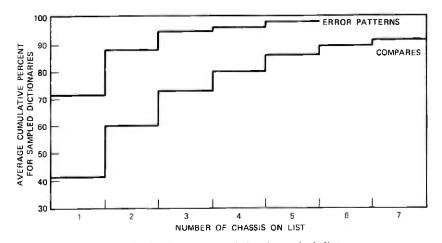

To illustrate the efficiency of DPCM techniques in the coding of the synthesis parameters, Fig. 3 shows the improvement factor  $G_{\text{opt}}$  in decibels as a function of the number of DPCM predictors. The figure

<sup>\*</sup> The gain is approximate because the effects of the quantizer in Fig. 2 are ignored.

Fig. 3— $G_{opt}$  for the sentence, "May we all learn a yellow lion roar."

shows  $G_{\text{opt}}$  for the first two log-area coefficients  $(g_1 \text{ and } g_2)$ ,\* pitch period and power<sup>†</sup> for the all-voiced utterance, "May we all learn a yellow lion roar." The improvement factor was calculated by considering each particular parameter across the entire sentence and then calculating the optimum predictors using eq. (5) and  $G_{\text{opt}}$  using eq. (7). The results depicted in Fig. 3 are for a male speaker, but the results are typical of those obtained for other male and female speakers. For the complete ensemble of parameters necessary to produce synthetic speech (12 log-area coefficients, pitch, and power), the set of improvement factors were all significantly greater than 1.

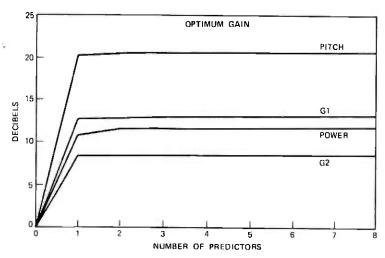

Figure 4 shows a typical plot of the improvement factor calculated for a sentence containing unvoiced sounds, "Few thieves are never

† Power is defined as the energy in the speech frame. For the synthetic system employed, it is more convenient to transmit power instead of the amplitude of the input excitation.

<sup>†</sup> Log-area coefficients were transmitted because of their optimum quantization properties.

<sup>\*</sup>The parameters were calculated at the rate of 50 samples per second. The filter parameter was calculated by the covariance method (Ref. 1), and pitch was measured by a method developed by B. S. Atal (Ref. 8).

Fig. 4—Gopt for the sentence, "Few thieves are never sent to the jug."

sent to the jug." In this sentence, the DPCM improvement over PCM coding is not as dramatic as for the all-voiced sentence. The reason for the decreased values of  $G_{\rm opt}$  is that the synthesis parameters tend to change sharply during the unvoiced-voiced transition. Thus, during the transition region there is an abrupt reduction in the correlation between successive samples, and very little information can be gained about the signal from past values. Another reason for the reduced values of  $G_{\rm opt}$  is that the variation of the LPC parameters during un-

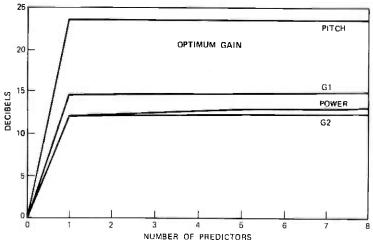

Fig. 5— $G_{\rm opt}$  for the sentence, "Few thieves are never sent to the jug." A separate DPCM analysis is used in each unvoiced and voiced segment.

voiced sounds is inherently more random than during voiced sounds and is thus less predictable. Fortunately, during unvoiced regions the quality of the synthesized speech is more tolerant to quantization noise than during voiced regions.<sup>4</sup> Thus, the diminished values of the  $G_{ont}$ 's is not as significant as might at first appear.

One method of increasing the improvement factor for utterances containing unvoiced sounds is to update the DPCM predictors whenever the spectral properties of the speech signal change from unvoiced to voiced sounds. Figure 5 shows  $G_{\rm opt}$  for the same sentences as were used to obtain the results of Fig. 4, but in this figure the optimum DPCM predictors were separately calculated for each different section of unvoiced and voiced speech. The improvement factor for this form of DPCM coding is about 5 dB better than a single calculation of the predictors. In a later section of the paper, we discuss another method for updating or adapting the DPCM predictors to the changing spectral properties of the speech signal.

### IV. SPEECH SYNTHESIS

### 4.1 Synthesizer

The improvement factors for the LPC parameters demonstrate that DPCM coding is superior to PCM coding. To confirm the results of the  $G_{\rm opt}$  experiments, a synthetic speech system was constructed in the manner illustrated in Fig. 2. To take advantage of the fact that the improvement factor saturates near n=1 (Figs. 3 and 5), only a simple first-order DPCM system was used. The optimum predictor was recomputed for each separate unvoiced and voiced region and the LPC parameters were calculated at a rate of 50 samples per second. The speech was synthesized using the formulation discussed by Atal and Hanauer. After quantization, the parameters were geometrically interpolated (linear interpolation on a logarithmic scale) to allow pitch synchronous resetting of the synthesizer.

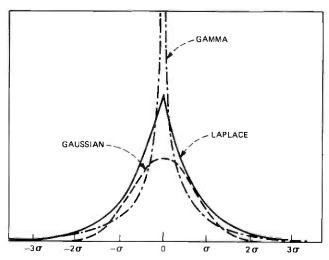

The quantizer used in the ppcm coding of the synthesis parameter was a nonuniform quantizer that was designed to exploit the properties of each parameter's error signal. An experimental investigation has indicated that the difference signal for pitch, power, and  $g_1$  are most suitably modeled by a zero mean gamma density,

$$P_{\sigma_r}(e_r) = \frac{\sqrt{k}}{2\sqrt{\pi |e_r|}} \exp(-k|e_r|),$$

(9)

where

$$\sigma = \frac{\sqrt{0.75}}{k}.$$

The higher-order log-area coefficients are more Laplacian in character:

$$P_{e_r}(e_r) = \frac{1}{2\beta} \exp\left(-\frac{|e_r|}{\beta}\right),$$

where

$$\sigma = \sqrt{2}\beta$$

.

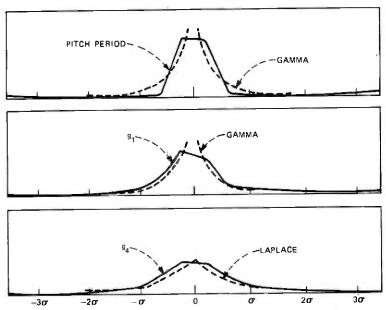

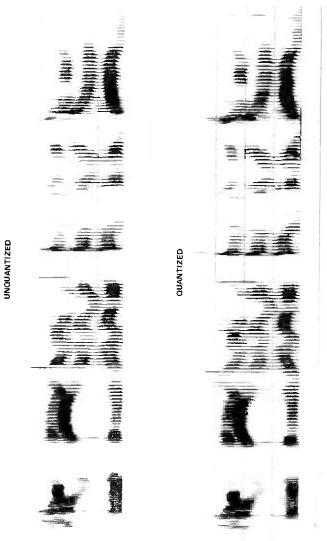

A signal with a gamma distribution is highly concentrated near its mean, but can also readily achieve values more than three standard deviations from its mean. A Laplacian signal is less concentrated than a gamma signal near its mean value. Figure 6 illustrates the statistical characteristics of a zero mean, unit standard, deviation signal with a gamma density, a Laplacian density, and a gaussian density. Figure 7 shows a comparison between the calculated distributions for the difference signal of several typical synthesis parameters and their approximated distributions.

For a gamma-behaved signal, the properties of the optimum quantizer are summarized in Table I.<sup>9</sup> The  $x_i$  values in the table define the ends of quantizer input ranges, and the  $y_i$  values are the corresponding outputs. Thus, for a two-bit quantizer, an input between 0 and 1.205 is quantized as 0.302. Similarly, an input between 0.229 and 0.588 for a four-bit scheme is quantized as 0.386. The properties of the optimum quantizer for Laplacian signals are summarized in Table II.<sup>9</sup> Included in these tables is the expected mean square between the difference

Fig. 6—Comparison of a gaussian, gamma, and Laplacian density with zero mean and unit standard deviation.

Fig. 7—Comparison between calculated density and approximated density for difference signals.

signal and the quantized difference. Thus, for a four-bit quantization of a gamma signal, the mean square error is 0.0196.

Tables I and II are constructed for signals with unit standard deviation. To obtain the levels  $y_i$  and boundaries  $x_i$  for signals with standard

Table I — Optimum quantizers for signals with gamma density  $(\mu=0, \ \sigma^2=1)$

| В                                                                       |       | 1     | 2     | 2              |                         | 3                                | 4                                                           | 1                                                                    |                                                                                                                                     | 5                                                                                                                                   |

|-------------------------------------------------------------------------|-------|-------|-------|----------------|-------------------------|----------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| i                                                                       | $x_i$ | $y_i$ | $x_i$ | $y_i$          | $x_i$                   | $y_i$                            | $x_i$                                                       | $y_i$                                                                | $x_i$                                                                                                                               | $y_i$                                                                                                                               |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | 00    | 0.577 | 1.205 | 0.302<br>2.108 | 0.504<br>1.401<br>2.872 | 0.149<br>0.859<br>1.944<br>3.779 | 0.229<br>0.588<br>1.045<br>1.623<br>2.372<br>3.407<br>5.050 | 0.072<br>0.386<br>0.791<br>1.300<br>1.945<br>2.798<br>4.015<br>6.085 | 0.101<br>0.252<br>0.429<br>0.630<br>0.857<br>1.111<br>1.397<br>1.720<br>2.089<br>2.517<br>3.022<br>3.633<br>4.404<br>5.444<br>7.046 | 0.033<br>0.169<br>0.334<br>0.523<br>0.737<br>0.976<br>1.248<br>1.892<br>2.287<br>2.747<br>3.296<br>3.970<br>4.838<br>6.050<br>8.043 |

| 16<br>MSE                                                               | 0.    | 6680  | 0.2   | 3 <b>2</b> 6   | 0.0                     | 712                              | 0.0                                                         | 196                                                                  |                                                                                                                                     | 052                                                                                                                                 |

Table II — Optimum quantizers for signals with Laplace density  $(\mu = 0, \sigma^2 = 1)$

| В                                                                                   |       | 1     | :     | 2              |                         | 3                                |                                                             | 4                                                                    | ,                                                                                                                                   | 5                                                                                                                                            |

|-------------------------------------------------------------------------------------|-------|-------|-------|----------------|-------------------------|----------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| i                                                                                   | $x_i$ | $y_i$ | $x_i$ | y,             | $x_i$                   | $y_i$                            | $x_i$                                                       | $y_i$                                                                | $x_i$                                                                                                                               | $y_i$                                                                                                                                        |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | 60    | 0.707 | 1.102 | 0.395<br>1.810 | 0.504<br>1.181<br>2.285 | 0.222<br>0.785<br>1.576<br>2.994 | 0.266<br>0.566<br>0.910<br>1.317<br>1.821<br>2.499<br>3.605 | 0.126<br>0.407<br>0.726<br>1.095<br>1.540<br>2.103<br>2.895<br>4.316 | 0.147<br>0.302<br>0.467<br>0.642<br>0.829<br>1.031<br>1.250<br>1.490<br>1.756<br>2.055<br>2.398<br>2.804<br>3.305<br>3.978<br>5.069 | 0.072<br>0.222<br>0.382<br>0.551<br>0.732<br>0.926<br>1.365<br>1.365<br>1.616<br>1.896<br>2.214<br>2.583<br>3.025<br>3.586<br>4.371<br>5.768 |

deviation different from unity, simply multiply the given values by the actual standard deviation.\* The standard deviation for each parameter can be approximated as the rms power of the unquantized error signal. The rms value of the unquantized error signal is obtained directly from the calculation of the optimum DPCM predictors and is given by

$$\sigma^2 = C_0 - \sum_{i=1}^n b_i C_i$$

#### 4.2 Experimental results

Four sentences were synthesized in the experimentation:

- A. Few thieves are never sent to the jug.

- B. May we all learn a yellow lion roar.

- C. It's time we rounded up that herd of Asian cattle.

- D. Should we chase those young outlaw cowboys?

High-quality recordings of these sentences were made by two male and two female speakers, and these utterances were used to obtain the analysis data for the prom coding method.

<sup>\*</sup> To obtain the mean square error, multiply the values by the signal variance.

<sup>†</sup>Since the properties of the unquantized error signal are explicitly known, it is sometimes advantageous to use a more complex nonuniform quantizer to truly optimize the transmission system.

Various schemes were tested for assigning bit rates for each individual error signal. From informal listening experiments, it was determined that synthetic speech that was negligibly different from the unquantized synthesis could be generated according to the following bit assignment:

Pitch: 3 bits/frame Power: 3 bits/frame

Unvoiced-voiced: 1 bit/frame

$g_1$ : 4 bits/frame  $g_2$ : 4 bits/frame

$g_3$ : 4 bits/frame  $g_4$ : 4 bits/frame

$g_{5}$ : 3 bits/frame

$g_6$ : 3 bits/frame

g<sub>7</sub>: 2 bits/frame g<sub>8</sub>: 2 bits/frame

$g_9$ : 2 bits/frame

$g_{10}$ : 1 bit/frame  $g_{11}$ : 1 bit/frame

$g_{12}$ : 1 bit/frame

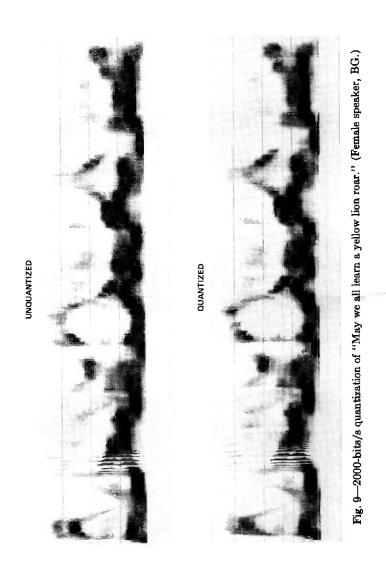

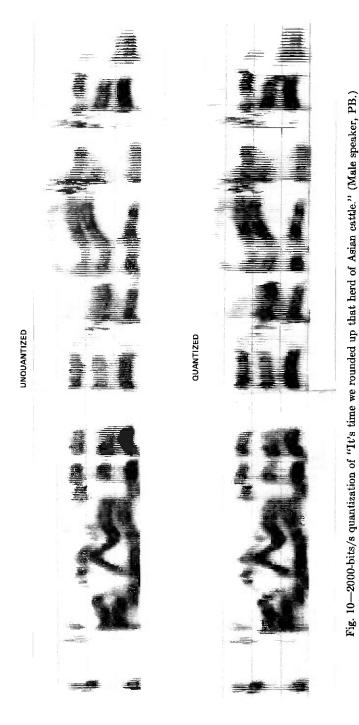

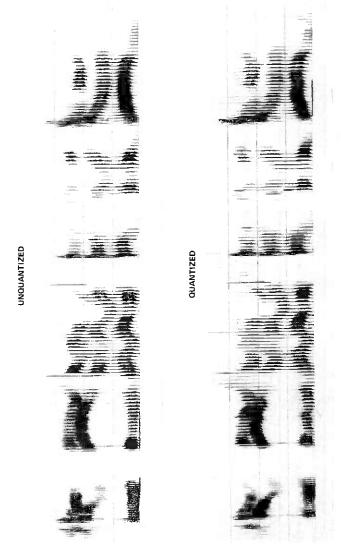

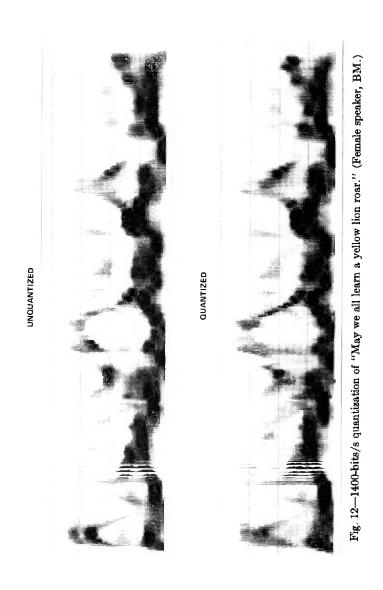

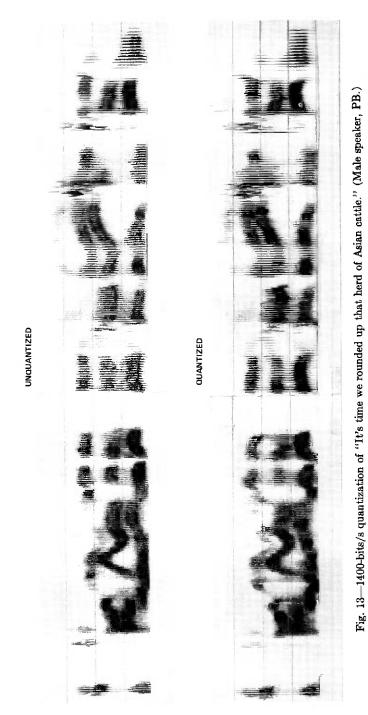

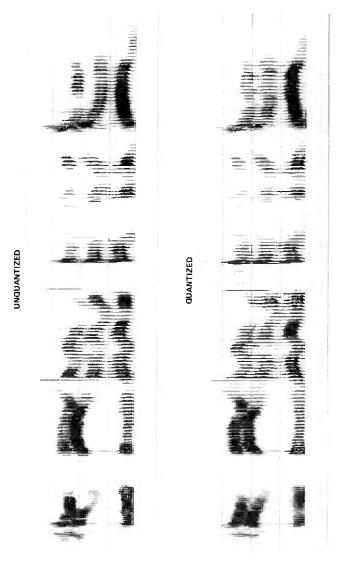

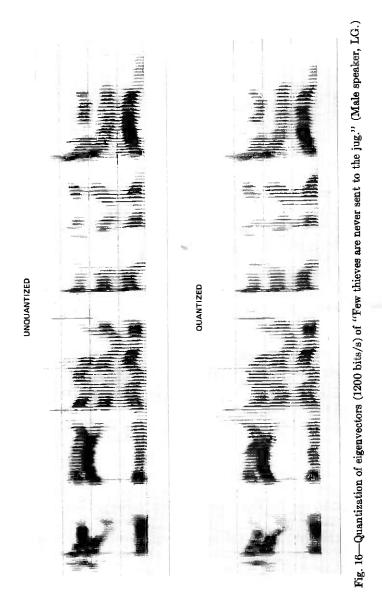

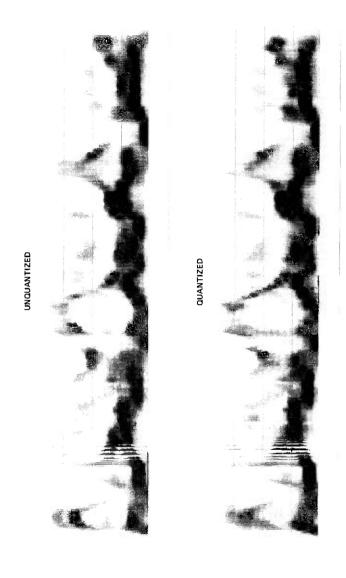

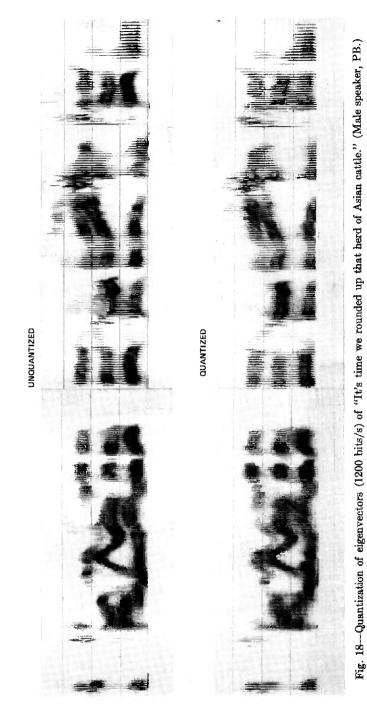

The total number of bits dedicated to the complete set of LPC parameter is only 38 bits/frame or 1900 bits/s. On the average, an additional 100 bits/s are required to transmit the necessary DPCM information (DPCM predictors, standard deviations, and initial values of the LPC parameters). As can be observed from Figs. 8, 9, and 10, the spectrogram of the DPCM synthetic speech closely resembles that of the unquantized synthetic speech but requires only a fraction of the storage.

As the bit rate for the DPCM linear prediction vocoder is lowered below the value of 2000 bits/s, the quality of the synthesis slowly begins to deviate from that of the unquantized synthesis. Since the log-area parameters are approximately ordered in terms of their sensitivity, the most expandable bits are those allotted to the lower-ordered  $g_i$ 's. Depending on the speaker and the utterance, the bit rate can be lowered to between 900 and 1500 bits/s and still allow acceptable quality synthesis. Figures 11, 12, and 13 illustrate the above examples for a bit-rate of 1400 bits/s (3; 3; 1; 4, 3, 2, 2, 1, 1, 1, 1, 1, 1, 1). The synthetic speech in these examples is slightly degraded from the unquantized synthesis, but the speech is still readily understood and the vocal attributes of the speaker are still apparent. It should be appre-

<sup>\*</sup>Acceptable quality speech synthesis is defined as speech containing all the information content of the original without containing any annoying degradation in speech quality.

Fig. 8-2000-bits/s quantization of "Few thieves are never sent to the jug." (Male speaker, LG.)

LINEAR-PREDICTION VOCODER

Fig. 11-1400-bits/s quantization of "Few thieves are never sent to the jug." (Male speaker, LG.)

LINEAR-PREDICTION VOCODER

THE BELL SYSTEM TECHNICAL JOURNAL, DECEMBER 1975

ciated that the necessary storage requirements to produce acceptable quality synthetic speech in this method are nearly  $\frac{1}{3}$  the requirement for the PCM transmission of the LPC parameters (see Section I).

#### V. REAL-TIME DPCM TRANSMISSION

The DPCM scheme developed in Section III suffers from the draw-back that the calculation of the DPCM predictors and the quantizer step size are delayed until all the LPC parameters are available. For real-time speech synthesis, it is desirable that the process of parameter transmission be done concurrently with the measurement of the LPC parameters. In this section, we discuss several schemes for achieving real-time transmission while still retaining almost the performance of the optimum DPCM strategy.

#### 5.1 Average statistical system

The first means of obtaining a real-time system is based upon the observation that the optimum decay first-order predictor for many of the LPC parameters is nearly equal to one  $[b_1 = 1.0 \text{ in eq. (4)}]$ . Thus, the optimum linear prediction of the parameter  $x_r$  is approximately  $x_{r-1}$ . Table III is a comparison of the improvement factors  $G_{\text{opt}}$  obtained for  $b_1 = 1.0$  and  $b_1$  set equal to the optimum value. The overall improvement factors for  $b_1 = 1.0$  are not significantly different from the optimum values, and the delay in calculating the optimum  $b_1$  can be avoided by simply letting  $b_1 = 1.0$ .

To design the optimum quantizer, it is necessary to know the standard deviation of the signal to be quantized. However, our statistical studies have indicated that the standard deviation of the various difference signals are quite stable across different utterances and different speakers. Table IV shows the measured standard deviations for each difference signals computed with  $b_1 = 1.0$ . Table IV also

Table III — Comparison of  $G_{\rm opt}$  in decibels with  $b_1$  set equal to optimum value and  $b_1=1.0$ . Sentence A is "Few thieves are never sent to the jug" and sentence B is "May we all learn a yellow lion roar."

|                                                 | Pitch | Power | $g_1$ | <i>g</i> <sub>2</sub> |

|-------------------------------------------------|-------|-------|-------|-----------------------|

| Sentence $A$ $b_1 = \text{Optimum}$ $b_1 = 1.0$ | 23.7  | 12.2  | 14.7  | 12.2                  |

|                                                 | 20.2  | 10.1  | 14.1  | 11.0                  |

| Sentence $B$ $b_1 = \text{Optimum}$ $b_1 = 1.0$ | 33.8  | 19.0  | 24.0  | 19.6                  |

|                                                 | 33.1  | 18.8  | 23.9  | 19.2                  |

Table IV — Measured standard deviations for the synthesis parameters

|                 | $\mathbf{U}_{\mathbf{p}}\mathbf{dated}$ | No Updating        |

|-----------------|-----------------------------------------|--------------------|

| Pitch Period    | 13.01                                   | 16.5               |

| Power           | $27 	imes 10^{5}$                       | $27 \times 10^{5}$ |

| g <sub>1</sub>  | 0.697                                   | 0.959              |

| g <sub>2</sub>  | 0.729                                   | 0.830              |

| g 3             | 0.509                                   | 0.559              |

| g 4             | 0.510                                   | 0.554              |

| g 5             | 0.413                                   | 0.446              |

| g 6             | 0.417                                   | 0.430              |

| g <sub>7</sub>  | 0.386                                   | 0.406              |

| g <sub>8</sub>  | 0.385                                   | 0.406              |

| g <sub>9</sub>  | 0.377                                   | 0.399              |

| g <sub>10</sub> | 0.346                                   | 0.364              |

| $g_{11}$        | 0.332                                   | 0.342              |

| g 12            | 0.322                                   | 0.328              |

contains the standard deviation for a system in which the prediction scheme is not updated for each unvoiced and voiced region.

Using the standard deviations listed in Table IV and the quantizer discussed in Section IV, a robust transmission scheme is achieved. For example, the difference signal for the pitch period can be accurately quantized for differences as small as two samples or as large as 50 for three-bit quantization.\* The synthetic speech quality for the average statistical system compares quite favorably to the optimum scheme, and has the added advantage of real-time implementation.

#### 5.2 Adaptive system

#### 5.2.1 Adaptive DPCM prediction

The DPCM predictors can also be calculated without knowing the entire sequence of parameters by an adaptive method that is based upon the technique of "steepest descent." In this scheme, an initial estimate of the DPCM predictors is determined and then a new set of predictors is calculated to reduce the prediction error. The perturbation in the predictors is in a direction opposite the gradient of the prediction error taken with respect to the DPCM predictor vector. The resulting perturbation is given by

$$\delta^{r}(b_{j}) = B \cdot \operatorname{sgn}(e_{r}) \cdot \bar{x}_{r-j} / \sum_{k=1}^{n} |\bar{x}_{r-k}|, \qquad (10)$$

where B is the adaptation rate (typically, B = 0.09), and  $x_r$  is the

<sup>\*</sup>If a nonlinear smoothing algorithm (Ref. 10) is applied to the raw pitch measurements, the variance of the corresponding difference signal is reduced by more than \( \frac{1}{2}\). A two-bit quantization can then be used for pitch without diminishing the quality of the synthesis.

quantizer value of the parameter. For the prediction of the (r + 1)th sample of the parameter, the DPCM predictors are given by

$$b_j^{r+1} = b_j^r + \delta^r(b_j).$$

(11)

For a quantizer with  $B \ge 2$ , it can be shown that the adaptation scheme will match the changing spectral properties of the speech signal and result in near-optimum performance.<sup>12</sup> For the two methods given above, it should be noted that, in addition to the on-line calculation of the ppcm predictors, it is unnecessary to transmit the predictors.

#### 5.2.2 Adaptive quantization

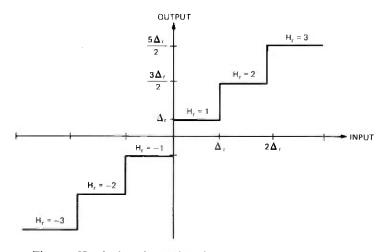

In the previous section, the quantizer was constructed to take advantage of the known properties or average statistical properties of each parameter's difference signal. In this part of the paper, we introduce an alternate technique for estimating the signal variance. This method is based upon an adaptive approach developed by Cummiskey, Jayant, and Flanagan.<sup>13</sup> In their scheme, a simple uniform quantization of the difference signal is used, but the step size for every new input is varied by a factor depending on which quantizer slot was occupied by the previous sample. Numbering the quantizer slots in the manner shown in Fig. 14, the updated step size  $\Delta_{r+1}$  is calculated from the previous step size  $\Delta_r$  by

$$\Delta_{\tau+1} = \Delta_{\tau} \cdot M(|H_{\tau}|), \tag{12}$$

where  $H_r = 1, 2, \dots, B$  and the multiplier function M() is a time-invariant function of the quantizer slot number.

Fig. 14—Numbering of quantizer slots for adaptive quantization.

To adequately match the step size to the signal variance, the multiplier function must be properly chosen. Table V shows the multiplier functions found to be experimentally optimum for quantizing speech waveforms. Using this adaptive scheme (ADPCM) and these multipliers, the quantization of the difference signals can also be efficiently achieved even when the initial step size is a poor estimate of signal variance. Table VI is a comparison of the signal-to-noise ratio for the adaptive scheme with a crude initial estimate of step size and the optimum quantizer discussed in Section IV. The results in Table VI are an encouraging demonstration that it is not necessary to know the statistical structure of the difference signal to efficiently quantize the signal. In fact, it can be shown that, if the properties of the signal are nonstationary, the adaptive method is more suitable than the scheme used in Section IV.

It should be noted that the above scheme does not apply for one-bit quantization (B=1). A simple strategy for one-bit quantization has been developed by Jayant.<sup>14</sup> Let  $c_{\tau}$  and  $c_{\tau-1}$  denote the values of successive bits in a one-bit scheme, then

$$\Delta_r = \Delta_{r-1} P^{c_r c_{r-1}}, \tag{13}$$

where P has the typical value P=1.5. Although this method was developed for quantizing speech waveforms, it performs quite well in quantizing the parameter difference signals. A comparison of this method and the optimum technique is shown in Table VII. Again, the adaptive scheme works well even with a poor initial estimate of signal variance.

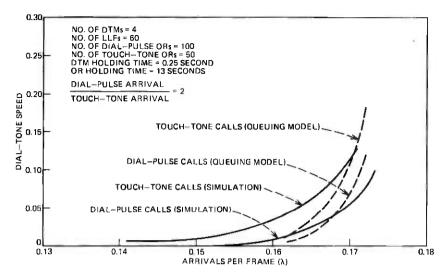

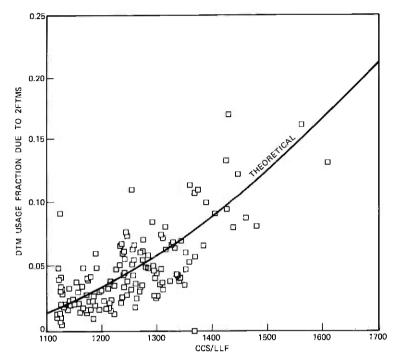

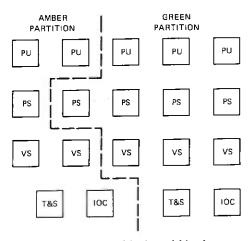

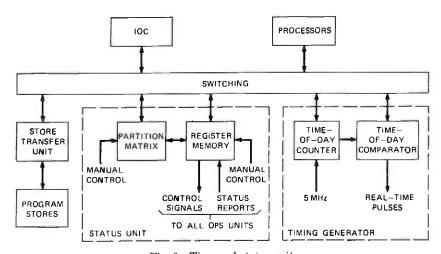

#### 5.3 Synthesis