Copyright © 1977 American Telephone and Telegraph Company THE BELL SYSTEM TECHNICAL JOURNAL Vol. 56, No. 2, February 1977 Printed in U.S.A.

1A Processor:

# **Organization and Objectives**

By R. E. STAEHLER

(Manuscript received July 16, 1976)

This paper presents an overview of the 1A Processor in terms of objectives, design philosophy, major features, and applications in the Bell System. It also serves as an introduction to the detailed technical papers that follow.

### I. INTRODUCTION

A steady and rapid increase has occurred in urban and toll traffic and service features during the past decade. This has highlighted the need for large, high-traffic capacity electronic switching systems for local, tandem, and toll applications in the Bell System. The 1A Processor<sup>1-3</sup> has been developed to meet this high-processing capacity need. It is a stored program processor having a basic instruction execution speed of 700 ns, a memory access speed of 1400 ns, direct-memory access to bulk memory and data links, and a peripheral bus system and associated controls for interfacing to the switching networks. The technology is based upon beam-leaded integrated circuits that are used for most logic functions. A common processor was designed for use in a variety of applications to minimize the expenditure of both development and manufacturing resources.

The 1A Processor provides a number of improvements over its Bell System predecessors. It executes instructions faster, provides more program and call storage capacity, and permits more rapid program and translation changes. It also employs an improved order structure that uses less storage and leads to more efficient program development. In addition to space, power, and cost reductions, it provides improved trouble detection and repair, shorter installation intervals, and increased dependability. The maintenance programs and fault-recognition programs are an integral part of the processor. It has stand-alone capability that permits use in a variety of applications.

The intent here is to outline the objectives, design philosophy, major features, and applications of the 1A Processor and to provide an introduction to the more detailed technical papers that follow.

# **II. OBJECTIVES**

# 2.1 Capacity

Capacity objectives for the 1A Processor were set to meet the processing needs of electronic switching systems, which must handle about 500,000 busy-hour calls in a toll environment.

### 2.2 Flexible network interface

Another objective in the design of the processor was a flexible network interface that permits control of either the space-division network used in No. 1 ESS that requires central pulse distribution enabling or the time-division network used in No. 4 ESS that uses coded enabling.

### 2.3 Dependability

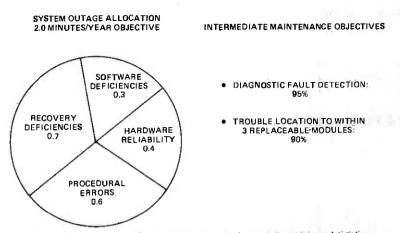

Bell System electronic switching systems must provide dependable telephone service 24 hours a day during the life of the system. Converting this requirement to a specific design objective, a service interruption which results in a total loss of service, should average less than 3 minutes per year per office.

Since total loss of service can be caused by facilities other than the processor, the processor has been allocated only two-thirds of the downtime; that is, 1A Processor service interruptions that result in a total loss of service should be less than 2 minutes per year per office.

### 2.4 Self-sufficiency

The processor was designed with the capability of stand-alone operation. In other words, it consists of a self-sufficient hardware-software package that permits self-testing without any auxiliary equipment.

# 2.5 Program compatibility

Another important goal was the ability to retrofit the processor into capacity-limited operational No. 1 ESS offices. To achieve compatibility, the No. 1 ESS instruction set was included as a subset of the 1A Processor instruction set. This allows well-tested No. 1 ESS call-processing pro-

grams to be semiautomatically computer-translated for operation on the 1A Processor.

# 2.6 Environmentai

The processor was designed to operate over a wide temperature and humidity range. Specifically, the worst-case range is from 0°C to 50°C and from 20 percent to 80 percent relative humidity.

### 2.7 Economy

The processor was designed to be economically competitive with its predecessors, while still adhering to the preceding objectives. To minimize development and manufacturing costs, a low-cost standardized technology based on integrated circuit building blocks was used, and computer aids were concurrently developed to accelerate all aspects of hardware and software development, manufacture, and test.

# 2.8 Other objectives

Many other objectives were established for the 1A Processor. For example, the processor should require minimum floor space, energy consumption, and installation time, while maintaining enough of a structural similarity to the No. 1 ESS processor and standardized input/output message format to minimize additional training required for experienced ESS craftspersons.

## III. DESIGN PHILOSOPHY

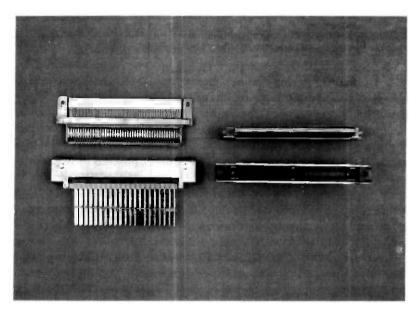

# 3.1 Standardízed technology<sup>4</sup>

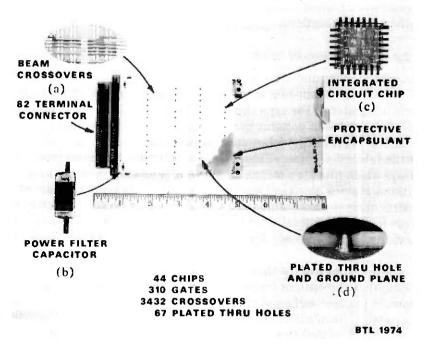

The ultrahigh performance requirements of the 1A Processor require maximum use of integrated-circuit and thin-film techniques. The packaging methods used in the first generation of electronic switching systems are not adequate for such complex and advanced circuitry. As a result, a fundamental premise in the design of the 1A Processor was recognition of the need for a new and innovative packaging approach. To meet this need, a standardized packaging system called 1A technology was developed.

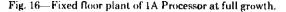

1A technology consists of a set of standardized high-performance devices and packaging techniques that provide miniaturization, highspeed performance, low-energy consumption, ultrareliability, low-cost manufacture, and ease of installation and maintenance. These elements form the basic building blocks for the processor. Application guidelines: stress design standardization and full connectorization of packs, units, and frames. Connectorization permits rapid assembly of complete processors for comprehensive factory testing, rapid disassembly for shipping, and rapid reassembly of a pretested processor on site. It also provides for rapid repair and maintenance. The guidelines also specify a standardized, fixed floor plan, which is applicable to local, tandem, and toll offices and provides graceful store growth. The net result is a reduced engineering and cabling effort and a shortened telephone company order to service interval.

1A technology is designed for use in a broad spectrum of other digital units or processors. It is used in the space-division networks of No. 1 ESS, No. 2 ESS, and No. 3 ESS; the processor of No. 2B and No. 3 ESS; and the time-division network of No. 4 ESS.

# 3.2 Improved development methods

In the formative stage of the project, it was evident that methods used in the development of the first generation of the electronic switching system family were inadequate for the development of the new generation. This was due to the complexities of integrated circuit technology as well as the increased size of the software package. Hence, a decision was made to designate the attainment of improved development techniques as a specific goal and to form organizations chartered to achieve this goal. The thrust for new techniques was designated as the development of development methods.<sup>5</sup> The main objectives were improved quality, enhanced diagnosability, assured manufacturability, reduced cost, shortened intervals, and more efficient utilization of the members of the development team.

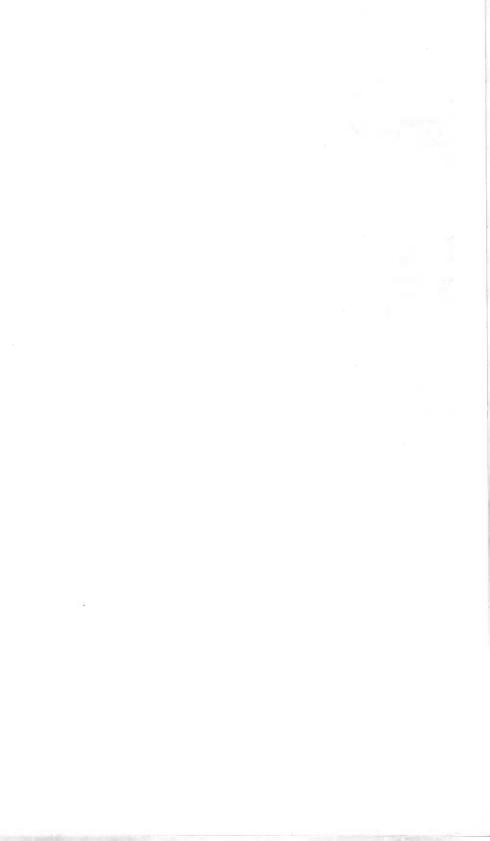

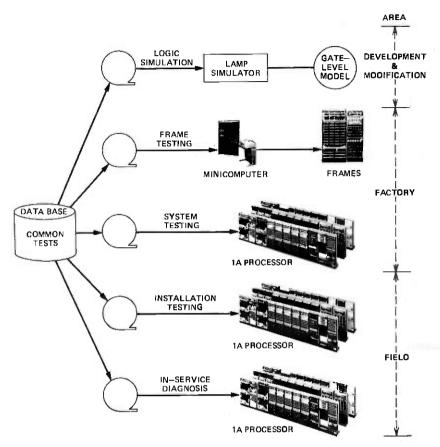

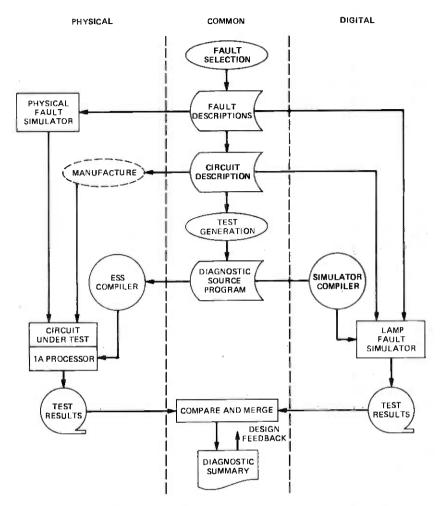

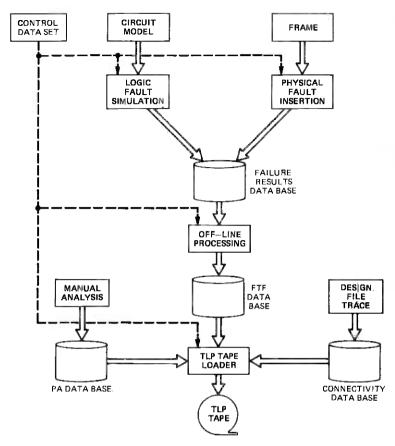

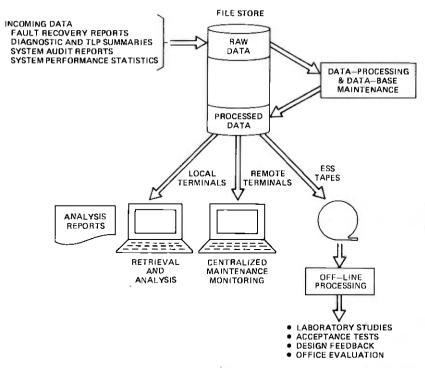

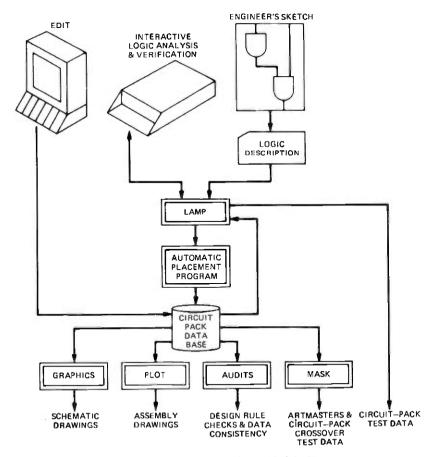

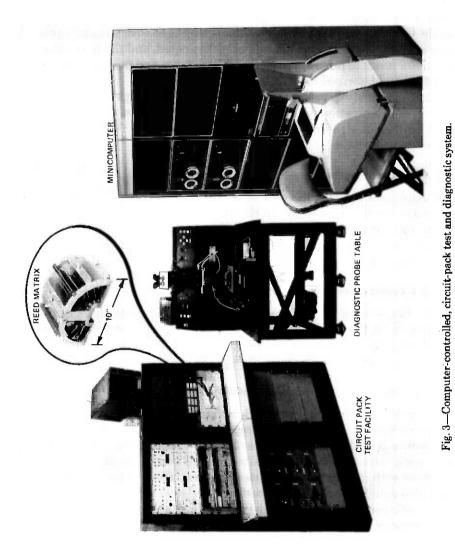

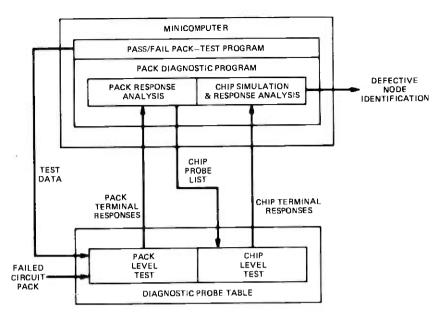

As a result, Bell Laboratories has developed a complete computerbased data-management facility that permits design specifications to be introduced into a massive data base and enables their subsequent use by complex application programs (see Fig. 1).

The design verification, physical design, documentation, and manufacturing application programs have been essential to the development of the hardware and software of not only the 1A Processor, but also the networks of No. 1 ESS, No. 2 ESS, No. 3 ESS, and No. 4 ESS, and the processor of No. 2B ESS and No. 3 ESS.

The application programs include both automatic and interactive capabilities. The latter permits the designer to interrupt, query, and make changes as an application program is run.

Use of a general-purpose computer with virtual memory simplified the storage of massive quantities of data and made feasible the simulation of large-scale systems containing tens of thousands of gates. For example, simulation of the 50,000-gate central control eliminated many clerical encoding and logic errors at a time when the only existing central

Fig. 1-Computer-aided design.

control was "logically built" in the memory bank of a general-purpose computer.

Interactive simulators were also used to validate new system or program strategies, to design programs, and to debug programs that have been designed. Simulation was found to be an effective debugging tool for all types of programs including fault recovery and diagnostic programs.

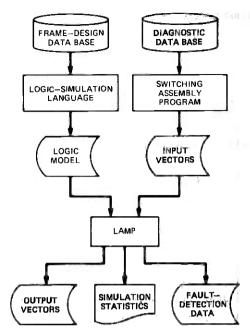

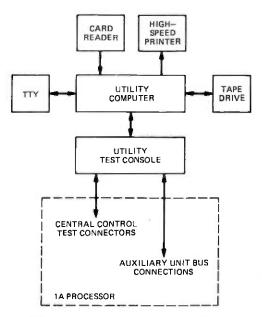

The need for a sophisticated laboratory software testing tool triggered the design of a comprehensive utility test system. The hardware consists of over 80,000 gates and 16,000 words of memory. It provides an electrical and time buffer between the processor and a utility minicomputer. The system, the minicomputer in conjunction with its resident utility program, provides direct and conditional control over any processor-resident program as well as monitor, trace, load, and dump capabilities.

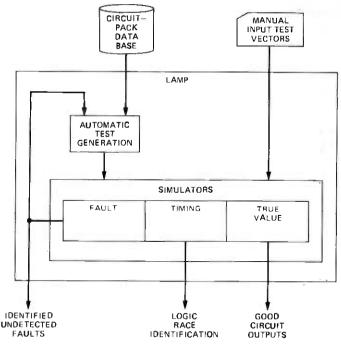

### 3.3 Integrated development, manufacture, and test<sup>6</sup>

The need to automatically convert a staggering volume of design information was recognized as an integrated part of the development methods. To meet this need, application programs were designed to extract manufacturing information from the data base in the generalpurpose computer. This information is used by Western Electric to generate artmasters for the plated-interconnection patterns on both circuit packs and printed-wire backplanes, and to produce machinereadable data to control wiring machines for automatic wiring of those connections, which are not contained on the printed-wire backplanes. Bell Laboratories and Western Electric engineers collaborated on the development of computer-controlled test facilities. The test sequences are verified using the design data base and are used to program minicomputers that control a variety of test stations that test everything including interconnection patterns, circuit packs, backplanes, frames, and complete processors. The processor test sequences from the data base are also used for installation and performance testing in the field.

Still another set of application programs use the design data base to generate documentation such as schematic diagrams and wiring lists.

# IV. PROCESSOR ORGANIZATION

# 4.1 Hardware<sup>7,8</sup>

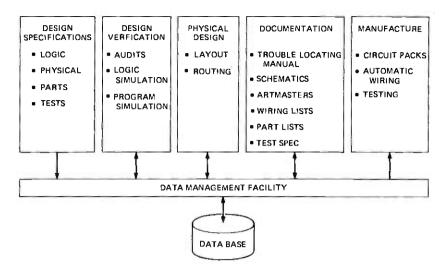

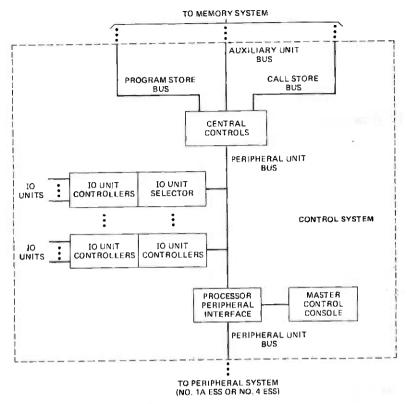

As shown in Fig. 2, the general architecture of the 1A Processor is similar to the No. 1 ESS processor<sup>9</sup>, except for the provision of a directmemory-access feature for auxiliary units. This is accomplished over an auxiliary unit bus on the central control. Thus, data can be transferred between program and call stores, and file stores, tape units, and external data links with minimal interference with other processor activities. This feature is essential to the achievement of the modern services planned

Fig. 2-1A Processor block diagram.

for electronic switching systems without impacting heavily on the callprocessing capacity of the system.

The direct-memory-access feature also permits a varied spectrum of maintenance programs to be retained on lower-cost file stores with programs paged into high-speed random-access stores only as needed. Substantial reduction in high-speed memory can thus be realized. Furthermore, many maintenance features, which were not included in earlier generation electronic switching systems because of a high-cost penalty, are now economically provided in the 1A Processor.

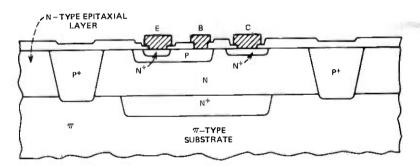

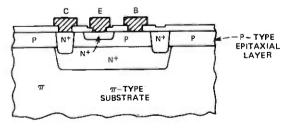

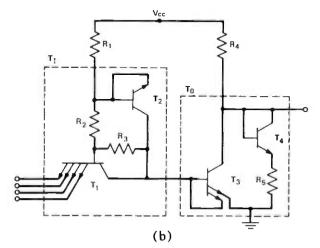

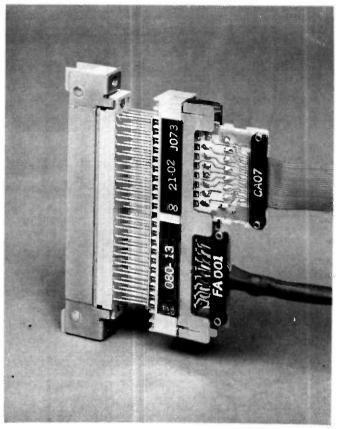

High-speed, low-power DTTL logic integrated circuit devices are used for all logic circuits. The beam leads of the chips are thermocompression bonded to a ceramic substrate. The complete ceramic is mounted on a supporting aluminum plate and bonded to a male-connector assembly.

Program and call stores contain two magnetic core modules and are capable of storing 65,536 words of 26 bits (24 data bits plus 2 parity bits). File stores contain four magnetic disks and are capable of storing a total of 64 megabits. A sufficient number of each type of store is provided to meet the needs of each of the contemplated processor applications.

In the 1A Processor, all subsystems have redundant units and are connected to the basic system via redundant bus systems. Thus, it is possible to operate at full capacity with faults in some units.

The central control units are fully duplicated; they normally operate in step and compare results.

The program store community consists of a prime set plus two additional (or "roving spare") stores. If one of the prime stores fails, the program that is contained in that store is transferred from the duplicated copy of the system program contained in the file store to one of the "rover spares."

The call-store community consists of a prime set plus a full on-line duplicate set for only those stores that contain transient call data. For those stores that contain translation data, one of the duplicated stores containing transient call data is preempted and loaded with the necessary translation data from the duplicated copy in the file store.

Remaining critical units in the processor are duplicated while less critical units are not duplicated.

### 4.2 Maintenance software 10

Error-detection is the basis for automatic detection and resolution of problems without service interruption. This is achieved through matching of duplicated units, parity checks on communications (both address and data) over all buses, interval self-checking in hardware units (control pulsing, timing, internal data transfer), and system sanity timers.

A failure reported by any one of these error-detection schemes triggers a program interrupt, and control is transferred to a fault-recovery program. This program verifies that a fault is present, identifies the most probable subsystem or unit, and then removes the faulty unit from service by reconfiguring the system to maintain call-processing capability. The intent is also to retain as much redundancy as possible in the remaining hardware units in the working configuration.

Special programs, called restart programs, set a diagnostic-request flag and save any data that will aid in identifying trouble symptoms. Upon completion of these actions, system operation is continued by returning control to the interrupted program.

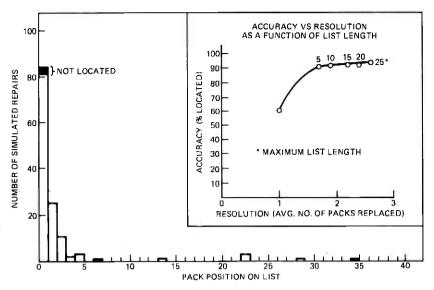

Maintenance experience with earlier generation electronic switching system processors clearly highlighted a need for rapid repair through the use of a comprehensive set of diagnostic tests. To meet this need, a number of diagnostic practices, which differed significantly from those employed in the sixties, were introduced. These practices included organization of the development team to emphasize early and continuing diagnostic planning and execution, use of a common standard macrooriented test design language, and application of a complementary fault-simulation process involving the merging of logical simulation in a general-purpose computer with physical simulation in an operational system laboratory.

The resulting diagnostic programs differ from those used in previous electronic switching systems in that they are also used, as noted earlier, for computer-controlled hardware testing in the manufacturing plant and during installation on the telephone company site.

Hardware or software errors can cause mutilation of the program or data base. Special programs for mutilation detection provide for a progressive verification of integrity. If the mutilation is minor, audit programs analyze the affected data base and correct any errors on a timeshared basis with normal call-processing programs. If the mutilation is severe, the call-processing program is stopped until the mutilation programs are regenerated by transferring the backup information from file memory.

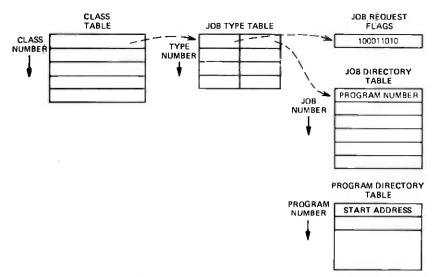

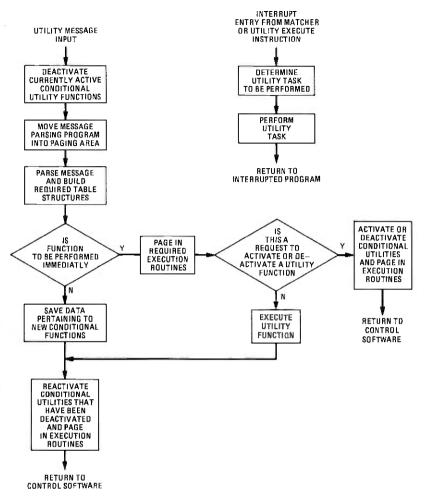

# 4.3 Administrative software

To provide a number of the required 1A Processor capabilities, an extensive set of administrative programs was developed and is included in the processor software package. (These perform many of the functions normally included in an operating system, but since program control is not included, it would not be correct to use that term here.)

These programs serve many functions, such as: transferring data between the call and program stores and the auxiliary units such as the file store, tape store, and input/output terminals; transferring programs into the program store from the file store; controlling (on a predetermined priority basis) the execution of deferred programs in a time-shared mode with call-processing programs, gathering all system-detected trouble symptoms and recording them in the file store for later analysis (these data include audit errors, interrupt reports, fault recovery actions, and diagnostic failure results); executing utility features permitting on-site analysis; temporarily allocating and loading stores for special programs; and providing an on-line complete and partial update capability.

### V. APPLICATIONS

## 5.1 Large toll offices—No. 4 ESS<sup>12</sup>

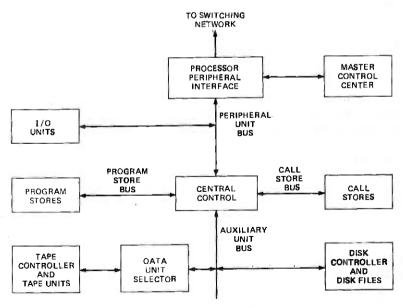

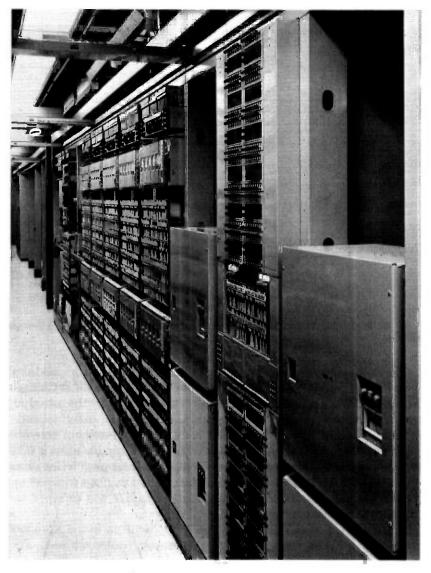

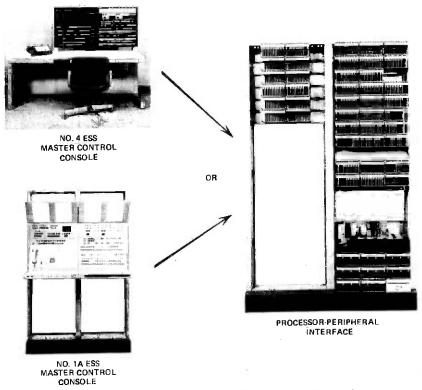

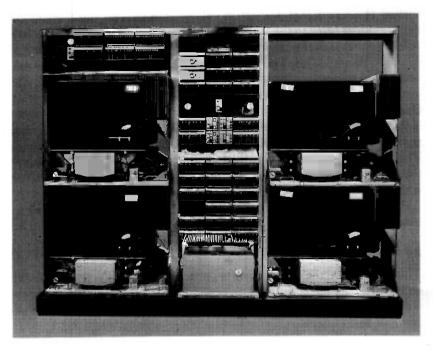

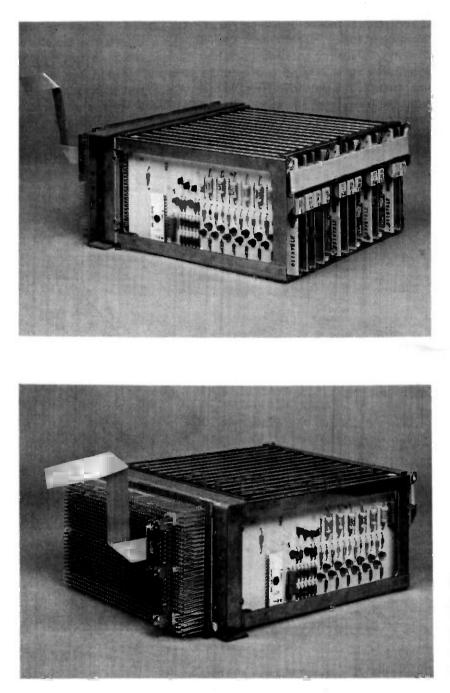

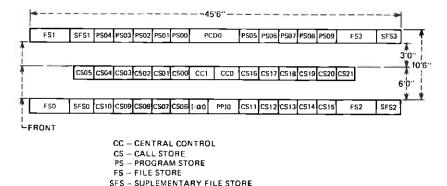

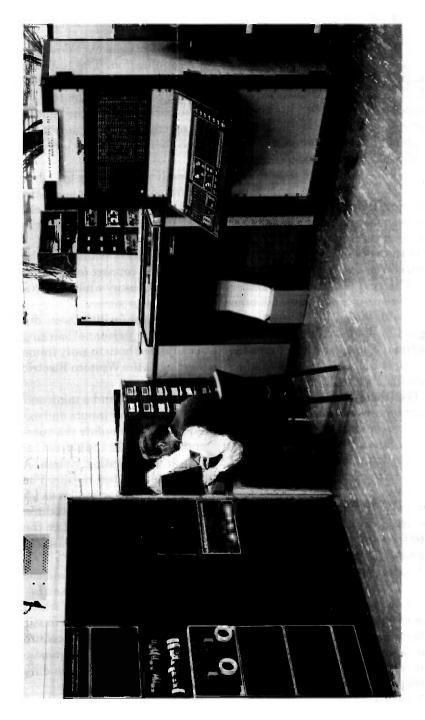

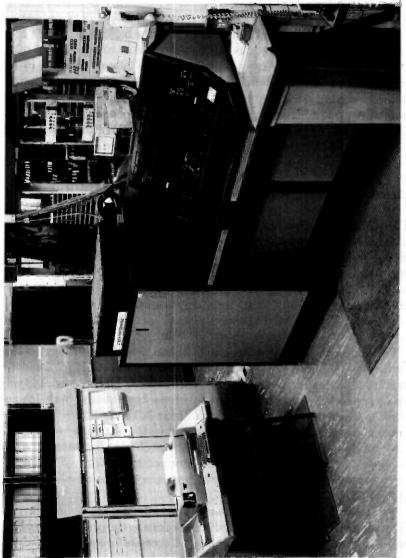

On January 17, 1976, the first 1A Processor for toll applications was cut into service as the common control for the No. 4 ESS toll switching office in Chicago (see Fig. 3). No. 4 ESS uses a solid-state time-division network and can switch up to 550,000 peak busy-hour calls from 107,000 trunks. It is described in a future special issue on No. 4 ESS. The second No. 4 ESS was cut into service in Kansas City on July 3, 1976.

Two more No. 4 ESS offices are expected to become operational in 1976.

### 5.2 Metropolitan local offices-No. 1A ESS 13

On October 15, 1976, the first 1A Processor for local applications cut into service as the common control for the No. 1A ESS local switching office in Chicago (see Fig. 4).

No. 1A ESS uses a remreed space-division network and can handle up to 240,000 peak busy-hour calls and about 100,000 line terminations. No. 1 ESS call-processing programs are semiautomatically computer-translated to operate on the 1A Processor. The 1A Processor occupies less than one-half the space of the No. 1 ESS processor.

# 5.3 Retrofit into No. 1 ESS offices

Plans call for the 1A Processor to replace the No. 1 ESS processor in capacity-limited working offices (the first retrofit is scheduled for 1978). The new processor will provide more than twice the present call-processing capacity of a No. 1 ESS.

### **VI. PERFORMANCE**

### 6.1 Laboratory

Prior to field service, extensive laboratory testing was conducted during which over 100,000 processor hours were logged. This testing

OVERVIEW 127

Fig. 3-1A processor in No. 4 ESS (Chicago toll office).

indicates that the design objective of hardware component reliability, automatic isolation of faulty units without service interruption, rapid repair, and automatic recovery from program and data mutilation are being met. More detail is presented in the associated papers.

Fig. 4-1A Processor in No. 1A ESS (Chicago local office).

### 6.2 Field

Field performance of the 1A Processor in both No. 4 ESS and No. 1A ESS has been excellent. This is best illustrated by key operational data gathered from the first two offices put into service.

OVERVIEW 129

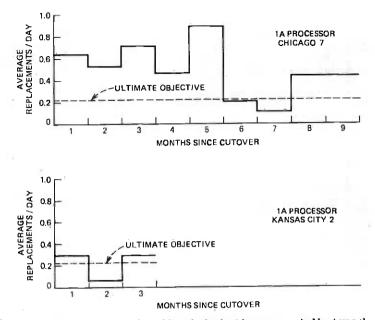

Fig. 5—Replacement rate for pluggable units in the 1A processors in No. 4 ESS through October 1, 1976.

The replacement rate for pluggable units (circuit packs, core modules, power modules) in both offices is shown in Fig. 5. The trend at Chicago 7 shows a marked reduction in the replacement rate after the introduction of some design improvements and the removal of marginal early production units. The ultimate or steady-state replacement rate objective for the 1A Processor complex with 7000 pluggable units is 0.22 unit per day. The data from Kansas City 2 (with later production units and where design improvements were introduced prior to cutover) indicate that the ultimate replacement rate objective was attained essentially at cutover.

Hardware, software, or memory mutilation problems in the No. 4 ESS can result in the need for system reinitialization (called a phase). Fig.

| DURATION<br>(SECONDS) | EFFECT OF PHASE            |

|-----------------------|----------------------------|

| 1                     | NO SERVICE EFFECT          |

| 27                    | TRANSIENT CALLS LOST       |

| 40                    | TRANSIENT CALLS LOST       |

| 40                    | ALL CALLS LOST             |

|                       | (SECONDS)<br>1<br>27<br>40 |

Fig. 6—No. 4 ESS reinitialization phase structure.

Fig. 7-Phase events and outage time in No. 4 ESS caused by 1A Processor through October 1, 1976.

6 shows the No. 4 ESS reinitialization phase structure. Note that a phase 1 has no system effect. Phases 2 and 3 result in the retention of established calls, but the loss of transient calls. Phase 4 results in a total system outage with a loss of all calls.

Fig. 7 shows both the number of phase 2 and 3 events as well as the average phase outage time by month caused by the 1A Processor for both No. 4 ESS offices. The outage time represents the duration of the phase, during which established calls were retained, but no new calls were established. The trend at Chicago 7 shows a rapid reduction in the frequency and outage time for phase 2 and 3 events as the causes of the phases were determined and corrected. The ultimate or steady-state total 1A Processor phase outage time objective is 0.16 minute per month or 2 minutes per year. Note that at Kansas City 2 there have been no 1A Processor phase events or outages.

As noted in Fig. 7, no phase 4 or total system outage has been caused

OVERVIEW 131

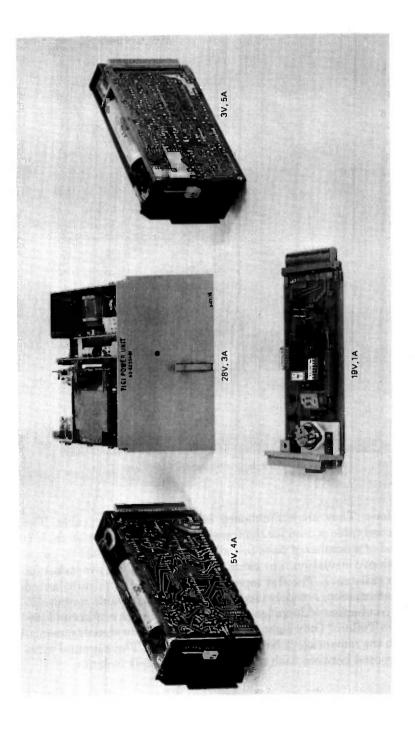

Fig. 8—Program and call stores using 4 K MOS integrated-circuit devices. 132 THE BELL SYSTEM TECHNICAL JOURNAL, FEBRUARY 1977 by the 1A Processor in either Chicago 7 or Kansas City 2.

# VII. CONCLUSION

After logging more than a total of 8000 in-service hours, 150,000 laboratory and field hours, 4 million unit hours, 350 million ceramic integrated-circuit pack hours, and 10 billion semiconductor integratedcircuit hours on the 1A Processor, overall performance indicates that the design objectives are being realized.

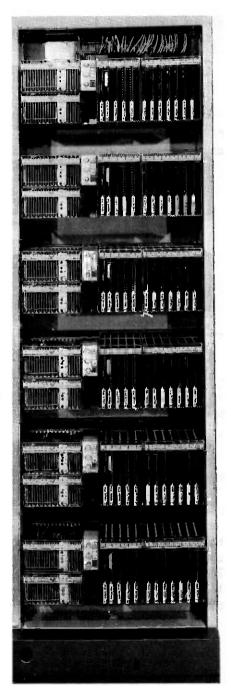

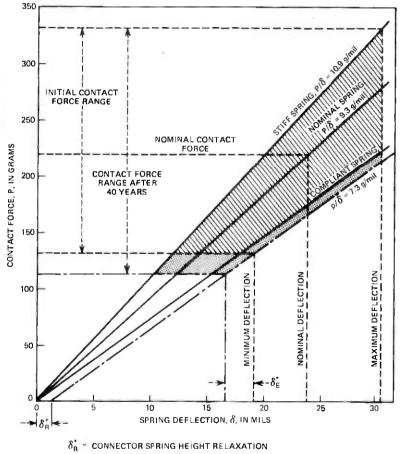

Nevertheless, constant attention is being given to possible areas of improvement. 1A technology was designed so that larger scales of integration could be smoothly introduced into the 1A Processor. Furthermore, as with the No. 1 ESS processor, as technological advances occur. it is expected that subsystems can be redesigned and smoothly introduced into the 1A Processor. A specific example is a program and call store using 4 K MOS integrated-circuit chips in place of magnetic cores. These stores require less space and power than the magnetic core stores currently used in the 1A Processor. As shown in Fig. 8, six stores (over 10 megabits) can be mounted in one 2-foot, 2-inch bay. The integrated circuit program and call store is currently being manufactured by Western Electric with shipment expected in early 1977. These continuing refinements of the 1A Processor should provide additional improvements in performance as well as additional economic advantages.

### VIII. ACKNOWLEDGMENT

The design of the 1A Processor required the cooperative efforts of hundreds of people in Bell Laboratories, Western Electric, and A.T. & T. The author wishes to acknowledge the contributions of all the team members whose work is summarized herein.

#### REFERENCES

- R. E. Staehler, "1A Processor—A High Speed Processor for Switching Applications," International Switching Symposium, Boston, Massachusetts, June 1972.

R. E. Staehler and T. S. Greenwood, "1A Processor—Development and Status," In-ternational Switching Symposium, Munich, Germany, September 1974.

R. E. Staehler and R. J. Watters, "1A Processor—An Ultra-Dependable Common Control," International Switching Symposium, Kyoto, Japan, October 1976.

J. O. Becker, J. G. Chevalier, R. K. Eisenhart, J. H. Forster, A. W. Fulton, and W. L. Harrod, "Technology and Physical Design," B.S.T.J., this issue, pp. 207-236.

R. W. Ketchledge, "Development of Development Methods," International Switching Symposium, Munich, Germany, September 1974.

H. A. Hilsinger, K. D. Mozingo, C. F. Starnes, and G. A. Van Dine, "Testing and In-tegration," B.S.T.J., this issue, pp. 289-312.

- A. H. Budlong, B. G. De Lugish, S. M. Neville, J. S. Nowak, J. L. Quinn, and F. W. Wendland, "Control System," B.S.T.J., this issue, pp. 135-179.

C. F. Ault, J. H. Brewster, T. S. Greenwood, R. E. Haglund, W. A. Read, and M. W. Rolund, "Memory Systems," B.S.T.J., this issue, pp. 181-205.

"No. 1 Electronic Switching System," B.S.T.J., 43, Parts 1 and 2, September 1964.

P. W. Bowman, M. R. Dubman, F. M. Goetz, R. F. Kranzmann, E. H. Stredde, and R. J. Watters, "Maintenance Software," B.S.T.J., this issue, pp. 255-287.

G. F. Clement, P. S. Fuss, R. J. Griffith, R. C. Lee, and R. D. Royer, "Control, Ad-ministrative, and Utility Software," B.S.T.J., this issue, pp. 237-254.

A. E. Spencer, Jr. and H. E. Vaughan, "No. 4 ESS—A Full-Fledged Toll Switching Node," International Switching Symposium, Kyoto, Japan, October 1976.

J. S. Nowak, "No. 1A ESS—A New High Capacity Switching System," International Switching Symposium, Kyoto, Japan, October 1976.

# 1A Processor:

# **Control System**

# By A. H. BUDLONG, B. G. DE LUGISH, S. M. NEVILLE, J. S. NOWAK, J. L. QUINN, and F. W. WENDLAND

(Manuscript received July 16, 1976)

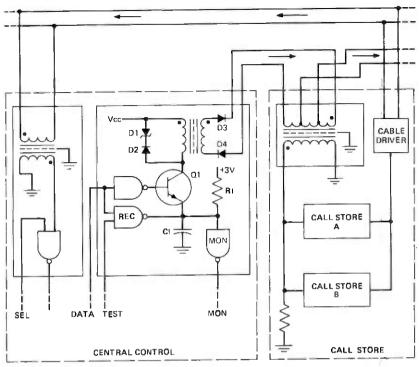

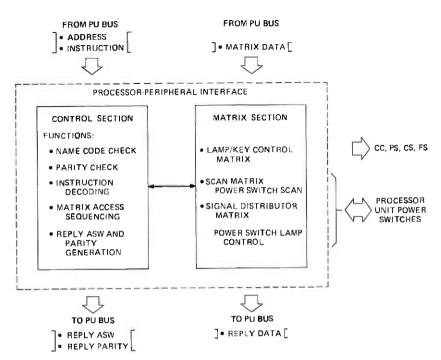

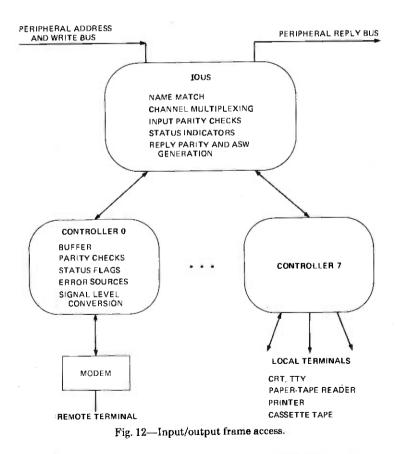

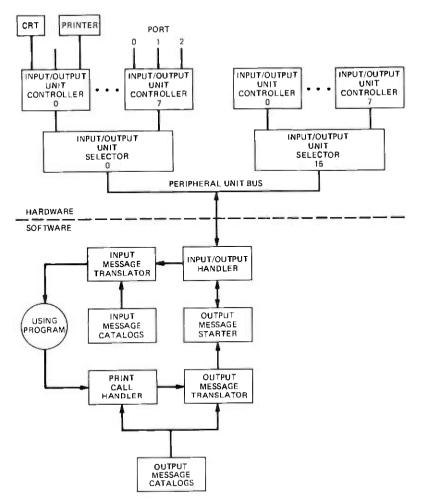

This article contains a description of the central control, input/ output subsystem, processor-peripheral interface, master control console, and the interunit communication bus system. The units are discussed in a manner which highlights comparison of features with No. 1 ESS and stresses those features which are most important in meeting the stringent reliability objectives.

### I. INTRODUCTION

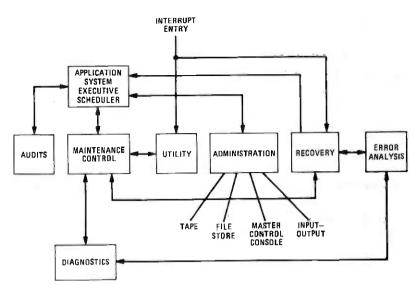

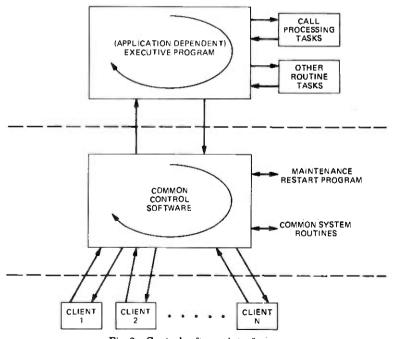

The 1A Processor control system, coupled with program, call, and auxiliary memory, is an independent, stand-alone processor with full operational and maintenance capability. It provides for execution of the processor and system program, automatic system maintenance actions, manual control and monitoring, and interfaces to memory, network, and external systems.

This processor is an outgrowth of previous Bell System switching processors. Although it contains many similar or modified features, the new processor offers significant improvements over its predecessors. In comparison with the No. 1 ESS processor,<sup>1</sup> several major new features and improvements are provided—for example, four to eight times faster instruction execution, writable program memory, greatly expanded program and call memory size capability, and auxiliary memory with autonomous transfer to and from program and call memory (direct memory access). These advancements are achieved while maintaining compatibility with the No. 1 ESS network and programs.

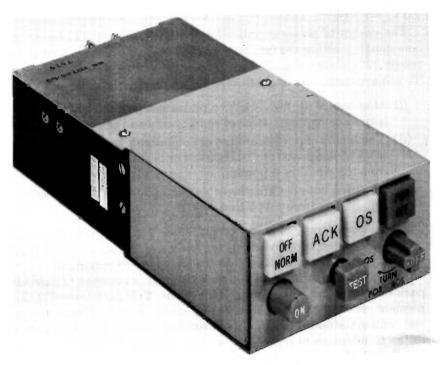

The control system consists of the central controls  $(CC_8)$ , communication buses, and the man-machine interface and control. The manmachine interface and control includes the master control console (MCC),

Fig. 1-Control system.

processor-peripheral interface (PPI), and the input/output unit selectors and controllers (10). These are illustrated in Fig. 1.

This article presents an overview of the control system features and then details the operation and maintenance features of each subsystem.

# II. CONTROL SYSTEM FEATURES

## 2.1 General

The control system coupled with the memory system constitutes a stored program processor. For switching system control, the instruction capability of the central processing unit (CC) is tailored for control and logical operations rather than mathematical operations such as multiplication, division, and function evaluation. Internal CC operations include fixed-point addition and subtraction, word and item manipulation (such as rotation and masking), sequencing to perform multiple autonomous tasks associated with each communications bus, sophisticated instruction address manipulation, and sequencing and logic operations

dedicated to maintenance functions and interrupt handling. The instruction set reflects these features and is oriented to provide efficient transfer of control, item manipulation, index register modification, and condition testing. Special instructions and instruction sequences are provided to optimize control of the switching network, and other special instructions are oriented toward maintenance actions such as interrupt handling, configuration control, and subsystem fault diagnosis.

In addition to the improvements previously mentioned, the 1A Processor surpasses the No. 1 ESS processor in other areas. Operational improvements include an expanded instruction set, more general internal CC logic, a coded enable unit selection capability on the peripheral bus, expanded IO capability for input and monitoring, and a centralized peripheral interface. Maintenance features have been improved by including more access and control, so that virtually all memory elements can be initialized and monitored. In addition, checking circuits can be exercised, all bit combinations can be transmitted over buses, and critical control signals can be sent to each unit over two completely separate paths.

# 2.2 Central control

The internal structure of the 1A Processor CC is similar to the No. 1 ESS CC, in part to achieve a high degree of forward compatibility. Within this constraint, a great many improvements have been made to its instruction set.

Internal registers and arithmetic logic functions have been expanded and enhanced. Processing features include generalized adder access, generalized registers, "shadow" registers which save the contents of each general register on request, and 24-bit internal data paths and registers. These changes are provided to improve the development of application and maintenance programs.

Instruction set features include generalized No. 1 ESS options, instructions with multiple functions, new instructions to utilize new internal processing features, memory protection features, and an instruction to search memory for a word matching selected register contents. Instructions are one or two 24-bit words, where appropriate, to save memory when only one word is necessary. In many cases, an instruction is available in either one- or two-word format, and the format selection is based on the length of fields or options specified by the programmer. Transfer addressing capability is improved by the use of an address stack utilizing a pointer in CC. Program and call store interfaces and internal CC logic are designed to work with either a 700-ns or 1400-ns CC-store cycle. Maintenance instructions allow communication paths and subsystem interfaces to be fully checked.

The peripheral control has been expanded beyond the central pulse

CONTROL SYSTEM 137

distribution (CPD) scheme used in No. 1 ESS to provide coded enabling with bus transmission checks. The coded-enable scheme accommodates a long bus without an excessive time penalty. This is possible because the CC recognizes the completion of an operation and resumes processing immediately, rather than allowing a fixed time for the full bus length. The reply bus has also been expanded from 16 to 24 bits, and nonperipheral instructions that do not interfere with peripheral registers are processed simultaneously with the completion of peripheral instructions.

The new auxiliary unit control provides for mass memory units with autonomous transfer of data between program or call memory and the auxiliary memory. This saves substantial processing time, since the transfers are not directly controlled by instructions executed in the CC. An interface controller in the CC administers the data transfer to or from auxiliary memory units on a priority basis. The priority can be altered by program control.

Enhanced maintenance features in the CC include selective inhibits of clock pulses, read and write access for nearly all memory elements including sequencer circuits, sophisticated start-stop control, and two 24-bit matchers in each CC. The CCs have access to each other over fast, dc interconnecting buses which provide control and route the CC data for matching. They also have the capability to generate maintenance and configuration signals for each unit and a circuit to check for proper operation.

### 2.3 Communication buses

Communication buses are used to transfer control, timing, and data signals between processor subsystems. The buses are designed to provide physical and electrical isolation, to provide for simple addition of units on an in-service basis, and to provide a pluggable connection for efficient factory testing, installation, and maintenance.

Peripheral buses are directly compatible with the No. 1 ESS peripheral system and, therefore, the timing and signal levels are constrained to be the same as No. 1 ESS. Other buses utilize advanced circuits, packaging, and cable techniques to achieve faster, lower-power operation consistent with the 700-ns CC cycle.

Each bus system is duplicated and has configuration control circuits, as in any major subsystem.

# 2.4 Man-machine interface and control

Normally, communication between personnel and machine is via terminals, such as teletypewriters, that interface through input/output unit selectors and controllers. Up to 96 channels are available with 110-

or 1200-word-per-minute data rates. Terminals may be local or remote, with data sets used for remote terminals.

The master control console (MCC) provides direct manual control and monitoring of key indicators. In addition to this console for the 1A Processor, a companion console is associated with each system using the 1A Processor, such as No. 1A  $ESS^2$  or No. 4  $ESS.^3$

The processor peripheral interface (PPI) provides the logic and access circuitry for the MCC. It also contains circuitry to monitor and control individual unit power switches and other manual controls.

A major function of the PPI is to provide a common unit for interface to peripheral systems such as the No. 1A ESS or No. 4 ESS network. The ability to loop peripheral bus transmissions back to the CC is provided. This allows intraprocessor bus cables and circuits to be checked independently from the peripheral units.

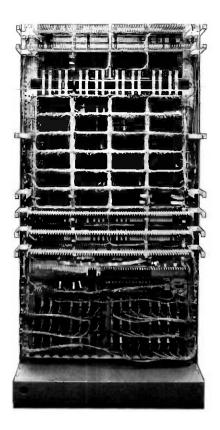

# III. CENTRAL CONTROL OPERATIONAL HARDWARE FEATURES

Central control is a synchronous stored-program central processing unit designed with a multiplicity of hard-wired sequencers to facilitate the level of concurrent operation required. It is worst-case designed to operate on a tightly synchronized basis with main and auxiliary memory units within the 1A Processor complex. The worst-case design is based on a model of 1A technology interconnection and devices and is supported by both extensive measurements and analytical methods. Within central control, over 100 representative critical timing chains were simulated using simulation models and tools that evolved with the hardware design. With specifications on the devices and hardware, which also evolved with the design, the average worst-case maximum delay per logic stage for typical critical paths in the CC is about 12 ns, allowing about 58 stages of delay in a 700-ns cycle.

In addition to serving as an instruction execution and control unit, central control provides system synchronization. System timing originates from a 20-MHz crystal oscillator circuit in the active central control. This oscillator circuit provides signals for both the active and standby CCs, thus synchronizing them. The active CC also generates synchronization pulses for other units in the system, including main and auxiliary memory units. These synchronization pulses are sent every CC cycle (700 ns) on a per-unit basis.

Central control is designed to operate with any mixture of 700-ns and 1400-ns cycle time main memory units. In the normal system mode, the central controls are synchronized and running in step. In other words, they are executing the same instructions and operating on the same data. This is referred to as "duplex operation." In the 1A Processor system, transient data are generally duplicated, that is, stored in two physically separate main memory units assigned the same locations in the address spectrum. Valid system configurations include duplex central controls fetching data from duplicate stores at different speeds. Each central control monitors the speed of the main store unit accessed by the mate central control, and if either CC accesses a slow (1400-ns) module, then both CCs run at the slower rate.

The instruction execution rate is strongly influenced by the speed of the main memory units since a significant proportion of the instructions are executed in one main memory cycle time. For representative code with 1400-ns memories presently available for field use, the average execution rate is about 750,000 instructions per second. Although instructions are designed to execute in an integral number of 700-ns cycles, the "average" instruction requires only 1100 ns to execute; the execution control is idle about 18 percent of the time, particularly as a result of waiting for the target of a successful transfer to be fetched.

### 3.1 instruction fetching

Modern processors achieve high capacity not only because of fast hardware but also because of the increase in concurrent operation including the overlapping of instruction fetching and executing. The fetch control may be several instructions ahead of the execution control. When the fetch control system detects a conditional transfer instruction that is not yet ready to be executed, it is assumed that the transfer will not be made and straightline fetching continues. However, when an unconditional transfer is detected and a transfer is not currently being executed, no fetch operation is initiated until the target address is calculated by the execution control system (this may save a CC cycle).

To facilitate concurrent memory operations, the main memory is split into two systems: program store and call store. Typically, the program store system provides the instruction stream and the call store system provides the data. This distinction is not rigid, however, since either system can perform either function and both systems communicate with central control in similar fashion (timing, synchronization pulses, etc.). The major difference between the program and call store systems is the width of the communication path. On each read operation, the program store returns an even-odd address pair of words and central control selects the required portion, whereas the call store returns only a single word.

Since fetching program code from call store is an inherently slower operation than fetching from program store, this use is restricted and protection is provided so that unplanned transfers to call store are not allowed. Execution of program from call store is used for fault recovery and diagnostic for the program store system. These programs are in-

frequently used and therefore require a very small fraction of system real time. Gating and sequencer action for call store fetching closely emulate gating and sequencer action for program store fetching. To minimize memory access conflicts between the execution and fetch control systems, only seldom-used data are located in program store.

A program instruction may be either one or two words in length, that is, either 24 or 48 bits. The number of bits in an instruction is not directly related to the execution time, although double-word instructions tend to take more cycles to execute because they allow greater flexibility in special features and options. The two words read on each program-store fetch may be two single-word instructions, a single-word instruction and either half of a double-word instruction, halves of two double-word instructions, or one entire double-word instruction. The single-word orders save substantial program storage space since two-thirds of the instructions are typically single-word orders.

To improve efficiency in fetching long (double-word) instructions, these instructions may be aligned on even-address boundaries by inserting a special no-operation order which is not executed if encountered on an odd boundary following a short (single-word) instruction.

The instruction stack size of six (24-bit) words is chosen to best accommodate the frequency of transfers which is relatively high (about 15 percent). Because the stack is small, no attempt is made to determine if the target instruction of a transfer might already have been fetched; instead the target is fetched again.

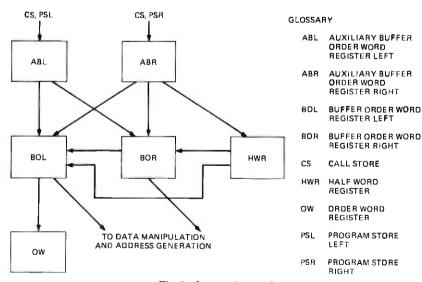

A pictorial representation of the instruction stack is shown in Fig. 2.

Fig. 2—Instruction stack.

A double-word program store reply is accepted into the ABL and ABR. If both words are required and if the BOL and BOR are available (empty), then the contents of the ABL and ABR are immediately gated down into position to be executed. If the BOL contains an instruction which has not yet started execution, and the BOR and HWR are available, then the contents of the ABL and ABR are gated to the BOR and HWR, respectively. If only the right half of the reply is required (for example, on a transfer to an odd address), then the ABR contents are gated to the BOL. Other gating paths within the stack are shown in the figure.

Instruction decoding and execution begin from the BOL with the data portion of a long instruction in the BOR. In the first cycle of execution, the contents of the BOL are duplicated in the OW and the data portion of the instruction is gated to the appropriate data-manipulation or address-calculation circuitry. The remainder of instruction decoding is performed from the OW with an overlap of decoding which assures continuity of gating and control signals.

### 3.2 Instruction execution

The 1A Processor order set is a substantially enhanced version of the No. 1 ESS order set. One of the basic requirements of the order set is to allow for the conversion of No. 1 ESS operational code into 1A Processor code via off-line translator programs with a minimum of redesign. Although the resulting order set contains some redundant features such as two address-return mechanisms, it is efficient in both real time and memory usage. The short instructions, for example, reduce required storage for programs by about 33 percent. The mask and shift facilities allow fetching a data word from memory and adjusting an item (a contiguous set of bits) within that data word in either direction with a single-word order in one memory cycle time. A double-word instruction allows detection of the least significant (right-most) one in any general-purpose register (or the logic register) and optionally clears that bit. If the register tested contains all zeros, the instruction transfers control. Conditional instructions employ the two control flip-flops storing the sign and homogeneity (all "1s" or "0s") of the result of an arithmetic or logical operation performed by either a memory read or a test instruction.

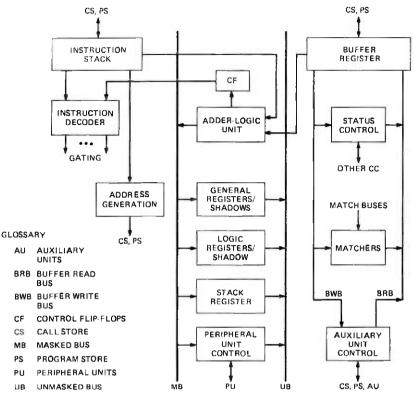

The adder and logic unit (ALU) shown in Fig. 3 is oriented to a control and decision-making type of function. The ALU performs common logical operations and fixed-point addition and subtraction using one's complement arithmetic. Arithmetic, logic, and shift functions are provided on all seven general-purpose registers. Each of these registers and the logic register, which is used both as a masking register and as a peripheral operation data reply register, has a shadow register to save data for client

Fig. 3-Central control, block diagram.

programs. Single-cycle short instructions save or restore the contents of any combination of these registers.

To optimize the use of the available code space, particularly on single-word instructions, operation codes are of variable length and may be noncontiguous. The double-word instructions provide access to the full address spectrum, which should be large enough (over four million words) to allow using the 1A Processor in any high-capacity switching application.

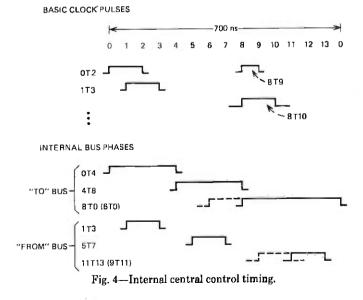

### 3.2.1 Details of execution and timing

The 700-ns central control cycle is divided into fourteen 50-ns basic clock phases. Typical clear and gate pulses are 50 ns and 100 ns in duration, respectively.

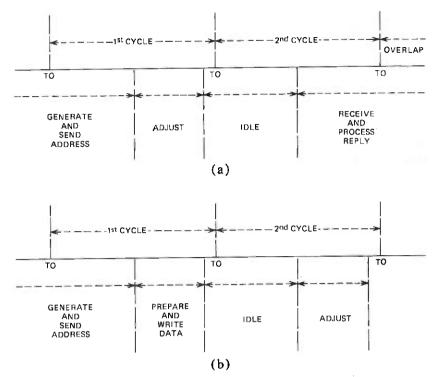

As can be seen in Fig. 3, the logical flow of instructions is centered around the use of two major internal bus systems: unmasked bus (UB) and masked bus (MB). The CC cycle is divided into three internal bus phases (0T4, 4T8, 8T0), as indicated in Fig. 4. These bus phases are intentionally unsymmetrical to allow certain data processing functions (e.g., addition) to be performed in one bus phase without penalizing the system cycle time. Even so, the longest bus phase (8T0) is extended to 6T0 for preparation of data (with parity) to be written into memory. It is desirable to execute a memory operation (read or write) within one memory cycle time. Write operations present data to the memory near the end of the first cycle of the instruction and, in the case of the 1400-ns memory, wait for a completion indication during the second cycle. In the case of a 700-ns memory, the operation is completed in one central control cycle.

The time required to perform the three basic steps of a read operation exceeds the memory cycle time by about 300 ns for either memory speed. The first step of a read operation, address generation, requires approximately 350 ns and begins by decoding the instruction as it is accepted into the instruction stack (before T12); the address is ready for transmission before T5 of the first cycle. The second step of a read operation consists of the access time of the memory system, including clock uncertainty, synchronization, cable drivers and receivers with associated logic, and bus transmission delays. For a 1400-ns memory system, this access time totals about 1050 ns; for a 700-ns memory system, about 350 ns is allocated. In either case, the data reply is available in the central control data buffer register by T12 of the appropriate cycle. The third step, processing the data reply, requires as much as 300 ns and may include performing an addition or logic operation (perhaps masking and/or complementing) and placing the result in the destination register. Thus. a read operation is not completed until almost T4 of the cycle following

the store data reply. Decoding of a new order begins as soon as it is available in the instruction stack so that the final 300 ns of the memory read operation overlaps the first 300 ns of the following operation. This overlapping results in restrictions on the use of portions of the circuitry which may be used during this 300-ns interval by each instruction. The read operation may use the data buffer register, the ALU, the masked bus, and the destination register. The operation following the read is restricted during this interval to the unmasked bus and the address generation circuitry. If the beginning instruction requires that the data being gated into the destination register of the read instruction be used for indexing or testing, the normal sequence of accessing a register via the unmasked bus is modified. In the case of indexing, the data are loaded directly from the output of the ALU into the address-generation circuit. In the case of register testing, it is sufficient to inhibit gating the previous contents of the specified register to the control flip-flops since the read operation always loads the control flip-flops from the output of the ALU.

A beginning instruction has access to adequate resources to allow at least the beginning steps of address generation to take place during the initial 0T4 interval. This initial interval is also the time during which the preparatory steps take place for index-register modification which is completed during the 4T8 bus phase. These options are discussed later in this section. Similarly, the argument register within the ALU is commonly loaded during the 4T8 phase in preparation for the 8T0 (or 6T0) data processing phase. A mask may be prepared by gating encoded instruction data from the BOL or BOR to the size-displacement translator in the ALU during 0T4 and by gating the translated (24-bit) mask to the logic register during 4T8 for use during the data processing phase. Table I summarizes the basic operations performed in each internal bus phase.

| Internal<br>Bus Phase | Activity                                                                                                                      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 0Т4                   | Address generation<br>Condition test<br>Logic functions (overlap)<br>Generate mask<br>Preload add-one logic (A-option)        |

| 4T8                   | Index register modification (A-, S-, and W-options)<br>Preload argument<br>Return address save<br>Move mask to logic register |

| STO (6TO)             | Write data to buffer register<br>Data word through ALU<br>Special register, bit, or item test                                 |

| Table I — Allocation of | internal | bus | phases |

|-------------------------|----------|-----|--------|

|-------------------------|----------|-----|--------|

The effective address is usually the sum of a data field in the instruction and either the contents of a general-purpose register (indexing) or the address of the instruction currently being executed (relative addressing). The address-generation circuitry includes a fast, carry-lookahead, two-input adder. In the relatively infrequent case that all three of the above-mentioned components must be added to produce the effective address, a second pass through the address-generation circuitry and an additional cycle are required. A single level of indirect transfer orders is provided via hardware. For indirect transfers, the effective address generated as indicated above represents the location (i.e., address) of the address to which the instruction transfers. Since a memory read must be performed, either one or two additional cycles are required. Vector table addressing is the method of indirect addressing used to address locations external to a program unit. The location of the external address is formed as the sum of the beginning of the vector table (wired address) and the data field of the instruction that serves as an index into the vector table of addresses.

Interject transfers, like vector table transfers, employ wired addresses. The interject facility is discussed in Section 3.3.

A 64-word pushdown stack for return addresses is provided to facilitate subroutine transfers. The top of the stack is the stack (S) register in the central control, and the remainder of the stack is in a reserved location in call store. Before a return address is saved in the stack register, the previous contents of that register are stored in the call store location pointed to by the stack counter. The stack (push) option requires an extra cycle to process. The pop return-address option returns the last data stored in the call store stack to the S register. The pop option requires an extra cycle to process only if the call store is a 1400-ns unit. Automatic increment or decrement of the stack counter is performed with check for overflow or underflow each time the stack is pushed or popped.

The J return-address option, provided chiefly for compatibility with No. 1 ESS translated programs, saves the return address for successful transfer instructions in the J register, which is one of the general-purpose registers. In general, execution of the J option, which saves the address of the instruction immediately following the transfer, does not add to the number of cycles required to process an instruction.

Three index-register-modification options are available: add-one (A) option, set-register (S) option, and word (W) option. These options are available on a subset of the long instructions, some of which offer only the A option due to limited code space.

The add-one option causes the contents of the index register to be incremented after the contents are used in the indexing operation. On a store instruction, if the index-register field is null, the A option is in-

terpreted as add one to memory. In this case, the register contents to be stored are incremented before the data are stored. On certain conditional transfer orders with the A option specified, the test register is incremented after the test has been performed but only if the test is successful.

For the set-register option, the index register is not used in address generation. Instead, the specified register is set to the value of the effective address. The word option is the same as the set-register option except that the contents of the index register are used in address generation in that case.

Index-register modification does not add to the time required to execute an instruction.

## 3.2.2 Typical instruction timing and cycle counts

In several cases, two normally separate instructions are encoded as a single instruction. These "combined" instructions are designed to make efficient use of the time that the CC execution circuitry is normally idle on memory-access instructions to 1400-ns memory units waiting for either a data reply (read) or a completion indication (write). During the otherwise idle time, a shift or rotate operation is performed on the data in another (usually unrelated) general-purpose register.

A combined instruction may perform a load, add, compare, product, union, or exclusive-OR read operation. The data reply from the store may be product masked with the contents of the mask register and/or complemented before the main logic operation (add, compare, etc.) is performed. Alternatively, the instruction may perform a write operation with either product or insertion masking with the contents of the logic register. Figure 5 illustrates how the adjust operation is fit into the idle data processing phase.

Minimum cycle counts for various types of orders are shown in Table II. The actual execution time for a program depends on conflicts between fetch and execution control, instruction mix, and auxiliary unit data transfers.

### 3.2.3 Typical instruction encoding

As previously mentioned, the length of an instruction is often determined by the length of the required data fields or by the particular options specified. Figure 6 shows the encoding of two typical conditional transfer orders: one short, the other long. Both of these instructions offer relative addressing, but the single-word order allows less range. The double-word order allows indexing and/or indirect addressing, while the single-word does not. Both orders provide a stack return-address option, but only the long instruction offers a J-return-address option or an

Fig. 5-Combined instruction timing. (a) Combined load. (b) Combined store.

| 47 |   | 45 | 44       | 43 41             | 40 38            | 37 | 36                         | 24 |

|----|---|----|----------|-------------------|------------------|----|----------------------------|----|

| 1  | 0 | O  | <u>+</u> | TEST<br>CONDITION | TEST<br>REGISTER | т  | RELATIVE ADDRESS INCREMENT |    |

| 47 |   |   |   |   |   |   |   |   | 38 | 37 | 36           | 34   | 33 |      | 31      | 30 | 29 | 28 | 27 | 26        | 24           |

|----|---|---|---|---|---|---|---|---|----|----|--------------|------|----|------|---------|----|----|----|----|-----------|--------------|

| 0  | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0  | A  | TES<br>CONDI | TION | RE | TEST | r<br>ER | I  | 1  | т  | R  | IN<br>REG | DEX<br>ISTER |

- A ADD ONE OPTION

- I INDIRECT ADDRESSING

- J J RETURN ADDRESS OPTION

- T STACK RETURN ADDRESS OPTION

- R RELATIVE ADDRESSING

Fig. 6—Short and long instruction encoding.

| Operation                                                              | 1400 ns<br>Store    | 700 ns<br>Store    |

|------------------------------------------------------------------------|---------------------|--------------------|

| $\mathbf{EA} \otimes \mathbf{REG} \rightarrow \mathbf{REG}$            | 1                   | 1                  |

| $EA \bigoplus REG \rightarrow REG$ $MEM \bigoplus REG \rightarrow REG$ | $\overline{2}$      | ī                  |

| $EA \rightarrow MEM$                                                   | 2                   | 1                  |

| Transfer direct                                                        | 2                   | 1                  |

| Transfer indirect                                                      | 4                   | 2                  |

| Combined                                                               | 2                   | 2                  |

| Search (N words) <sup>†</sup>                                          | $2N + \overline{1}$ | $N + \overline{1}$ |

# Table II - Typical cycle counts

EA Effective address. MEM Any memory location.

Operation.

Note: Add 1 cycle if order is both relative and indexed.

<sup>†</sup>The search instruction facilitates a sequential search of memory for a selected code.

add-one option. For the particular long transfer selected, the A option causes incrementing of the test register rather than the index register if the test is successful.

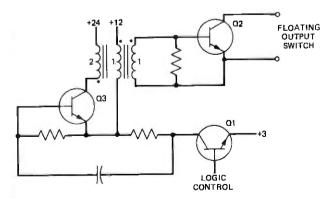

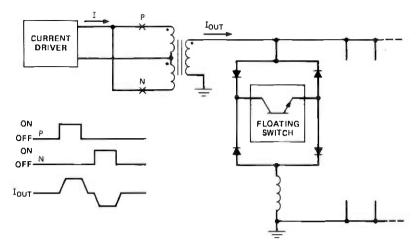

# 3.2.4 Peripheral operations

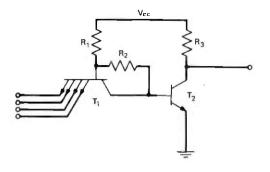

Central control monitors and controls the peripheral system by transmitting information to the peripheral units (PUs) which perform the functions of scanning, signal distribution, and network control. The CC communicates with the PUs by one of three methods. The first method, coded enabling, involves addressing PUs by transmitting an enable code to be accepted by the appropriate unit in a manner analogous to store operations. The second method, CPD enabling, requires a central pulse distributor such as that used in No. 1 ESS. Polling, the last method, employs a maintenance control pulse to obtain status from several PUs simultaneously.

Peripheral units may be located as far as 137 meters and 385 meters from the CC for CPD and coded enabling, respectively. Upon initiation of a PU operation, control is passed from instruction-execution control to peripheral-operation control, and nonconflicting instructions may be processed during the remainder of the peripheral operation. Conflicting instructions are those that either use or change the logic register, peripheral data register, or peripheral enable address register. If execution control encounters a conflicting instruction, it stalls until informed by peripheral operation control that the peripheral operation is complete.

Coded enable operations are performed on a variable-cycle basis, except for a limited class of orders intended for line scanning which are executed at a fixed rate. Variable-cycle operations were adopted to gain speed during peripheral operations. The first two cycles of coded-enable operation are used to set up the enable address and peripheral data registers and may require a store access. Address and data are transmitted in the third cycle and the CC waits as long as 30 additional cycles for a response. If no completion indication is received by the end of that interval, an interrupt flag is set. CPD enable operations are performed on a fixed-cycle basis with different types of operations requiring different numbers of cycles. Operating on a predetermined cycle basis facilitates the overlap of repetitive operations. When operating in an overlap mode, repetitive scanning operations typically require either 10 cycles (trunk or line scanning) or 11 cycles (digit scanning), and nonscanner operations repeat in 14 cycles. In a typical sequence, the first two cycles are required to set up CC registers. Address information is sent to the CPD in the third cycle. The CPD transmits the peripheral address shortly thereafter, and the CC awaits completion of the operation. On scanning operations, a data reply into the logic register is expected.

Each PU which receives a polling control pulse from central control returns a status indication such as whether or not a data buffer is full. Units respond into uniquely defined positions in the reply register. A PU polling operation consumes 32 cycles unless it is terminated early by encountering a logic-register-usage instruction which, in effect, allows a software-controlled early termination.

# 3.3 Interrupt system

An interrupt causes program control to be passed from the current program to the program corresponding to the interrupt level. The higher priority interrupt levels are maintenance oriented whereas the lower levels are processing oriented. The immediacy of interrupt recognition by central control is a function of the type of interrupt (maintenance or processing), the level of the interrupt, whether the software-controlled inhibit is set, and the instruction sequence currently being executed. Under certain conditions, for example, couplets of instructions or AU data transfers may be allowed to complete before an interrupt is recognized.

When an interrupt is recognized by central control, the interrupt system saves vital information in memory that might otherwise be destroyed before it could be saved via software control. This vital information includes the return program execution address, the contents of the data buffer register, and the value of the control flip-flops. The last program word fetched (ABL/ABR) is saved if the error indication points to a problem encountered on that fetch operation. On maintenance levels, the interrupt system also freezes a group of save registers which are useful for fault recognition (save data address, save program address,

save current address, and so on). When a CC mismatch is detected, the matchers are halted to preserve the mismatched data. Finally, the interrupt system initializes fetch and execution control and sets up a transfer to the appropriate interrupt level program. Having completed this sequence, the interrupt system releases fetch and execution control and allows software to perform its tasks. Next, a go-back-to-normal sequence is initiated which restores the CC to its preinterrupt state. The severity of the interrupt will determine whether or not the interrupted program is continued.

For fault situations, it is important that the level of interrupt taken be the lowest consistent with the failure indication. A main memory parity failure, for example, is not allowed to cause a CC mismatch since the latter is a higher level of interrupt.

The processing level interrupts are provided in the CC to facilitate the administration of software tasks such as input/output which must be performed within specified intervals of time. Similarly, the interject facility is used to efficiently interpose priority processing in the normal cycle of program tasks. Flags (flip-flops), which indicate that interject tasks need to be performed, may be set in the CC either by program control or by hardware in various units external to the central control (e.g., auxiliary units) that require attention. Some of these interject flags are maintenance oriented but are deferrable and should therefore not set a maintenance-level interrupt source. Certain base-level programs utilize transfer instructions which test the interject flags. An automatic check is made on this mechanism by a processing level interrupt which occurs if no interject work is performed within 10 ms.

### 3.4 Auxiliary unit data transfers

Direct handling of the data involved in the auxiliary unit (AU) data transfer tasks by CC execution control would require a significant amount of real time and, therefore, the control of these data transfers is handled largely by separate control on a cycle-stealing basis.

Although the AU system is connected directly to the central controls, the CCs do not have direct access to the data stored on the disks and tapes. Instead, the requests that data be transferred between bulk storage and main memory are placed in main memory by administrative software. The auxiliary unit controller receives the location of request details and initiates the data transfer. Once a job is initiated, the AU system processes the request by transferring one word at a time through the CC, allowing the CC to resolve the bus conflicts between itself and the AU. The CC gives the AU bus priority about 25 percent of the time to keep AU buffer overflows within bounds.

CONTROL SYSTEM 151

# 3.4.1 AU priority system and signaling

Central control can accommodate up to 16 auxiliary unit interface ports. In the case of multiple requests from AU<sub>8</sub> for bus usage, the CC administers bus granting on a priority structure. The AU ports are divided into two groups of eight members each. Any AU within the first group may, under program control, be assigned highest priority; members of the second group have a wired priority that is lower than that assigned to any members of the first group.

Each AU memory operation requires three cycles. The first cycle is used to establish communication between the CC and an AU. The following two cycles correspond to the actual memory operation during which the AU interface control in the CC controls buffering of the address and data information. The buffering is performed so that all memories appear to the AU to be 1400-ns memories.

Auxiliary units requiring access to the store submit requests to the CC near the beginning of the first cycle. The AU interface control in CC sends an enable to the requesting AU with the highest priority. The enabled AU replies with address information and a verify signal. If the communication path is available, a storage-access-permitted signal is sent to the AU and the AU returns a recognition signal. If the communication path is not available, a storage-access-permitted signal is not sent and the AU is blocked and must request again.

### 3.4.2 Bus usage administration

The operations of instruction fetching, data fetching and storing by execution control, and passing of information between main and auxiliary storage all require access to main memory. To conserve real time, execution control is normally given highest priority, fetch control is given second priority, and the AU system is normally relegated to lowest priority. However, the number of AU data-transfer tasks that must be aborted due to overflow of buffers is minimized by allowing AU system bus usage if this system is blocked in three successive attempts to obtain bus usage. The fetch or execution control may use the bus (call or program store) not required by the AU system since only a single AU task is allowed memory access at any time.

# 3.5 Address structure and memory protection

An address containing 22 bits allows accessing memory of up to 4.2 million words. For compatibility with No. 1 ESS programs, an alternate mode is available under program control that uses only 21 bits. In either case, the lower half of the address spectrum is assigned to call store. Except for a few thousand addresses near the top of the spectrum (which

are used for direct access of CC registers, file store controller registers, and so on), the upper half of the spectrum is assigned to program store.

It is essential to protect areas of the memory spectrum which are not duplicated within main memory such as program and translation stores, and areas which vitally affect system operation such as CC internal registers, disk controller registers, main program constants, interrupt bins, etc. Therefore, the memory address spectrum is divided into protected and unprotected areas each requiring different write instructions. An interrupt results if the address is incompatible with the instruction. Typically, only a portion of call store lies in the unprotected area. The lower- and upper-protected area registers in the CC, which define the secure and unsecure areas of the spectrum, are software controllable via secure write instructions.

### **IV. PROCESSOR COMMUNICATIONS**

# 4.1 Definitions and characterization

Communication between units of the 1A Processor and between the 1A Processor and the network take place over a system of high-speed digital communication channels called buses. Each bus is made up of a number of parallel channels and each channel consists of a balanced wire pair and associated transmitting and receiving circuits. Transformer coupling is employed between the bus and the transmitting and receiving circuits.

Information on a bus is represented by the presence or absence of pulses on the individual wire pairs. Information is passed between units in parallel form with pulses sent simultaneously over a group of wire pairs.

### 4.2 Objectives of the bus system

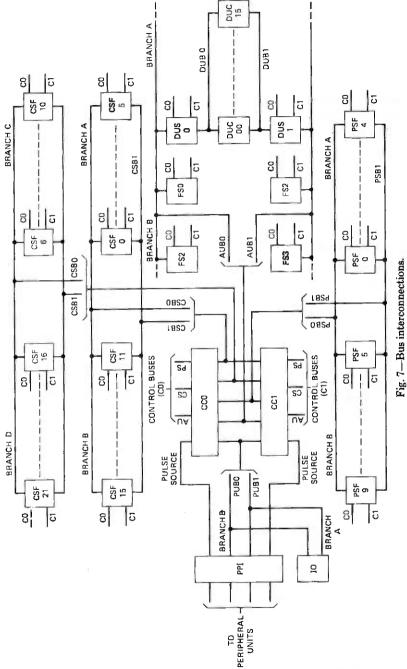

The 1A Processor bus system was designed to meet two primary objectives: to provide reliable communications and to be compatible with the No. 1 ESS peripheral units. To meet these objectives, the various bus groups are duplicated as shown in Fig. 7. Bus duplication methods are covered in a later section. In addition to required information channels, each bus provides channels for parity bits which are used for error detection. Pulse transformers help to achieve reliable bus operation. These pulse transformers have electrostatic shields and high-voltage breakdown characteristics for protection against longitudinal noise signals and induced currents or voltages caused by lightning strikes or power faults. Further, failure-conducive stress conditions on bus circuit devices are avoided by using devices well within allowable operating ranges.

Another bus system objective is to achieve a speed compatible with the 1A Processor digital circuits. A cable with irradiated polyvinylchloride (IPVC) insulation is used between frames. This cable has controlled propagation delay and pulse-dispersion characteristics to minimize delay variations and degradation of pulse rise times. Within the processor frames, Teflon\*-insulated cable is used for proper impedance matching and low propagation delay.

Bus driver and receiver circuits are also designed to minimize propagation delays and delay variations. This has been made possible by placing all circuit components for drivers or receivers on a circuit board and by the electrical design itself.

Another important feature is ease of bus cable installation and improved maintenance features. Use of pretested, connectorized bus cables between frames permits quick initial installation and simplifies subsequent bus growth for system additions. Connectorized cables also eliminate the common problem of wiring bus pairs incorrectly during bus installation.

Bus repair time is reduced with the use of connectorized cables and with bus circuit components mounted on plug-in circuit packs. To troubleshoot bus problems, access points are provided on bus-termination resistor assemblies. These resistor assemblies are connectorized and slip over the connectors of bus packs located at the ends of a bus.

#### 4.3 Bus configurations

Two types of buses, shared and private, are used for communication between units of the processor. Shared buses branch out from the central control in two directions and are multipled from frame to frame, carrying data that is common to all frames on a bus. Private buses are connected between the CC and individual frames and are used for synchronization and control information. Cable assemblies consisting of eight wire pairs are used for both private and shared buses.

#### 4.4 Bus system characteristics

The various bus groups are arranged into two main bus systems, the processor-unit bus system and the peripheral-unit bus system. Buses interconnecting units of the processor are included in the processor system. The peripheral bus system consists of buses providing communication between the processor and peripheral frames.

The processor bus system is designed for minimum delay. This objective was achieved by using the following:

<sup>\*</sup> Tradename of E.I. Dupont de Nemours & Co.

- (i) A high-speed cable driver to minimize circuit delay and recovery time.

- (ii) A passive cable receiver capable of extracting sufficient energy from the bus to drive a low impedance without introducing an impedance discontinuity and unwanted pulse reflections.

The properties of the processor bus system are tabulated in Table III. A pulse amplitude of 7.2 V is determined by the minimum signal required by a receiver at the end of a bus having the maximum number of 10 receivers connected to it. Adequate pulse width at this receiver under worst-case timing variations is provided by a nominal 100-ns-wide pulse. The narrow pulse allows use of 700-ns memory units as well as 1400-ns memory units.

To minimize the worst-case bus cable delay on call-store and program-store buses, these cables are routed in a loop between the central control and the stores. That is, address and write cables are connected to the first store frame on a bus branch while the data-reply cables are run directly from the furthest frame. The shorter length of the reply cable compensates for the furthest store having the longest bus distance for address and write data.

The peripheral unit bus design provides an adequate signal over a long bus having up to 50 receivers connected to it. This design was implemented by the use of the following:

- (i) A cable driver that provides a 500-ns bus pulse to compensate for pulse dispersion (rise-time degradation) and bit-to-bit timing variations inherent with long, fully loaded buses.

- (ii) A cable receiver with an active gate for bus signal amplification, resulting in a minimum amount of energy being extracted from the bus.

Table III also lists the peripheral bus system characteristics. For compatibility with the No. 1 ESS peripheral units,<sup>1</sup> the 9.3-V pulse amplitude provides a sufficient signal for 50 receivers over a 137-m bus length. A minimum cycle time of 2800 ns was determined to be the time needed for bus circuits to recover, and permit system execution of peripheral instructions at maximum speed.

Bus length, as shown in Table III, may be increased by the use of a repeater for regenerating bus pulses in order to reach a maximum 385-m length with up to 50 receivers on the bus.

#### 4.5 Bus system organization

Four bus groups make up the processor unit bus system: the call store bus (CSB), program store bus (PSB), auxiliary unit bus (AUB), and data unit bus (DUB). The call store bus group consists of two buses or four

| Bus             | Bus<br>Pulse<br>Amplitude<br>(v) | Bus<br>Pulse<br>Width<br>(ns) | Min<br>Cycle<br>Time<br>(ns) | Max<br>Loop<br>Length*<br>(m)            |

|-----------------|----------------------------------|-------------------------------|------------------------------|------------------------------------------|

| Call store      | 7.2                              | 100                           | 700                          | 18.6                                     |

| Program store   | 7.2                              | 100                           | 700                          | 18.6                                     |

| Auxiliary unit  | 7.2                              | 100                           | 700                          | 30.5                                     |

| Data unit       | 9.3                              | 500                           | 2800                         | 143.2                                    |

| Peripheral unit | 9.3                              | 500                           | 2800                         | 274.3 <sup>†</sup><br>769.4 <sup>‡</sup> |

## Table III --- Bus characteristics

\* Bus length includes path length through connectors and circuit packs.

\* With 50 receivers connected.

\* With bus repeater.

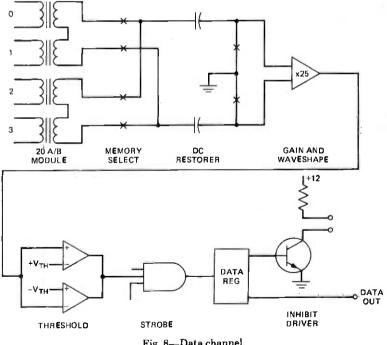

| Table IV(a) Call stor | e bus lavout |

|-----------------------|--------------|

|-----------------------|--------------|

| Bus Group                                    | Bit Names                                                                                                                                                                                                                                         | Function/Definition                                                                                                         |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Call<br>Store<br>Address                     | $\begin{array}{c} \mathrm{CSA00} \rightarrow \mathrm{CSA15} \\ \mathrm{CSA16} \rightarrow \mathrm{CSA20} \\ \mathrm{CSAMP} \\ \mathrm{CSA3T5} \\ \mathrm{CSA1T3} \\ \mathrm{CSAM} \\ \mathrm{CSAC} \\ \mathrm{CSAW} \\ \mathrm{CSAR} \end{array}$ | Data location address<br>K-code<br>Address parity<br>Timing<br>Maintenance mode<br>Control mode<br>Write mode<br>Reply mode |

| Call<br>Store<br>Write                       | CSWE<br>CSWP2<br>CSWP1<br>CSW00 → CSW23                                                                                                                                                                                                           | Write enable<br>Data parity<br>Data parity<br>Data                                                                          |