# **ELECTRONIC RECORDING PRODUCTS**

# MAINTENANCE

# **TR-22 Television Tape Recorder**

**SERVO SYSTEMS**

#### EQUIPMENT LOST OR DAMAGED IN TRANSIT

When delivering the equipment to you, the truck driver or carrier's agent will present a receipt for your signature. Do not sign it until you have (a) inspected the containers for visible signs of damage and (b) counted the containers and compared with the amount shown on the shipping papers. If a shortage or if evidence of damage is noted, insist that notation to that effect be made on the shipping papers before you sign them.

Further, after receiving the equipment, unpack it and inspect thoroughly for concealed damage. If concealed damage is discovered, immediately notify the carrier, confirming the notification in writing, and secure an inspection report. This item should be unpacked and inspected for damage WITHIN 15 DAYS after receipt. Report all shortages and damages to RCA, Broadcast and Television Department, Camden 2, N. J.

Radio Corporation of America will file all claims for loss and damage on this equipment so long as the inspection report is obtained. Disposition of the damaged item will be furnished by RCA.

#### **REPLACEMENT PARTS AND ENGINEERING SERVICE**

RCA field engineering service is available at current rates. Requests for field engineering service may be addressed to your RCA Broadcast Field Representative or the RCA Service Company, Inc., Broadcast Service Division, Camden, N. J. Telephone: WOodlawn 3-8000.

When ordering replacement parts, please give symbol, description, and stock number of each item ordered.

The part which will be supplied against an order for a replacement item may not be an exact duplicate of the original part. However, it will be a satisfactory replacement differing only in minor mechanical or electrical characteristics. Such differences will in no way impair the operation of the equipment. Parts with no stock numbers are standard components. They are not stocked by RCA and should be obtained from your local electronic parts distributor.

The following tabulations list service parts and electron tube ordering instructions according to your geographical location.

#### SERVICE PARTS

| LOCATION                                                                           | ORDER SERVICE PARTS FROM:                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Continental United States, including Alaska<br>and Hawaii                          | RCA Parts and Accessories Department, P.O. Box 654, Camden,<br>New Jersey or through your nearest RCA Regional Office. Emergency<br>orders may be telephoned, telegraphed, or teletyped to RCA Emer-<br>gency Service, Bldg. 60, Camden, N. J. (Telephone: WO 3-8000). |

| Dominion of Canada                                                                 | RCA Victor Company Limited, 1001 Lenoir Street, Montreal, Quebec or through your local Sales Representative or his office.                                                                                                                                             |

| Outside of Continental United States, Alaska,<br>Hawaii and the Dominion of Canada | RCA International Division, Clark, N. J., U.S.A. or through your local Sales Representative.                                                                                                                                                                           |

#### ELECTRON TUBES

| LOCATION                                                                           | ORDER ELECTRON TUBES FROM:                                                                                                                    |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Continental United States, including Alaska<br>and Hawaii                          | Local RCA Tube Distributor.                                                                                                                   |

| Dominion of Canada                                                                 | RCA Victor Company Limited, 1001 Lenoir Street, Montreal, Quebec or through your local Sales Representative or his office.                    |

| Outside of Continental United States, Alaska,<br>Hawaii and the Dominion of Canada | Local RCA Tube Distributor or from:<br>Tube Department<br>RCA International Division<br>30 Rockefeller Plaza<br>New York 20, New York, U.S.A. |

#### **RETURN OF ELECTRON TUBES**

If for any reason, it is desired to return tubes, please return them through your local RCA tube distributor, RCA Victor Co. Ltd., or RCA International Div., depending on your location.

Please do not return tubes directly to RCA without authorization and shipping instructions.

It is important that complete information regarding each tube (including type, serial number, hours of service and reason for its return) be given. When tubes are returned, they should be shipped to the address specified on the Return Authorization form. A copy of the Return Authorization and also a Service Report for each tube should be packed with the tubes.

#### LIST OF RCA SALES OFFICES

Atlanta 3, Georgia 1121 Rhodes-Haverty Bldg. 134 Peachtree St. N.W. 524-7703

*Chicago 54, 111.* Merchandise Mart Plaza Room 2000 — 467-5900

> Burbank, Calif. 2700 Olive Street 849-6741

New York 20, New York 36 W. 49th St. MU 9-7200 Dedham, Mass. Dedham Office Park 866 Washington St. DAvis 6-8850

Cleveland 15, Obio 1600 Keith Bldg. CHerry 1-3450

Indianapolis, Ind. 501 N. LaSalle St. MElrose 6-5321

Portland 12, Oregon 1841 N.E. Couch St. 232-5343 Camden 2, N. J. Building 15 WOodlawn 3-8000

Dallas, Texas

7901 Carpenter Freeway MElrose 1-3050

Kansas City 14, Missouri

7711 State Line Road

EMerson 1-6770

San Francisco 2, Calif.

420 Taylor St.

ORdway 3-8027

Charlotte 4, N. C. 504 Charlottetown Mall 333-3996

> Detroit 39, Mich. 12605 Arnold St. KEnwood 4-5100

Memphis, Tenn. 3189 Summer Ave. FAirfax 4-4434

Seattle 4, Washington 2250 First Ave., S. MAin 2-8350

West Palm Beach, Fla. 645 S. Military Trail 683-2219

BTE-9

Washington 6, D. C. 1725 K St., N.W. FEderal 7-8500

# ELECTRONIC RECORDING PRODUCTS

MAINTENANCE

# **TR-22 Television Tape Recorder**

**SERVO SYSTEMS**

RADIO CORPORATION OF AMERICA

BROADCAST AND COMMUNICATIONS PRODUCTS, CAMDEN, N. J. PRINTED IN U.S.A.

GO 634

## TABLE OF CONTENTS

|                                     | Page |

|-------------------------------------|------|

| HEADWHEEL SERVO                     | . 1  |

| Systems Description                 | . 1  |

| General                             | . 1  |

| RECORD Mode                         | . 1  |

| PLAY Mode                           | . 2  |

| Setup Procedure                     | . 6  |

| Module Circuit Analyses             |      |

| Reference Generator                 |      |

| Reference Generator (International) |      |

| Tonewheel Processor                 |      |

| Tonewheel Servo                     |      |

| Headwheel Modulator                 | . 40 |

| Linelock                            |      |

| Tape Sync Processor                 |      |

| Tape Sync Processor (International) |      |

|                                     |      |

| CAPSTAN SERVO                       |      |

| Systems Description                 |      |

| General                             |      |

| RECORD Mode                         |      |

| PLAY Mode                           |      |

| Setup Procedure                     |      |

| Module Circuit Analyses             |      |

| Control Track Record/Playback       |      |

| Capstan Phase                       |      |

| Capstan Phase (International)       |      |

| Capstan Error                       |      |

| Capstan Oscillator                  | 119  |

| VACUUM GUIDE SERVO                  | 128  |

| Systems Description                 | 128  |

| Module Analysis                     | 131  |

| General                             |      |

| Automatic Guide Control             |      |

| Manual Guide Control                |      |

| Setup Adjustments                   |      |

| Jog Adjustment                      |      |

| Zero Adjustment                     |      |

| Trouble-Shooting Chart              |      |

|                                     |      |

| POWER AMPLIFIERS                    |      |

| Module Circuit Description          |      |

| Maintenance                         | 149  |

.

## LIST OF ILLUSTRATIONS

| He  | oure |

|-----|------|

| 1.1 | yure |

|     |      |

| gure        |                                                                                           | Page     |

|-------------|-------------------------------------------------------------------------------------------|----------|

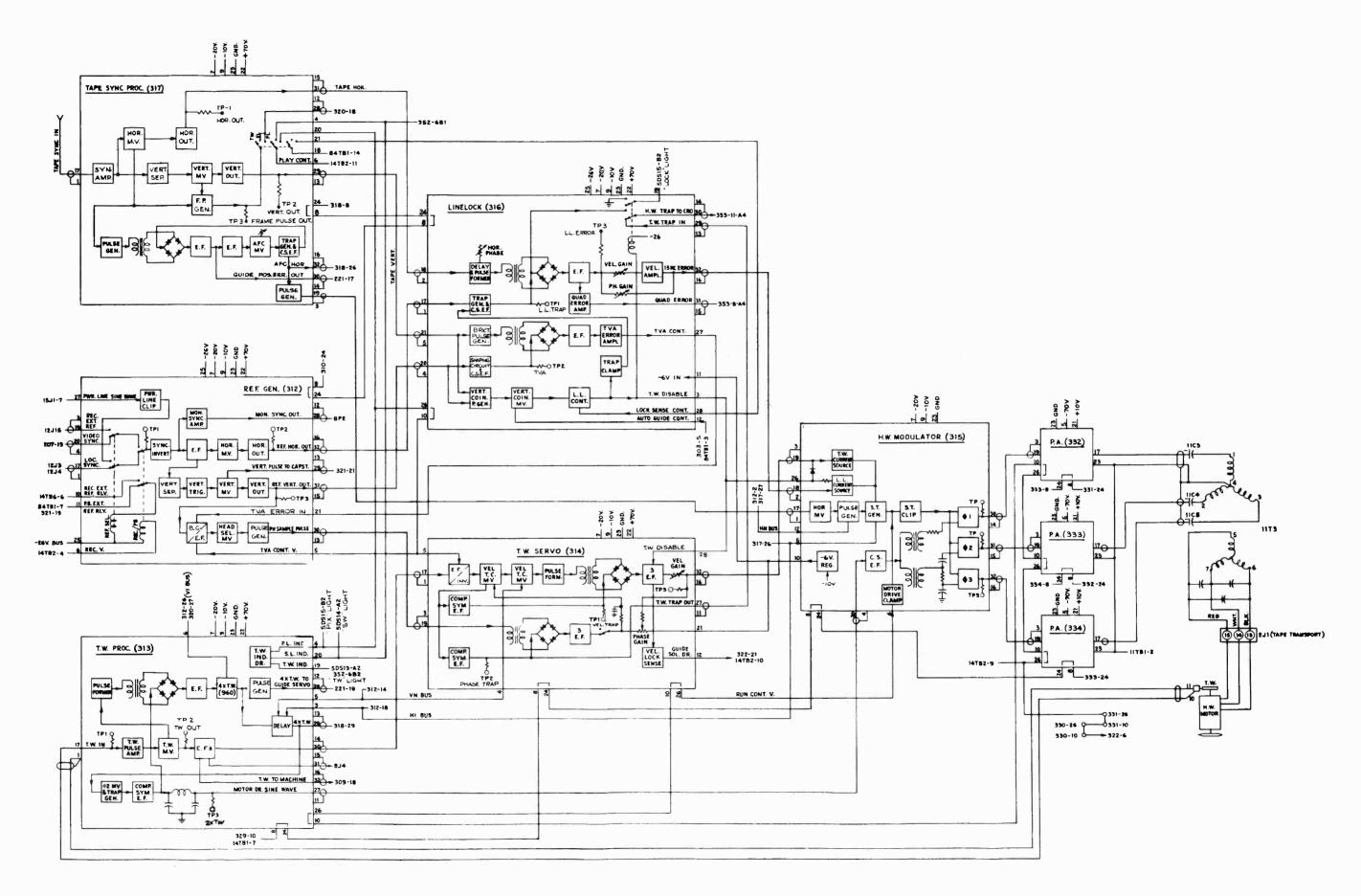

| 1.          | Simplified Block Diagram of Headwheel Servo in Tonewheel Mode with TVA                    | 2        |

| 2.          | Simplified Block Diagram of Headwheel Servo in Linelock Mode                              |          |

| <br>3.      | Reference Generator Module Block Diagram                                                  |          |

| 4.          | Power Line Clipper and Relay Circuits                                                     |          |

| 5.          | Reference Horizontal and Monitor Sync Pulse Generator                                     |          |

| 6.          | Vertical Sync Separator and Pulse Generator                                               |          |

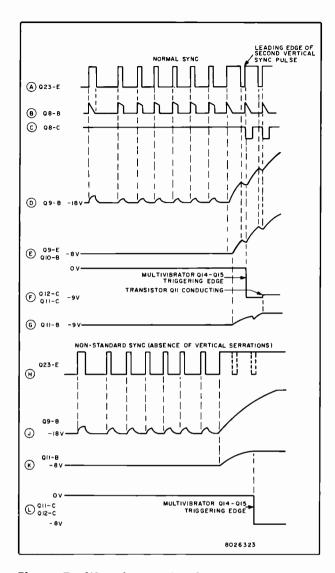

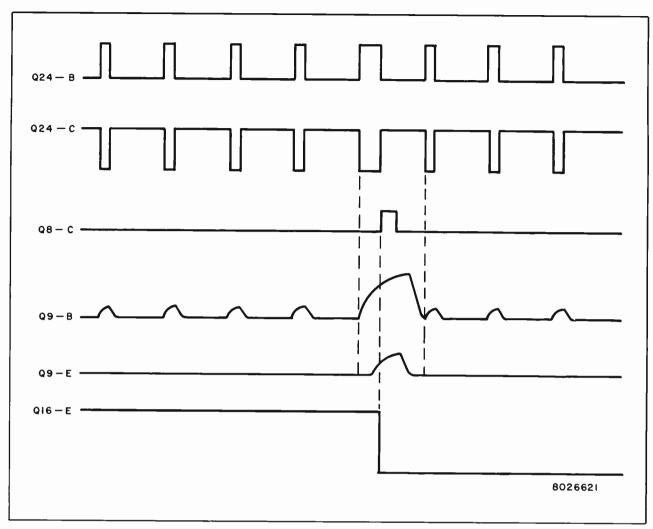

| 7.          | Waveforms Showing Development of Multivibrator Q14-Q15 Triggering Pulse                   |          |

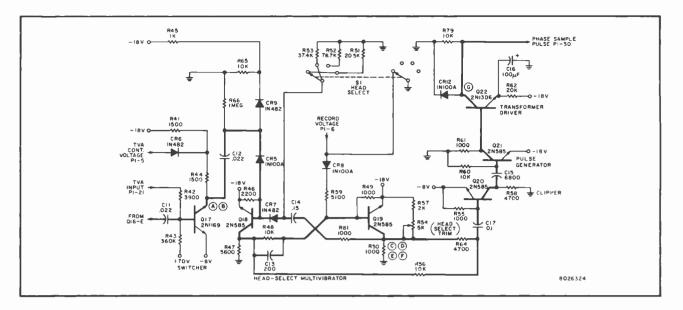

| 8.          | Head Select Multivibrator and Phase Sample Pulse Generator                                |          |

| 9.          | International Reference Generator Module Block Diagram                                    |          |

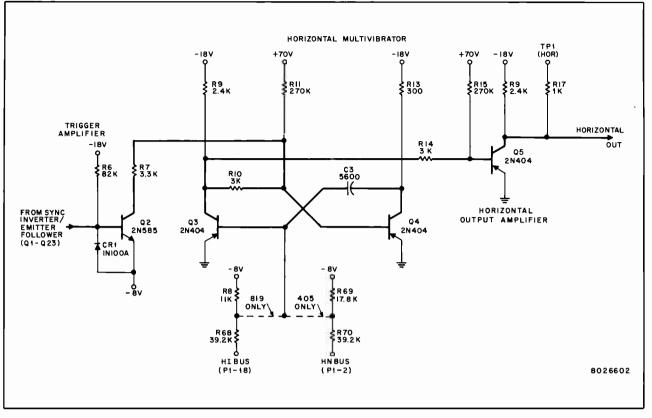

| 10.         | Horizontal Multivibrator                                                                  |          |

| 11.         | Vertical Sync Separator Circuit                                                           |          |

| 12.         | Vertical Sync Separation in 819-Line French System                                        |          |

| 13.         | Head Select Multivibrator                                                                 |          |

| 14.         | Tonewheel Processor Module Block Diagram                                                  |          |

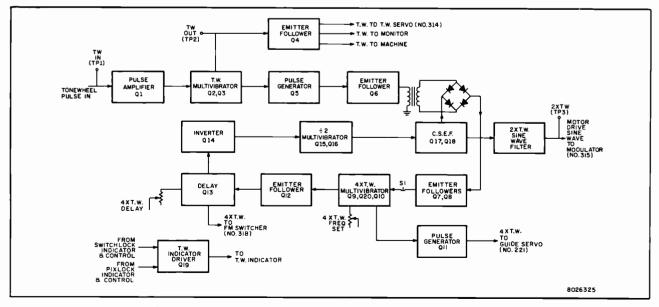

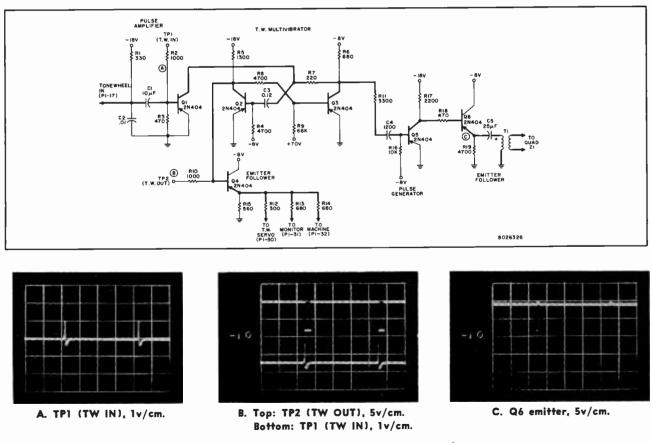

| 15.         | Pulse Amplifier and Tonewheel Multivibrator                                               |          |

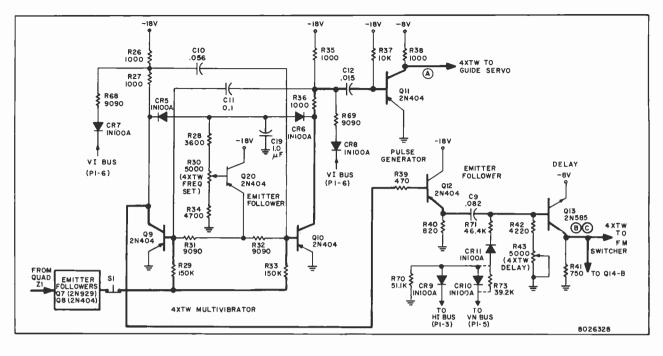

| 16.         | 4XTW Multivibrator and Delay Circuits                                                     |          |

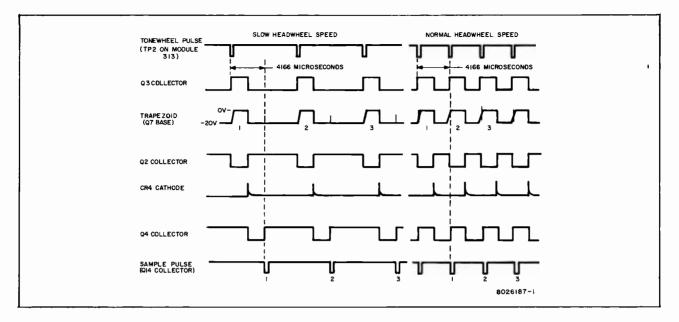

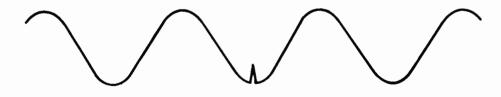

| 17.         | Oscillator Circuit Waveform Relationships                                                 |          |

| 18.         | 4XTW Divide-by-Two Multivibrator and Trapezoid Generator                                  |          |

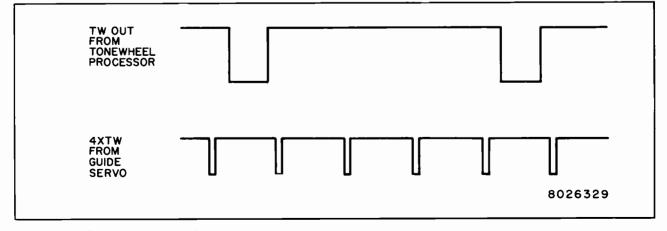

| 19.         | Waveform Relationships for Correct 4XTW Frequency Adjustment                              | 29       |

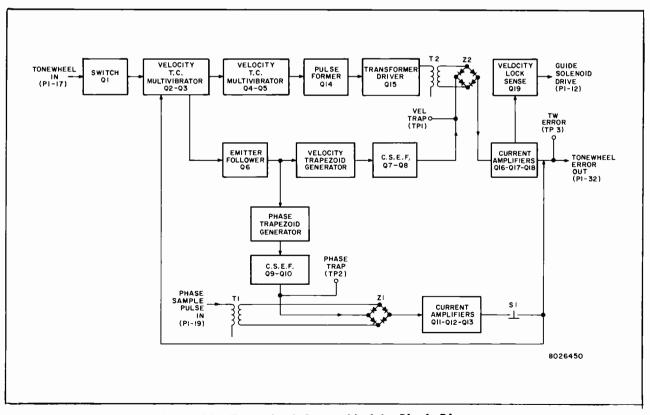

| 20.         | Tonewheel Servo Module Block Diagram                                                      |          |

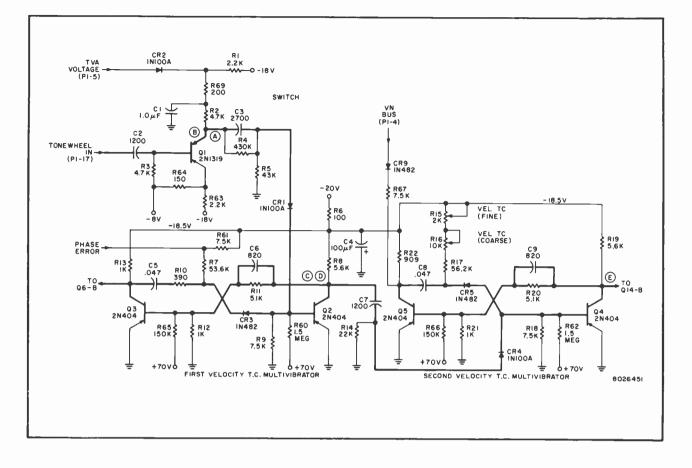

| 21.         | Velocity Time Constant Multivibrators                                                     |          |

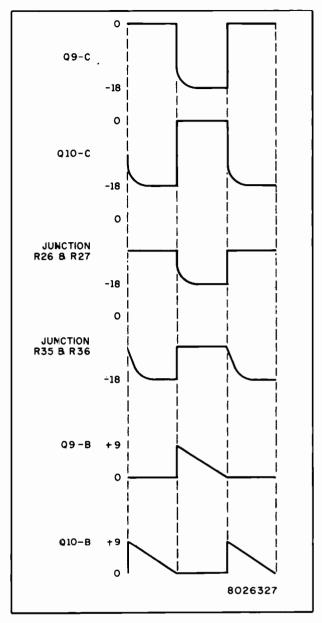

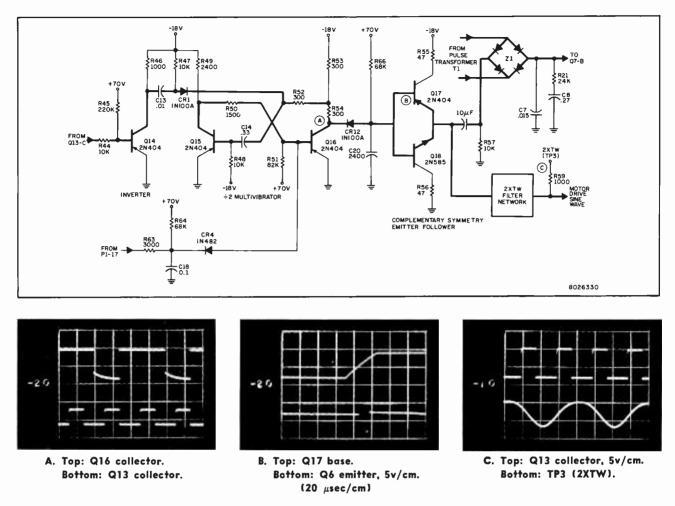

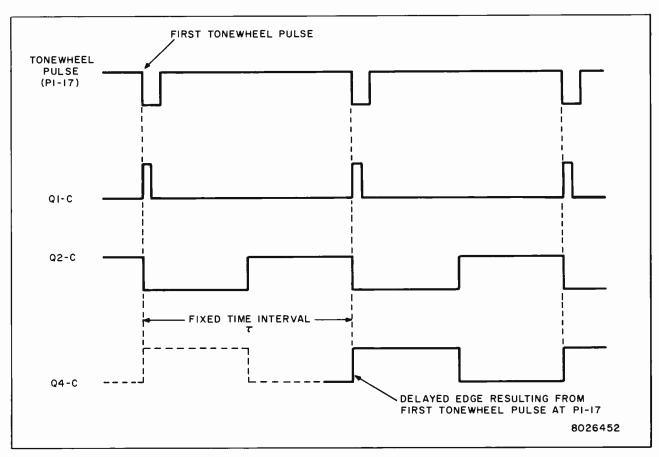

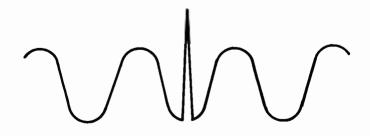

| 22.         | Waveform Timing Relationships in the Velocity Time Constant Multivibrator Circuits        |          |

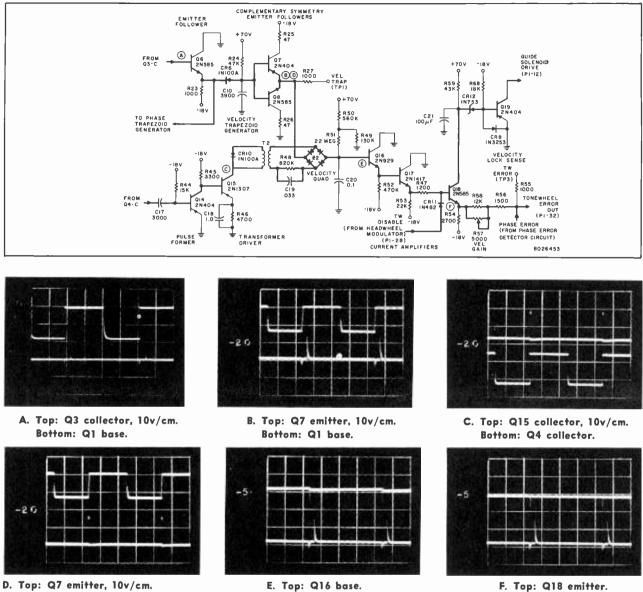

| 23.         | Velocity Error Detector and Amplifiers                                                    |          |

| 24.         | Waveforms Indicating Sample Pulse Positioning Relative to Reference Trapezoid Slope (525- |          |

|             | Line Standards)                                                                           |          |

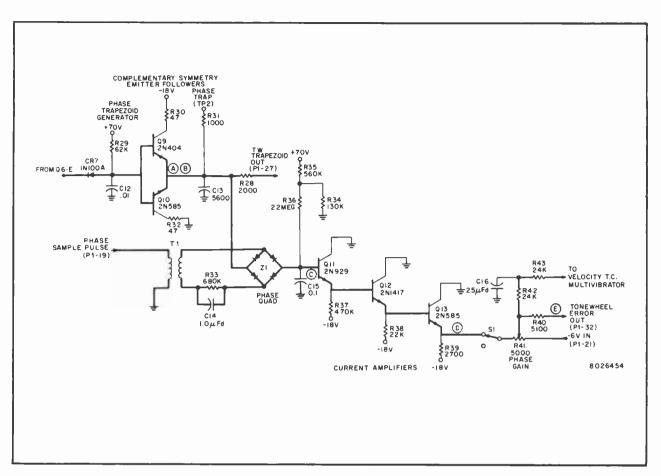

| 25.         | Phase Error Detector and Amplifiers                                                       |          |

| 26.         | Headwheel Modulator Module Block Diagram                                                  |          |

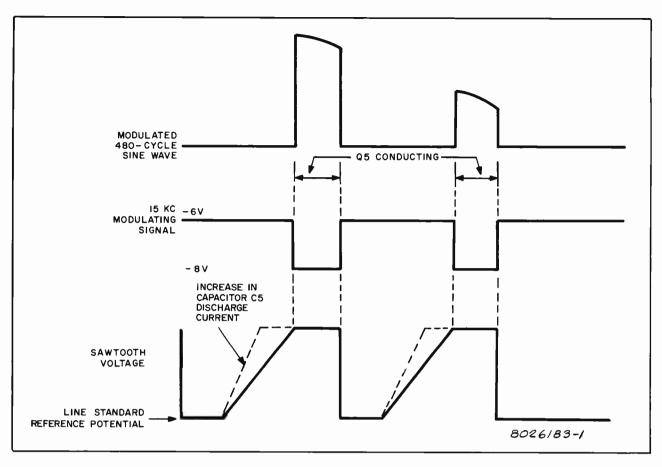

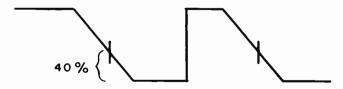

| 27.         | Variation in 480-Cycle Sine Wave Amplitude as Width of 15.75 kc Modulating Pulse Varies   |          |

| 28.         | Modulation Pulse Generator                                                                |          |

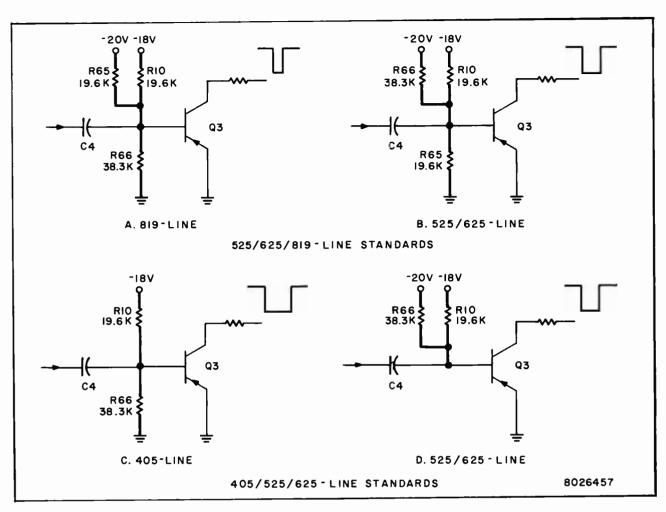

| 29.         | Transistor Q3 Biasing Networks as Determined by the Line Standard Used                    | 45<br>43 |

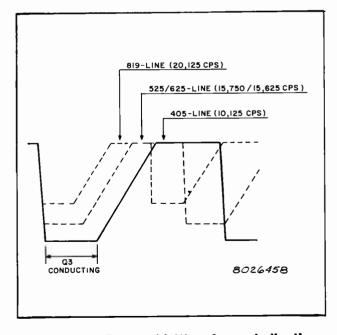

| 30.         | Trapezoid Waveforms Indicating Slopes Independent of Line Standards                       | 45<br>44 |

| 31.         | Effect of an Increase in Capacitor Discharge Current on the Sawtooth Voltage Waveform     |          |

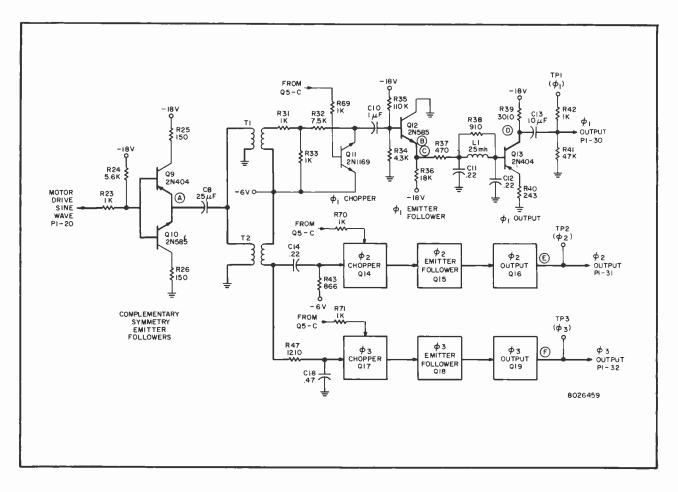

| 32.         | Modulator and Amplifier Circuits                                                          |          |

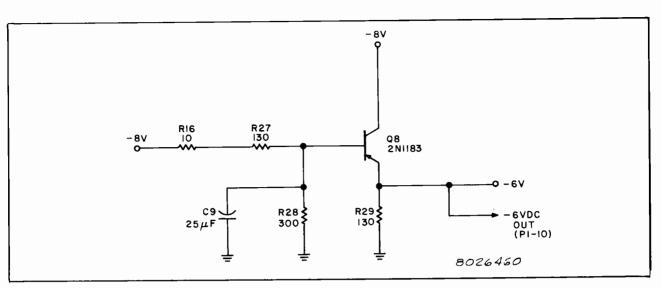

| 33.         | -6 Volt DC Power Circuit                                                                  |          |

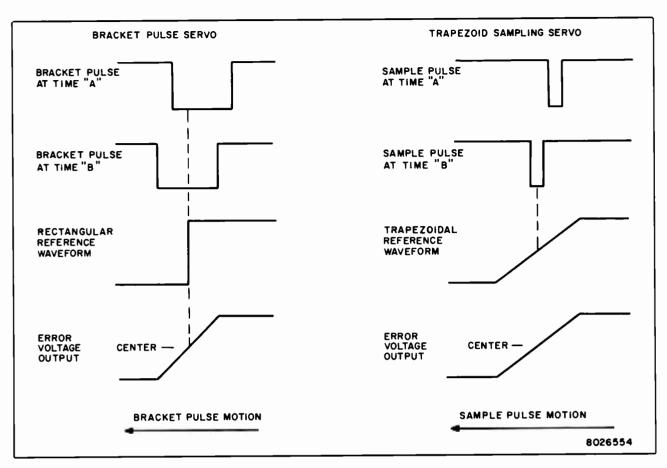

| 34.<br>25   | Bracket Pulse and Trapezoid Sampling Servo Waveforms                                      | 49       |

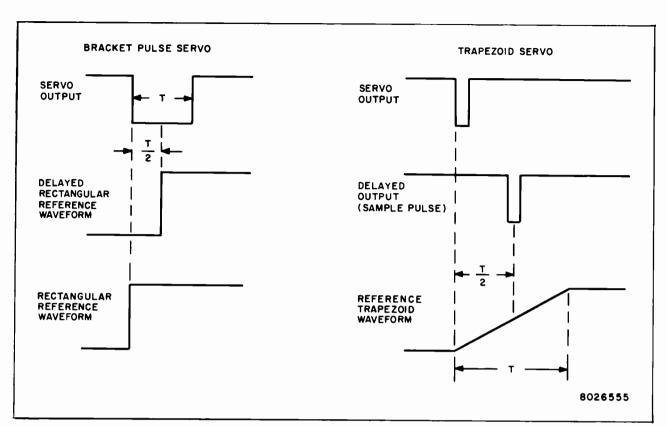

| 35.<br>36.  | Half-Pulse and Half-Slope Delays                                                          |          |

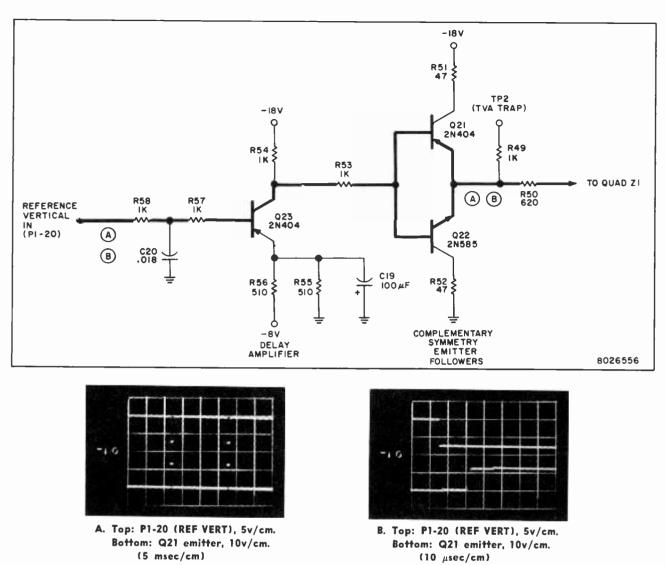

| 37.         | Reference Vertical Delay Generator                                                        |          |

| 38.         | Bracket Pulse Generator and Error Detector                                                |          |

| 39.         | Vertical Coincidence Pulse Generator and Lock Sense Control                               | 54       |

| 40.         | Pixlock Trapezoid Generator                                                               |          |

| 41.         | Pixlock Trapezoid Waveforms                                                               |          |

| 42.         | Tape Horizontal Delay and Sample Pulse Generator                                          |          |

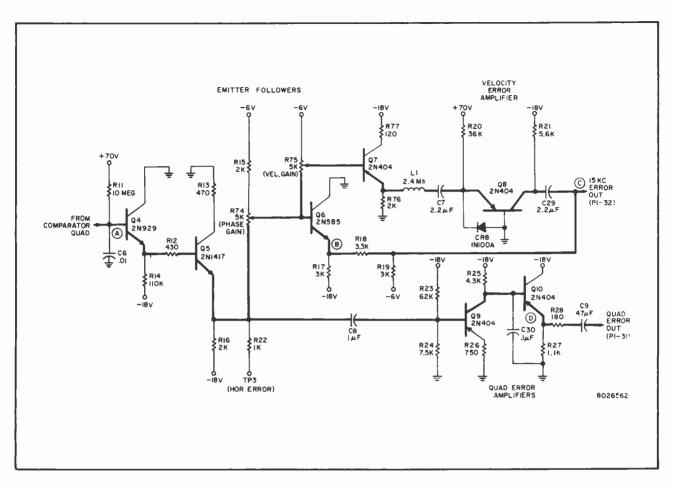

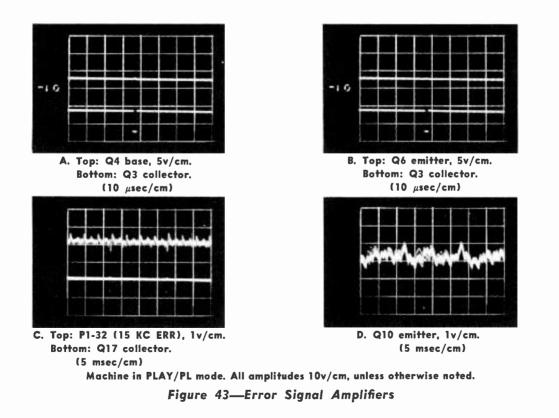

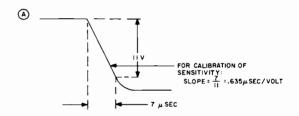

| 43.         | Error Signal Amplifiers                                                                   |          |

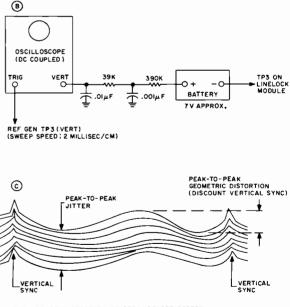

| <b>4</b> 4. | Measurement of Jitter and Geometric Distortion                                            |          |

| <b>45</b> . | Tape Sync Processor Module Block Diagram                                                  |          |

| 46.         | Tape Horizontal Sync Pulse Generator                                                      |          |

| 47.         | Tape Vertical Sync Pulse Separator                                                        |          |

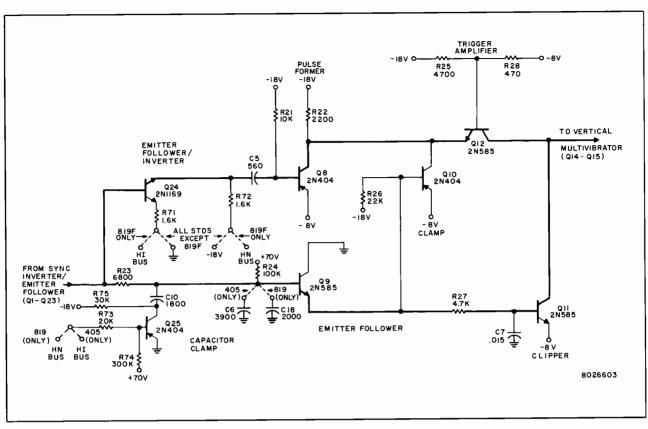

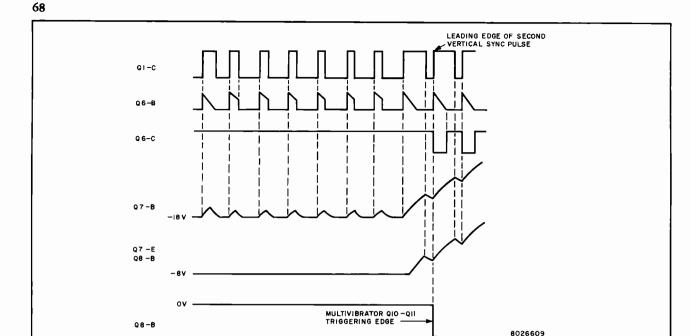

| 48.         | Waveforms Showing Development of Multivibrator Q10-Q11 Triggering Pulse                   |          |

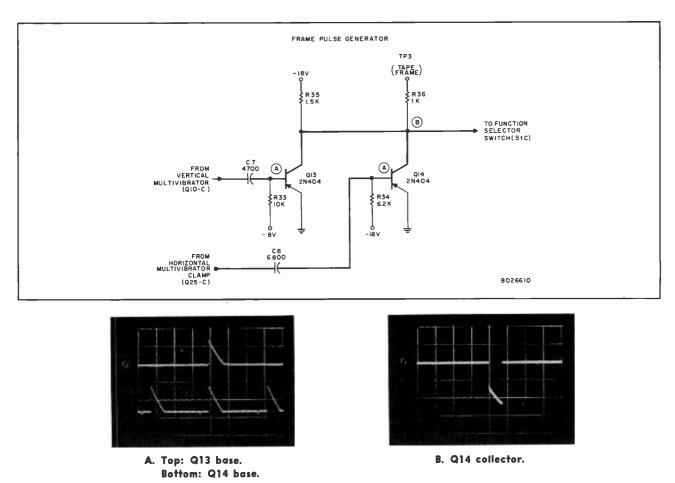

| 40.<br>49.  | Frame Pulse Generator                                                                     |          |

| т).         | rume rune Senerator                                                                       |          |

2

iv

# LIST OF ILLUSTRATIONS (Continued)

| Figure     |                                                                                              | Page     |

|------------|----------------------------------------------------------------------------------------------|----------|

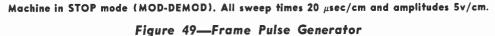

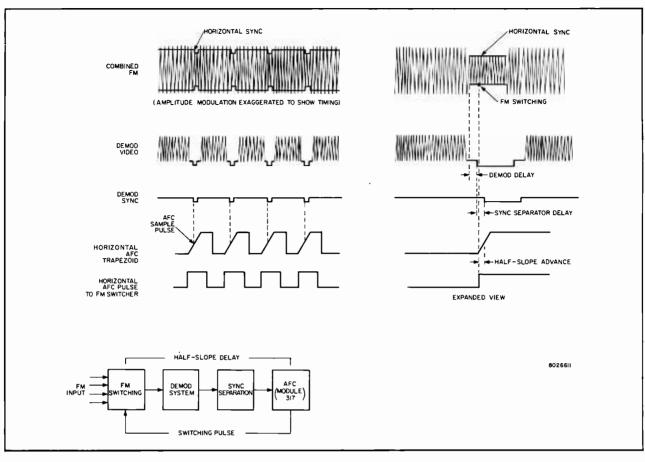

| 50.        | Development of Half-Slope Advance                                                            | 70       |

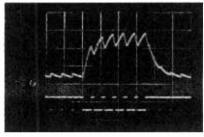

| 51.        | AFC Oscillator Circuit Waveform Relationships                                                | 71       |

| 52.        | Frequency Controlled Horizontal Oscillator                                                   | 72       |

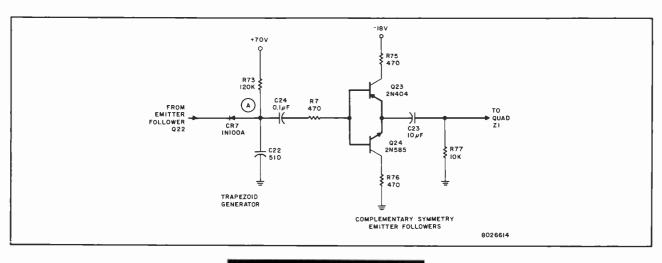

| 53.        | Trapezoid Generator                                                                          | 73       |

| 54.        | Sample Pulse Generator and Error Signal Amplifiers                                           | 74       |

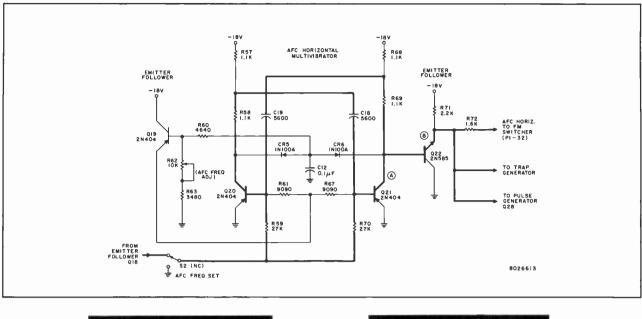

| 55.        | AFC Horizontal Pulse Generator                                                               | 76       |

| 56.        | Servo Mode Selector Switch                                                                   | 77       |

| 57.        | International Tape Sync Processor Module Block Diagram                                       | 78       |

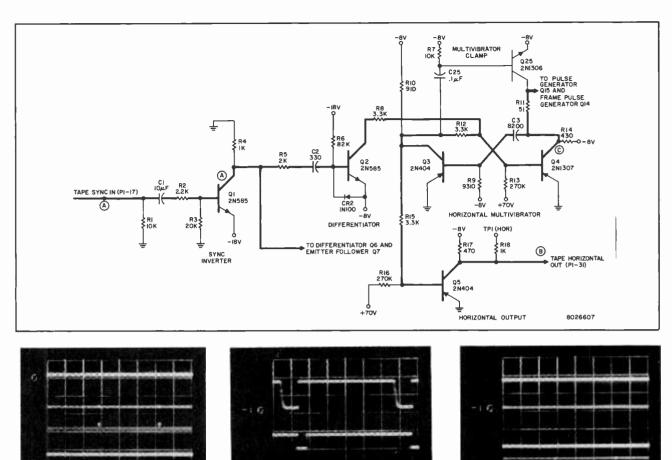

| 58.        | Horizontal Multivibrator                                                                     | 79       |

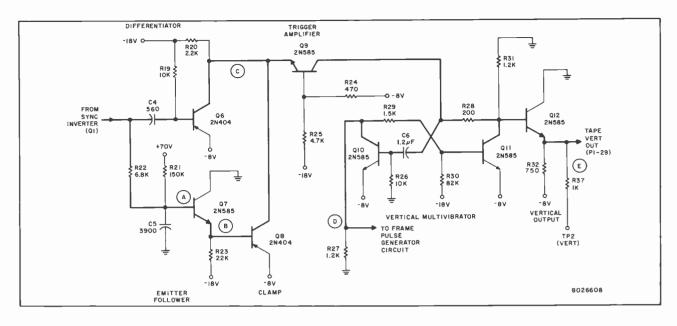

| 59.        | Tape Vertical Sync Pulse Separator                                                           | 80       |

| 60.        | Vertical Sync Separation in 819-Line French System                                           | 81       |

| 61.        | Horizontal Oscillator (405-, 525-, 625-Line Standards)                                       | 82       |

| 62.        | Horizontal Oscillator (525-, 625-, 819-Line Standards)                                       | 83       |

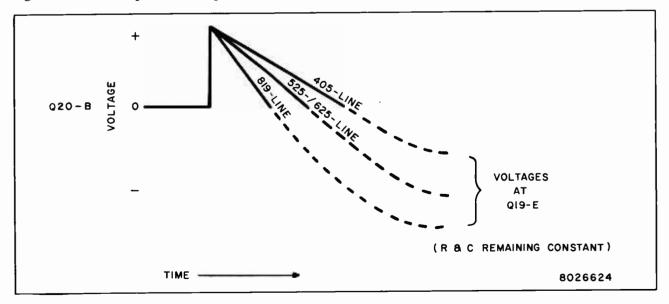

| 63.        | Waveforms at Base of Transistor Q20 Showing Relationship Between Voltage at Emitter of       |          |

|            | Transistor Q19 and Half-Cycle Period of Horizontal Multivibrator                             | 83       |

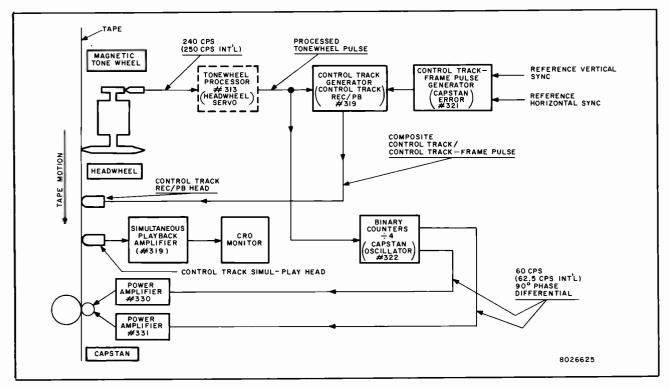

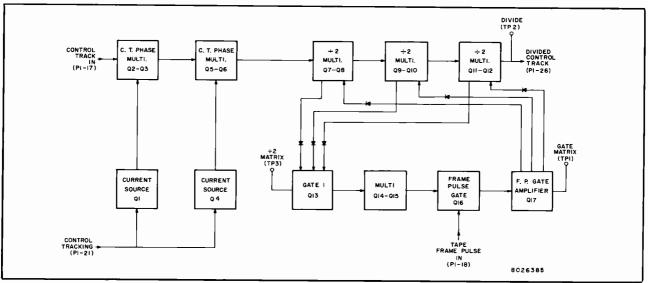

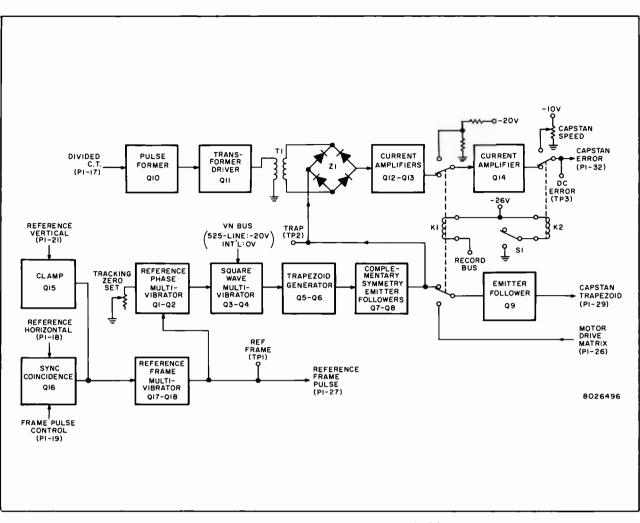

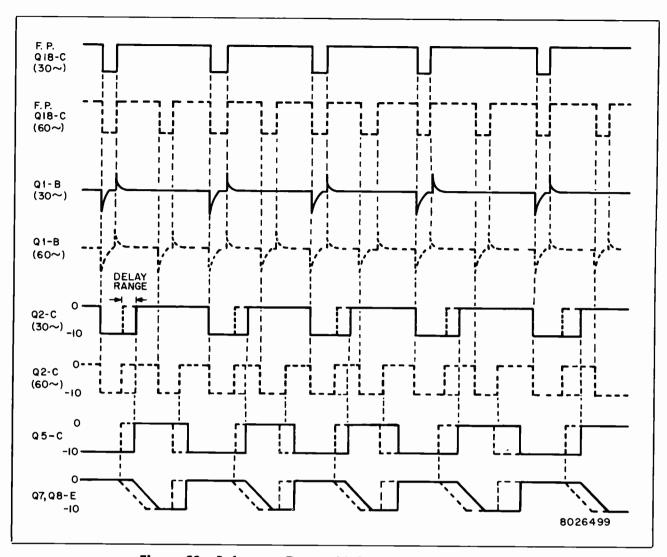

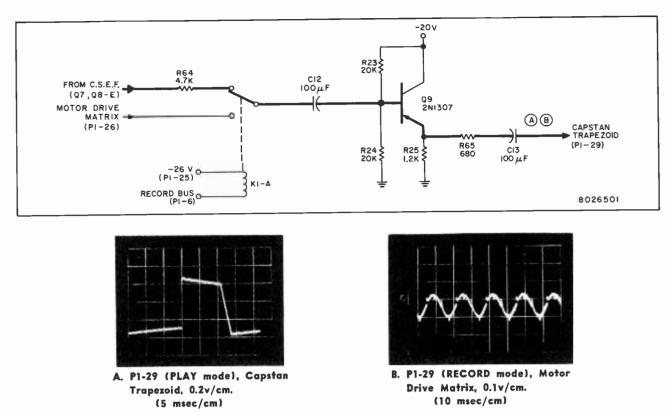

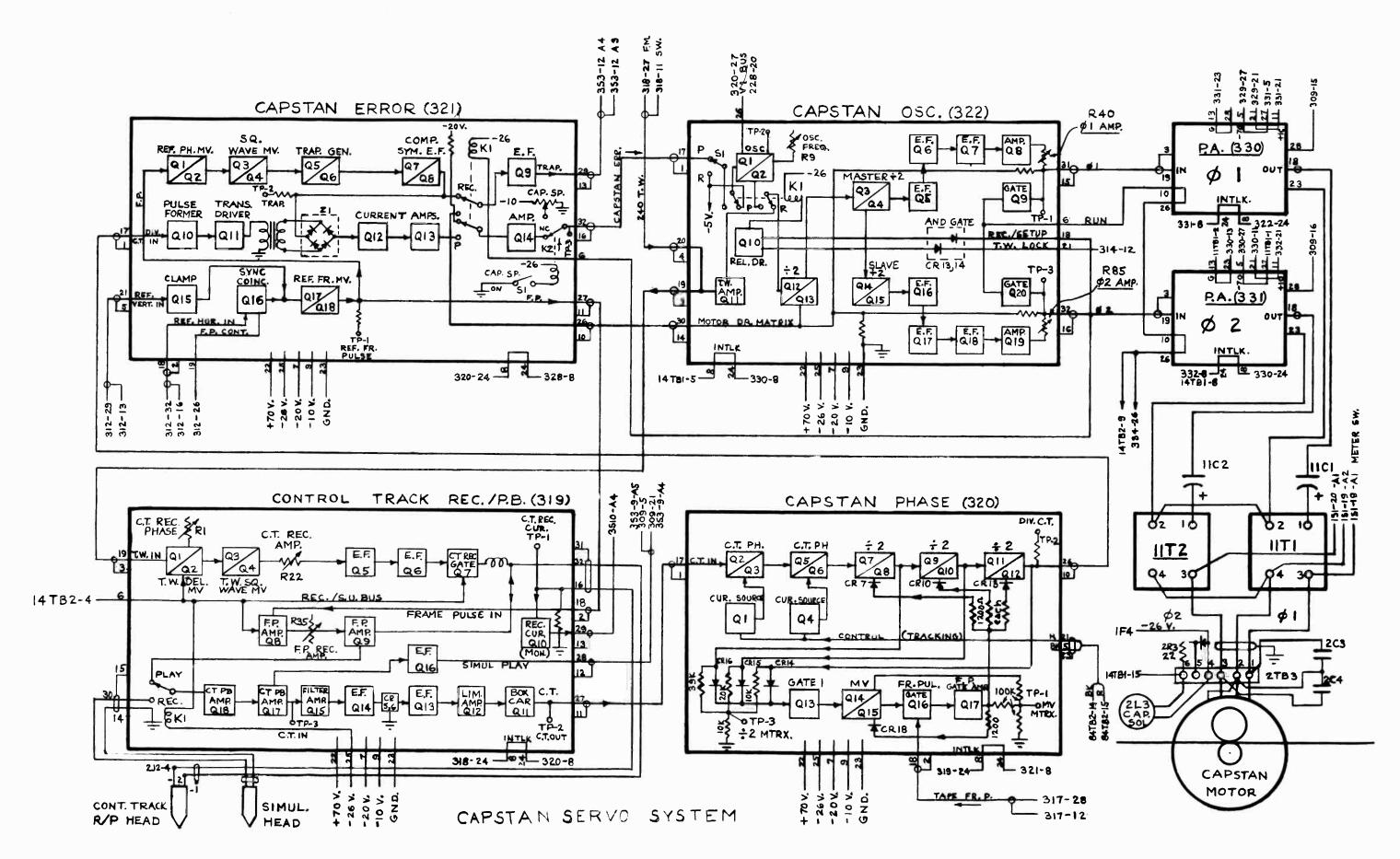

| 64.        | Capstan Servo System (RECORD Mode)                                                           | 85       |

| 65.        | Capstan Servo System (Playback in Tonewheel Mode)                                            | 86       |

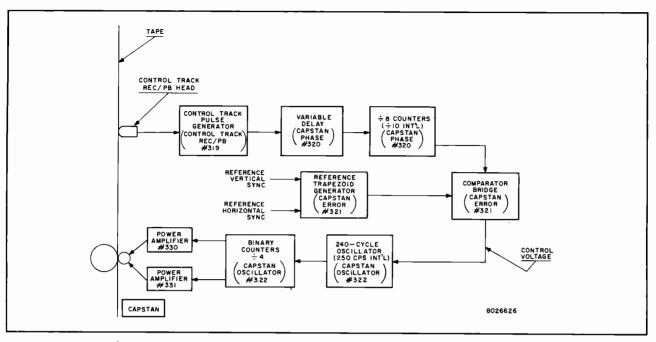

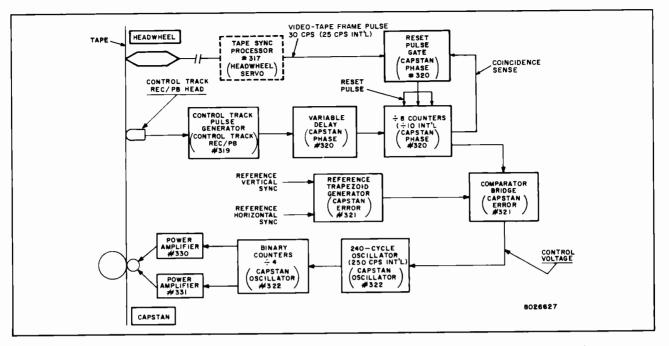

| 66.        | Capstan Servo System (Playback in Switchlock or Pixlock Mode)                                | 87       |

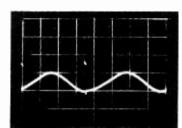

| 67.        | Correct Location of Pip on Trapezoid Slope                                                   | 88       |

| 68.        | Correct Control Track Playback Waveform                                                      | 88       |

| 69.        | Excessive Control Track Record Current                                                       | 89       |

| 70.        | Insufficient Control Track Record Current                                                    | 89       |

| 71.        | Control Track Phase Adjustment Waveform                                                      | 89       |

| 72.        | Frame Pulse Amplitude Adjustment Waveform                                                    | 89       |

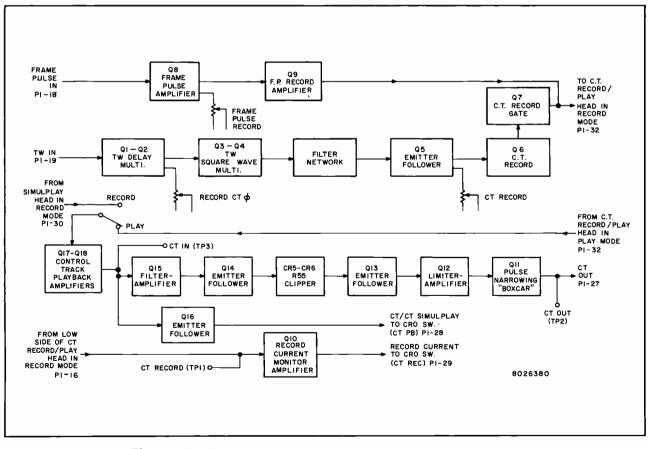

| 73.        | Control Track REC/PB Module Block Diagram                                                    | 90       |

| 74.        | Control Track Sine Wave Generator                                                            | 92       |

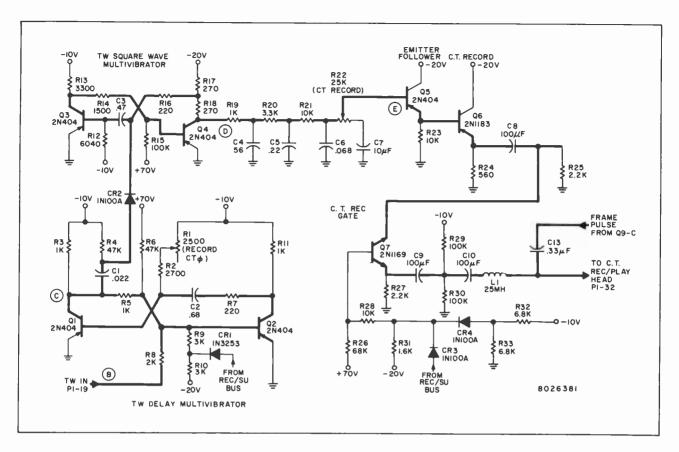

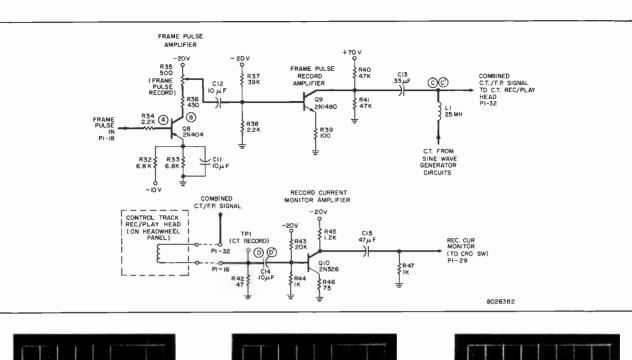

| 75.        | Frame Pulse and Record Current Amplifiers                                                    | 94       |

| 76.        | Control Track Playback Amplifiers                                                            | 95       |

| 77.        | Control Track Pulse Generator                                                                | 96<br>97 |

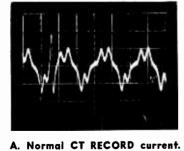

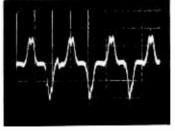

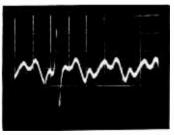

| 78.        | Waveforms Indicating Correct and Incorrect Settings of CT RECORD Adjustment                  | 98<br>98 |

| 79.        | Waveforms Indicating Correct Setting and Range of RECORD $CT_{\phi}$ Adjustment              | 90<br>98 |

| 80.        | Inductor L2 Tuned for Maximum Amplitude Signal While Maintaining Symmetry                    | 99       |

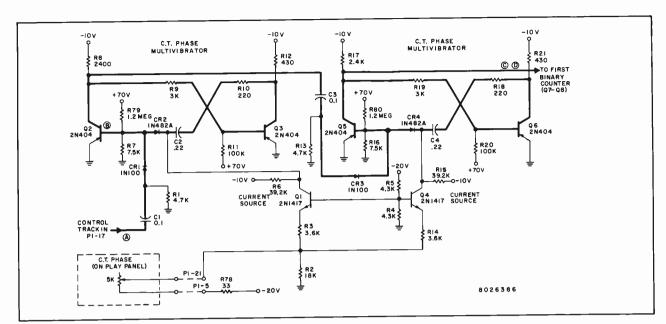

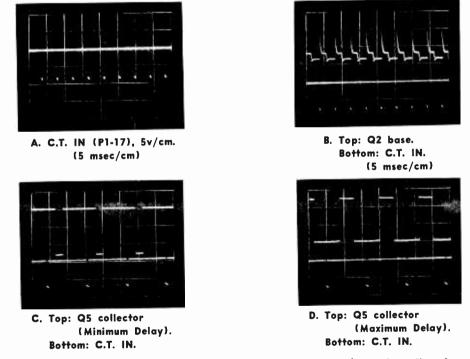

| 81.        | Capstan Phase Module Block Diagram<br>Control Track Phase Delay Multivibrators               |          |

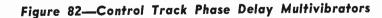

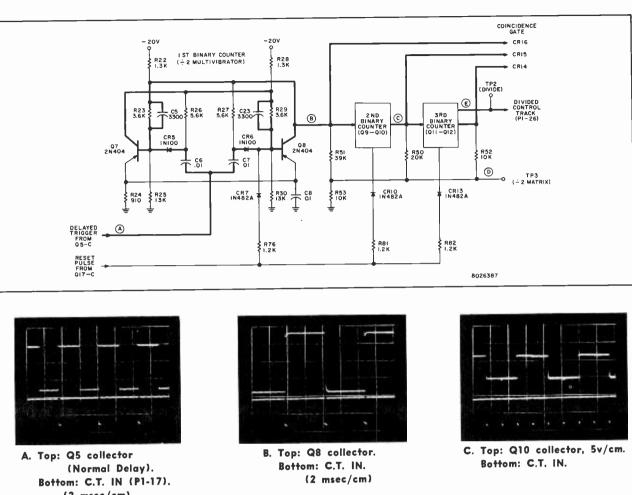

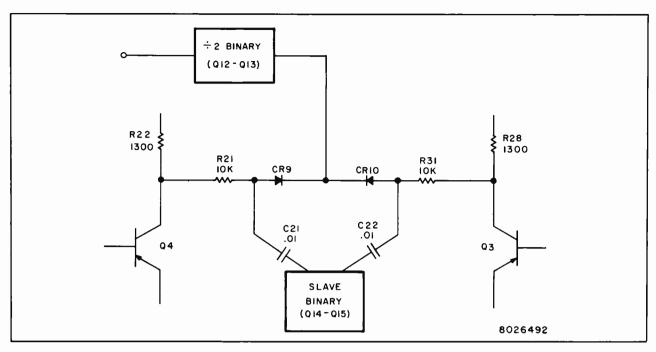

| 82.        | Binary Counters                                                                              | 102      |

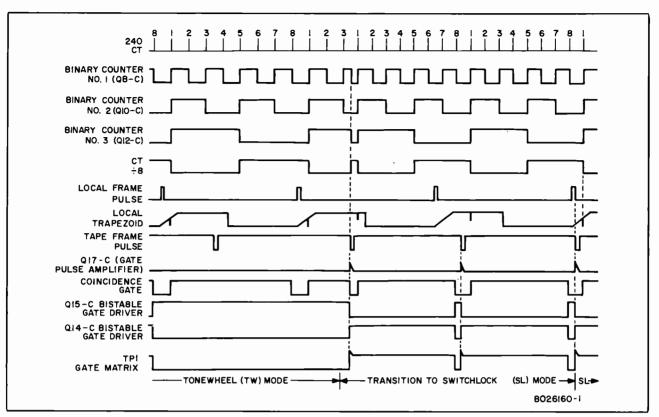

| 83.<br>84. | Timing Diagram Indicating Gating Action During Transition from Tonewheel to Switchlock Mode  | 103      |

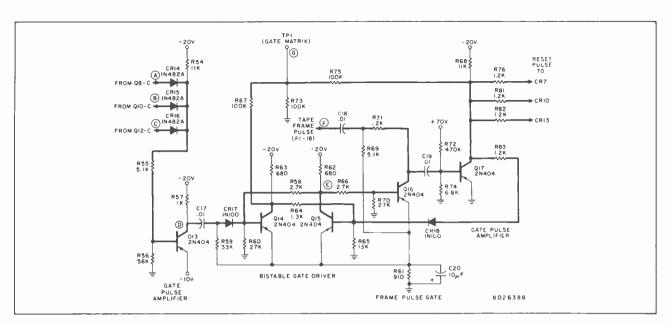

| 84.<br>85. | Reset Pulse Gating Circuits                                                                  | 104      |

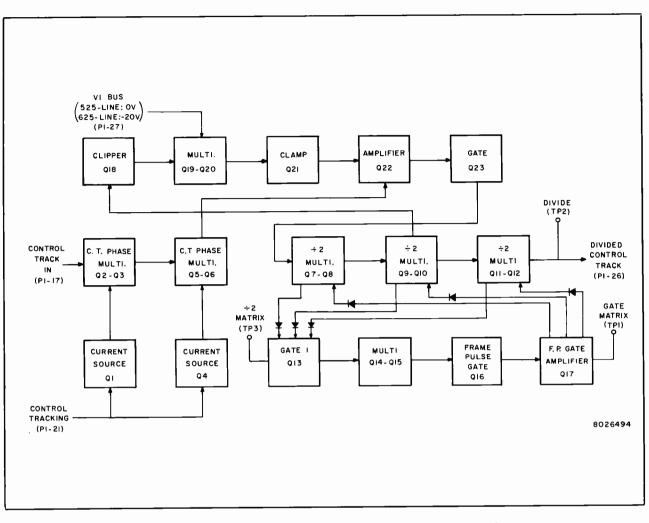

| 85.<br>86. | Capstan Phase Module (International) Block Diagram                                           | 106      |

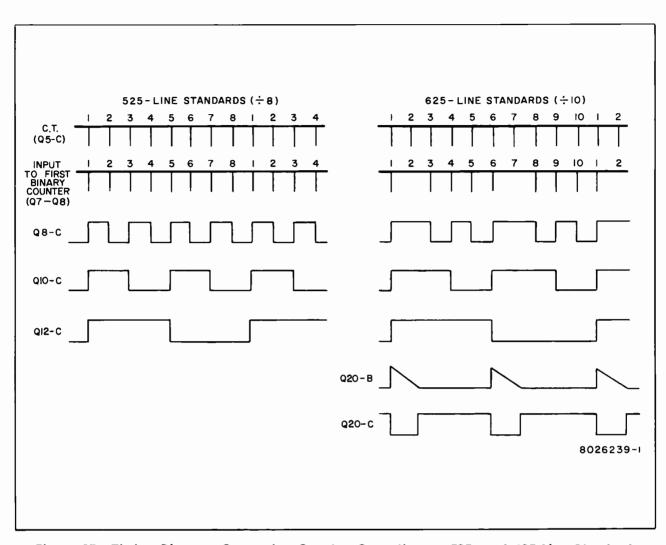

| 80.<br>87. | Timing Diagram Comparing Counter Operation on 525- and 625-Line Standards                    | 107      |

| 88.        | Fifth Pulse Eliminator                                                                       | 108      |

| 89.        | Waveforms Obtained at Capstan Phase Module (International) Test Points on 625-Line Standards | ; 109    |

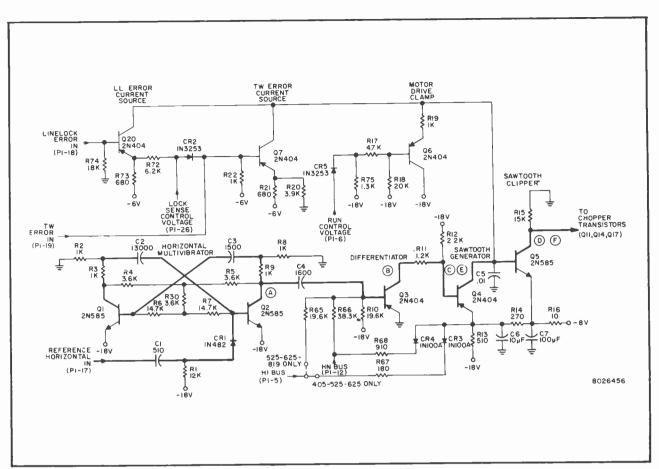

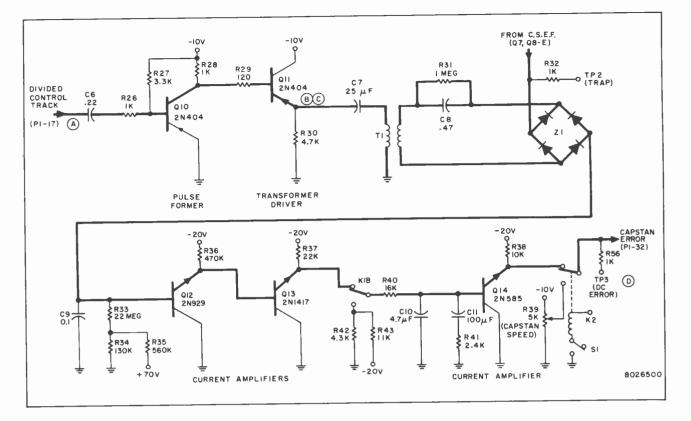

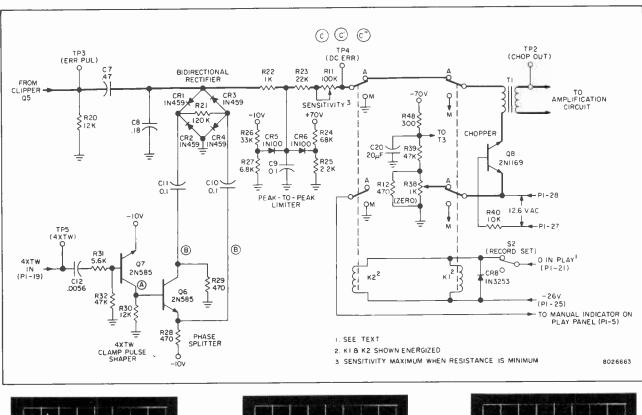

| 90.        | Capstan Error Module Block Diagram                                                           | 110      |

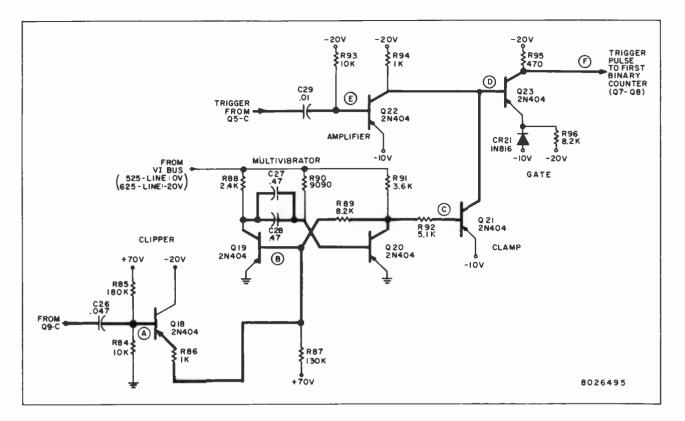

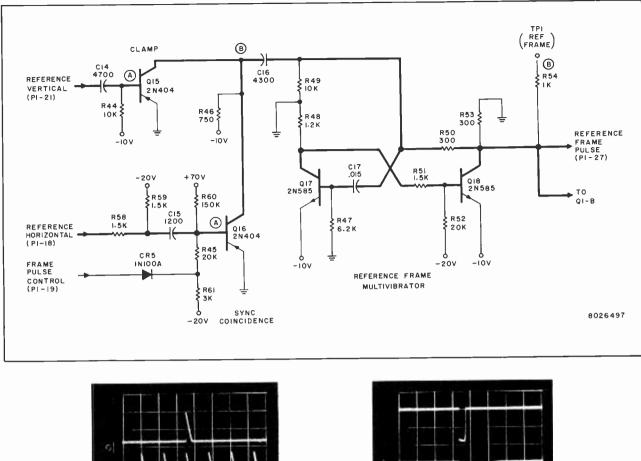

| 91.        | Reference Frame Pulse Generator                                                              | 111      |

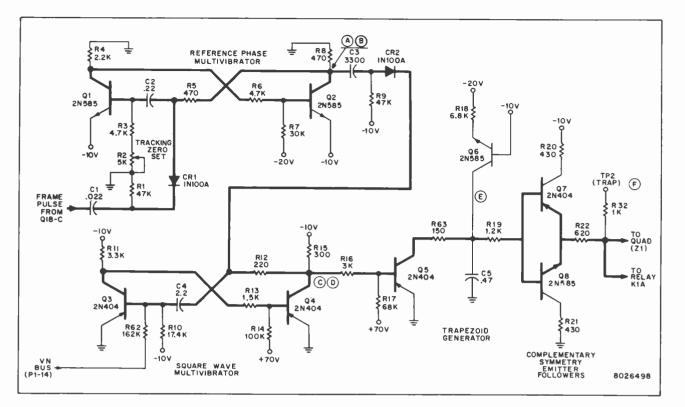

| 92.        | Reference Trapezoid Generator                                                                | 114      |

| 93.        | Reference Trapezoid Generator Timing Diagram                                                 | 115      |

| 94.        | Sample Pulse Generator and Comparator Bridge Circuit                                         | 116      |

| 94.<br>95. | CRO Driver Circuit                                                                           | 118      |

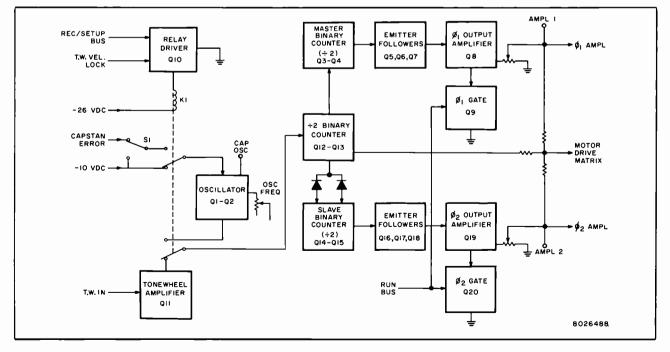

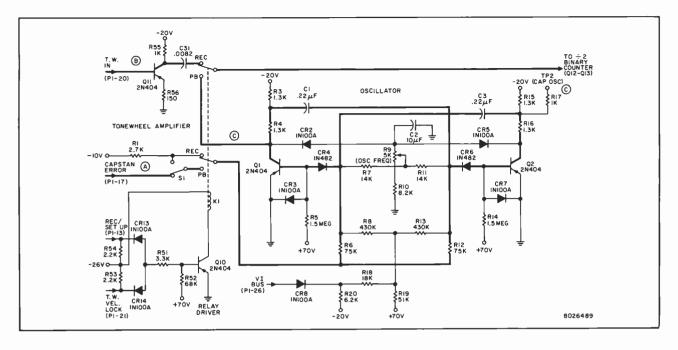

| 95.<br>96. | Capstan Oscillator Module Block Diagram                                                      |          |

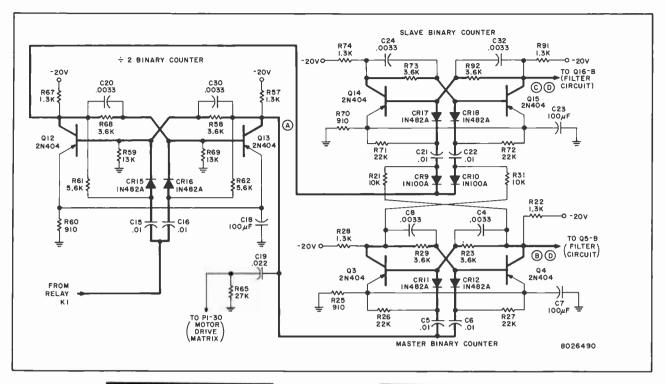

|            | 240-Cycle Capstan Oscillator                                                                 | 120      |

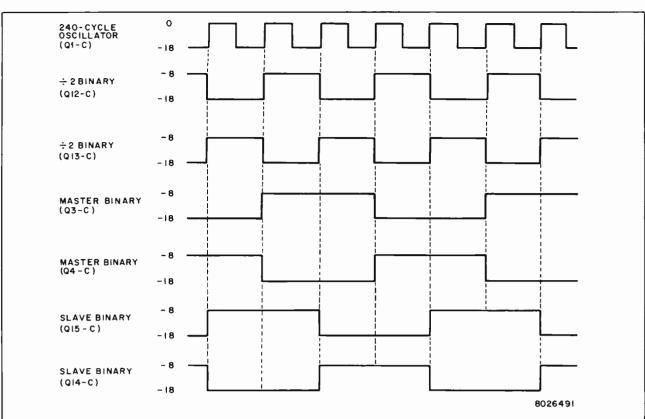

| 97.        | Binary Counters                                                                              | 123      |

| 98.        | Dinary Counters                                                                              |          |

# LIST OF ILLUSTRATIONS (Continued)

| Figure |                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------|------|

| 99.    | Binary Counter Waveform Timing Relationships                                            | 124  |

| 100.   | Phase-Locked Master/Slave Binary Counters                                               | 125  |

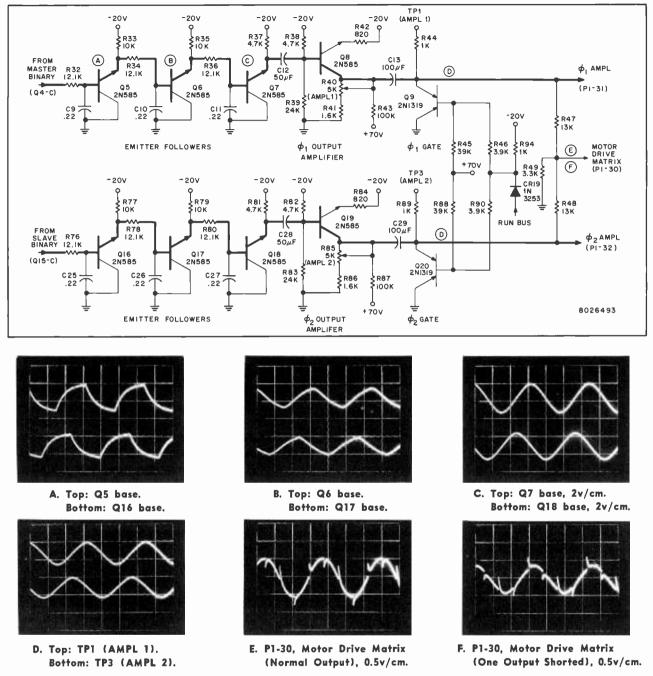

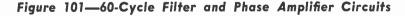

| 101.   | 60-Cycle Filter and Phase Amplifier Circuits                                            |      |

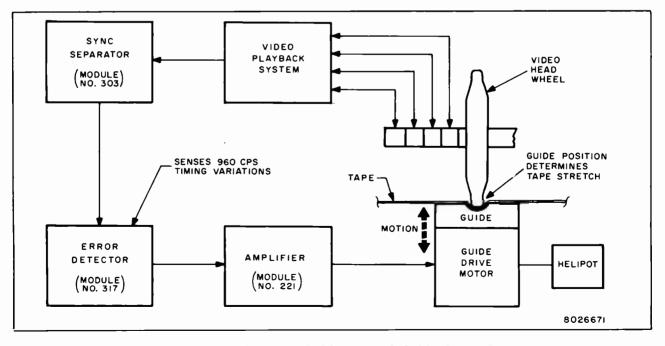

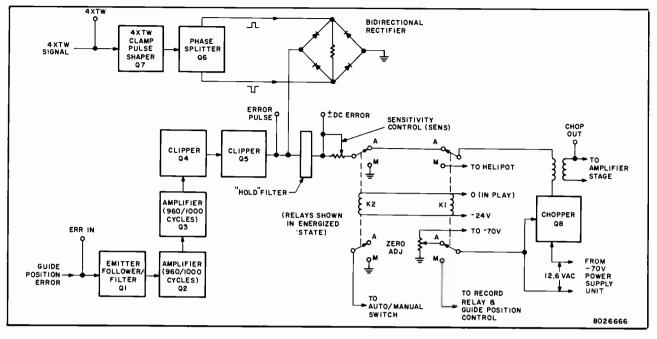

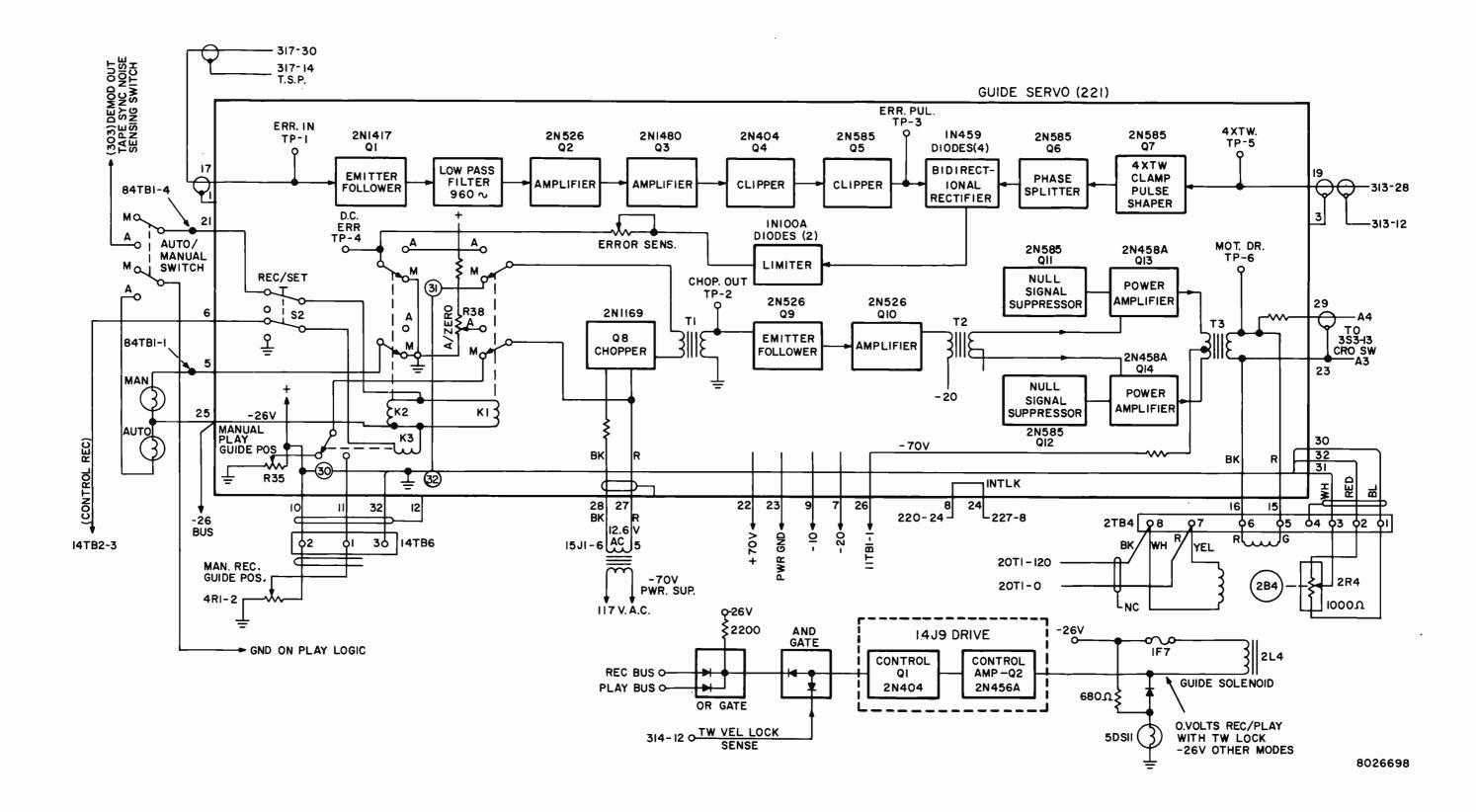

| 102.   | Simplified Block Diagram of Guide Servo System                                          |      |

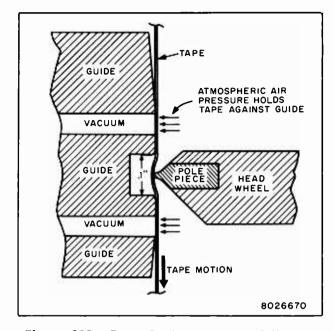

| 103.   | Cross-Sectional View of Vacuum Guide and Headwheel                                      |      |

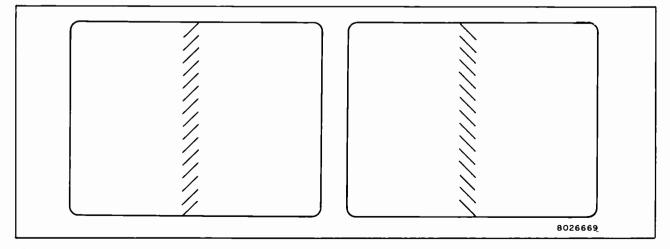

| 104.   | Sketch of TV Raster Showing Jogs Due to Insufficient Head-to-Tape Pressure (Left) and   |      |

|        | Excessive Head-to-Tape Pressure (Right)                                                 |      |

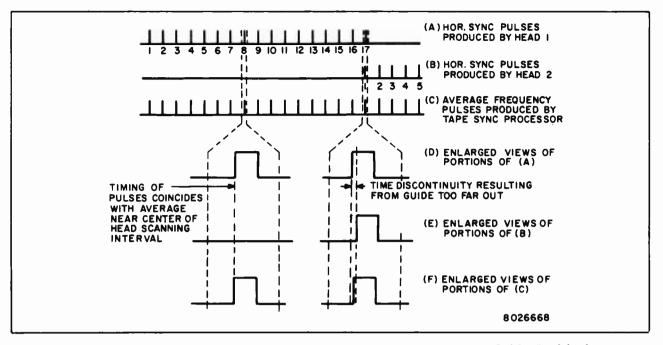

| 105.   | Waveforms Showing Timing Errors Due to Incorrect Guide Positioning During Tape Playback |      |

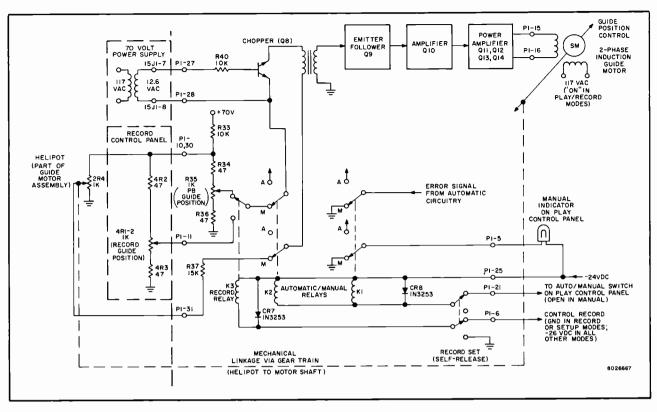

| 106.   | Guide Servo Manual Control Circuit                                                      |      |

| 107.   | Automatic Guide Positioning, Block Diagram                                              | 132  |

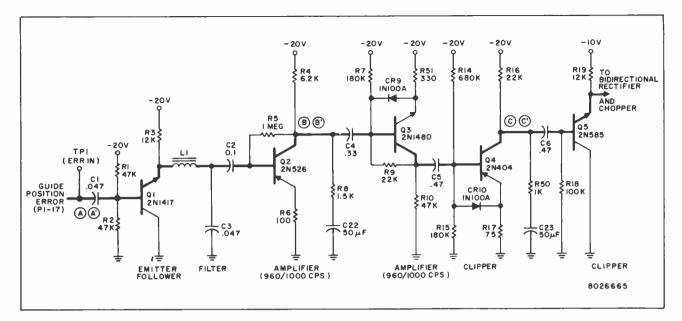

| 108.   | Error Signal Amplifier and Clipper Circuits                                             |      |

| 109.   | Bidirectional Rectifier and Chopper Circuits (Automatic Guide Control)                  |      |

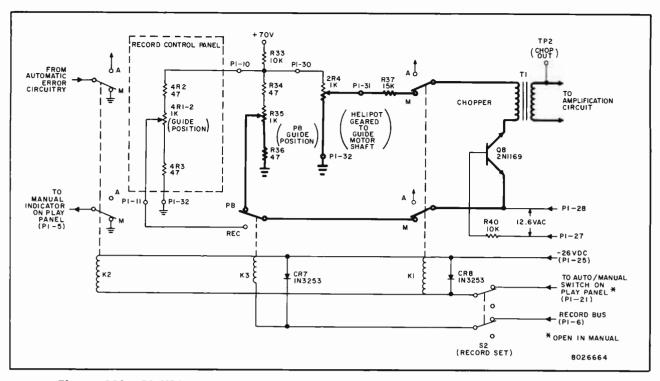

| 110.   | PLAY/RECORD Controls and Chopper Circuit (Manual Guide Control)                         |      |

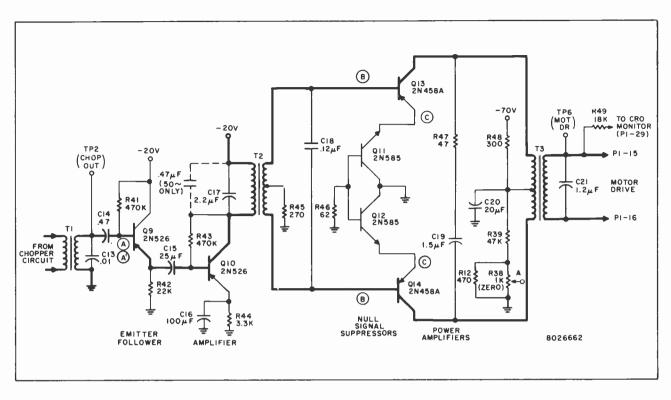

| 111.   | AC Servo Amplifier                                                                      |      |

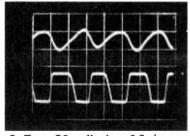

| 112.   | Waveforms Obtained at Test Point TP6 (MOT DR)                                           |      |

| 113.   | Guide Servo Mechanical Adjustment                                                       |      |

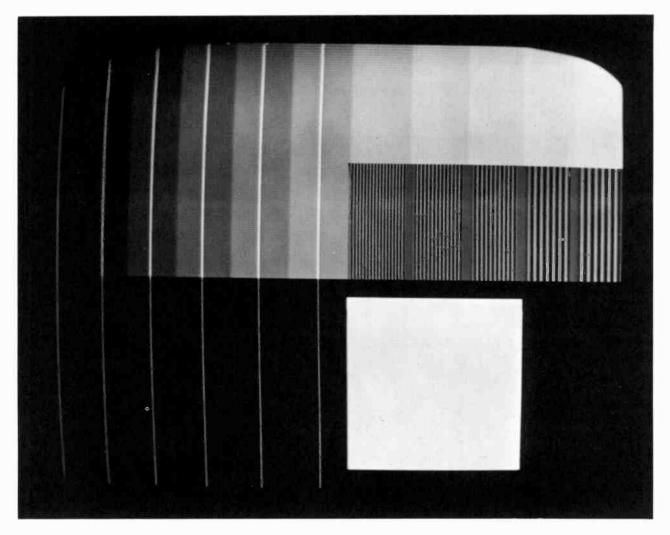

| 114.   | Jogs in Bar Pattern (Insufficient Head Penetration)                                     | 141  |

| 115.   | Jogs in Bar Pattern (Excessive Head Penetration)                                        |      |

| 116.   | Normal Appearance of Alignment Tape Playback                                            |      |

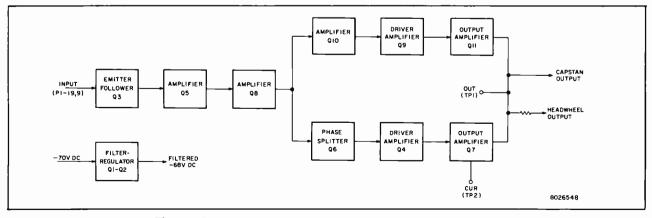

| 117.   | Power Amplifier Module Block Diagram                                                    |      |

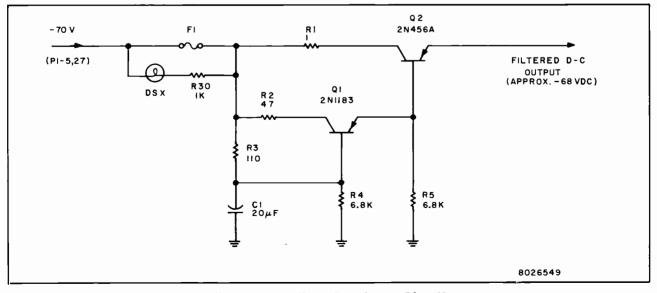

| 118.   | Filter-Regulator Circuit                                                                |      |

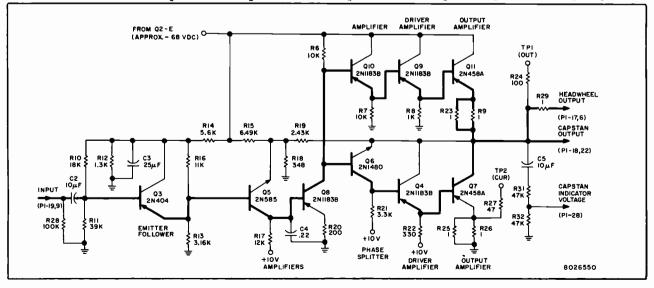

| 119.   | Amplifier Circuits                                                                      |      |

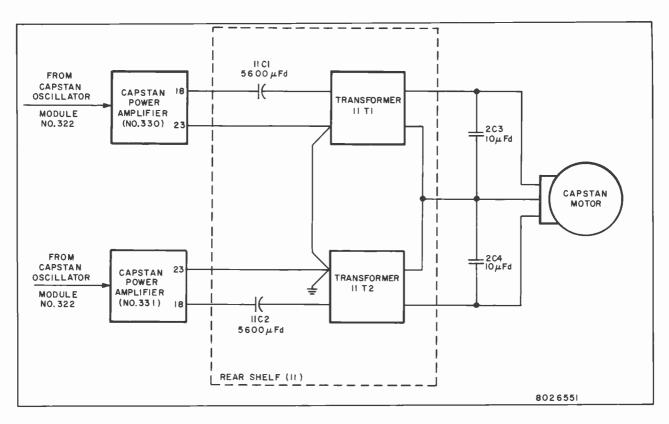

| 120.   | Capstan Power Amplifier and Motor Circuits                                              |      |

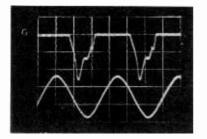

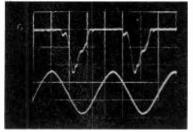

| 121.   | Capstan Power Amplifier Voltage and Current Output Waveforms                            |      |

| 122.   | Headwheel Power Amplifier and Motor Circuits                                            |      |

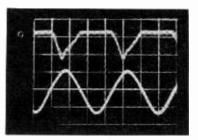

| 123.   | Headwheel Power Amplifier Voltage and Current Output Waveforms                          | 148  |

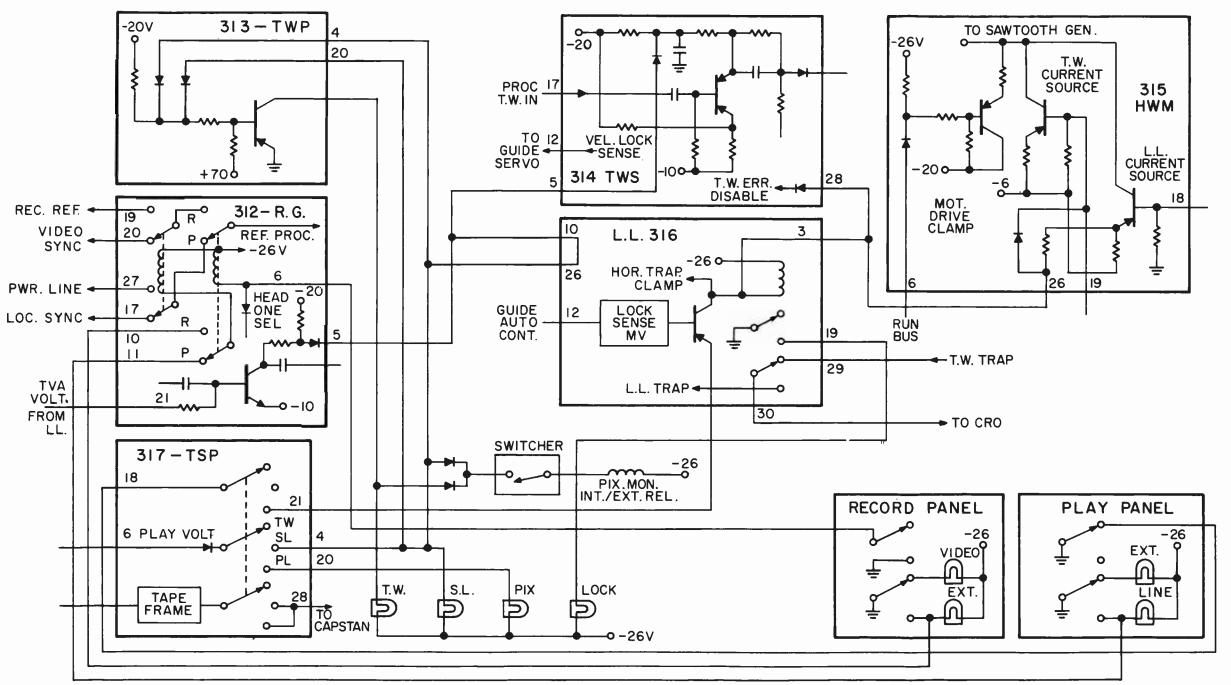

| 124.   | Headwheel Servo Controls and Indicators Diagram                                         | 151  |

| 125.   | Headwheel Servo Functional Diagram                                                      |      |

| 126.   | Capstan Servo Functional Diagram                                                        | 155  |

| 127.   | Guide Servo Functional Diagram                                                          | 157  |

vi

# HEADWHEEL SERVO

### SYSTEMS DESCRIPTION

#### GENERAL

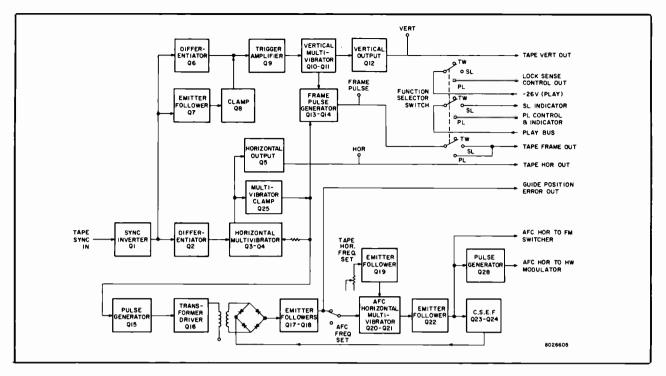

The headwheel servo system of the TR-22 Television Tape Recorder includes the following modules:

> Reference Generator (no. 312) Tonewheel Processor (no. 313) Tonewheel Servo (no. 314) Headwheel Modulator (no. 315) Linelock (no. 316) Tape Sync Processor (no. 317) Power Amplifiers (nos. 332, 333, 334)

If the machine is to be operated on International standards, the International version of the reference generator and tape sync processor modules must be incorporated into the headwheel servo system. All other modules function properly on either domestic or International standards.

The purpose of the headwheel servo system is to control the headwheel motor speed during both the tape recording and the tape playback processes. In either the RECORD or PLAY mode, the nominal speed of the headwheel motor is 240 rps; however, it is desired to exercise very tight control over this speed for reasons which are explained below.

NOTE: Throughout the following discussion of the headwheel servo system, timing references in text and illustrations pertain to 525-line, 60-cycle, domestic standards. When dealing with International (50-cycle) standards, the appropriate timing differences must be taken into consideration; e.g., the 240-cycle tonewheel pulse becomes 250-cycle, etc.

#### **RECORD** Mode

In the RECORD mode, it is desirable to attain a headwheel motor speed in revolutions per second which is exactly equal to four times the vertical scanning frequency; i.e., 240 cps. Because the timing reference for the television system may be derived from any one of several sources, the most practical method of controlling the headwheel speed is by utilizing a servo system in which an error detector compares the frequency and phase of a signal developed by the tonewheel attached to the headwheel motor shaft against a reference pulse derived from the signal itself. This action assures that each television field period occupies exactly sixteen complete transverse tracks on the tape. (Note that each revolution of the headwheel produces four tracks because of the four video magnetic heads equally spaced around the headwheel circumference.)

If the headwheel motor speed were fixed at 240 cps during recording, with no direct comparison to the vertical scanning frequency, the relative phase of the television signal as laid down on the tracks would tend to drift slowly in one direction or the other. For example, the first vertical sync pulse in each field would occur sometimes near the center of the tape, and sometimes near the edge of the tape where the head switching action occurs. In addition, the 60cycle pulse applied to the control track as a means of identifying the beginning of each field for tape splicing purposes would tend to drift in phase relative to the 240-cycle sinusoidal control track signal. While an individual machine could be made to operate effectively with such a condition of relative drift (provided no attempt is made to play back a tape that has been spliced after recording), the practical problems associated with tape splicing and the interchangeability of tapes between machines make it important that the headwheel speed be closely controlled relative to the scanning frequencies.

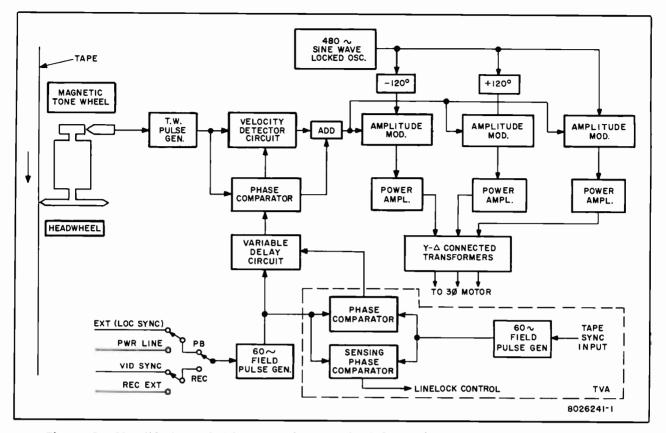

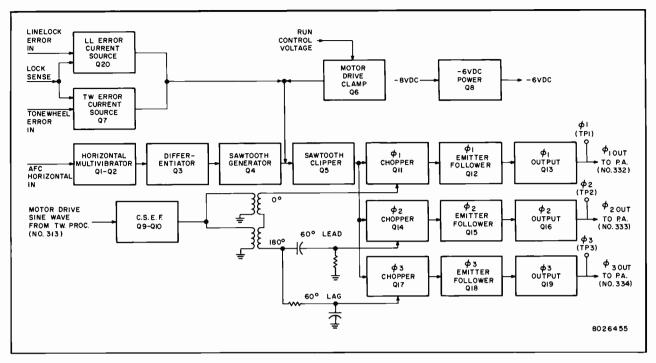

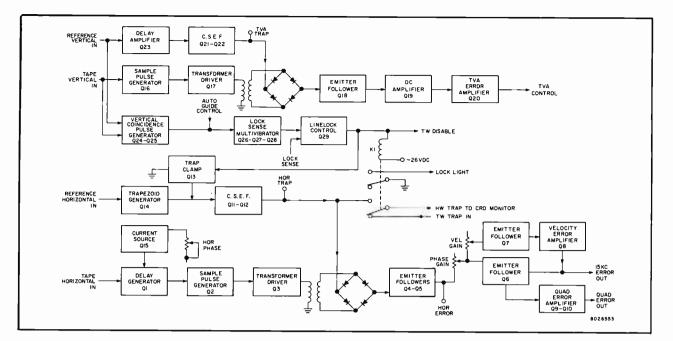

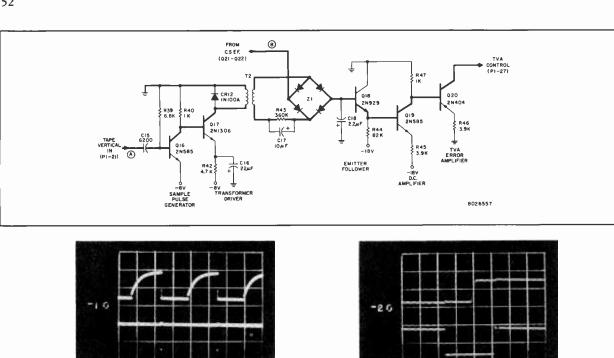

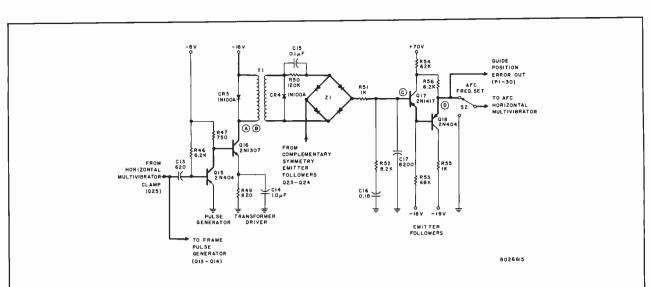

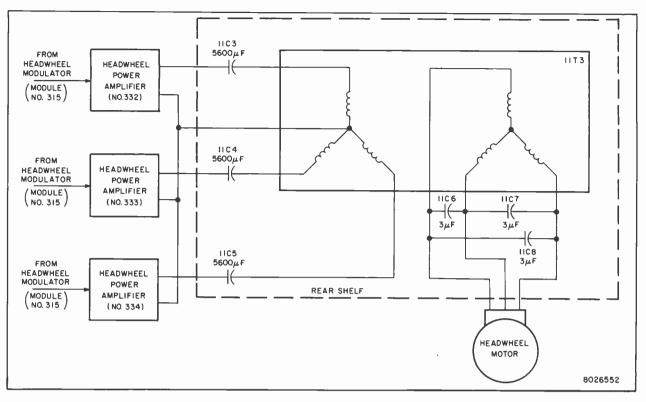

Figure 1 is a simplified block diagram of the headwheel servo system during recording. The 480-cycle motor drive sine wave, locked in phase to the tonewheel pulse, is developed from the output of an afc circuit. The sine wave is split into three individual sinusoidal signals which are separated in phase by 120 degrees, amplitude modulated, and fed to power amplifiers. The power amplifiers in turn drive the three-phase synchronous headwheel motor.

Amplitude modulation of the motor drive sine wave is controlled by: (1) a comparison of the tonewheel pulse phase with a fixed reference signal to obtain phase information, and (2) a comparison of the tonewheel pulse period with a fixed time interval to obtain velocity information. (In the RECORD mode the fixed reference signal may either be sync from the incoming video signal, or the signal from an external sync generator or oscillator.) The error signals derived from the phase and frequency comparisons are added in such a manner as to cause the velocity error signal to predominate when large errors occur (e.g. during headwheel motor start-up when the phase is changing rapidly), and the phase error signal to predominate when the motor is at approximately the correct speed with only slight variations in phase.

Figure 1—Simplified Block Diagram of Headwheel Servo in Tonewheel Mode with TVA

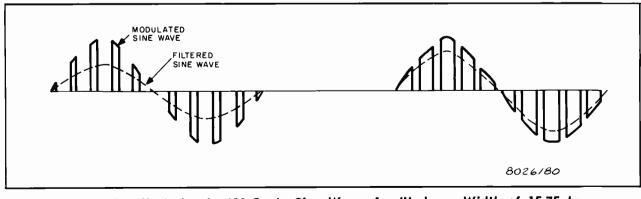

The motor drive signals are pulse modulated at a line frequency rate (15,750 cps) by chopper circuits, and the width of the modulating pulse is controlled by the combined error signal referred to above. Thus the energy contained in each sinusoidal signal will be proportional to the error signal amplitude. The line frequency information is then filtered out, thus leaving the fundamental 480-cycle sine wave signal whose amplitude is a function of the energy remaining after modulation.

NOTE: In International machines the line rate, and thus the modulating pulse frequency, depends upon the line standard in use. Headwheel servo modules in the International machines are wired for one of two line rate sequences. These are either the 405/525/625 standards or the 525/625/819 standards.

The tape vertical alignment (TVA) circuit shown within the dashed lines in figure 1 has no function during recording or during tape playback in the tonewheel servo mode. However, the TVA circuit does produce an output control voltage during these modes which converts the variable delay in the reference pulse path into a conventional emitter follower. This action eliminates the delay, which is utilized only during tape playback in the pixlock servo mode as will be explained later.

#### **PLAY Mode**

#### Tonewheel and Switchlock Servo Modes

During tape playback, provision is made to operate the TR-22 Television Tape Recorder servo system in the tonewheel, switchlock, or pixlock mode. These modes constitute increasingly greater control of tape to reference vertical and horizontal sync timing as the machine is switched from tonewheel to switchlock to pixlock mode. The function selector switch, by which the operator may select the desired mode, is located on the tape sync processor module (no. 317) front panel. The actual choice of modes selected depends upon the degree of timing control required to perform a certain operation; however, it should be noted that to successfully play back tape in the pixlock servo mode the tape must be of good broadcast quality (i.e., a tape containing clean sync signals, without dropouts or other forms of discontinuity).

Normally, satisfactory performance will be attained when tape is played back with the servo system operating in the tonewheel mode. In this mode no attempt is made to align tape and reference vertical sync, and the headwheel motor speed is controlled by the tonewheel pulse in exactly the same manner as that described above for the RECORD mode (see figure 1). The choice of servo reference during tape playback in the tonewheel mode is either a signal from an external sync generator or oscillator, or the power line frequency.

If it is desired to attain vertical framing so that vertical rollover of the picture is prevented when switching between tape and other program sources, the servo system must be operated in the switchlock mode. In this case the headwheel servo remains in the tonewheel mode, while the capstan servo operates in the switchlock mode to control the tape speed and vertical sync phasing to achieve vertical framing. Operation of the machine in the switchlock servo mode is explained in greater detail below during the pixlock servo discussion. (Refer also to the *Capstan Servo System* description.)

#### Pixlock Servo System

The function of the pixlock servo system is to accurately synchronize vertical and horizontal sync pulses derived from television tape signals with vertical and horizontal sync pulses provided by the station's local sync generator. This allows an extension to tape television signals of the lap dissolve, special effects, and other types of transition currently employed between two or more live or film television signals.

The pixlock servo system is actually a combination of the switchlock and linelock servo systems. Briefly, the switchlock system operates independently of the linelock system, and its function is to control the capstan servo so that the speed of the tape and phase of the tape vertical sync is such that vertical rollover of the picture is prevented when switching between tape and other program sources. The linelock system, however, operates in conjunction with the switchlock system in providing accurate control of the headwheel motor speed to maintain a precise relationship between tape and local horizontal sync pulses, thus insuring that the tape system is completely locked both vertically and horizontally.

The operation of the pixlock system in lining up vertical and horizontal sync from television tape signals with the local station sync pulses may be divided into four distinct phases which automatically occur in sequence. Phases one and two are performed by the switchlock servo while phases three and four are performed by the linelock servo. In the pixlock system, the time required to complete all four phases is less than five seconds from the moment the PLAY pushbutton is pressed for tape playback in the pixlock mode. The pixlock functions are completely automatic so that if there are any discontinuities in the tape signal or reference signal while playing back tape, the machine will go through only the necessary opera-

tions to re-synchronize, taking a total time of three

seconds or less.

The first phase of operation begins when the machine is signalled to start in the PLAY mode. Capstan and headwheel motor power are immediately switched on and the motors are accelerated to their correct operating speeds so that a stable picture signal is played back from the tape. Once a picture signal is received, the machine begins the second phase of operation, designated "coarse vertical framing." In this operation the machine shifts video tracks until it plays back the recorded track containing vertical sync at the same time as the local vertical sync is occurring. This operation does not provide exact vertical framing however, because it does not compensate for errors of placement of vertical sync in the recorded pattern on the tape. To compensate for these errors the machine enters the third phase of operation, designated tape vertical alignment (TVA). Here the tape and local vertical sync signals are accurately compared and the necessary slight adjustment of the headwheel phase is introduced, resulting in "fine vertical framing."

At this point the picture signal from the tape will be timed to within a few microseconds of its correct position, and will be moving several microseconds left and right of this position. The motion results because the information fed to the servo occurs at too slow a rate (60 samples per second) to allow for complete correction. The fixed error is present because the loop gain cannot be made large enough, at a low sampling rate, to reduce the error further.

When the machine senses that the TVA cycle has been completed, it switches into the final or "linelock" phase of operation. In the linelock mode, the headwheel servo is controlled by comparison of horizontal sync from the tape signal with the local horizontal sync. Error information is thus provided at a suf4

ficiently high rate that the servo gain is readily increased to overcome much more rapidly varying errors.

The following discussion presents a more detailed explanation of the four phases of pixlock operation in terms of the servos themselves. The first phase (headwheel and capstan motor acceleration) is accomplished with the headwheel servo operating from the tonewheel and the capstan servo operating from the control track. This is primarily the same operation as the tonewheel mode, however the TVA circuit is actually in the headwheel servo loop although it does not furnish any additional information in the first phase of the pixlock sequence.

In the TVA tonewheel mode, the magnetic tonewheel head delivers one pulse for each rotation of the headwheel. After passing through shaping circuits, the 240-cycle pulse obtained from the tonewheel is fed to a velocity detector circuit and to a phase comparator as shown in figure 1. The velocity detector circuit produces a d-c voltage which is a function of the period between pulses, and this error voltage feeds the modulator which modulates a three-phase 480-cycle sinusoidal signal. The output of the modulator feeds three power amplifiers, and  $Y - \Delta$  connected transformers drive the three-phase induction headwheel motor.

When the headwheel motor is started from rest, the velocity error voltage fed to the modulator causes full power to be delivered to the motor so that it will accelerate as fast as possible. As the headwheel motor speed approaches 240 rps, the error voltage is reduced and less power is delivered to the motor by the modulator, thereby resulting in rapid headwheel speed stabilization. At this point the phase error voltage, obtained from the phase comparator circuitry, assumes control of the headwheel motor speed. This voltage is a function of the phase relationship between the tonewheel pulse and a 60-cycle pulse derived from local vertical sync. The servo loop controls the headwheel motor so that these pulses are locked together.

In this servo, the motor drive voltage responds very rapidly to error voltages because phase shifting is accomplished before modulation and very little filtering or wave shaping is required in the channels which follow the modulator. Also, the 480-cycle motor drive frequency is derived from an oscillator which locks at exactly twice the tonewheel frequency, thereby eliminating any beats which would be caused by a free-running motor drive frequency. These features greatly increase the accuracy of the tonewheel servo, thereby minimizing recorded servo error or jitter.

When the capstan and headwheel motors have come up to speed and have locked-in in their normal modes, a video signal becomes available from the tape being played back and the machine enters the second phase of operation (coarse vertical phasing). This phase of operation takes place wholly within the capstan servo while the headwheel servo continues to operate from the TVA tonewheel. The action here consists of the capstan servo looking at the frame information played back from the tape, and "slipping tracks" until this frame information matches frame information derived from the local sync signals. A 30-cycle frame pulse is formed from the tape sync signal input by a circuit similar to that used in deriving a frame pulse from local sync. The tape frame pulse thus formed is then injected into the capstan servo system as a reset pulse to accomplish framing.

The third phase of system operation consists of compensating for errors which exist between the local and tape vertical sync signals because of placement errors of the recorded vertical sync in its track. This compensation is provided by the TVA function of the system.

Basically, the TVA circuit directly compares vertical sync, or field pulses, derived from the tape and from the local signals. The comparator output (a d-c voltage) controls a variable delay circuit which has been added in the 60-cycle reference input path of the headwheel servo (figure 1). The delay circuit adjusts the apparent phase of the 60-cycle reference, thereby controlling the rotational phase of the headwheel. By this means the TVA variable delay circuit can make small adjustments of headwheel phase to shift the phase of the tape playback signal. The TVA loop has a very high gain, so that the resultant error when it stabilizes will be small; however, the loop is deliberately designed to be slow-acting so that it does not interfere with the normal start-up and lock-in of the headwheel servo. TVA comes into action only after the main servo has locked-in and the capstan phasing cycle has been completed, because prior to this there is either no signal from the tape or the framing is so

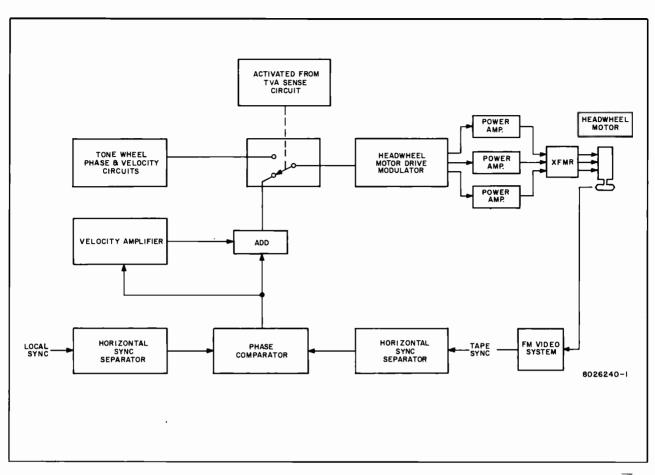

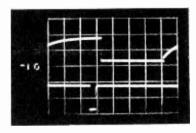

Figure 2—Simplified Block Diagram of Headwheel Servo in Linelock Mode

far off that the TVA phase comparator is outside of its useful range.

A coincidence circuit is used as a sensing device which indicates when the TVA circuits have stabilized at their correct phase. This circuit provides an output signal only when the local and tape vertical sync signals are within a few microseconds of each other. The presence of the sensing signal causes the pixlock servo to automatically switch to the fourth (linelock) phase of operation.

Figure 2 is the block diagram of the pixlock servo in the linelock mode. The input to the headwheel motor drive modulator is electronically switched by the TVA sense circuit from the tonewheel phase and velocity circuits to the linelock circuits. These circuits include a phase comparator which compares tape and local horizontal sync signals. The d-c error signal thus derived is fed to the headwheel motor drive modulator by two paths. The first path is direct; the second path passes the signal through a velocity amplifier circuit whose purpose is to provide a stabilizing function in the loop, thus allowing higher loop gain without overshoot or oscillation.

Control of the headwheel motor speed by the linelock loop is limited only by the power capabilities of the motor drive system. The gain and response speed are sufficiently high that the maximum phase error between local and tape sync signals is less than  $\pm 0.1$ microsecond when playing back a tape which was recorded with a pixlock servo system.

It should be recognized that the performance of the pixlock system is a function of both the recording and the playback equipments. Therefore, the jitter of the recording is very important, and for best stability tapes should be recorded by a low jitter recording servo system such as is provided by the pixlock system itself. Recordings made with other servo systems may contain excessive jitter which is not of great importance during conventional playback, but which may be very detrimental when trying to achieve precise control of the headwheel motor by the pixlock servo operating in the pixlock mode.

5

#### HEADWHEEL SERVO SETUP PROCEDURE

The setup procedure outlined below is intended as a guide in making rapid checks and minor adjustments which insure optimum headwheel servo performance. All waveforms specified may be monitored directly on the machine, and therefore no external test equipment is necessary. Detailed procedures for making each adjustment in the headwheel servo system according to the various modules are presented in the *Adjustment* section of the individual module descriptions, and should be referred to when setting up the servo initially and when module or component replacement necessitate complete re-adjustment.

#### **Head Select Operation**

1. Depress the VID IN and DEMOD OUT pushbuttons on the CRO monitor switcher simultaneously, and also depress the EXT SYNC pushbutton.

2. Depress the V and EXP pushbuttons located along the right-hand edge of the CRO monitor.

3. Play back a tape in the switchlock servo mode and switch from head no. 1 to head no. 4 (utilizing the HEAD SELECT switch on the reference generator module, no. 312) while noting the tape vertical sync displacement on the CRO monitor at each position of the switch.

4. With switch position no. 1 as a reference, the displacement of tape vertical sync should not exceed three-fourths of a horizontal line in any of the remaining switch positions. If the maximum displacement is exceeded, re-adjust potentiometer R54 to obtain a minimum displacement.

#### **Velocity Time Constant**

1. Play back a tape, using the EXT SERVO reference, and operate the picture monitor on external sync.

2. Press the VEL TC button on the tonewheel servo module (no. 314), and observe the picture on the monitor.

3. If horizontal roll-through occurs, re-adjust the VEL TC potentiometer on the tonewheel servo module to minimize the roll-through. (Adjust the potentiometer in the clockwise direction to stop the picture from rolling to the left, and adjust the potentiometer in the counterclockwise direction to stop the picture from rolling to the right.)

#### **4XTW DELAY**

1. Play back a tape and observe the picture monitor to detect the presence of 960-cycle streaks which may enter the picture from either the left or the right side. 2. If streaks are present, adjust the 4XTW DELAY potentiometer on the tonewheel processor module (no. 313) so that the potentiometer is centered in the range over which no streaks appear.

#### **FM** Switching

1. Play back a tape in the tonewheel servo mode, using EXT servo reference.

2. Operate the picture monitor on EXT sync.

3. Utilizing the HEAD SELECT switch on the reference generator module front panel, select the head which allows the horizontal blanking and sync pulse to be observed.

4. Operate the guide servo manually and, utilizing the PB GUIDE POSITIONING control on the guide servo module (no. 221), decrease tip penetration slightly to emphasize switching dots. (Adjust picture monitor brightness and contrast to obtain best results.)

5. Correct switching is indicated when the switching dots are located within the horizontal sync interval, and approximately one-third in from the leading edge of sync. If necessary, adjust the TAPE HOR FREQ SET potentiometer on the tape sync processor module (no. 317) to properly position the switching dots.

#### **Tonewheel Servo Gains**

The VEL GAIN and PHASE GAIN potentiometers on the tonewheel servo module (no. 314) generally require re-adjustment only when the headwheel panel is replaced.

#### **Linelock Servo Gains**

Because the linelock servo utilizes the tape signal in obtaining some of its information, the VEL GAIN and PHASE GAIN potentiometers on the linelock module (no. 316) may require re-adjustment when certain tapes are played back. If re-adjustment is required, it will be necessary to follow the procedure outlined in the linelock module description.

It should be noted that optimum results during tape playback will be obtained from tapes which have a minimum of recorded jitter. Therefore, for maximum stability during tape playback tapes should be recorded by a low-jitter recording servo system such as that provided by the pixlock system itself. Recordings made with other servo systems may contain excessive jitter which is not of great importance during conventional (tonewheel) playback, but which may be detrimental when attempting to achieve precise control of the headwheel motor speed by operating the machine in the pixlock servo mode.

### MODULE CIRCUIT ANALYSES

In the following analyses of the individual modules which are contained in the headwheel servo system, timing references pertain to domestic standards; i.e., a 15,750 cps horizontal rate (525-line) and a 60-cycle field rate. A special reference generator and tape sync processor module (nos. 312 and 317) will be utilized in the International machines to accommodate International line standards and a 50-cycle field rate. The description of each of these modules is presented separately, following the domestic module description. The remaining headwheel servo modules contain circuitry which allows them to operate efficiently in either domestic or International machines.

Partial schematic diagrams are intended to show only the area under discussion. For a complete schematic diagram refer to the TR-22 TV Tape Recorder Diagram Manual, IB-31616. A functional diagram of the headwheel servo system (figure 125) and a diagram of controls and indicators (figure 124) will be found at the rear of this instruction book. These diagrams are provided as aids in obtaining an overall conception of the function of the circuits which make up the modular portion of the headwheel servo system.

### **REFERENCE GENERATOR MODULE (DOMESTIC)** Circuit Description

#### General

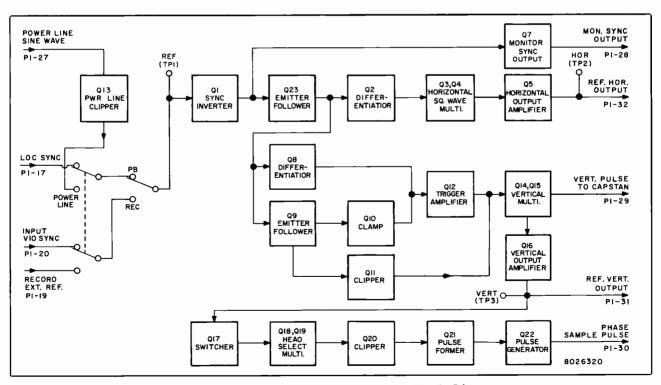

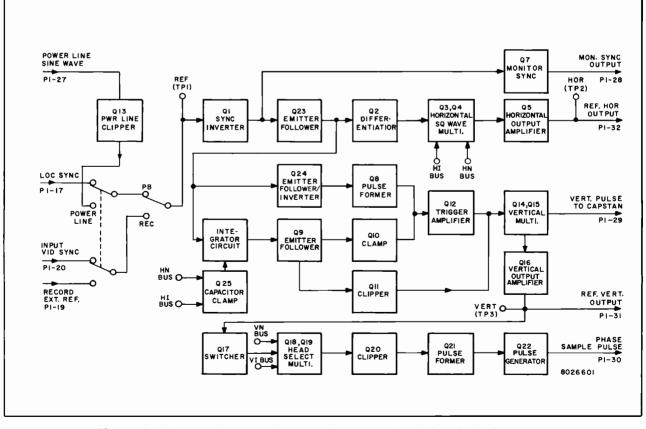

The function of the reference generator module (no. 312) is to produce five individual output signals for use in the headwheel servo, capstan servo, and monitoring subsystems, from any one of four input reference signals. (See block diagram, figure 3.) The output signals and their destinations are as follows:

1. Reference horizontal sync to the CRO and picture monitors for synchronizing the monitors.

2. Vertical sync to the capstan servo subsystem where it is used in developing the reference frame pulse.

3. Phase sample pulse (derived from reference vertical sync) to the headwheel servo subsystem for phase control of the headwheel motor in tonewheel or switchlock modes during playback, or tonewheel mode when recording.

4. Reference vertical sync to the headwheel servo subsystem for tape vertical alignment (TVA) control in the pixlock mode of operation during playback; and to the reference pulse switch position (REF PULSE) of the CRO monitor switcher for monitoring purposes.

Figure 3—Reference Generator Module Block Diagram

5. Reference horizontal sync to the headwheel servo subsystem for speed and phase control of the headwheel motor on a line-for-line basis in the pixlock mode during playback; and to the capstan servo subsystem where it is used in developing the reference frame pulse.

The input signals to the reference generator are determined by the operating mode of the machine (RECORD or PLAY), and two choices of reference are available for each mode. The input signals to the reference generator are:

1. Local sync or power line reference, which may be selected for system reference during playback by means of a pushbutton on the PLAY control panel.

2. Video sync or record external reference sync, which may be selected for system reference when recording by means of a pushbutton on the RECORD control panel.

#### Reference Horizontal and Monitor Sync Pulse Generator

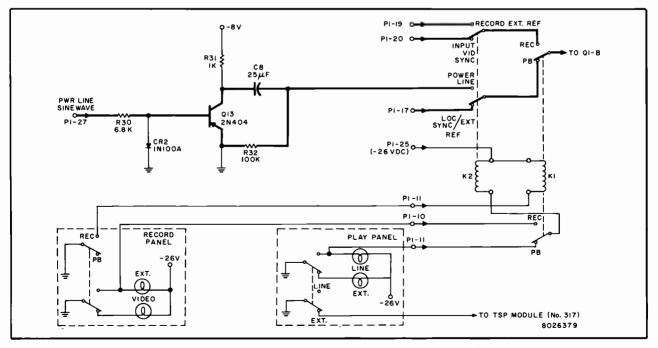

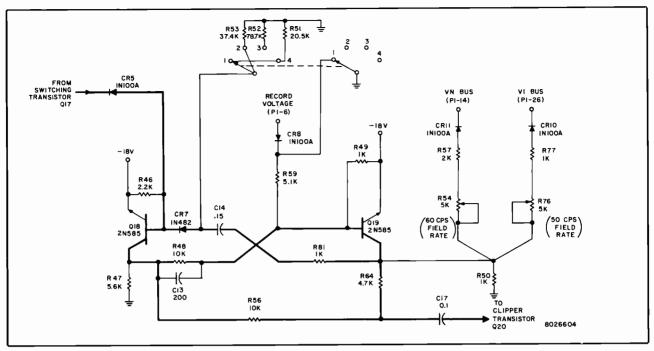

Relay K1 (REC/PB) is deenergized when the tape recorder is operated in the PLAY mode (figure 4). The input reference signal is then selected by relay K2 (REF SELECT RLY), and the choices available are local sync (when K2 is deenergized) and power line (when K2 is energized). The condition of relay K2 during playback is controlled by the SERVO REF pushbutton on the PLAY control panel. Similarly, two input reference signals are available when the tape recorder is operated in the RECORD mode. In this mode relay K1 is energized, and the input signals available are video sync (when K2 is deenergized) and record external reference sync (when K2 is energized). The condition of relay K2 when recording is controlled by the SERVO REF pushbutton on the RECORD control panel.

Power line clipper transistor Q13 is used to generate a square wave from the power line sine wave fed to its base through pin 27 of plug P1. However, the square wave output from Q13 is fed to sync inverter transistor Q1 only when the SERVO REF pushbutton on the PLAY control panel is depressed for LINE reference input. When power line reference is used, the outputs of all the sync pulse generator circuits, including that of the horizontal multivibrator, will be 60-cycle pulses which are generated from the power line input.

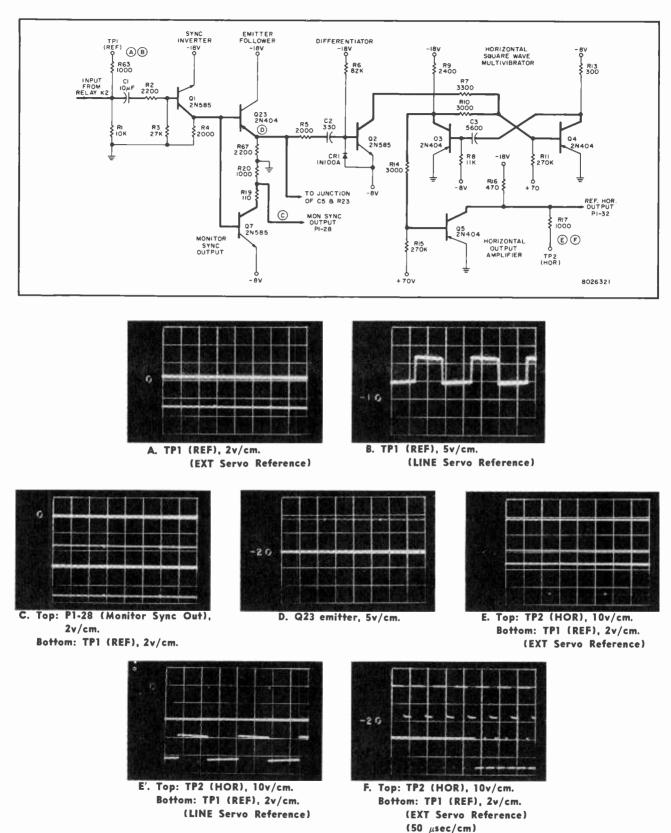

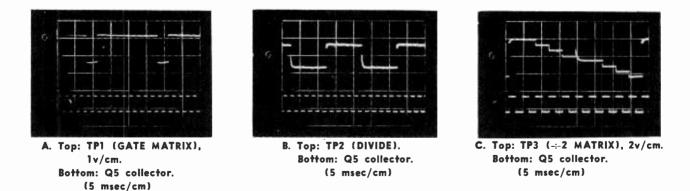

As shown in the block diagram (figure 3), the selected reference signal is fed to the base of transistor Q1, and may be observed at test point TP1 (REF). (See figures 5A and B.) Transistor Q1 is a sync inverter amplifier which is biased so that it is normally conducting, and its collector is therefore normally clamped at -18 volts. When a negative-going signal appears at the base of Q1, the transistor is cut off and its collector potential begins to rise toward ground. The maximum value that this potential can reach, in the positive direction, is determined by monitor sync output transistor Q7, whose base is driven directly by the signal at the collector of Q1. Transistor Q7 is

Figure 4—Power Line Clipper and Relay Circuits

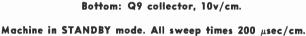

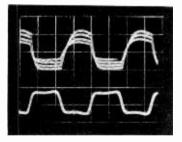

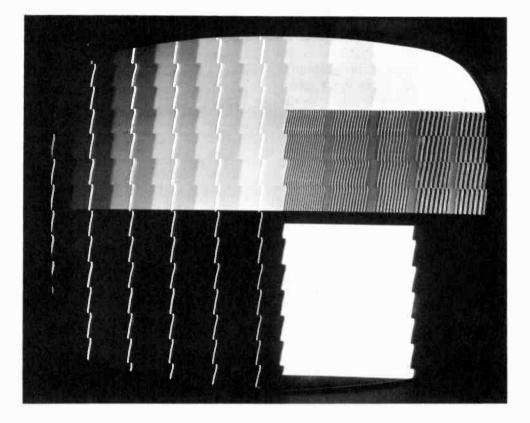

Machine in STOP or STANDBY mode. All sweep times 5 msec/cm, unless otherwise noted.

Figure 5—Reference Horizontal and Monitor Sync Pulse Generator

9

initially biased at cut-off, and its collector is at ground potential when the collector of transistor Q1 is at -18 volts. Then, as the collector voltage of Q1 attempts to go more positive than the potential at the emitter of Q7, Q7 conducts and its collector is clamped at -8 volts. When transistor Q7 conducts, its base also clamps the collector of transistor Q1 at -8 volts. Therefore, for each negative-going pulse input appearing at the base of transistor Q1, a positive-going pulse (from -18 volts to -8 volts) appears at the collector of Q1 and a negative-going pulse (from ground to -8 volts) appears at the collector of Q7. The negative-going pulse at the collector of transistor Q7 is divided-down by the resistor combination of R19 and R20, and is fed from pin 28 of plug P1 to the CRO and picture monitors where it is terminated in 75 ohms and used as a source of external sync (figure 5C).

The positive-going pulse at the collector of transistor Q1 is also fed directly to the base of emitter follower transistor Q23, whose emitter voltage follows the voltage at the collector of Q1 (figure 5D). Transistor Q23 provides the current gain and low impedance necessary to drive transistors Q2, Q8, and Q9 in parallel. Capacitor C2 and resistor R6 form a network which differentiates the signal obtained from the emitter of transistor Q23. Differentiator amplifier Q2, normally biased at cut-off, is driven into conduction by the positive-going leading edge of the incoming sync signal applied to its base. The signal at the collector of transistor Q2 is fed to the base of transistor Q4, which combines with transistor Q3 to form the monostable horizontal square wave multivibrator.

In the multivibrator stable state, transistor Q3 is biased into conduction by the current withdrawn from its base through resistor R8 returned to -8 volts, and transistor Q4 is biased at cut-off by the combined effect of the fixed positive voltage applied to its base through resistor R11 and the ground potential at the collector of transistor Q3 when Q3 is conducting. When transistor Q2 is driven into conduction, its collector voltage drops from ground potential to -8volts. This voltage develops a current, limited by resistor R7, which is fed to the base of transistor Q4 thus driving the transistor into conduction. While transistor Q4 is cut off, however, the potential at its collector is -8 volts and the base of transistor Q3 is at ground potential; therefore, capacitor C3 is charged to -8 volts. At the instant transistor Q4 begins to conduct, its collector voltage rises very rapidly to ground potential and the full charge across capacitor C3 is applied to the base of transistor Q3, thus cutting Q3 off.

This action begins the one-shot period of the multivibrator, and the duration of the period is determined by the discharge rate of capacitor C3 through resistor R8 toward -8 volts. The period exceeds that of half a TV line so that the multivibrator divides by two during the double rate pulses in the 9H interval of vertical blanking. Thus, the horizontal square wave multivibrator removes all vertical components and produces reference horizontal at a horizontal rate from the input reference sync signal.

Horizontal output amplifier transistor Q5 doubles the amplitude of the multivibrator output signal and isolates the multivibrator from the output load. The reference horizontal output signal is fed from pin 32 of plug P1 to the linelock module (no. 316) and may be observed at test point TP2 (HOR). (See figures 5E and F.)

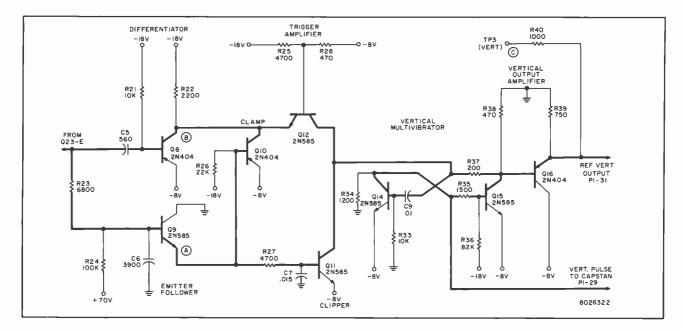

#### Vertical Sync Pulse Separator and Pulse Generator

As mentioned previously, emitter follower transistor Q23 provides the current gain and low impedance necessary to drive transistors Q8 and Q9 in parallel. In the vertical sync pulse separator circuitry, the signal at the emitter of transistor Q23 is fed to the junction of capacitor C5 and resistor R23, from which it continues in two parallel paths. One of the paths is through capacitor C5 to the base of differentiator transistor Q8. The second path is through resistor R23 to the base of emitter follower transistor Q9.

Transistor Q8 functions in a manner similar to the familiar pulse narrowing boxcar circuit. The transistor is biased into conduction by the current withdrawn from its base through resistor R21 returned to -18 volts, and its collector voltage is then driven to -8 volts. When a positive-going pulse from the emitter of transistor Q23 is applied to the base of Q8 through capacitor C5, Q8 will be cut off for an interval which is proportional to the time constant determined by capacitor C5 and resistor R21.

During the interval that transistor Q8 is cut off, its collector voltage attempts to fall to -18 volts. However, it is prevented from doing so because it is clamped at -8 volts by transistor Q10, which is normally saturated by the current withdrawn from its base through resistor R26 returned to -18 volts. Therefore, no signal can appear at the collector of transistor Q8 until the clamping action of transistor Q10 is removed.

Returning to the second path mentioned above, the signal from the emitter of transistor Q23 is integrated by the network consisting of resistor R23 and capacitor C6, and is then applied to the base of emitter follower transistor Q9. The time constant of the integrator nétwork is such that the output charges to approximately 80% of its maximum amplitude within a period equal to that of one half of a TV line. Thus

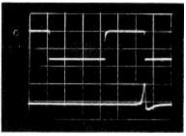

A. Top: Q9 emitter. Bottom: Q9 base. (50 µsec/cm)

C. Top: TP3 (VERT). Bottom: TP1 (REF), 2v/cm. (EXT Servo Reference) (100 μsec/cm)

B. Top: Q8 collector, 1v/cm.

Bottom: Q9 emitter.

(50 μsec/cm)

C'. Top: TP3 (VERT). Bottom: TP1 (REF). (LINE Servo Reference) (5 msec/cm)

Machine in STOP or STANDBY mode. All amplitudes 5v/cm, unless otherwise noted.

Figure 6—Vertical Sync Separator and Pulse Generator

the amplitude of the integrator network output is low when horizontal sync appears, and high when vertical sync appears.

Transistor Q9 is biased at cut-off by the voltage applied to its base through resistor R24 in conjunction with the output from transistor Q23 fed through resistor R23. When the positive-going output from the integrator network exceeds the negative cut-off bias voltage of transistor Q9, it causes Q9 to conduct. The integrated signal then appears at the emitter of Q9 as shown in figure 6A. In figure 6A, the waveform at the emitter of transistor Q9 has been superimposed

upon the waveform at its base so that the relationship between the cut-off bias voltage and the signal at the emitter may be seen. Note that the level of the cut-off bias voltage is sufficient to prevent any of the horizontal sync pulses from triggering Q9, while the greater amplitude pulse derived from vertical sync exceeds the bias voltage level and causes Q9 to conduct.

When transistor Q9 conducts, due to the integrated vertical sync signal at its base, it cuts off transistor Q10. This removes the clamping action on the collector of transistor Q8, allowing the signal from Q8 to pass to the emitter of trigger amplifier transistor Q12. The signal from transistor Q8 appears only during vertical sync, and the first pulse is the boxcar pulse derived from the leading edge of the second vertical sync pulse, as shown in figure 6B. Transistor Q12 operates as a common base amplifier, and its purpose is to amplify the signal from the collector of transistor Q8 without inverting it. When the negative-going pulse appears at the collector of transistor Q8, transistor Q12 is saturated and its collector clamps the potential at the junction of capacitor C9 and resistor R37 in the vertical multivibrator circuit at -9 volts. This places the full charge of capacitor C9 on the base of transistor Q14, thereby cutting Q14 off and beginning the multivibrator action. Thus the vertical multivibrator is triggered in effect by the leading edge of the second vertical sync pulse, as shown in figure 6C.

The signal at the emitter of transistor Q9 is also fed to the base of clipper transistor Q11, after being integrated by the network consisting of resistor R27 and capacitor C7. Normally, the potential at the base of Q11 is -9 volts (figure 7G) thus cutting the transistor off, and the collector of Q11 is then at ground potential since it follows the potential at the collector of transistor Q12 (figure 7F). When the integrated signal is applied to the base of transistor Q11, the base potential increases in a positive-going direction until it reaches the level which will allow Q11 to conduct, as shown in figure 7, F and G. If the machine is operating with a normal local sync input (vertical serrations present), transistor Q12 is triggered into conduction by the leading edge of the second vertical sync pulse, as explained in the paragraph above, and thus the collector of transistor Q11 is actually at -9volts before Q11 begins to conduct. With normal sync input then, transistor Q11 has no effect in triggering multivibrator Q14-Q15 since the multivibrator has already been triggered by the leading edge of the pulse from transistor Q12. However, if the machine is operated with a non-standard local sync input, such as that used in industrial TV, serrations may not occur during the vertical sync interval, or may occur late.

In this case, transistor Q11 generates the pulse which is used in triggering multivibrator Q14-Q15 (figure 7, H through L). (The time constant of the integrator network consisting of resistor R27 and capacitor C7 is such that transistor Q11 is forced to conduct slightly after transistor Q12 would normally conduct if the vertical serrations were present; thus transistor Q11 is prevented from producing a false triggering pulse.)

The base of transistor Q14 is connected to ground through resistor R33, and its potential is therefore positive with respect to the emitter potential; thus transistor Q14 is conducting in the multivibrator stable state. Simultaneously, transistor Q15 is cut off by the combined effect of the fixed negative bias voltage applied to its base through resistor R36 and the -8 volts at the collector of transistor Q14. The collectors of transistors Q11, Q12, and Q15 are at ground potential, and the base of transistor Q14 is at -8volts, until a triggering pulse appears at the collectors of Q11 and Q12. Thus capacitor C9 charges to the base voltage of transistor Q14 during the interval between triggering pulses. When a triggering pulse occurs, the junction of capacitor C9 and resistor R37 is clamped at -8 volts and the full negative charge on C9 is applied to the base of transistor Q14, thus cutting the transistor off. Current is then supplied to the base of transistor Q15 through resistors R34 and R35 returned to ground, thereby driving Q15 into saturation. This action begins the one-shot period of the multivibrator, and the duration of the period is dependent upon the time constant determined by resistor R33 and capacitor C9.

The signal at the collector of transistor Q14 is a positive pulse, having an amplitude of approximately 8 volts and a period of 680 microseconds. This pulse is fed from pin 29 of plug P1 to the capstan error detector module (no. 321) in the capstan servo subsystem, where it is used in generating the reference frame pulse.

The signal at the collector of transistor Q15 is a negative pulse, also having an amplitude of approximately 8 volts and a period of 680 microseconds. This pulse is fed to vertical output amplifier transistor Q16, which operates as an emitter follower. Transistor Q16 provides the current gain necessary to drive the output signal, and also isolates the multivibrator from the output circuit. The output signal at the emitter of transistor Q16 is fed from pin 31 of plug P1 to the linelock module (no. 316) in the headwheel servo subsystem for reference purposes when the recorder is operated in the pixlock mode with TVA control. Test point TP3 (VERT) is provided for convenience in observing the output signal (figure 6C).

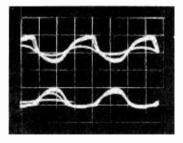

Figure 7—Waveforms Showing Development of Multivibrator Q14-Q15 Triggering Pulse

#### Head-Select Multivibrator and Phase Sample Pulse Generator

The vertical pulse at the emitter of transistor Q16 is fed through capacitor C11 to the base of switching transistor Q17. Transistor Q17 is a bidirectional junction transistor which functions as an emitter follower when the electrode connected to resistor R44 is negative with respect to the electrode connected to -8volts, and forms part of a boxcar circuit when the relative electrode polarities are reversed.

In every mode of tape recorder operation except the pixlock mode with TVA control, a control voltage of -26 volts (selected by the switch on the tape sync processor module, no. 317, in TW and SL position) is applied to the anode of diode CR6 from pin 5 of plug P1. This voltage reverse-biases CR6, thus cutting

the diode off. The total resistance of resistors R41 and R44 is then in the emitter circuit of transistor Q17, and the transistor functions as an emitter follower. Capacitor C11 and resistors R42, R43 form a differentiation network which differentiates the leading edge of the vertical signal obtained from transistor Q16. The differentiated signal appears at the emitter of transistor Q17 as a negative-going pulse (figure 8A), which is then fed to the head-select multivibrator (Q18-Q19) as a triggering pulse.

When the recorder is operated in the pixlock mode with TVA control, pin 5 of plug P1 is at ground potential and diode CR6 is forced to conduct, thus connecting the junction of resistors R41 and R44 to ground. This converts the circuit of transistor Q17 into a boxcar circuit. Transistor Q17, normally conducting, is cut off by the pulse fed to its base from transistor Q16. A positive-going pulse then appears at the collector of transistor Q17 (figure 8B), and the negative-going edge of this pulse is used in triggering the head-select multivibrator. Since the positive-going pulse appears at the collector of transistor Q17 only when Q17 is cut off, capacitor C12 must charge through the path formed by diode CR9 (biased into conduction by the positive-going edge of the pulse) in conjunction with resistors R45 and R46. The values of resistors R45 and R46 are chosen so as to provide a low impedance charging path, thereby insuring an adequate rise-time of the positive-going edge of the pulse, and at the same time to prevent any additional loading effect on the negative-going or triggering edge. The negative-going edge is actually formed by the discharging of capacitor C12 through the low impedance of transistor Q17 when Q17 is saturated (during the interval between pulses fed to its base from transistor Q16).

The width of the pulse at the collector of transistor Q17 is determined by the value of capacitor C11 and the control current (originating in the linelock module, no. 316) fed to resistor R42 through pin 21 of plug P1. Since the value of capacitor C11 is fixed, the pulse width is actually determined by the control current which in turn is dependent upon the error between tape and local vertical sync. Further discussion of the TVA servo loop operation appears in the headwheel servo System description.

Transistors Q18 and Q19 form the monostable head-select multivibrator, whose purpose is to insert any one of three different delays into the path of the phase sample pulse which is utilized by the tonewheel servo module (no. 314). The delays are provided in increments equal to the period of a quarter revolution of the headwheel, and may be selected by switching

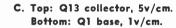

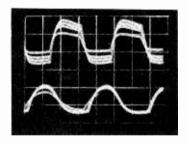

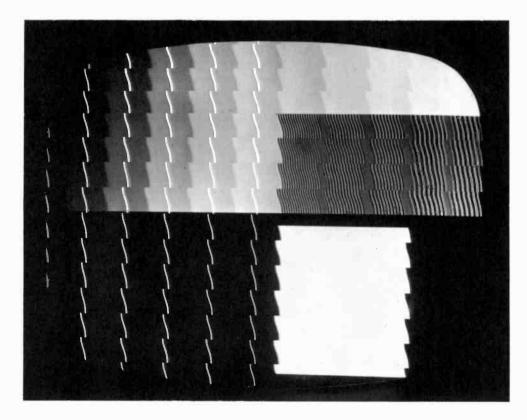

A. Top: Q17 emitter, 10v/cm.

Bottom: TP1 (REF), 2v/cm.

(Tonewheel Servo Mode)

(100 μsec/cm)

B. Top: Q17 emitter, 10v/cm. Bottom: TP1 (REF), 2v/cm. (Pixlock Servo Mode) (100 µsec/cm)

C. Top: Q19 collector, 10v/cm. Bottom: TP1 (REF), 2v/cm. (Head #1)

D. Top: Q19 collector, 10v/cm. Bottom: TP1 (REF), 2v/cm. (Head #2)

E. Top: Q19 collector, 10v/cm. Bottom: TP1 (REF), 2v/cm. (Head #3)

G. Q22 collector, 5v/cm.

Machine in PLAY mode. All sweep times 5 msec/cm, unless otherwise noted.

Figure 8—Head Select Multivibrator and Phase Sample Pulse Generator

14

the appropriate time constant network into the multivibrator circuit with switch S1 (HEAD SELECT).

Provision of the delays allows the heads to be "slipped" so that any head may play back the track containing vertical sync. In the normal tonewheel mode of operation, it is possible to "slip" heads by adjusting the capstan phasing. However, in switchlock or pixlock modes this is not possible because proper switchlock operation requires that the tracking of head and tape be maintained to insure correct alignment of the tape and local frame pulses. Therefore, with no delay introduced into the multivibrator circuit (switch S1 in position 1) capstan phasing should be adjusted so that head no. 1 is playing back vertical sync. Then, when the sample pulse is delayed with respect to the local reference pulse by an interval equal to the period of a three-quarter revolution of the headwheel, the tonewheel trapezoid (and hence head no. 1, whose position relative to the notch in the tonewheel is fixed) must follow the delay. This causes head no. 2 to play back the track containing vertical sync. Similarly, a delay equal to the period of onehalf or one-quarter revolution of the headwheel will cause head no. 3 or head no. 4 respectively to play back the track containing vertical sync.

This method of "slipping" heads eliminates the need for shifting control track phasing; thus the switchlock function continues to operate normally. It should be noted that it is not possible to slip heads while the machine is playing back tape in the pixlock mode, because under these conditions the tonewheel servo does not have control of the headwheel motor. Therefore, the head desired must be selected while operating the machine in tonewheel or switchlock mode, and it is then possible to go into the pixlock mode while playing back vertical sync with the head which has been selected. However, if the HEAD SELECT switch position is changed while the machine is playing back tape in the pixlock mode and an interruption occurs which causes the servo system to automatically switch to the switchlock mode, the newly-selected head will play back vertical sync when the system "re-locks" in the pixlock mode.

Returning to the head-select multivibrator circuit, the base of transistor Q19 is connected to ground through resistor R59 and diode CR8 when switch S1 (HEAD SELECT) is in no. 1 position, thus driving the transistor to saturation. At the same time, transistor Q18 saturates due to the current supplied to its base by returning diode CR7 and resistor R51 to ground. When transistor Q17 produces an output pulse, the negative-going edge of the pulse passes through diode CR5 to the base of transistor Q18 and cuts the transistor off. This produces an output pulse at the collector of transistor Q18 which is fed through resistor R56 to the junction of resistor R64 and capacitor C17. Here the output from transistor Q18 is combined with the output at the collector of transistor Q19. Since transistor Q19 conducts continuously when switch S1 is in no. 1 position, there will be no output pulse at its collector (figure 8C); therefore, only the pulse produced by transistor Q18 will appear at the junction of resistor R64 and capacitor C17.

Placing switch S1 in no. 2 position removes the ground connection (through resistor R59 and diode CR8) from the base of transistor Q19, and transistors Q18-Q19 then function as a monostable multivibrator with a time constant determined by the values of resistors R53, R57, capacitor C14, and trimmer potentiometer R54. In the multivibrator stable state, transistor Q18 is normally saturated due to the current supplied to its base by returning diode CR7 and resistor R53 to ground, and transistor Q19 is cut off because of the negative voltage applied to its base from the collector of transistor Q18. When transistor Q17 produces a pulse, the negative-going edge of the pulse is fed through diode CR5 to the base of transistor Q18, thus cutting the transistor off. Current is then supplied to the base of transistor Q19 through resistors R47 and R48 returned to ground, and Q19 is driven into saturation. Prior to the appearance of a triggering pulse, capacitor C14 is charged to -18volts with respect to ground. When the triggering pulse occurs, transistor Q19 saturates and the potential at the junction of capacitor C14 and diode CR7 immediately falls to -36 volts with respect to ground. Diode CR7 is reverse-biased by the negative voltage applied to its anode, so that the time constant circuit is disconnected from the base circuit of transistor Q18 during the timing cycle. Thus the leakage current of transistor Q18 and the triggering circuit is prevented from influencing the timing cycle, thereby insuring greater accuracy in timing.

With transistors Q18-Q19 operating as a monostable multivibrator, the output at the collector of transistor Q19 is a negative pulse whose positivegoing edge is utilized in generating the phase sample pulse for use in the tonewheel servo module. The negative pulse at the collector of transistor Q19 is matrixed with the output from transistor Q18 through resistors R56 and R64 and, in the matrixing process, the output at the collector of Q19 always predominates (except when switch S1 is in position 1 and Q19 has no output) because of the relative collector signal amplitudes and the values of the matrix resistors. When switch S1 is in no. 2 position, the negative pulse has a width equal to the period of a threequarter revolution of the headwheel (figure 8D); consequently, the phase sample pulse will be delayed by the period of a three-quarter revolution of the headwheel, and the headwheel will "re-phase" to allow head no. 2 to play back the track containing vertical sync. Output pulses from the collector of transistor Q19 with switch S1 in no. 3 position (delay equal to the period of one-half revolution of the headwheel), and in no. 4 position (delay equal to the period of one-quarter revolution) are shown in figures 8E and F. Switch positions 3 and 4 then, correspond to vertical sync playback on head nos. 3 and 4 respectively.

Potentiometer R54 acts as a fine adjustment in the timing circuit to insure that each increment of delay is as nearly equal to the period of a quarter revolution of the headwheel as possible. The adjustment is made internally while observing the tape and local vertical sync pulses simultaneously on an oscilloscope, with the machine operating in switchlock mode. While switching to each position of the HEAD SELECT switch, potentiometer R54 should be adjusted so that the vertical sync pulses are aligned as closely as possible at each position of the switch (see Adjustments).

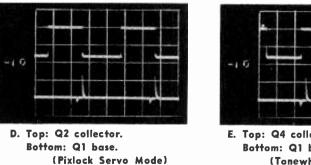

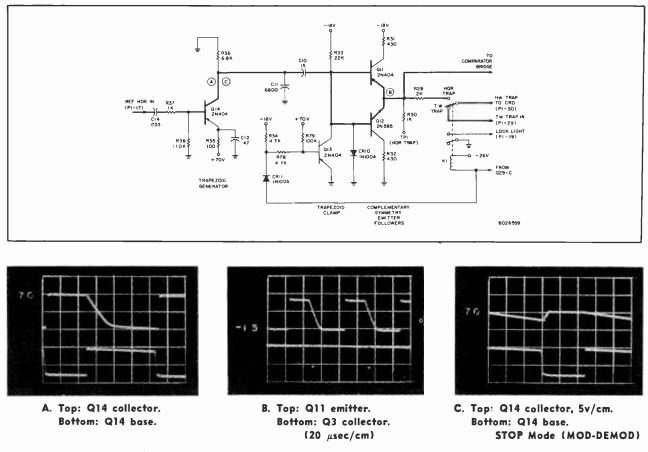

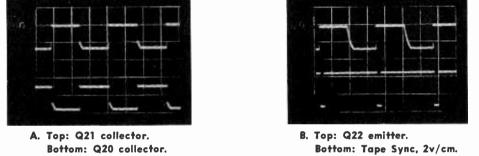

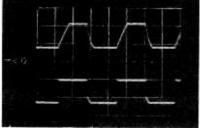

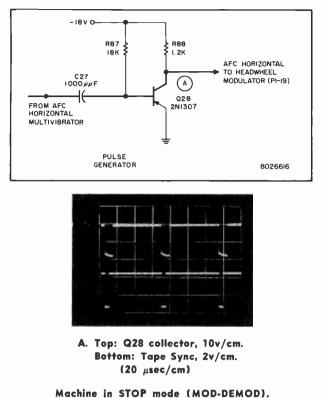

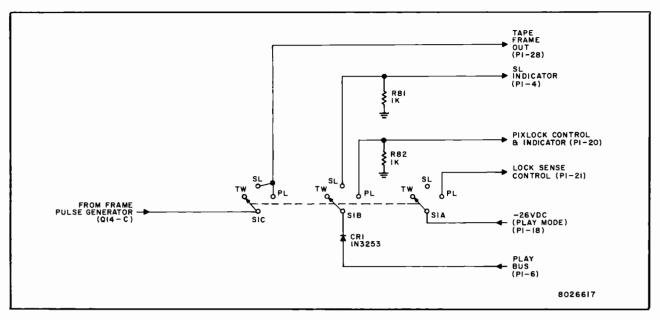

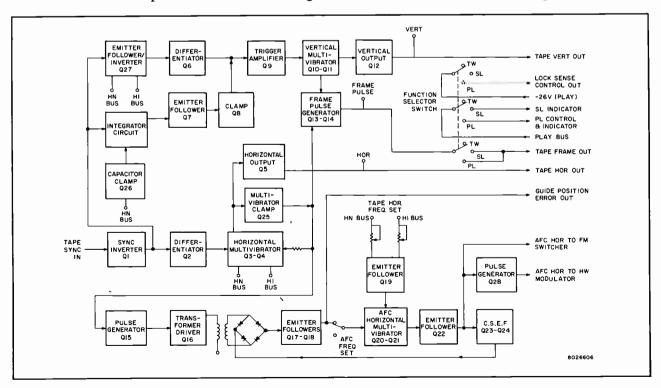

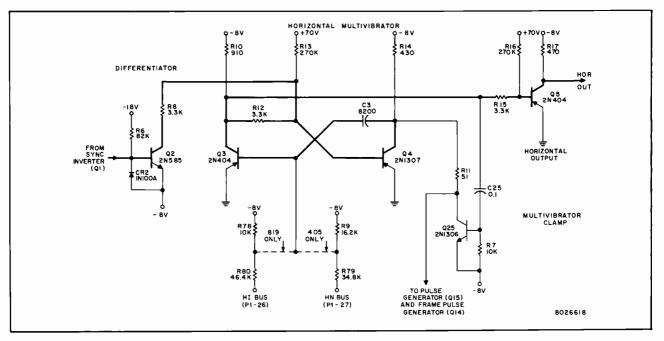

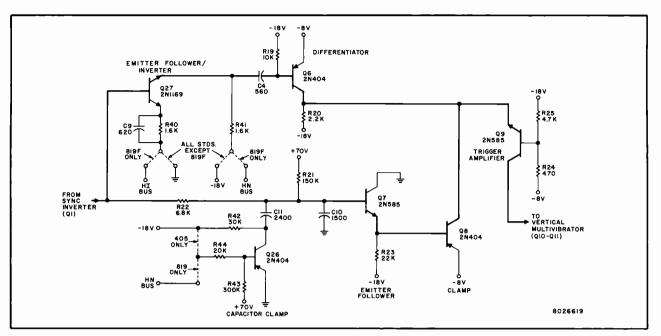

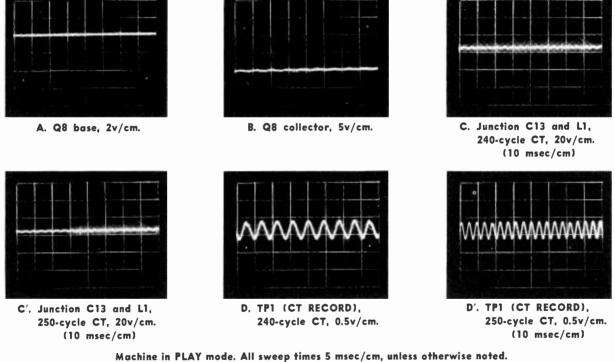

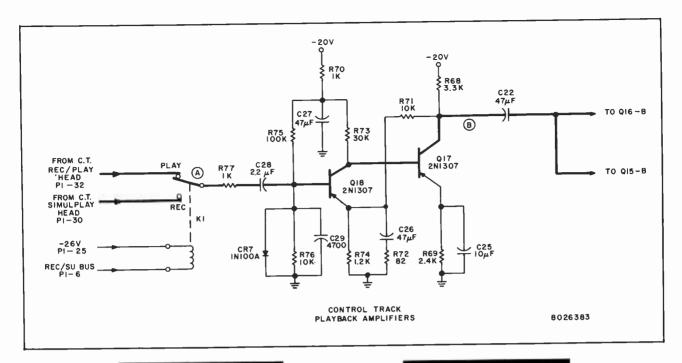

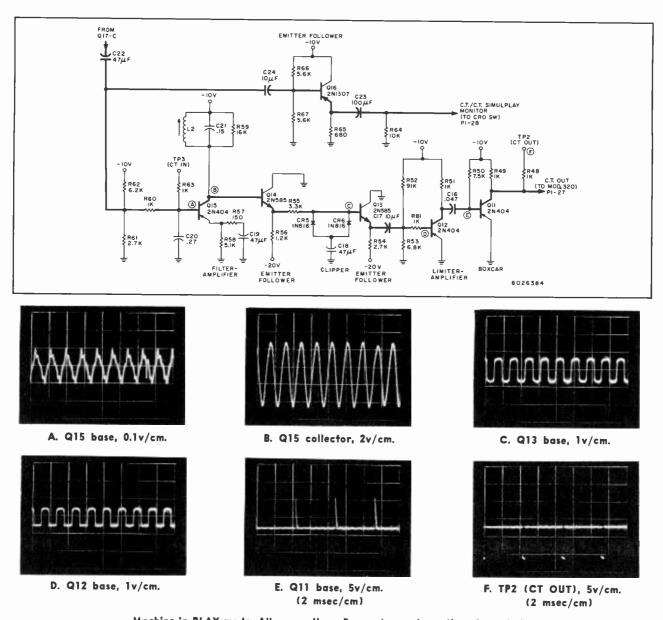

When the machine is operated in the RECORD mode, pin 6 of plug P1 is at ground potential and diode CR8 conducts. This connects the base of transistor Q19 to an external ground through resistor R59, and Q19 will then saturate regardless of the position of switch S1. Therefore, in the RECORD mode, no delay is introduced into the tonewheel phase reference pulse path by the multivibrator, and vertical sync will always be recorded by head no. 1.