A PENTON PUBLICATION \$10.00

JANUARY 20, 1997

0228-86178 MN 3UP340031A

## 200-Msample/s ADC Zips Through Color Conversion p. 67

Advanced Microprocessors Demand Amperes Of Current At <2V p. 31 Designing Power Systems Around Processor Specifications p. 53 Commercial Use Of Silicon MEMS Technology Is Coming Of Age p. 75 New Parasitic-Extraction Tools Needed For DSM Flows p. 111 Intelligent I/O Architecture Enables Faster, More Flexible Systems p. 125 Helpful Hints For Making Oscilloscope Measurements p. 143

# The 100,000 Gater.

## Introducing Altera's EPF10K100. The highest-density Programmable Logic Device ever.

With 100,000 gates, Altera signals a new era 🔊 for programmable logic. Big enough to handle most gate array designs and larger than any FPGA, the EPF10K100 satisfies even the most ferocious appetite for density. From prototyping through production, you get all the benefits of programmability plus new design capabilities.

## The secret to the EPF10K100 is below the surface.

The EPF10K100 features the industry's first embedded array architecture. Fast and efficient embedded array blocks can pack up to 24K bits of on-chip RAM, with room for other complex megafunctions such as microcontrollers and DSP

and PCI functions.\* These megafunctions shorten design cycles and allow for design re-use and re-targeting.

To help you attack your high density designs, our MAX+PLUS II development tools are completely compatible with leading EDA vendors, such as Synopsys, ensuring seamless integration with your existing design environment.

## It's time to give your designs more bite.

If high density, exceptional performance, and megafunction support will help you tackle your biggest design challenges, you're ready for the 100,000 Gater. Call us today at 800-9-ALTERA (800-925-8372),

Dept. A10NAP2. We'll send you a free FLEX 10K information kit. Or, find us at http://www.altera.com on the world-wide web.

Copyright 1996 Aftera Corporation Aftera FLEX, and VAX-PLUS are registered trademarks and FLEX 10K MAX+PLUS II and EPF10K100 are trademarks of Aftera Corporation AMPP, Altera Megafunction Partners Program, and The A teria Acventinge are service marks of Altera Carporation. All other trademarks are the property of their respective holders. All rights reserved

Developed through AMPP (Altera Megafunction Partners Pregram

## Complete Gigabit Ethernet solutions that go the distance.

HP's low-cost fiber optic transceiver modules and ICs enable you to accelerate the development of your Gigabit Ethernet products.

Whether you're designing products for intra-building or campus links, HP offers the most complete range of physicallayer Gigabit Ethernet solutions available. Our drop-in optical transceivers offer total flexibilty in link length, fiber type (MMF and SMF) and cost, and pair with our Serializer/Deserializer IC to complete your solution.

HP's 850nm VCSEL transceiver addresses standard multimode backbone applications at longer distances, higher reliability and lower costs relative to existing gigabit solutions. And our 1300nm controlled mode launch laser transceiver, proven in both datacom and telecom, drives MMF applications to over 500m and SMF applications up to 3km.

Add to this our 10-bit SERDES IC- a lowcost, low-power, field proven 3.3V bipolar IC- and you have a complete, cost effective phy-layer solution for all your network interface needs.

Of course, both HP transceivers are Class-1 eye safe and continue in our tradition of providing industry-leading technology that results in lower-cost, technically advanced products– such as our 1.5GBd module– all with HP's superior service and application support.

Gigabit Ethernet from HP. Because we go the distance.

**READER SERVICE 105**

Sampling now! Call 1-800-537-7715 ext. 2260 for *free* product literature and a special offer for discounted evaluation boards.

See us at Design Supercon

## Visit our Web site at www.hp.com/go/fiber

Call 1-800-450-9455 for a list of technical literature available by fax (U.S. and Canada).

CG0C9701

MICROPROCESSORS/PERIPHERALS MICROCONTROLLERS TELECOM LSIS VOICE SYNTHESIS LSIS VF DRIVERS/CONTROLLERS LCD DRIVERS/CONTROLLERS ASICS MEMORIES MEMORIES

# IC Solutions to a Winning Design

KGF 1639 GaAsPower FET for 3V dig =1 yrs ess communication efficiency =70% 33 40m/mm 1

MSM 7712 (XI) Wireless LAN Baseband Controller, IEEE802 11-D.3.1 compatible, 144-pin TOFP, +3V/+5V

MSM 6658A-XX, Speech Synthest, ar. 4Mbit RCM, 12-bit DAC, LPF, meloc, 127 phrases, 24-pin SOP

## Optimizing products for a wireless world

If you're working on the "next big thing" in the wireless market, Oki will support you with key IC solutions from concept to assembly.

With 115 years experience in manufacturing telecommunication and information systems, Oki has the expertise to help you to complete a winning design.

In digital cordless phones, digital and analog cellular communications, wireless LAN, PCS and more, Oki devices enhance product value with special features that end users notice and appreciate. You'll find features such as clear and natural ADPCM sound, high-efficiency, high-output, ultra small GaAs chips; small, 3-V telecom LSIs and 3-5V flexible interface ASIC devices with equally flexible design support.

We will assist your effort with close, personto-person partnership plus product development and field engineers dedicated to serving your needs.

Call Oki and finish on the winning side of wireless.

For more information, Contact: Oki Electric Industry Co., Ltd. Electronic Devices Group, Overseas Marketing Dept. 10-3, Shibaura 4-chome Minato-ku, Tokyo 108, Japan Tel: 81-3-5445-6000 Fax: 81-3-5445-6060

Oki Semiconductor Group 785 North Mary Avenue, Sunnyvale,

785 North Mary Avenue, Sunnyvale CA 94086-2909, U.S.A. Tel: 408-720-1900 Fax: 408-720-1918

#### Oki Electric Europe GmbH Head Office

Hellersbergstraße 2 D-41460 Neuss Germany Tel: 49-2131-15960 Fax: 49-2131-103539 Oki Electronics (Hong Kong) Ltd. Suite 1901-9, Tower 3, China Hong Kong City 33 Canton Road, Tsim Sha Tsui, Kowloon Hong Kong Tel: 852-27362336 Fax: 852-27362395

## 25 to 1910MHz SURFACE MOUNT VCO's from \$1395

J.Mini.Circuits

MININ' CIRCUIRS

Time after time, you'll find Mini-Circuits surface mount voltage controlled cscillators the tough, reliable, high performance solution for your wireless designs. JTOS wide band models span 25 to 1910MHz with linear tuning characteristics, low -120dBc/Hz phase noise (typ. at 100kHz offset), and excellent -25dBc (typ) harmonic suppression. JCOS low noise models typically exhibit -132dBc/Hz phase noise at 100kHz offset, and phase noise for all models is characterized up to 1MHz offset.

Miniature J leaded surface mount packages occupy minimum board space, while tape and reel availability for high speed production can rocket your design from manufacturing to market with lightening speed. Soar to new heights...specify Mini-Circuits surface mount VCO's.

D.Minicircuits

Mini-Circuits...we're redefining what VALUE is all about!

| JTOS/JCOS SPI                                                   | ECIFICATIO                                                | NS                                            |                                      |                                 |                                                        |                                           |

|-----------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------|--------------------------------------|---------------------------------|--------------------------------------------------------|-------------------------------------------|

|                                                                 | Freq. Range<br>(MHz)                                      |                                               | Harmonics<br>(dBc)<br>, Typ.         | V <sub>tun</sub> ···<br>1V to:  | Current (mA)<br>@+12V DC<br>Max.                       | Price<br>\$ea.<br>(5-49)*                 |

| JTOS-50<br>JTOS-75<br>JTOS-100<br>JTOS-150                      | 25-47<br>37.5-75<br>50-100<br>75-150                      | -108<br>-110<br>-108<br>-106                  | -19<br>-27<br>-35<br>-23             | 15V<br>16V<br>16V<br>16V        | 20<br>20<br>18<br>20                                   | 13.95<br>13.95<br>13.95<br>13.95          |

| JTOS-200<br>JTOS-300<br>JTOS-400<br>JTOS-535                    | 100-200<br>150-280<br>200-380<br>300-525                  | -105<br>-102<br>-102<br>-97                   | -25<br>-28<br>-25<br>-28             | 16V<br>16V<br>16V               | 20<br>20<br>20<br>20                                   | 13.95<br>15.95<br>15.95<br>15.95          |

| JTOS-765<br>JTOS-1025<br>JTOS-1300<br>JTOS-1650<br>JTOS-1910    | 485-765<br>685-1025<br>900-1300<br>1200-1650<br>1625-1910 | -98<br>-94<br>-95<br>-95<br>-92               | -30<br>-28<br>-28<br>-20<br>-13      | 16V<br>16V<br>20V<br>13V<br>12V | 20<br>22<br>30<br>30<br>20                             | 16.95<br>18.95<br>18.95<br>19.95<br>19.95 |

| JCOS-820WLN<br>JCOS-820BLN<br>JCOS-1100LN<br>Notes: *Prices for | 780-860<br>807-832<br>1079-1114<br>JCOS models            | -112<br>-112<br>-110<br>s are for 1 to 9 quar | -13<br>-24<br>-15<br>ntity. **Requir | 20V<br>14V<br>20V<br>ed to co   | 25 (@9V)<br>25 (@10V)<br>25 (@8V)<br>ver frequency ran | 49.95                                     |

Mini-Circuits

Mini-Circuits

reviews. Findes for access indicates are for it to 9 quantity. ""Hequired to cover frequency range. See "RF/IF Designer's Guide" or "VCO Designer's Handbook" for complete specifications.

DESIGNER'S KITS AVAILABLE

K-JTOS1 1 of each (10 pieces) JTOS-50, 75, 100, 150, 200, 300, 400, 535, 765, 1025, only \$149,95 K-JTOS2 1 of each (7 pieces) JTOS-50, 100, 200, 400, 535, 765, 1025, only \$99 K-JTOS3 2 of each (6 pieces): JTOS-1300, 1650, 1910, only \$114,95

**Mini-Circuits**

UAL SIZE

US 132 INT'L 133

P.O Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718)332-4661 INTERNET http://www.minicircuits.com CIRCLE READER SERVICE CARD For detailed specs on all Mini-Circuits products refer to • 740- pg. HANDBOOK • INTERNET • THOMAS REGISTER • MICROWAVE PRODUCT DATA DIRECTORY • EEM

F 234 Rev Orig

CUSTOM PRODUCT NEEDS...Let Our Experience Work For You.

January 20, 1997 Volume 45, Number 2

#### EDITORIAL OVERVIEW

## **TECH INSIGHTS**

VRMs: Technological First Aid, But For How Long? ... 44 While these off-the-shelf modules can satisfy current power requirements, future processor demands could spell the end of voltage regulator modules.

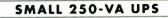

A 20-kHz Switcher Adapts UPSs For Consumer Use . . 62 A flyback switcher cuts size, weight, and cost of a 25-VA, 120-V uninterruptible power source.

## ANALOG OUTLOOK

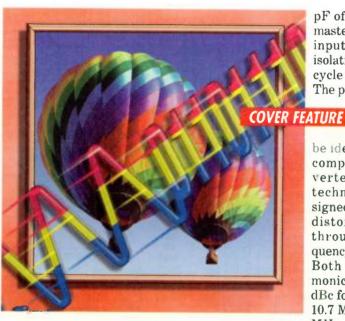

#### COVER FEATURE

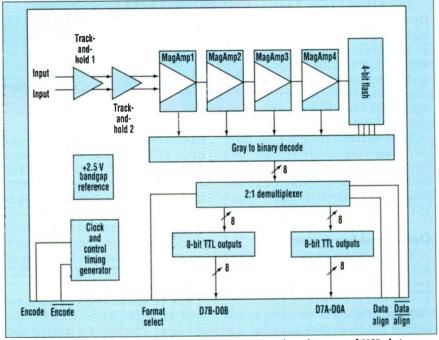

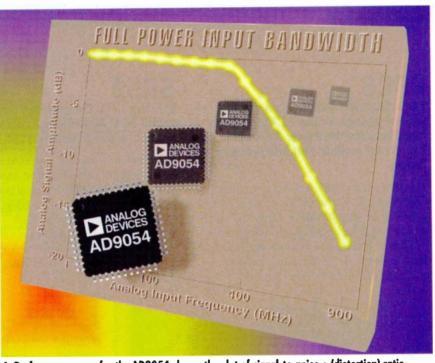

**Breakthrough Moves Conversion Into The Mainstream** ... 67 8-bit, 200 Msample/s ADC dramatically reduces the number of comparators needed, die size, and power consumption in comparison with flash converter technology.

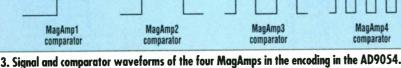

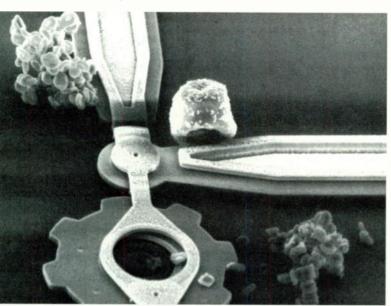

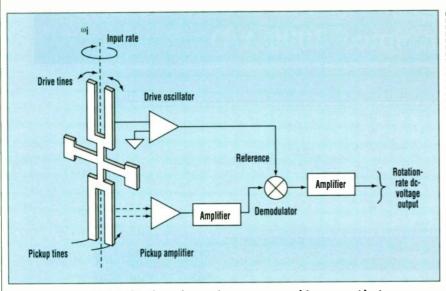

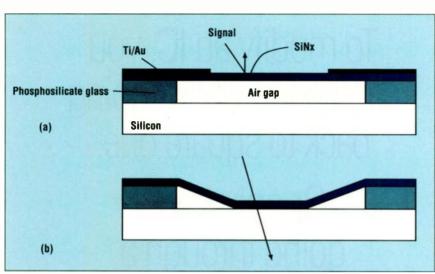

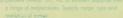

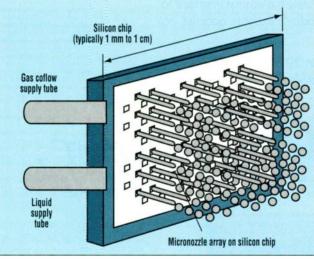

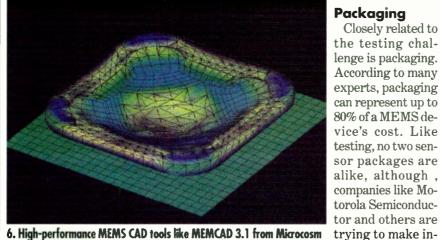

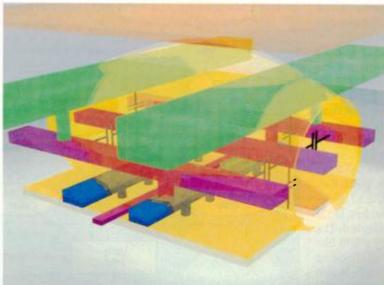

Silicon MEMS Is Coming Of Age Commercially .... 75 Micromachined sensors and actuators are expanding into new applications as they tackle the challenge of scarce CAD tools, and a lack of standardized packaging and testing methods.

| Upcoming Meetings10                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Editorial                                                                                                                                                         |

| Technology Briefing                                                                                                                                               |

| Technology Newsletter         23, 24           • Chip speeds genetic studies with its gene-scanning ability                                                       |

| ELECTRONIC DESIGN (USPS 172-080; ISSN 0013-4872) is published twice monthly<br>except for 3 issues in May and 3 issues in October by Penton Publishing Inc., 1100 |

ELECTRONAL STATUS IN 2006, ISAN OCIDER DY Panton Publishing Inc., 1100 Superior 3 issues in May and 3 issues in October by Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543. Paid rates for a one year subscription are as follows: \$105 U.S., \$185 Canada, \$210, \$255 International. Second-class postage paid at Cleveland, OH, and additional mailing offices. Editorial and advertising addresses: ELECTRONIC DESIGN, 611 Route #46 West, Hasbrouck Heights, NJ 07604. Telephone (201) 393-6060. Facsimile (201) 393-0204. Printed in U.S.A. Title registered in U.S. Patent Office.

## **ANALOG OUTLOOK**

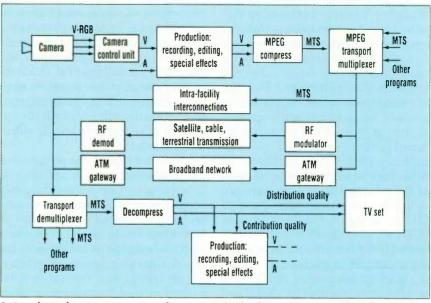

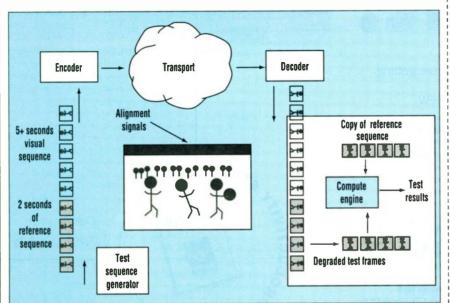

**Video Quality Measurements In Modern TV Systems** .... 91 In-service testing from vertical interval signals will no longer be possible.

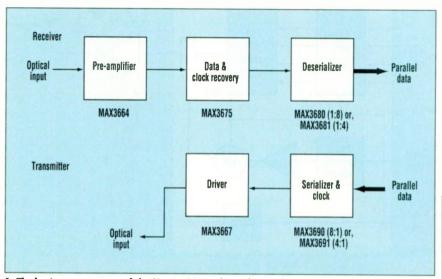

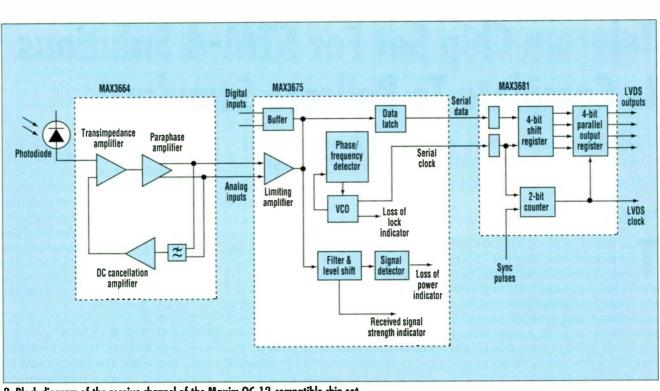

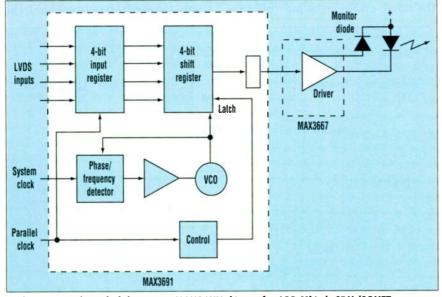

Telecom Chip Set For STM-4 Solutions Is Complete To<br/>Bellcore Standards101The latest use of HF processes and two serial/parallel<br/>rate conversions are now offered in the 3.3-V range.

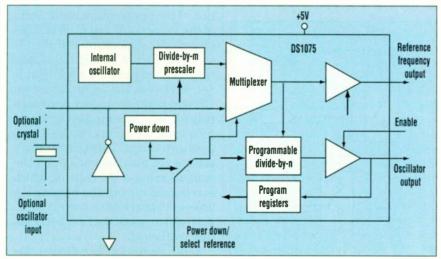

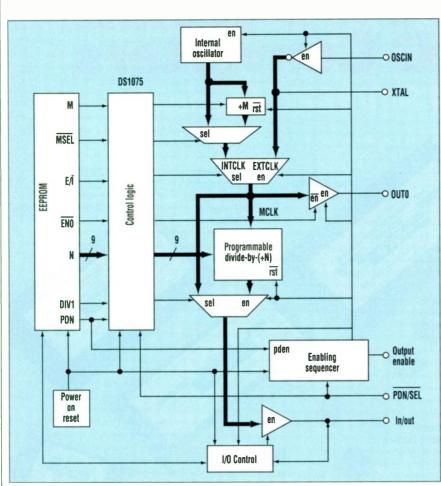

Monolithic IC Oscillator Has Near-Quartz Stability . . 105 A tiny 200-kHz to 100-MHz IC oscillator offers  $\pm 1\%$  frequency stability over commercial temperature range. while operating at 5 V  $\pm 10\%$ .

#### EDA

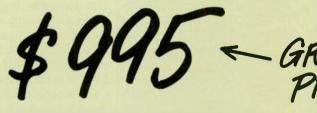

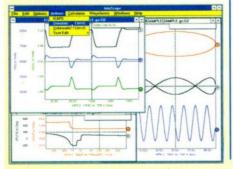

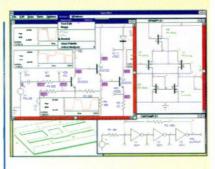

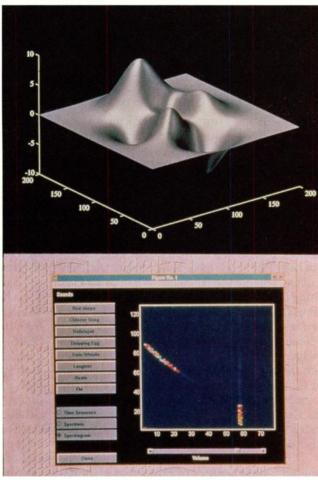

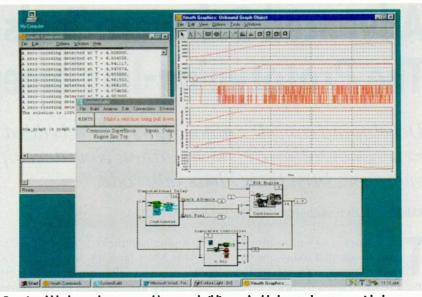

System-Level Tool Upgrades For Team-Based Design . . 121

• High-level systems design tool offers design-team management, automated optimization, and virtual troubleshooting/debugging capabilities.

- Acoustic methods used to identify defective heart valves

- Hardware vendors can develop hot-pluggable PCI systems

- I<sub>2</sub>O systems, peripherals, and software are starting to arrive

- New class of polymer to boost low-cost MCM manufacture

- All-silicon system processes light as well as electricity

Copyright 1997 by Penton Publishing Inc. All rights reserved. The contents of this publication may not be reproduced in whole or in part without the consent of the copyright owner. For subscriber change of address and subscription inquiries, call (216) 696-7000. Mail your subscription requests to: Penton Publishing Subscription lockbox, P.O. Box 96732, Chicago, IL 60693. POSTMASTER: Please send change of address to ELECTRONIC DESIGN, Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543.

-

When you think of QT Optoelectronics, you probably think of optocouplers. But, QT is also a leading supplier of LEDs.

We've got a complete line of high-quality, reliable LED lamps and displays. And our authorized distributors — in hundreds of cities around the world — can deliver the products you need on time and at a good price.

Don't go barking up the wrong tree for your LEDs.

Call **800-LED-OPTO** today for more information and the phone number of your nearest QT Optoelectronics distributor.

United States 800-533-6786 France 33 01/43.99.25.12 Germany 49 089/96.30.51 United Kingdom 44 01296/39.44.99 Asia/Pacific 603/735-2417

© 1996 QT Optoelectronics

# YOUR TOP DOG FOR LEDS

## FLFFTRI NH-

January 20, 1997 Volume 45, Number 2

### EDITORIAL OVERVIEW

#### EMBEDDED SYSTEMS

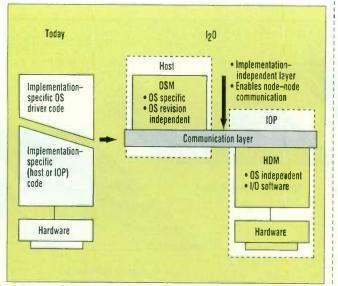

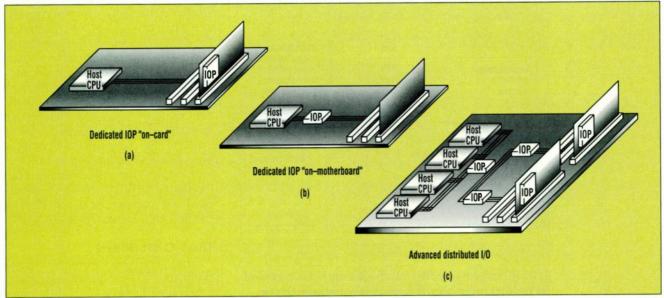

Intelligent I/O Architecture Enables Faster, More Flexible Systems ......125 Intelligent I/O subsystem eliminates multiple drivers for the same device and offers options for high-speed data transfer.

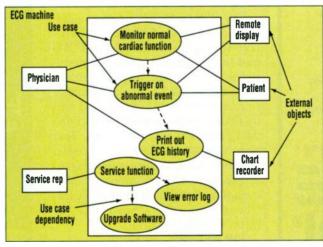

| Advanced Software Tools Narrow The Prototyping-              |  |

|--------------------------------------------------------------|--|

| Implementation Gap                                           |  |

| Development tools are helping engineers turn ideas into code |  |

| Update On Object Notation137 |

|------------------------------|

| Update On Web Servers        |

| Product Features             |

### **TEST AND MEASUREMENT**

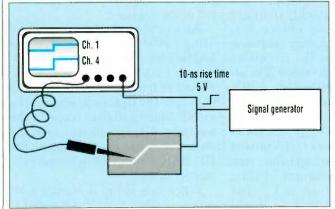

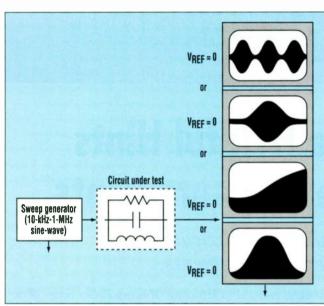

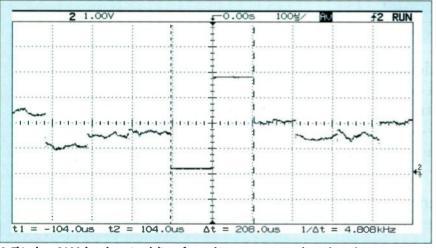

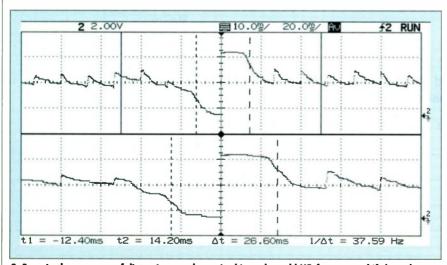

Helpful Hints For Making Scope Measurements ....143 Oscilloscope users supply some practical ideas on how to make better measurements.

| Update On ASIC Test      |

|--------------------------|

| Update On Wafer Probe150 |

| Product Features         |

####

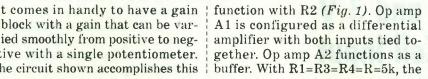

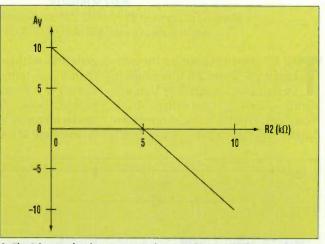

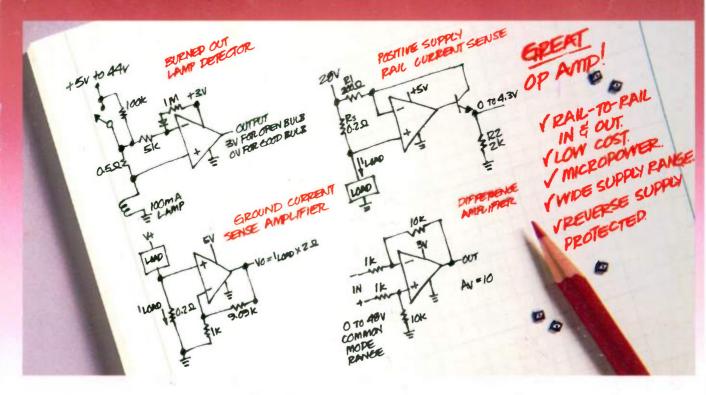

• Single pot swings amplifier gain positive or negative

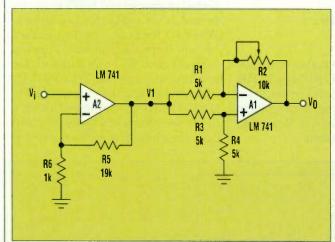

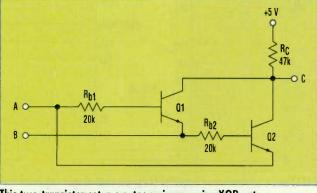

- Inexpensive two-transistor XOR gate

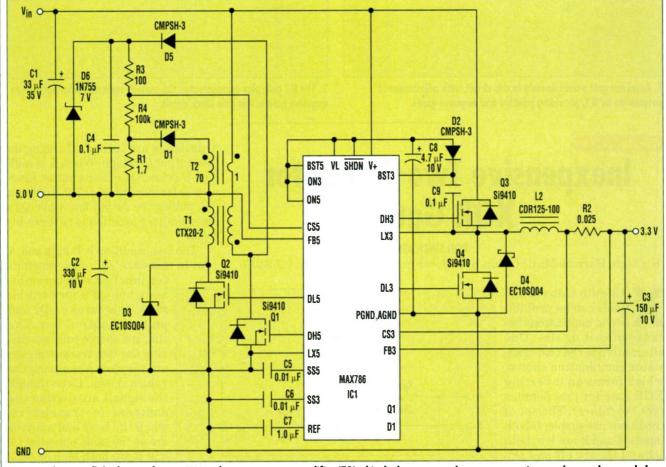

- Derive 5 and 3 V from 4-cell input

- Linear true-mean-square temperature controller

| Pease Porridge                                 |

|------------------------------------------------|

| Straight Talk For Serious Digital Designers165 |

| New Products                                   |

Permission is granted to users registered with the Copyright Clearance Center Inc. (CCC) to photocopy any article, with the exception of those for which separate copyright ownership is indicated on the first page of the article, provided that a base fee of \$2 per copy of the article plus \$1.00 per page is paid directly to the CCC, 222 Rosewood Drive, Danvers, MA 01923 (Code No. 0013-4872/94 \$2.00 +1.00). Can. GST #R126431964. Canada Post International Publications Mail (Canadian Distribution Sales Agreement Number 344117). Copying done for other than personal or internal reference use without the express permission of Penton Publishing. Inc. is prohibited. reference use without the express permission of Penton Publishing, Inc. is prohibited. Requests for special permission or bulk orders should be addressed to the editor.

### QUICKLOOK

## DEPARTMENTS

| Info Page             | <br>• | • | • | • • | <br>• | • | • | • | • | • • | <br>• | •  |    | ••• | 8 |

|-----------------------|-------|---|---|-----|-------|---|---|---|---|-----|-------|----|----|-----|---|

| EE Currents & Careers |       |   |   |     |       |   |   |   |   |     |       |    |    | 16  | 9 |

| Index of Advertisers  |       |   |   |     |       |   |   |   | • |     |       |    |    | .17 | 6 |

| Reader Service Card   |       |   | • |     |       |   |   |   |   |     |       | .1 | 76 | 5A- | D |

COVER ILLUSTRATION BY: BRUCE JABLONSKI

#### Jesse H. Neal Editorial Achievement

1967 First Place Award 1968 First Place Award 1972 Certificate of Merit 1975 Two Certificates of Merit 1989 Certificate of Merit 1976 Certificate of Merit

Low Profile .2" ht. Surface Mount Transformers & Inductors

All PICO surface mount units utilize materials and methods to withstand extreme temperature (220°C) of vapor phase, IR, and other reflow procedures without degradation of electrical or mechanical characteristics.

#### AUDIO TRANSFORMERS

Impedance Levels 10 ohms to 10,000 ohms, Power Level 400 milliwatt, Frequency Response ±2db 300Hz to 50kHz. All units manufactured and tested to MIL-T-27.

#### POWER and EMI INDUCTORS

Ultra-miniature Inductors are ideal for Noise, Spike and Power Filtering Applications in Power Supplies, DC-DC Converters and Switching Regulators. All units manufactured and tested to MIL-T-27.

#### PULSE TRANSFORMERS 10 Nanoseconds to 100

10 Nanoseconds to 100 Microseconds. ET Rating to 150 Volt-Microsecond. All units manufactured and tested to MIL-T-21038.

## **ELECTRONIC DESIGN**

#### NORTH AMERICAN EDITION

Executive Editor: **ROGER ALLAN** (201) 393-6057 rallan@class.org Managing Editor: **BOB MILNE** (201) 393-6058 bmilne@class.org

Technology Editors:

Analog: PAUL McGOLDRICK (San Jose) (408) 441-0550, ext. 113; 102447.346@compuserve.com Analog & Power: FRANK GOODENOUGH (617) 227-4388 75410.2361@compuserve.com Communications: LEE GOLDBERG (201) 393-6232 leeg@class.org Components & Packaging: PATRICK MANNION (201) 393-6097 pcmann@ibm.net Computer Systems: RICHARD NASS (201) 393-6090 richnass@class.org

Design Automation: CHERYL AJLUNI (San Jose) (408) 441-0550, ext. 102; cjajluni@class.org Digital ICs: DAVE BURSKY (San Jose) (408) 441-0550, ext. 102; cjajluni@class.org Embedded Systems/Software: TOM WILLIAMS (Scotts Valley) (408) 335-1509 tomwillm@ix.netcom.com

Test & Measurement: JOHN NOVELLINO (201) 393-6077 jnovelli@class.org

Test & Measurement: JOHN NOVELLINO (201) 393-6077 jnovelli@class.org New Products: ROGER ENGELKE JR. (201) 393-6276 rogere@csnet.net Contributing Products Editor: MILT LEONARD

Editorial Headquarters: (201) 393-6060 Fax: (201) 393-0204 E-mail: edesign@class.org P.O. Box 821, Hasbrouck Heights, N.J. 07604

Field Correspondents: West Coast Executive Editor: DAVE BURSKY (San Jose) (408) 441-0550, ext. 105; dbursky@class.org Western Regional Editors: CHERYL J. AJLUNI (San Jose) (408) 441-0550, ext. 102; cjajluni@class.org PAUL MCGOLDRICK (San Jose) (408) 441-0550, ext. 113; 102447.346@compuserve.com TOM WILLIAMS (Scotts Valley) (408) 335-1509 tomwillm@ix.netcom.com 2025 Gateway Place, Suite 354, San Jose, CA 95110 (408) 441-0550 Fax: (408) 441-6052

### London: PETER FLETCHER

16 Maylons Road, Hextable, Kent, UK 44 1 322 664 355 Fax: 44 1 322 669 829 E-mail: panflet@cix.compulink.uk.co

Munich: **ALFRED B. VOLLMER** Eichenstr. 6, 82024 Taufkirchen (near Munich) Germany 49 89 614-8377 Fax: 49 89 614-8278 E-mail: 75162.1246@compuserve.com

Chief Copy Editor: **MICHAEL SCIANNAMEA** (201) 393-6024 mikemea@class.org Copy Editor: **DEBRA SCHIFF** (201) 393-6024 debs@csnet.net Consulting Editor: **LISA MALINIAK** Ideas For Design Consulting Editor: **JIM BOYD**

Contributing Editors: RON KMETOVICZ, ROBERT A. PEASE, WALT JUNG, HOWARD JOHNSON Production Manager: PAT A. BOSELLI, Production Coordinator: WAYNE M. MORRIS

Group Art Director: PETER K. JEZIORSKI, Associate Group Art Director: TONY VITOLO Staff Artists: LINDA GRAVELL, CHERYL GLOSS, JAMES M. MILLER Editorial Support Supervisor: MARY JAMES Editorial Assistant: ANN KUNZWEILER, BRADIE SUE GRIMALDI (San Jose)

Advertising Production:

(201) 393-6093 or Fax (201) 393-0410 Production Manager: EILEEN SLAVINSKY, Assistant Production Manager: JOYCE BORER Production Assistants: MYLAN CHU, BARBARA LATORRE, DORIS CARTER, JANET CONNORS, LUCREZIA HLAVATY

Circulation Manager: BARBARA TILLETT (216) 931-9158 Reprints: ANNE ADAMS (216) 696-7000, ext. 2626

#### **Published by Penton Publishing**

Electronic Design Information Group: Editorial Director: **STEPHEN E. SCRUPSKI** (201) 393-6070 Publisher: **JOHN G. FRENCH** (201) 393-6055

R

Call, write, fax or visit us on the Internet for your FREE CATALOG today!

П

CORFORATION

TSU

M CE

+85°C

TSU

M CF

+85°0

TSU

+85°0

M

0

0

0

νnΩµF

(M)

μF

(M)

1700

1 // -1

OVDC VAC SOVDC

ΔΕ100Ω

S

кті **Я**

mo

HU Technology,

**4HEEGER**

MAIRE

son

ANN

11

822K

Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701-0677 Toll-Free: 1-800-344-4539 • Fax: 218-681-3380 READER SERVICE 101

Visit us on the Internet • http://www.digikey.com

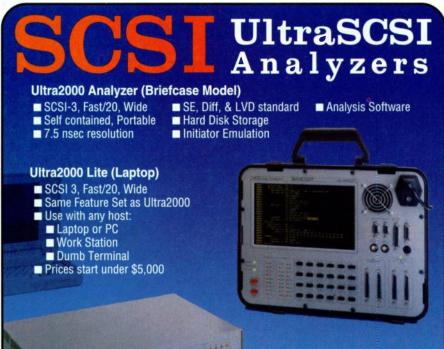

**READER SERVICE NUMBER 160**

#### Basics of SCSI booklet available free!!

**(415) 322-5322**

Fax: (415) 322-0455 http://www.ancot.com

115 Constitution Drive, Menlo Park, California 94025

## MEETINGS

#### **JANUARY 1997**

Asia & South Pacific Design Automation Conference with EDA Technofair (ASP-DAC '97), Jan. 28-31. Makuhari Messe Convention Center, Chiba, Japan. Contact Yoko Nishikawa, ASP-DAC '97 Secretariat, CONVEX Inc., Ichijoji Bldg. 2-3-22 Azabudai, Minatoku, Tokyo 106 Japan; (81) 3 3589 3355; fax (81) 3 3589 3974; e-mail: convex@po.iijnet.or.jp; Internet: http://www.jesa or jp/ASPDAC/.

Second Annual Pan Pacific Microelectronics Symposium, Jan. 29-31. Sheraton Maui Resort, Maui, HI. Contact JoAnn Stromberg, Pan Pacific Symposium, 5200 Wilson Rd., Suite 215, Edina, Minnesota 55424; fax (612) 929-1819.

#### FEBRUARY

IEEE Aerospace Conference, February 1-8. Snowmass at Aspen, Colorado Contact Stephen Franklin, Deputy Program Chair, 4800 Oak Grove Drive, Pasadena, California 91109; (818) 393-0814; fax (818) 393-0530; e-mail: stephen.f.franklin@jpl.nasa.gov; Internet:http://chip.plk.af.mil:1050/icee/index.html

IEEE Power Engineering Society Winter Meeting, February 2-6. New York Hilton & Towers, New York. Contact Frank E. Schink, 14 Middlebury Ln., Cranford, New Jersey 07016-1622; (908) 276-8847; fax (908) 276-8847.

IEEE International Solid-State Circuits Conference (ISSCC '97), February 6-8. San Francisco Marriott Hotel, San Francisco, California. Contact Diane Suiters, Courtesy Associates, 655 15th St. N.W., Suite 300, Washington, DC 20005; (202) 639-4255; fax (202) 347-6109; e-mail: isscc@mcimail.com.

Third Annual Conference on Business Opportunities & Operational Requirements for Utilities in Telecommunications (Utilicom '97), Feb. 19-21. Washington Vista Hotel, Washington, DC. Contact (800) 822-6338 or (202) 842-3022 ext. 317, or http://www.brp.com.

Second International Conference on Chip-Scale Packaging, February 20-21. Sunnyvale Hilton Inn, Sunnyvale, California. Contact Subash Khadpe; (610) 799-0419; fax (610) 799-0519; email: skhadpe@semitech.com.

READER SERVICE NUMBER 165

## One tiny footprint. A GIANT LEAP FOR POWER MOSFETS.

TEMIC's newest LITTLE FOOT<sup>®</sup> is the smallest power package available.

|            |                     | Maximum Ratings         |                         |                    |        |  |  |  |  |  |

|------------|---------------------|-------------------------|-------------------------|--------------------|--------|--|--|--|--|--|

| Part No.   |                     | rDS(e                   | on)(Ω)                  |                    |        |  |  |  |  |  |

|            | V <sub>DS</sub> (V) | V <sub>GS</sub> = 10 V  | V <sub>GS</sub> = 4.5 V | I <sub>D</sub> (A) | Gender |  |  |  |  |  |

| Si3454DV/X | 30                  | 0.065                   | 0.095                   | ±4.2               | N-Ch   |  |  |  |  |  |

| Si3455DV/X | 30                  | 0.100                   | 0.19                    | ±3.5               | P-Ch   |  |  |  |  |  |

| Part No.   | V <sub>DS</sub> (V) | V <sub>GS</sub> = 4.5 V | V <sub>GS</sub> = 2.5 V | I <sub>D</sub> (A) | Gender |  |  |  |  |  |

| Si3442DV/X | 20                  | 0.07                    | 0.095                   | ±4.0               | N-Ch   |  |  |  |  |  |

| Si3441DV/X | 20                  | 0.10                    | 0.135                   | ±3.3               | P-Ch   |  |  |  |  |  |

We've added an even smaller package to our popular line of LITTLE FOOT power MOSFETs, the TSOP-6. At one quarter the footprint of an SO-8 and with cool thermal characteristics, this new LITTLE FOOT MOSFET jumps way ahead of the competition for immediate application in portable phones and computers.

For today's ever shrinking designs, these TSOP-6 products are low enough in resistance and high enough in power to allow you to make small, high-efficiency dc/dc converters and power management circuits.

In fact, this new single LITTLE FOOT TSOP-6 has the same resistance and

power ratings as today's standard, the dual LITTLE FOOT SO-8, which means less board space for equal performance. And since these new power MOSFET products are dual sourced by TEMIC and Motorola, we're already a step ahead of demand.

So take the first step toward your smallest, most efficient designs ever. Call your local TEMIC sales office today, or call 1-800-554-5565 ext. 515 for more information.

TEMIC Semiconductors

TEMIC is a company of Dalmler-Benz. Members of TEMIC Semiconductors: Telefunken Semiconductors, Siliconix, Matra MHS, Dialog Semiconductor. 2201 Laurelwood Road, Santa Clara, CA 95054 Fax: 408-567-8995. TEMIC European Sales: GERMANY: 0130 857 320. UNITED KINGDOM: 01344-707300. FRANCE: 1-30 60 71 87. ITALY: 02-332 121. SCANDINAVIA: 08-733 0090. ©1996 TEMIC. All rights reserved.

# It's no longer system-on-a-chip or time-to-market. With SPGAs, it's both.

System Programmable Gate Arrays... The new direction in high-level logic design.

Scream onto the new design highway called System Programmable Gate Arrays (SPGAs). Designing with programmable logic has never been like this!!

Talk about open road, SPGAs will begin at 50,000 gates and go up to 1,000,000. That's big enough to handle a complete system–logic, memory, and processor cores– on a single chip.

Take the express lane to fast time-to-market. SPGAs will be the most advanced, cost-efficient programmable targets for reusable soft IP blocks or hard-wired IP cores.

Drive your next system level design onto an SPGA. Feel the functionality, performance and cost-effectiveness never before achievable on a single programmable device.

Follow the signs to SPGAs. It's the high road to fast time-to-market and system-on-a-chip design.

WWW.ACTEL.COM

To learn more about SPGAs, visit our Web site at *www.actel.com*.

©1997 Actel Corporation. All rights reserved. Actel Corporation, 955 East Arques Avenue, Sunnyvale, CA 94086. Actel Europe Ltd. Daneshill House, Lutyens Close, Basingstoke, Hampshire, England RG24 8 AG. The Actel logo is a trademark of Actel Corporation.

## What'll you get with our 16-bit micros?

## More code efficiency

Our TLCS-900 microcontrollers save space by letting you write more instructions in the same memory block.

## High performance

While on-board peripherals and a 25MHz clock rate take portable applications places they've never been.

## Low power

With operating requirements from 2.7 to 5.5V, it's flexible enough for today's mixed-voltage world.

## Highly concentrated intelligence

And has all the brainpower you need for those amazing new breakthroughs.

www.micro16.toshiba.com

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

1-800-879-4963

ISOPOOI Uncle URL is a trademark of Toshuba America Electronic Components, Inc @1996 Toshuba America Electronic Components, Inc HDQ-96-218

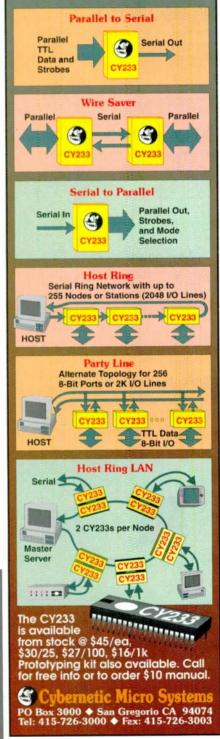

## CY233 Serial/Parallel Conversion or Networks

**CY233** connects up to 255 computers, peripherals, or remote sites, 5v CMOS 40-pin IC works with RS232/422 drivers. 300 baud to 57.6K baud. Supports a token in Peer or Host ring LAN modes. Numerous other operational modes:

## **ELECTRONIC DESIGN**

EDITORIAL

## The Government And R&D Funding

A ccording to "Science & Engineering Indicators 1996," a U.S. National Science Foundation (NSF) publication, total R&D funding in the U.S. reached a high of \$171 billion in 1995, representing a 2% real decline over 1990 funding. Moreover, federal outlays, representing 36% of total R&D outlays in 1995, have been falling annually since 1987. The report concludes that U.S. R&D funding can do better.

This is a troubling trend, especially at a time of tightening corporate budgets and the globalization of the economy. Unlike the U.S., R&D budgets for other countries have steadily increased, and many national, regional, state, and local governments are providing help to companies in the private sector to develop products for the commercial market. But in the U.S., much of the government's funding, provided via the NSF, the Defense Applied Research Agency (DARPA), the National Institute of Standards and Technology (NIST), and the National Aeronautics and Space Administration (NASA), is for the development of products and systems for the military and the government. The portion of the government's funding to the private sector to develop products for the commercial market pales in comparison.

Many in the private sector would argue against government funding for the private sector, correctly pointing out the many pitfalls they envision and examples of past government-sponsored "boondoggles." But how long can we really afford this "hands-off" approach? An industry consortium like Sematch, has shown that it can contribute positively to the private sector, thanks to some government funding. In this global economy, we seem to be on an uneven playing field, with many overseas companies getting unlimited government help while we cry out against any government involvement. Is it any wonder that technologies developed in the U.S. like semiconductor memories, robotics, flat-panel displays, TVs, and VCRs, have gone overseas, and have rapidly found applications in foreign markets, a situation that continues?

The U.S. economy has come a long way since the days of the space age and unlimited defense spending, when almost every electronics company had a government contract. Many private companies have weaned themselves off government funding for defense purposes and have channeled their efforts into profitable commercial markets. But that's no reason to espouse an inherent "distrust" of the government, as some in the private sector would have you believe. It's time to rethink this position before it may be too late. What do you think? rallan@class.org.

# In Wireless Communications, Team Up With The Frontrunner.

Competition is relentless in wireless design. So the best place to start is far ahead. With Oki. Whether you design products for use around the home, around town or around the world, only Oki has the advanced 3 Volt technology you need. Everything from CMOS baseband to the most efficient GaAs RF— complete system solutions for 3 Volt cordless, cellular and wireless LAN applications. No surprise. Oki's been offering wireless communications products from the industry's inception. That's why you find Oki's leading-edge technology in products from major communications manufacturers worldwide. Once you begin partnering with the wireless leader, you'll never look back. To find out more, vlsit our communications products corner, with application notes, on the Oki Web site at http://www.okisemi.com. Or call 1-800-OKI-6388.

Ok Semiconductor 785 North Mar. Alemue, Sunnyvale, CA 948 6-2009 Phone: 404-7 0-1 00 File 409-7 0-1 1

# SERIOUS PRODUCT

Ventitiex

Contour Defibrillator Manufactured by Ventritex, Inc. Sunnyvale, CA

## SPECIAL PROCESS, SPECIAL CUSTOMER

## MANUFACTURING MADE SIMPLE

Orbit offers the total solution to your manufacturing needs by providing a unique combination of process development and manufacturing efficiencies. Whether you need ten or ten million pieces, Orbit's process development programs can significantly reduce your non-recurring

engineering expenses. Our proven manufacturing expertise can provide production units in tested wafer form, raw die or packaged parts. We provide processes that meet or exceed the stringent requirements of either the aerospace/defense industry or the FDA. With our established on-site manufacturing facilities, Orbit is able to keep your manufacturing costs down, even at low volumes. And with a customer service organization that follows and protects your project throughout the entire manufacturing process, you have Orbit's total commitment.

We guarantee success. For more information contact Betty Newkirk, Vice President Customer Service or visit our web page at www.orbitsemi.com.

# SERIOUS SUPPLIER

## **TEN TO TEN MILLION PIECES**

- 0.5p 5p Processes

- Low NRE Costs

- Guaranteed Delivery\*

- Military/FDA Standards

- Any Commercial Package

- Raw Die

- Tested or Untested Wafers

"Orbit provides financial guarantees on delivery dates See your Orbit representative for more details.

A DII GROUP COMPANY

Orbit Semiconductor, Inc. 169 Java Dr., Sunnyvale, CA 94089 408-744-1800 Fax 408-747-1263 http://www.orbitsemi.com

800-331-4617

## **TECHNOLOGY BRIEFING**

## ASICS Analog & Mixed-Signal THE RIGHT PROCESSES • CMOS

- CMUS

- Bipolar

- Bi-CMOS

- DC to 2 GHz

## **FULL CUSTOM DESIGNS**

A/Ds & DACs PLL, Frequency Synthesis Mixers & Amplifiers Modulators & Detectors Video Processing Instrumentation Mixed Mode Control Switch Capacitor FIR Filters

## INTEGRATED VALUE

RF, analog and digital combined on-chip to increase your product performance with fewer parts. Designed for test, yield and reliability to meet your production and cost goals whether your volumes are 100s or 1,000,000s per year.

RTG has the signal processing experience to make your next ASIC a success. RTG uses a top-down design methodology and the latest Cadence IC design tools to quickly design and deliver integrated circuits for commercial, military and hi-rel markets.

e-mail: sales@rtg.com

## **To Infinity And Beyond!**

K, call me a hypocrite, a supporter of corporate welfare, but I'm nuts for the space program. Despite its waste and inefficiency, I get a lump in my throat when watching a launch, knowing that it's my tax dollars that NASA's burning. When my sensible friends ask me to justify the billions spent on heaving a few dozen souls and a few tons of hardware into the void, I mumble pious words about technical spin-offs and scientific discoveries, but it's all nonsense. I've finally realized that the only honest justification for it is that it's a really cool thing to do—and that it gives us a chance to dream.

Of all the breakthroughs and marvels that the space program gave us, its biggest contribution may have been inspiring generations of nerdy kids to crack their books, do their homework, and dream about one day going to the stars. Like our athletic counterparts, most of us fell short of playing in the major leagues. But, a lucky few made it, with the rest of us cheering them on from the sidelines —and we were all better off for having made the attempt.

It would be great to give today's kids a chance to dream about the stars again. Somehow, NASA has to regain the public support and sense of purpose it had back in the sixties, and I've got a plan.

The recent flurry of interest in Mars and the spectacular science the Hubble telescope is delivering makes us ripe for a renaissance of the space program. All that's needed is to gently nudge public opinion in the right direction and the politicians would be falling all over themselves to support the long-term programs that would lead us toward becoming a true spacefaring nation.

You can help by writing Dan Goldin, Director of NASA, and ask him to name me head of public relations. Once in charge, I'd launch a campaign to turn the space program into a spectator sport that rivals the popularity of baseball, football, or basketball.

First, I'd overhaul the NASA channel and market the distribution rights to the television networks. My version of launch coverage would be a blend of MTV and Monday Night Football, with a touch of Mr. Wizard. If the networks can make a bunch of guys knocking the stuffing out of each other look interesting, think of what we can do with something as exciting as a rocket launch!

Every launch would be covered with play-by-play analysis and the same mania for trivia that accompanies a baseball telecast. Coverage would begin an hour or more ahead, complete with color commentary from retired astronauts and scientists. As with other sports, they could analyze each team member's "stats" —number of missions, EVAs, total hours in space, etc. We could even compare them with their Russian counterparts. Can astronaut trading cards and NASA jerseys be far behind?

Rather than the bland, content-free babble that accompanies most launches, we could get lively, knowledgeable science personalities like Stephen Jay Gould or Bill Nye (The Science Guy) to interview NASA scientists and get plain-English explanations of the experiments to be conducted during the mission. And I'll bet that most aerospace companies would jump to pay for producing and airing videos that would give people a better understanding of the technical wizardry inside the launch vehicle or spacecraft that they've built. What about a national call-in show segment? Once we have viewership, the possibilities are endless.

If we start now, we can still give our children a chance to dream. We probably can't spend any more money on space each year than we do now, but a well-managed program with a long-range plan and public support could accomplish much in the next few decades. So get those cards and letters off to Mr. Goldin today! I look forward to seeing my child (and yours!) take her first steps onto the red sands of Mars. Comments can be sent to *leeg@class.org*.

LEE GOLDBERG

20

## OVER 100,000 PARTS IN STOCK, OVER 275 MANUFACTURERS, OVER 80 OFFICES NATIONWIDE!

Allied Engineering Manual and Purchasing Guide

Multimedia Catalog on CD-ROM

24-Hour Modem Instant Access to Stock Inventory and Pricing: 1-800-433-5003

Same Day Shipment

On The Internet — Order Entry, Stock Inventory and Pricing: http://www.allied.avnet.com

# They're taking over the world.

Low Profile International

Transformed

## Industry standard pin to pin capability has just landed!

Signal's new Low Profile Transformers deliver all these additional benefits at no extra cost:

- Construction designed to meet VDE/IEC/UL/CSA

- Hermetically sealed for wave soldering processes

- Encapsulated design provides superior protection in harsh environments

- Rigid pin construction for easier board insertion

- Mounting holes for easier installation and greater shock/vibration resistance

- Improved electrical characteristics including regulation, temperature rise, efficiency, etc.

- Dielectric strength test 4000 VRMS Hipot

Add it all up and you simply won't find a low profile transformer that delivers all the benefits that Signal's does. Whether your product is designed for domestic or international markets, Signal's new low profile transformers deliver lower initial cost, lower installed cost and superior performance. Signal Transformer. Your competitive edge ... around the world.

Call us for our detailed product literature and complete specs today.

Signal Transformer Co., Inc. Insilco Technologies Group

500 Bayview Avenue Inwood, NY 11096-1792 Call: 516-239-5777 Fax: (24 hrs) 516-239-7208

## TECHNOLOGY NEWSLETTER

## Chip Speeds Genetic Studies With Its Gene-Scanning Ability

Genetic discoveries may arrive at a much more fufunctions pace thanks to a new technique that gathers clues about the functions of thousands of different genes all at once. Stanford University researchers use what's called a "GeneChip," which is a thumbnail-sized silicon chip designed to carry a neat array of up to 100,000 DNA fragments.

The researchers are labeling the thousands of genes that make up an organism with distinguishing DNA tags. These will serve as "molecular bar codes" that can be detected simultaneously using the GeneChip. The technique should hasten the process and reduce the cost of key research areas, such as disease diagnosis, basic biological research, and the hunt for new drugs to fight infections.

The actual GeneChip, developed by Affymetrix, Santa Clara, Calif., combines two powerful technologies—photolithography methods used in the semiconductor manufacturers to layer microscopic structures on small silicon chips, and standard DNA-making techniques perfected by genetic researchers. With the chip's bar-code reading capability, scientists will be able to figure out which genes are important for survival under particular environmental conditions or at a given moment in an organism's life.

One of its first applications will be to determine the function of the estimated 6000 genes that are in baker's yeast. The reason yeast was chosen because its the most complex organism whose entire genetic sequence is already known. For more information, contact Stanford's Medical Center at (415) 725-5374 or (415) 723-6912. *RE*

## Acoustic Methods Used To Identify Defective Heart Valves

Noney granted from a class-action lawsuit settled in 1994 was poured into a research project that now may wind up helping thousands of people. Studies at Lawrence Livermore National Laboratory, Livermore, Calif., along with other research institutions, have focused on using acoustic differences to identify which mechanical heart valves manufactured by Shiley Inc. are susceptible to failure.

The recurring problem with Shiley Inc.'s Bjork-Shiley Convexo-Concave heart valves are "single leg separations," which occur when one leg of the valve's outlet strut breaks free. When both legs break, the strut is said to fracture, a condition that causes the heart valve to lose control of blood flow to the heart. Consequently, the research, funded by Shiley through the lawsuit, is to detect, without surgery, such separations of the valves. As of November 1996, there were 596 reported fractures of these heart valves, which lead to death in about two of three cases. About 42,500 convexo-concave valves (marketed between 1979 and 1986) are estimated to be implanted in patients now living.

Livermore's research project is split into two parts. First, there's an underwater study of the sounds made by normal and separated values. Scientists are studying the sounds of the two valves in an echoless chamber to observe how the values sound apart from biological sounds, such as fluids, heart beats, or tissue.

The second part involves a "blind test" with approximately 40 people using audio recordings to identify the different valves. The recordings were made by placing a microphone on the subject's chest and then using a digital audio tape to record, over a threeminute span, the opening and closing sounds of their heart valves.

"Finding the opening sound caused by a single leg separation heart valve is somewhat like searching for a single violin string that is out of tune in an entire orchestra of sounds," says Jim Candy, project co-leader. "It requires sophisticated signal-processing techniques to extract this sound because it is deeply buried in the noise." So far, Livermore engineers have employed computer workstations to pore through nearly 13 billion bytes of heart-valve acoustic data, the equivalent of almost 11,000 novels. *RE*

## Hardware Vendors Can Develop Hot-Pluggable PCI Systems

ndependent hardware vendors (IHVs) can take advantage of the Hot Plug PCI development platform to build PCI cards that can be installed in backplanes without powering down the entire system. This type of system would include fault-tolerant servers that can't tolerate any down time. Such functionality was previously available in proprietary platforms.

The development platform lets the IHVs develop their PCI-based software drivers. Engineered by Compaq Computer Corp., Houston, Texas, the platform is being delivered simultaneously with the first draft of a specification to create an open standard for hot-plug PCI technology. The draft, called Hot Plug Replacement, has been submitted to the PCI Hot Plug workgroup for review. Follow-on standards, specifically the Hot PCI Upgrade and Hot PCI Expansion, will make it possible for users to upgrade existing PCI peripherals and drivers without having to power down their systems. For more information, contact Compaq at (800) OK-COMPAQ, or on the Internet at http://www.compaq.com. RN

23

T E C H N O L O G Y N E W S L E T T E R

## I<sub>2</sub>0 Systems, Peripherals, And Software Are Starting To Arrive

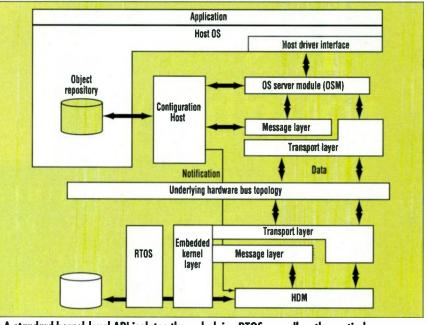

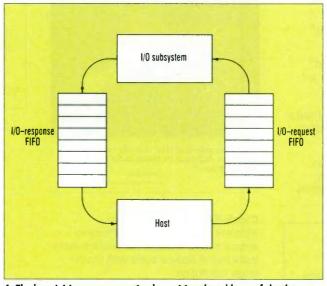

he Intelligent I/O (I<sub>2</sub>O) architecture improves I/O throughput and overall system performance by relieving host resources, such as the microprocessor, memory, and system bus, of interrupt-intensive tasks that cause data bottlenecks. Defined as a software layer, I<sub>2</sub>O also provides an open, standardsbased approach for intelligent I/O subsystems.

Systems based on  $I_2O$  now are starting to appear on the market. Recently, vendors participated in a demonstration sponsored by the  $I_2O$  Special Interest Group (SIG) to show their compatible products. The products included servers developed by Compaq and Hewlett-Packard; networking and storage devices from Adaptec, 3Com, and Symbios Logic; and operating systems from Microsoft, Novell, and SCO. Most of the products on display will be available in the early part of this year. For more information about  $I_2O$ , contact the SIG at (415) 750-8352 or on the Internet at http://www.i2osig.org. *RN*

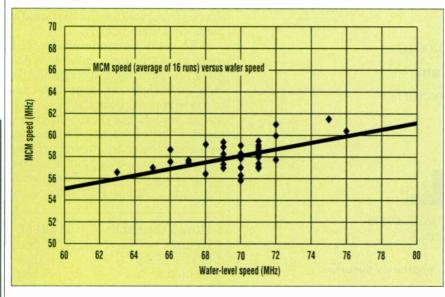

## New Class Of Polymer To Boost Low-Cost MCM Manufacture

A new class of packaging materials derived from polymers of cyclic olefins is being developed by the low-cost MCM research area of Georgia Tech. According to Dr. Paul A. Kohl and Dr. Sue Ann Bidstrup, both faculty members of the School of Chemical Engineering, the unique properties of these polymers are characterized by; a Tg (glass transition temperature) greater than 350°C, dielectric constant of less than 2.4 to 2.6, low moisture absorption of 0.1 %, and good ductility.

The materials were modified to have excellent adhesion to commonly used materials such as silica and aluminum, while also fusing well with copper and noble metals like gold and silver. The polymers require no adhesion promoter or adhesion layer such as titanium, tantalum, or chromium, and they do remain as adherent films even after being placed in boiling water for two hours.

Sponsored by BF Goodrich and conducted by Bidstrup and a group of graduate students, the results of the research are expected to "demonstrate utility in both semiconductors and packaging by offering superior performance over traditional materials, while reducing manufacturing cost," says Kohl. Contact Dr. Paul A. Kohl at (404) 894-2893 or paul.kohl@che.gatech.edu; or Dr. Sue Ann Bidstrup at (404) 894-2872 or sue.allen@che.gatech.edu. *PM*

## All-Silicon System Processes Light As Well As Electricity

• or the first time, engineers were able to integrate a porous silicon LED into conventional microelectronic circuitry, making possible an all-silicon system that can process light and electricity. A team of engineers from the University of Rochester and the Rochester Institute of Technology (RIT), both from N.Y., achieved this milestone by creating a sturdier form of porous silicon that can withstand the rigors of today's manufacturing environment. It's the first time that silicon was used for both the electronic and optical components on a single chip. Consequently, this eliminates the need for other materials or special processes during fabrication.

Of course, silicon has become synonymous with much of the electronics industry (read: Silicon Valley). But, as is also well known, it does have one major flaw—it emits light rather feebly. This flaw has magnified of late as scientists turn to light to carry the increasing amount of digital data traveling worldwide. To meet such a demand, companies have laid miles upon miles of fiber-optic cable because it transmits significantly more information cleaner and faster than electricity.

To provide these optical capabilities, engineers have turned to gallium arsenide or organic polymers, but they're costlier and/or extremely fragile. When porous silicon arrived on the scene in 1990, there was much anticipation because it could emit light. However, the porosity was too fragile to withstand conventional manufacturing techniques, rendering virtually useless to the electronics industry.

The Rochester team finally was able to strengthen the material by removing hydrogen atoms from the outer layer of tiny silicon nano-particles less than 100 Å wide—about one-thousandth the width of a human hair. They replaced the hydrogen with a double layer of silicon oxide to create a modified form of porous silicon known as silicon-rich silicon oxide. With these steps, the material, which is about three-quarters air and only one-quarter silicon, can withstand temperatures of 900°C, which is typically reached in the fabrication process.

The group holds the record for the most stable porous silicon LED. They were able to power the device for 11 straight days before stopping the experiment. Its brightness was about 1 mW per square centimeter and could flash up to 10 million times per second.

According to Philippe Fauchet, leader of the group, more improvements are needed before porous silicon becomes a standard material. For instance, researchers are looking to boost the efficiency 10-fold (to 1%), and increase frequency 100-fold, to one billion flashes per second. *RE*

24

## The C.A.N. Transceiver Everybody Likes

## ...From The Linear IC Company Everybody Follows

Device networks just got better with our new **UC5350** C.A.N. compatible transceiver. Everybody likes this rugged plug and play network solution because it saves money, reduces design time, increases production

line reliability and minimizes down time. With the UC5350, cross-wiring and loss of ground device faults will no longer destroy costly systems, causing extended line down situations. And no other C.A.N. transceiver meets the industrial node protection standards while minimizing per node propagation delay and signal loading. You can't afford not to update your network, and the new UC5350 makes automating more affordable than ever before.

For free samples and application information call today!

The UC5350 Advantage

- ISO 11898, SDS, DeviceNet Compatible

- Cross Wire Protection

- Loss of Ground Protection

- 50nS Propagation Delay Maximum

- 30kohm Minimum Input Impedance

TEL: (603) 429-8610

http://www.unitrode.com • FAX: (603) 424-3460 7 Continental Boulevard • Merrimack, NH 03054

# Micropower 12-Bit A/D for Portable Applications

LIGHT

Introducing the new SP8538, 12-bit ADC that redefines price/performance leadership in the micropower range. It delivers dynamic performance of The SP8538 in an 8-pin NSOIC package is ideally suited for Battery-Operated Systems, Portable Data Acquisition Instrumentation, and Remote Sensing.

If your application calls for best-in-class performance at micropower, you need to select an IC

from SIPEX's broad line of 12 Bit A/D and D/A

converters. For data sheets and technical information.

contact SIPEX at the number or web site

listed below.

| Benefits            | Sipex             | Linear Tech         | Condition                          |

|---------------------|-------------------|---------------------|------------------------------------|

| Cost                | \$4.20            | \$5 20              | @1k qily                           |

| Power               | 0.56mW            | 2.2mW               | @5v and 90µs                       |

| Complete Cycle Time | 40µs              | 90µs                | @5v                                |

| Inputs              | True Differential | Pseudo Differential |                                    |

| Linearity           | 1 LSB             | 2 LSB               |                                    |

| Crosstalk           | -120dB            | -66dB               | CH1 = 1MHz sqr<br>wave, CH0 = 4.5v |

SP8538 is a direct replacement for (Linear Tech) LTC 1298.

73dB Signal to Noise Ratio at a mere 1.25mW. Plus, the simple 3-wire SPI serial interface works easily with a wide range of microprocessors and microcontrollers. Noisy environments? The SP8538 with its "True" differential inputs and a Common Mode Noise Rejection (CMR) of 110dB @ 60Hz is the solution to your problem.

22 Linnell Circle, Billerica, MA 01821 Tel. 508-667-8700 Fax 508-670-9001 web site: www.sipex.com

## Low-Standby-Power SRAM Cell Promises High-Density Memories

esearchers at Texas Instruments Inc., Dallas, have devised an advanced memory cell that reduces the standby power of static-RAM memory cells used in III/V- or siliconbased circuits. The development promises to allow much higher levels of integration for high-speed circuits. The advanced memory cell consumes a record low 50 nA of standby current (almost 100 times less than currently achieved). Although initially fabricated on an indium-phosphide (InP) substrate, the same approach, according to the researchers, will be readily transferable to gallium-arsenide (GaAs) technology, since the materials have similar characteristics.

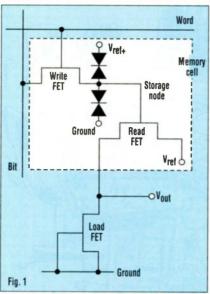

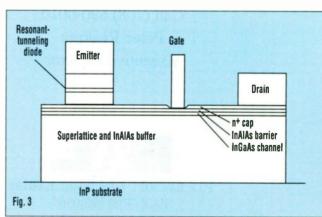

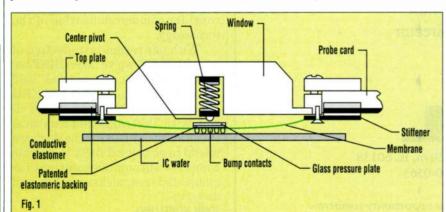

Described at last December's International Electron Devices Meeting (IEDM) in San Francisco, Calif., the cell, referred to as a tunneling-based SRAM, combines two heterostructure field-effect transistors-a read FET and a write FET-and two resonant-tunneling diodes (Fig. 1). The low-current-density resonant-tunneling diodes are used in a latch configuration to create two stable voltage levels in the storage node. The diodes are connected to the gate of an HFET, which can easily drive the bit line while not disturbing the storage node. When the word line is low (the cell is not selected), the gate leakage of either the write-HFET or the read-HFET steers the storage node voltage either low or high, depending on which of these currents is larger.

A simple static ram cell with ultra-low standby power can be created with just two heterostructure FETs and two resonanttunneling diodes.

The resonant-tunneling-diode latch can maintain two stable storage node voltage levels as long as the diode peak current is larger than the HFET leakage currents plus a diode valley current. This structure keeps the leakage currents to less than 100 nA for the read HFET device with a gate area of 50 by  $0.5 \,\mu\text{m}^2$ , and less than 10 nA for the 5-by-1- $\mu\text{m}^2$  gate write HFET (-2 V< V<sub>GS</sub> <0 V, and V<sub>DS</sub> <1 V). Additionally, the diode currents hit peak values of just over 150 nA.

Although the initial cell structure

provides two states (1 bit), a threestate version of the cell also can be implemented by increasing the number of vertically-integrated resonant-tunneling diodes. This arrangement allows the designer to achieve even higher storage densities. The same techniques can be applied in any materials system in which low-currentdensity, negative-differential-resistance devices can be fabricated. Assuming that such devices can be fabricated in silicon, the addition of two resonant-tunneling diodes to a DRAM cell converts the cell into an SRAM cell. That, in turn, can dramatically reduce the power waste associated with the refresh operation-a problem that is looming as chip densities approach the gigabit domain.

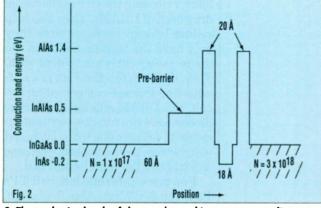

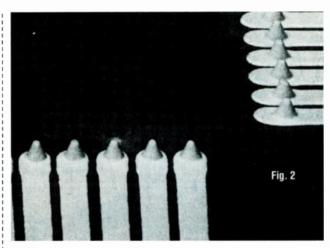

The resonant-tunneling diodes form the heart of the low-power memory cells, and are the critical elements that must be fabricated. To build the structures, TI's designers incorporated pseudomorphic aluminum-arsenide (AlAs) barriers, an indium-arsenide (InAs) well, and an indium-aluminum-arsenide (InAlAs) thin pre-barrier for current reduction (*Fig. 2*). The peak current density depends exponentially on the pre-barrier thickness.

To fabricate the cell, TI's designers crafted a new process that allows them to monolithically form both the HFETs and the diode structures in the indium-gallium-arsenide/indiumaluminum-arsenide (InGaAs/InAlAs) materials on top of an InP substrate (*Fig. 3*). The process also incorporates various improvements over previous processes that reduce, by an order of magnitude, the HFET gate leakage

3. The combined HFET and RTD structures are formed on the surface of a superlattice and buffer layer of InAlAs deposited on an InP substrate.

27

We look for church organists

Turn your excess inventory into a substantial tax break and help send needy kids to college as well.

Call for your free guide to learn how donating your slow moving inventory can mean a generous tax write off for your company.

> Call (708) 690-0010 **Peter Roskam Executive Director**

FAX (708) 690-0565

Excess inventory today...student opportunity tomorrow

## **TECH BREAKTHROUGH** SRAM CELL

current, setting a new low.

For high uniformity, selective etches are performed to create the diode mesas as well as the HFET channel recesses. Non-alloyed contacts-TiPtAu and InP etch-stop layers-provide a uniform, reproducible, and low-leakage process.

When applying this concept to DRAM cells, most of the attention is focused on reducing power during refreshing since the cells already have a low intrinsic leakage current. During refreshing, most of the power is consumed by the charging/discharging of the bit lines, and by the small percentage of cells that end up with the worst-case leakage-current variances. Additionally, the refresh operations must be able to function at 85°C.

The conceptual DRAM cell combines a standard single-transistor storage cell, plus the resonant-tunneling-diode latch connected at the same point as the storage capacitor. To function, the diodes must have extremely low current densities. However, silicon resonant-tunneling diodes do not yet exist, although research at TI into such structures is currently underway. Both the read and write operations execute exactly the same as the read and write in the standard DRAM cells. The difference lies in the storage function. A resonant-tunneling-diode latch has two stable voltage points, and as long as its peak current is larger than the total leakage current of the storage node plus the resonant-tunnelingdiode valley current, the diodes will hold the storage node close to one of the two stable points.

The resonant-tunneling diodes provide a local continuous refresh capability, removing the charge/discharge drawback of DRAMs. They also help reduce leakage currents since they only have the storage node and the diode valley currents to deal with. Thus, the latch functions act as a selfadjusting leakage-compensating circuit. But DRAM cells based on these diodes have drawbacks-a slight increase in cell area due to the latch, and a slight increase in complexity because an extra bias line must be provided.

For more information, call TI's Paul van der Wagt, Alan Seabaugh, or Ed Beam II at (972) 995-2011.

Dave Bursky

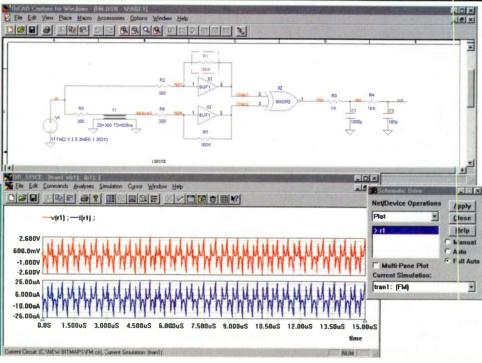

**Designers** set standards for excellence in our most critical industries. Often, lives and livelihoods depend on the circuits you design. Your goal: design better circuits faster. Since our inception, MicroSim has been setting the standards for desktop EDA systems that enable you to do just that. Try our evaluation software. See how MicroSim can help you set tomorrow's standards.

Contact MicroSim at 1.800.245.3022 or 714.770.3022

You can visit our Web site: http://www.microsim.com or call our faxback number: 714.454.3296 E-mail: sales@microsim.com

MicroSim is a registered trademark of MicroSim Corporation. All other brand or product nomes are registered trademarks of their respective houses. ©1996, MicroSine Corporation. All rights reserved.

# 33V ISP PLD Performance Breakthrough!

ispLSI 2032V 7.5ns 32 I/O 32 macrocells

unununununu

attice

ispLSI 2096V 10ns 96 I/O 96 macrocells

ispLSI 2064V 7.5ns 32 or 64 I/O 64 macrocells ispLSI 2128V 10ns 64 or 128 I/O 128 macrocells

## Design true 3.3V systems without compromise.

Smash the 3.3V high-density PLD speed barrier with Lattice's new in-system programmable ispLSI\* 2000V Family—the first 3.3V programmable logic devices to deliver 5V performance. Featuring logic densities from 32 to 128 macrocells and I/O options from 32 to 128 pins, this new family gives you all the logic options you need to design 3.3V systems with breakaway speed.

All ispLSI 2000V devices are available in space saving thin quad flat pack (TQFP) packages that maximize PCB space. And every ispLSI 2000V device is in-system programmable using only a 3.3V power supply—an industry first! So manufacturing with high-density ispLSI devices saves you both time and money.

Give yourself a break and come up to speed with ispLSI 2000V PLDs. Call us today at **1-888-ISP-PLDS** and ask for information packet 331 or check out our web site at www.latticesemi.com.

The Leader in ISP<sup>™</sup> PLDs

Copyright ©1997, Lattice Semiconductor Corp. ispLSI is a registered trademark of Lattice Semiconductor (Sorp. ISP is a trademark of Lattice Semiconductor Corp. Al' brand or product names are trademarks or registered trademarks of their respective holders.

Corruorate Headquarters: Tel: (503) 681-0118, Fax: (503) 681-3037 • France: Tel: (35) \* 69 33 22 77, Fax: (33) 1 60 19 05 21 • Germany: Tel: (49] 089-317-87-810 Fax: (49) 089-317-87-830 • Hong Kong: Tel: (852) 2319-2329, Fax: (852) 2319-2750 • Japan: Tel: (81) 3-5822-3533, Fax: (81) 3-5822-3531 • Korea: Tel: (822) 583-6783, Fax: (822) 583-6788 • Taiwan: Tel: (8862) 577-4352, Fax: (8862) 577-0260 • United Kingdom: Tel: (44) 1932 831180, Fax: (44) 1932 831181

# **TECHNOLOGY INSIGHTS**

Exploring power-management design issues for advanced microprocessors

## **Advanced Microprocessors Demand Amperes Of Current At <2 V**

Switching-Regulator Controllers Drive Power MOSFETs To Provide Regulated Power For Advanced Microprocessors At 1.3 To 3.5 V.

## Frank Goodenough

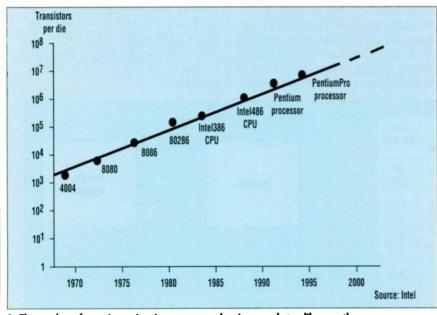

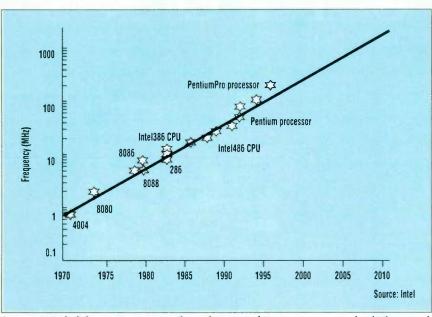

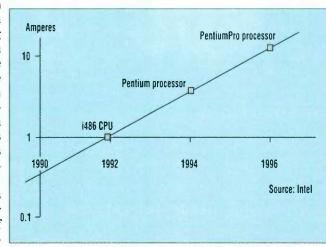

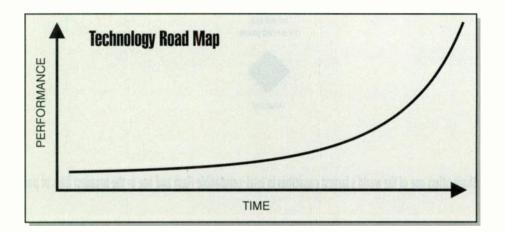

ate lengths for CMOS FETs in advanced microprocessors have shrunk rapidly in the last two years. This trend has followed the roadmap drawn by the Semiconductor Industry Association (SIA) for semiconductor device growth. Coupled with the demand for lower power, supply rails have dropped. Cutting supply voltages cuts the loss factor V (volts) in the equation:

$P = 1/2f CV^2$ where P = power dissipation f = frequency (clock te)

$^{7} = voltage$

oth the f and the iber of FETs per cessor, as well as the supply currents. keep climbing at similarly fast rates. That is, power does not usually fall. The extra FETs use more current while enabling

the processor to perform additional sophisti- Courtesy: cated functions.

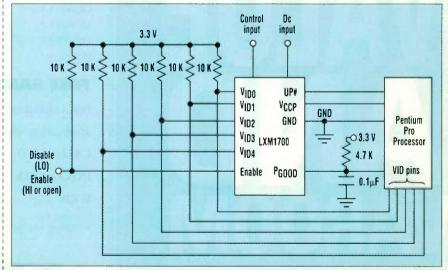

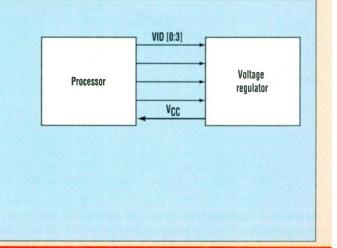

Complicating matters further at the system design level, Intel, since it introduced the Pentium, has let each microprocessor determine its own supply voltage. The P-6 Pentium Pro has four pins, each of which is either open or shorted. They represent a 4-bit code that calls out the supply voltage required by the processor in 100mV steps between 2.1 and 3.5 V. The supply must read the code and provide the required voltage. Five-bit codes are on the way in nextgeneration processors.

Temic Semiconductor

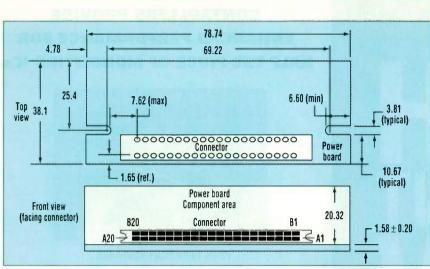

To make the task of the system designer a little simpler, Intel has defined a family of standard plug-in supplies for their processors called voltage regulator modules (VRMs). The VRM reads the code and sets the output voltage (see "VRMs: Technological First Aid, But For How Long?" p. 44). Each processor type (P54/P55/P-6) has its own unique standard plug. The standard plug for

> the VRM goes on the PC's motherboard. If the processor has been changed and now demands a different supply voltage, only the VRM is changed, not the motherboard. Power-supply companies and several semiconductor companies are building VRMs. A number of semiconductor suppliers (including those building VRMs) are building some of the active semiconductor guts for VRMs and motherboard-based power

supplies. Supplies for these processors must regulate line and load voltages to within ±5%, and hold their accuracy specifications over time. temperature, and load transients.

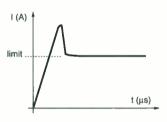

The supplies also must continue to meet their specifications while handling these ultra-fast transients produced when, in order to save power, most of the microprocessor's FETs are repeatedly turned off and on by software. One example of that situation is word-processing software that disables FETs between key strokes. Often, the supply must pull its output into regulation within a few clock cycles at rates

21

SPECIAL

REPORT

TECH INSIGHTS

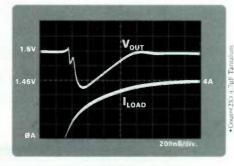

approaching more than 500 MHz. The latest Pentiums demand that the supply provide 5 A of current in 20 ns. However, the basic specification most supplies are designed to meet states that the output must hold within  $\pm 5\%$  of the specified value over time, the environment, and transients.

Some split-plane processors are powered by two separate supply voltages. The logic and I/O run off 3.3 V, and the processor core runs off less than 3 V. Besides the Intel processor family, there are upcoming genrations of Sparc, Alpha, PowerPC, the AMD/NextGen machine, the MIPS-R server, and devices

from Cyrix that have this arrangement.

Although designers are busy adding power-hungry bells and whistles to their systems, maximum efficiency is demanded at both low- and full-load conditions. The supplies have generated a succession of moving target challenges for analog IC designers who have come up with many different architectures to meet

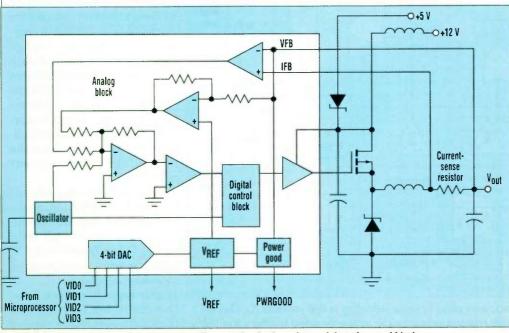

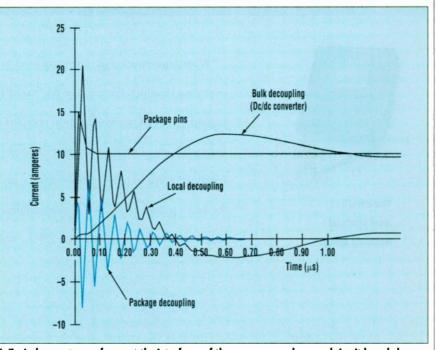

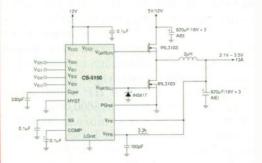

sides the Intel processor 1. A proprietary circuit technique in Cherry Semiconductor's controllers family, there are upcoming uses the voltage dropped across a switcher's load-capacitor's ESR by genrations of Sparc, Alpha, current flowing into the capacitors to handle severe load transients by powerPC, the putting the output in a 0 or 100% duty cycle mode. The V<sup>2</sup> technique AMD/NextGen machine, the does not depend on the gain-bandwidth product of the error amplifier.

these challenges.

#### **Science Fiction**

Expect one day to see processors demanding over 100 A of current. Within the near future, 50 A or more will be common. Some Intel processors will soon demand 17 A at less than 2 V. Four of them in a server will call for close to 70 A. At 100 A, a  $1-m\Omega$  copper trace on a pc board

| Processor             | Clock Rate (MHz) | Current<br>(core) (A) | Supply<br>voltage(s) (V)                                                   | Code (bits)   |

|-----------------------|------------------|-----------------------|----------------------------------------------------------------------------|---------------|

| P-54 Pentium          | 60/200           | . 4                   | 3.5 to 3.525                                                               | None          |

| P-55 Pentium          | 150/250          | 5.7                   | Split plane<br>(2.8 for core,<br>3.3 for I/O)                              | None          |

| P-6 Pentium Pro       | 150/200          | 12.4                  | Split plane<br>(2.1 to 3.5<br>in 100-mV steps<br>for core,<br>3.3 for I/O) | 4             |

| P-6 Klamath           | 200/500          | 14                    | Split plane<br>(1.8 to 3.5<br>in 100-mV steps<br>for core,<br>3.3 for I/O) | 5             |

| P-7                   | Not available    | 17                    | Not available                                                              | Not available |

| AMD K5                | Not available    | 4                     | 2.38 to 3.6                                                                | None          |

| PowerPC               | Not available    | 3                     | 3.6                                                                        | None          |

| Cyrix<br>Cx486DX2-V80 | Not available    | 2                     | 4                                                                          | None          |

| Nexgen NX586          | Not available    | 7                     | 4 ±3%                                                                      | None          |

| AMD DXL2,<br>DXL4     | 75/100<br>66/80  | 3                     | 3.3                                                                        | None          |

drops 100 mV and dissipates 10 W. A 100-mV drop, even from a 5-V rail, is not significant. But from a 1-V rail, where it's 10% of the voltage, it will be significant. The pc board and copper trace may handle that power, but can the system? A look at the power requirements of some of the past. present, and near-future processors represents a possible baseline from which to make projections for the f ture (see the table).

It's easy to come up with numbers like >70 A. Put more than two million CMOS FETs on a chip and assume each FET pair nominally switches 50 µA. That's a total of 100 A—procesors

have been built with five times that many FETs. If supplies for such processors are putting out less than 1.5 V, then holding ±5% regulation means holding the output voltage within ±50 mV. That's a significantly tighter specification than the  $\pm 250$ mV required by a 5-V ±5% rail. Some supplies (regardless of the architectures they use), handle the transient specification by letting the output swing its full ±5% for the transient. and holding the basic dc value of the output an order of magnitude cle This arrangement requires that regulator circuit sport a very l open-loop gain and a very stablternal dc reference. Performa sponse.

#### **Change The Silver Boxes**

There are several ways to get well-regulated voltages below 5 V, at relatively high currents, for systems running off the ac line such as desktop PCs and servers. The obvious way of redesigning the silver box so it converts the ac line voltage to dc voltages below 5 V has not appeared, yet. There are several reasons for this. First, systems have not moved completely to voltages below 5 V. Second, disk drives and other peripherals still need more than 5 V. Third, no sub-5-V standard exists. Additionally, given the SIA roadmap and the advanced processors showing up

this report.

**TECH INSIGHTS**

#### **ADVANCED-PROCESSOR SUPPLIES**

on the market, few off-line-to-highcurrent sub-3.3-V supplies will appear soon. The voltage is a moving target, consequently the power supply industry saw no reason to come up with new silver boxes.

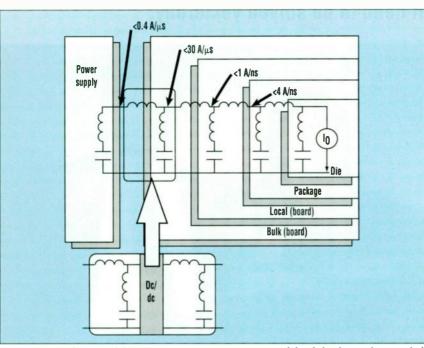

Rather, system designers took advantage of the already well-regulated 5- and 12-V rails, using linear regulators and switchers to convert them to voltages below 5 V. Most of the time, they used the existing highcurrent 5-V rail as a power-distribution bus, albeit a very inefficient one. If a system needs 10 A at 3.3 V, that translates to over 6 A at 5 V, and 100 A at 1.5 V still translates to 30 A at 5 V. As noted earlier, at those kinds of currents, voltage drops and power losses along the bus can be significant.

The industry has not implemented efficient distributed power in PCs and PC-based systems, despite the fact that mainframes and other large systems have been using distributed power for years. In fact, some mainframes distribute over 300 V.

For example, PCs could distribute the telecommunication industry's 48 V, 24 V, or even 12 V (100 A at 1 V

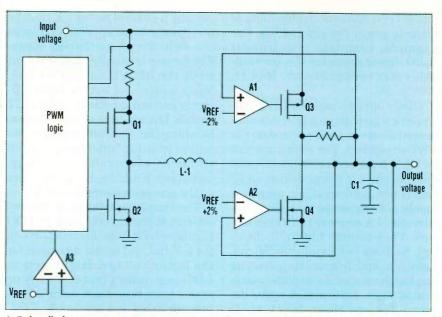

3. To handle fast transients, Maxim added a complementary half-bridge circuit (built from Q1 and Q2) to their controllers. When the output differs from the reference by more than 2%, gain blocks A1 and A2 turn on the upper or lower FET in the half-bridge circuit. The FET will either dump current into the the load capacitor or take current from of the load capacitor to ground.

translates to just under 2 A at 48 V or less than 4 A at 24 V). Since they have 12 V available for disk drives, some PC-based systems distribute it to low-power applications, and/or run

power-management circuits such as switcing regulators off the regulated 12-V rail. Many of the available solutions can run off 5- or 12-V rails.

However, a move toward a stan-

dard distributed power bus would have taken cooperation between system, power-supply, IC, and power-switch designers. In such a system of distributed power, the silver box would put out one or more well-regulated dc voltages for distributuion. Similar to current circuits that convert 5-V rails to 3.3 V or lower, at each major point of use an efficient buck regulator converts the distributed voltage to the required voltage. Very low-current, or higher-voltage applications (but lower than the bus voltage), can use linear regulators.

Assuming the use of a 5-V rail for power distribution, a system designer can draw on either of two basic circuit techniques to get from 5 to 3.3 V, or lower voltages—linear or switching regulators.

Linear regulators tend to be less costly, but less efficient than switchers. Each type of regulator can be partitioned

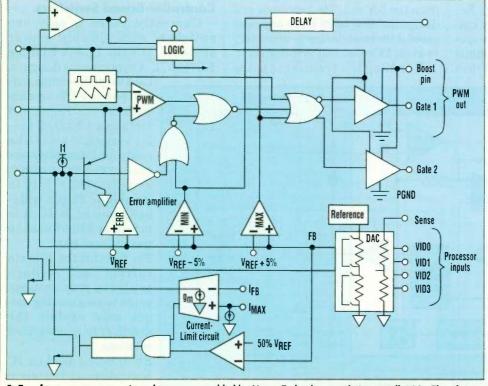

2. Two fast comparators, min and max, were added by Linear Technology to their controller ICs. They fire when the feedback voltage exceeds the reference voltage by 2%, putting the output in either a 0 or 100% duty cycle mode. The technique does not depend on the gain-bandwidth product of the error amplifier.

ELECTRONIC DESIGN / JANUARY 20, 1997

#### **TECH INSIGHTS**

into several different combinations of discrete power devices and ICs. For example, complete low-dropout (LDO) linear regulator ICs are available (*ELECTRONIC DESIGN*, May 13, 1996, p. 65).

Other options include LDO controllers which drive a follower-connected discrete power transistor (a FET or bipolar). The circuit also can be built from scratch with ICs and discrete parts (a power device, an IC reference, and an IC op amp.). A number of companies now offer highcurrent (7 A or more) LDO regulators. They include Linear Technology, National Semiconductor, Micrel, Semtech, and Telcom. However, no one has developed a completely integrated, high-current, high-speed device. Telcom does label their TCL1584 through TCL1587 series of regulators rated at 7 to 3 A as "fast response," but no transient response specifications are provided.

#### Low-Cost Power

Most switching regulators are built with IC controllers and discrete power switches which tend to be power FETs. In addition, a few devices are available with the power switches on the controller chip. Regardless of the approach, they employ either synchronous or non-synchronous designs. Synchronous designs use two power switches (usually n-channel power FETs). The non-synchronous approach replaces one switch with a Schottky diode. The former is usually more efficient while the latter is usually cheaper. Many designs use both to boost efficiency and reduce stress on the FET switch. Irrespective of the solution, handling the transients usually requires locating hundreds, or even thousands of microfarads of bulky, costly, low-ESR/low-ESL capacitors on the processor's supply pin(s).

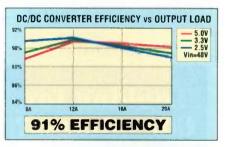

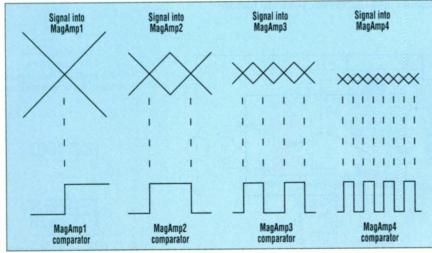

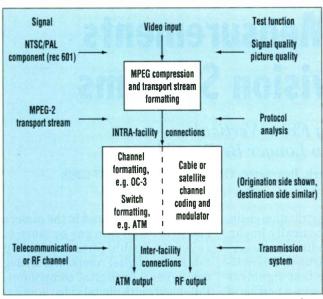

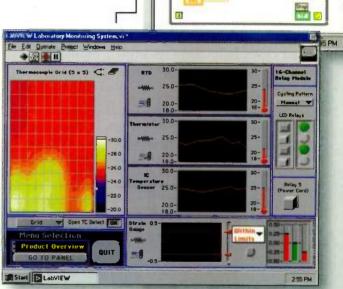

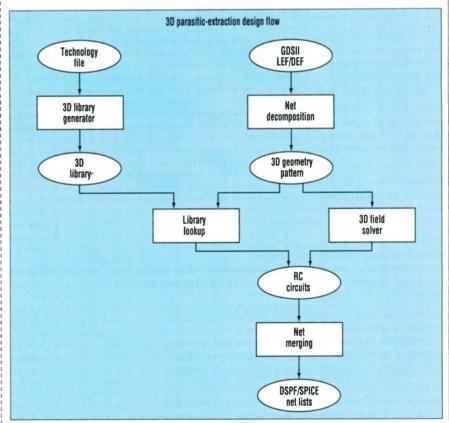

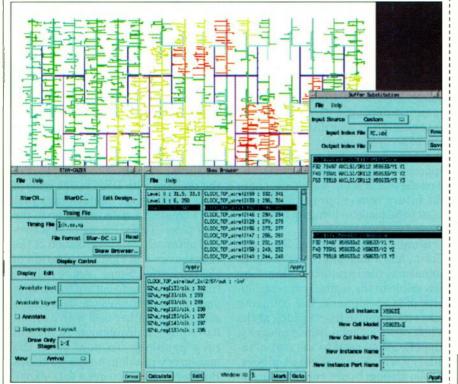

The simplest, and usually the lowest-cost approach, is to hang an LDO regulator built from discrete parts on the 5-V rail, and adjust its output for the lower voltage. High-current LDO regulators (rated at 1 A or more) have been built using a lowcurrent (rated at a few hundred milliamperes) LDO regulator as a controller driving a pnp transistor. But, like most supplies for the high-speed processors, these regulators have trouble handling the transients.