## **Redefining Distribution** Thru Superior Service

Your Ultimate Source For Quality Electronic Components! #1 for Availability of Product #1 for On-Time Delivery #1 for Overall Performance

QUALITY SYSTEMS

Call, write, fax or visit our web site for your FREE CATALOG today!

1-800-344-4539

Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MM 56701 • Fax: 218-681-3380 • http://www.digikey.com

READER SERVICE 84

# 33V ISP PLD Performance Breakthrough!

ispLSI 2032V 7.5ns 32 I/O 32 macrocells

In the second second

inninni

ispLSI 2096V 10ns 96 I/O 96 macrocells

ispLSI 2064V 7.5ns 32 or 64 I/O 64 macrocells

nannannannannannanna

Million Million

ispLSI 2128V 10ns 64 or 128 1/0 128 macrocells

## Design true 3.3V systems without compromise.

Smash the 3.3V high-density PLD speed barrier with Lattice's new in-system programmable ispLSI® 2000V Family—the first 3.3V programmable logic devices to deliver 5V performance. Featuring logic densities from 32 to 128 macrocells and I/O options from 32 to 128 pins, this new family gives you all the logic options you need to design 3.3V systems with breakaway speed.

All ispLSI 2000V devices are available in space saving thin quad flat pack (TQFP) packages that maximize PCB space. And every ispLSI 2000V device is in-system programmable using only a 3.3V power supply—an industry first! So manufacturing with high-density ispLSI devices saves you both time and money.

Give yourself a break and come up to speed with ispLSI 2000V PLDs. Call us today at **1-888-ISP-PLDS** and ask for information packet 331 or check out our web site at www.latticesemi.com.

The Leader in ISP<sup>™</sup> PLDs

Copyright @1997, Lattice Semiconductor Corp. ispLSI is a registered trademark of Lattice Semiconductor Corp. ISP is a trademark of Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders.

Corporate Headquarters: Tel: (503) 6H1-0118, Fax: (503) 681-3037 • France: Tel: (33) 1 69 33 22 77, Fax: (33) 1 60 19 05 21 • Germany: Tel: (49) 089-317-87-810, Fax: (49) 089-317-87 830 • Hong Kong: Tel: (852) 2319-2929, Fax: (852) 2319-2750 • Japan: Tel: (81) 3-5820-3533, Fax: (81) 3-5820-3533 • Korea: Tel: (822) 583-6783, Fax: (822) 583-6788 • Taiwan: Tel: (8#62) 577-4352, Fax: (8862) 577-0260 • United Kingdom: Tel: (44) 1932 831180 From jet planes to Chunnel trains, QNX goes the distance: testing turbines, loading cargo, even controlling air traffic. QNX helps healthcare applications run faster, and cost less, thanks to its executive-class speed and full x86 support.

### The QNX realtime operating system is

With its tiny, full-featured Internet suite, QNX helps web-transaction appliances do big business.

From traffic control to process control, QNX drives thousands of mission-critical applications nonstop, 24 hours a day.

#### So many applications. So many demands. How does QNX do it?

Start with rock-solid OS technology field-tested for over 15 years. Add in innovative products like the award-winning Photon microGUI<sup>™</sup>, QNX's embeddable windowing system. Provide a rich, robust toolset so developers hit the ground running. And keep the memory footprint exceptionally small to ensure runtime costs stay exceptionally low.

Most important, make it all fully scalable. So developers can deliver everything from web phones to factory-wide control systems—using a single OS. It all adds up to

Using a QNX-based vision system, shuttle astronauts stay focused on important things. Like launching satellites.

QNX serves up reliable service at the point of sale, whether it's handling fast-food orders or checking credit cards.

## found in these worldwide locations

When safety is measured in microseconds, nuclear power stations count on QNX: it's a *real* realtime OS.

Thanks to QNX, the web is coming to your living room faster than you can say "URL."

### www.qnx.com call 800 676-0566 ext. 2242

#### Available Now:

internet toolkit embeddable GUI & browser POSIX and Win32 APIs embedded filesystems memory protection fault-tolerant networking distributed processing multilingual support unrivalled x86 support embedded OEM pricing

QNX Software Systems Ltd., Voice: 613 591-0931 Fax: 613 591-3579 Email: info@qnx.com Outside North America: Voice: (44)(0)1923 284800 or 613 591-0931 Fax: (44)(0)1923 285868 Email: QNXeurope@qnx.com © QRX Software Systems Ltd. 1997 QNX is a registered trademark and Photon microGUI is a trademark of QNX Software Systems Ltd. All other trademarks belong to their respective owners:

READER SERVICE 94

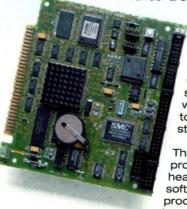

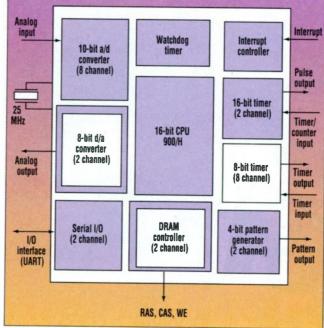

#### Palm-sized PC Microcontroller packs industrial I/O power with embedded PC control.

When a proven technological innovator emerges in any industry, it becomes the one to watch. Octagon Systems' new PC Microcontroller™ series blends I/O innovation with embedded PC control. The PC Microcontroller series not only provides a uniquely integrated hardware platform, but includes the industry's largest suite of embedded software in flash memory. You get the best of all

worlds-a single card industrial solution that you can adapt to hundreds of applications without the compatibility problems of multiple card variations. Each of the Octagon PC Microcontroller cards includes DOS 6.22, but will run under QNX as well as many other popular real-time operating systems. They also include CAMBASIC, Octagon's fast multitasking control language that supports all the I/O on the card-no drivers to write. Each 4.9"x 4.5" package is rated from -40° to 85°C, plugs into an ISA bus slot or operates stand-alone with a 5V supply.

| Octagor<br>Microcontrol          |                    |   |

|----------------------------------|--------------------|---|

| CPU<br>Parallel Port             | 40 MHz<br>IEEE1284 | l |

| Digital I/O                      | 17-65 lines        | ł |

| COM Ports<br>Analog I/O          | 2-4<br>Up to 10    |   |

| CAMBASIC                         | ~                  |   |

| Networking<br>Diagnostics        | ~                  | į |

| Flash File<br>DRAM Supplied      | 2 MB               | ł |

| Flash Supplied                   | 1 MB               | l |

| SRAM Supplied<br>Real Time Clock | 128K               |   |

| KBD/Speaker                      | V                  |   |

| Prices Start at                  | \$340/100s         |   |

The Octagon PC Microcontroller series. It's loaded with software.

There's no memory to buy. You don't need a professional programmer. And it eliminates the headaches of mixing and matching the CPU, I/O and software from different sources. It's an irresistible new product family from Octagon Systems-I.O. with I.Q!-the latest innovation in our sixteen year history of success.

#### **OCTAGON SYSTEMS®**

6510 West 91st Avenue Westminster, CO 80030 USA TEL: 303-430-1500 FAX: 303-426-8126 www.octa.com

"See us at the Embedded Systems East Conference, Booth #1404"

#### **Embedded Systems Features**

#### 9 **Tuned RISC Devices Deliver Top Performance**

The latest crop of 32-bit RISC processors integrate many functions needed to reduce embedded system costs.....By DAVE BURSKY

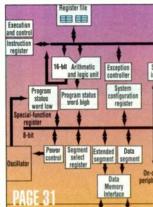

#### 16-bit Embedded Controllers Open New Markets 31

Higher levels of integration and throughput in the newest 16-bit MCUs help trim system cost ......By DAVE BURSKY

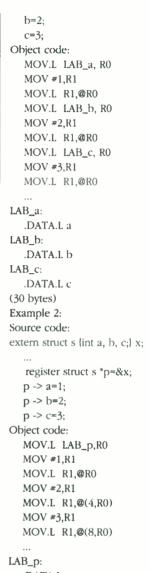

### 49 Coping with 32-bit code density

Compiler optimizations and programming techniques ease working with embedded 32-bit RISC microprocessors.....By YUGO KASHIWAGI

### 54 How to Mix RTOS with RISC And Come Out A Winner

Characteristics of RISC machines require special considerations in choosing a real-time operating system......By TOM BARRETT

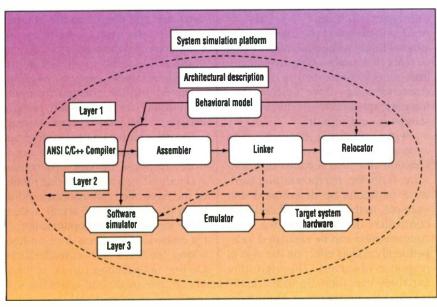

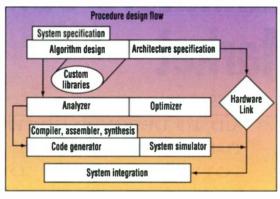

#### System Simulators Can Speed Time-To-Market 57

System designers have not taken full advantage of system or architectural simulators as design resources.....By NAVIN GOVIND

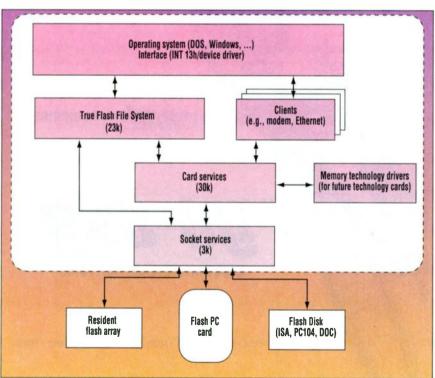

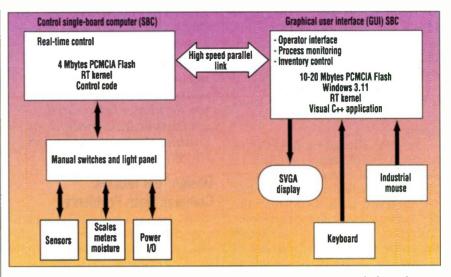

### 60 Embedded Process Control Gets Boost From Flash Card

Computer boards combine with flash-file system software and PC Cards to upgrade a control system.....By KENT TABOR & RAZ DAN

#### **Departments Editorial**

- **67 Products**

- **64** Advertisers Index

MARCH 3, 1997 • SUPPLEMENT TO ELECTRONIC DESIGN •5

## HE WORLD BECOMES A Smaller PLACE WITH EVERY PRODUCT YOU DESIGN.

19% NEC Eleptentin Ite

You have a remarkable power.

It is the power to bring people together, by allowing them to be farther apart. And it is a power that, while firmly grounded, is nothing less than nomadic in spirit.

#### Choose your embedded processor wisely.

PDAs are now reaching their full potential. And you have the power to make the world a smaller place. But can you really find an embedded processor that can keep up with the shrinking size of reality? The

answer, of course, is a resounding "yes." You need look no further than NEC's  $V_{\rm R}4100^{\rm ns}$  core technology as your solution of choice.

The V<sub>R</sub>4100 Series frees you from the constraints of time and space with a unique, customized "system on a chip," allowing you to create a more streamlined design and send it off to find its place in the world in record speed. And for the more pressing deadline, the V<sub>R</sub>4101 offers a built-in memory controller for up to 8Mb DRAM/ 16Mb MROM.

But is all that enough to change the world? When combined with full 64-bit performance (with a 32-bit interface) and more MIPS/mm<sup>2</sup> in a low-priced, small die size package, it is very possible indeed. Then, factor in low power consumption, on-board Multiply Accumulate Instruction, plus on-chip management features such as the ability to operate at 3.3 volts, and changing the world of PDAs is virtually assured.

In all, NEC offers significant performance, flexibility and serious power management features in a compact, affordable embedded processor. All of which offers you a chance to bring the world a little closer together.

For more information about the V<sub>R</sub>4100 Series, call 1-800-366-9782.

Ask for Info Pack #165. It's a small step to take for something that could go so far.

NEC's  $V_R$ 4100 processor is uniquely designed to power the next generation of PDA products.

READER SERVICE 103

#### **Editorial**

As electronics pervades our everyday lives, embedded microcontrollers are leading the way-they're all around us, in cellular telephones, in TV sets, in automobiles, in household appliances, in .... They're also pervading industry, where they are the front-line troops in the battle to automate processes and increase worker productivity. Of more importance in the context of Electronic Design and its readers, embedded microcontrollers

are causing a profound change in the way electronic systems are being designed.

Today, almost every design engineer comes face-to-face, in one way or another, with a microcontroller as part of a system under design. The growth of embedded microcontrollers has had another profound effect: The growth of software as a key element in most new

systems, as well as a key skill for EEs that is becoming much more in demand.

This Special Supplement, with its collection of recently published technical articles, focuses on both the hardware and the software elements of the design of embedded systems. Designing an embedded system requires many different types of components and tools, including microcontrollers and microprocessors, memory chips and memory management systems, software tools for development and debugging, real-time operating systems, and

others. The articles in this Supplement cover a wide range of topics, from overviews of RISC CPUs and 16-bit microcontrollers authored by the Electronic Design Editorial Staff, to detailed technical explanations authored by experts in industry-on topics such as programming techniques for 32-bit RISC microprocessors, the value of system simulation as a design resource, and the use of flash PC Cards in embedded process control sys-

> tems. Descriptions of several recently introduced products round out the article package presented here.

> This year, to continue our deep focus on this critical subject area, Electronic Design has established a new section: Embedded Software and Hardware, which will appear monthly throughout 1997. The new section will be managed by Electronic Design's Embedded

Systems/Software Editor, Tom Williams, who is based in our San Jose, Calif. office. The section will contain news and overview articles authored by Williams, technical articles, and a collection of the most important embedded systems-related products introduced each month.

This Special Supplement thus mirrors many elements of the Embedded Software and Hardware Sections. We hope you find it, as well as the upcoming Embedded Sections, useful references in the future.

> STEPHEN E. SCRUPSKI Editorial Director

"Embedded microcontrollers are causing a protound change in the way electronic systems are being designed."

## And some people

## still think Microtec

## is just a tools company.

JIM READY MICROTEC

Embedded Software Expert

68K, CPU32, x86, PowerPC,™ ColdFire,™ ARM and i960 Supporter

Confidant RTOS Guru Networking Expert Software Debugger Legacy Software Migrator Butt-Saver HW/SW Design Authority Telecom Specialist Partner JavaOS™Licensee C++ Wizard Windows® Developer

**Internet Enabler**

-

But we're so much more. Our complete line of products and services can differentiate your designs, add value, and get you to market faster. Products like Spectra', Microtec's fully integrated—yet remarkably open—embedded development environment. It includes VRTX', the industry's most powerful and proven RTOS, as well as our renowned XRAY' debugger and C/C++ compilers. Use them together, separately, or with your own choice of RTOS and tools.

> Or let us do it for you. Microtec offers a full range of consulting and professional services, so we can provide everything from off-the-shelf point products to completely integrated, turnkey solutions.

So if you're ready to slice serious time and money off your next development project, call Microtec at 1-800-950-5554, Dept. 320. Mention this ad, and we'll send you your own copy of the Embedded Software Expert badge.

Think of it as a little reminder from your total solutions company.

Microtec' www.mri.com

1977 Microte All rights mean call as the Microte Jogs, NRT3 and RAY and registered trademarks of Microtex, a Microtex Company All other hand a product names are the property of their respective outputs.

See us at the Embedded Systems Conference, Booth #1004 READER SERVICE 104 The latest crop of 32-bit RISC processors integrate many functions needed to trim embedded system costs.

\_\_\_\_\_

DAVE BURSKY WEST COAST EXECUTIVE EDITOR

## **Tuned RISC Devices Deliver Top Performance**

AS NEW SYSTEMS ARE BEING DESIGNED THAT RE-QUIRE MORE INTELLIGENCE, 8- AND 16-BIT CON-TROLLERS ARE GIVING WAY TO 32-BIT RISC PRO-CESSORS. BUT THE RELATIVELY HIGH COST OF first- and second-generation RISC processors has delayed their implementation into cost-sensitive applications such as consumer products, video games, and automotive systems.

But as designers start looking at total system cost rather than the cost of the CPU chip alone, the latest crop of highly-integrated 32-bit processors makes the use of 32-bit architectures more cost-effective than ever. The last year or two has also seen increasing interest in the "system-on-a-chip" approach offered by various ASIC and CPU suppliers. In this approach, designers start with the basic CPU core and add standard and custom megacells. This allows them to craft a processing solution optimized for the system and gives them a level of uniqueness that would be hard for a competitor to duplicate.

Designers can select from among many highly-integrated commodity offerings, or from various cell-based building blocks, which in total, provide a wide range of integration options and cost/performance trade-offs to meet almost any system requirement. The choice of 32-bit embedded controllers includes holdovers from the CISC world, as well as many new challengers based on RISC architectures. CISC choices, in the form of various implementations of the Intel 386/486 architecture, as well as versions of Motorola's 68000 processor, deliver throughputs between 5 and 15 MIPS. The biggest plus of these families is that they can leverage the extensive programming knowledge built up over the years as well as volumes of code libraries and the variety of low-cost software devel-

| R3000 core         | 1-kbyte data cache<br>1-kbyte instruction |                | Bus-interference  |

|--------------------|-------------------------------------------|----------------|-------------------|

|                    | and a set of the set of the set           | tegration unit |                   |

| interrupt module   | DN                                        | l arbiter      | Decoder module    |

| Power management m | odule                                     |                | Clock module      |

| Timer module       | ARTICLE                                   |                | I/O module        |

| Infrared module    | 1                                         | 1              | UART module       |

| Video module       |                                           | To             | uch Screen module |

| Sound module       |                                           | 0              | n-Chip Reference  |

**1.** ALMOST ALL THE functionality needed for a personal digital assistant is integrated into the PR30100 RISC processor developed by Philips. At the beart of the processor is a power-reduced version of the 32-bit R3000 core.

opment tools that run on PCs and Macintoshes. These processors will be covered in a future article.

In many cases even these CISC-based processors are rapidly giving way to the latest-generation RISC CPUs. These RISC CPUs have been optimized for high code efficiency, small chip areas, and much higher throughputs. And they're proliferating from two different roots. On one side, designers can select from familiar RISC processors that are extensions of families originally designed for desktop computers. On the other side, designers have available a wide choice of new RISC architectures designed from the ground up to tackle embedded applications.

MARCH 3, 1997 • SUPPLEMENT TO ELECTRONIC DESIGN •9

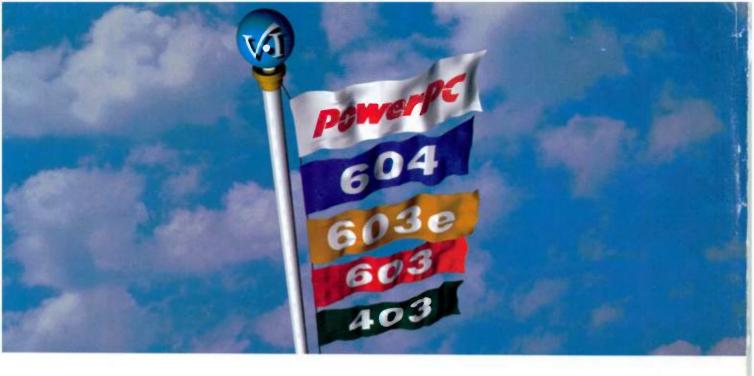

The "traditional" RISC options include the R2000/3000/4000 architectures from the MIPS Technology Division of Silicon Graphics, the SPARC architecture from Sun Microsystems, and the Power PC from IBM and Motorola. And, perhaps not as widely recognized, the PA-RISC architecture, licensed by Hewlett-Packard to OKI Semiconductor and Winbond Electronics, has also been reshaped by those licensees to provide a cost-effective solution for embedded applications. Similarly, the Alpha RISC processor family from Digital Equipment includes one family member targeted for embedded applications.

#### ARMS FROM THE UK

To a lesser extent, at least here in the U.S., the ARM processor did have desktop roots in its country of origin, the United Kingdom, where Advanced RISC Machines crafted the CPU for the Apricot family of personal computers. But in other regions of the world, most designers view the latest versions as designed from the ground up for embedded applications.

The ARM is now widely licensed to more than half-a-dozen companies that are producing "standard" CPU chips. These chips are aimed at designers who want either an off-theshelf solution, application-specific circuits that include an ARM core along with a set of features optimized for a particular application, or CPU cores with a uniquely-optimized set of features. The ARM partners include Asahi Kasei Microsystems, Cirrus Logic, Atmel/ES2, GEC Plessey, LG Semicon, NEC, OKI Semiconductor, Samsung, Sharp, Symbios Logic (formerly NCR), Texas Instruments, and VLSI Technology. This grouping of companies represents one of the broadest industry CPU partnerships, and makes the ARM the highest-volume RISC CPU (in all its variations) to date.

An early 32-bit embedded entry, the Am29000 family developed by Advanced Micro Devices, is one of the first to reach a sort of end-of-life status. AMD has indicated it will not develop any new versions of its 29000 family, but it will continue to manufacture and support existing family members and produce the recently-released enhanced versions of the 29200

#### RISC PROCESSORS

series.

The other early RISC entry targeted at embedded applications from the start, the i960 family of RISC processors from Intel, has maintained a strong presence, with some significant inroads into applications such as network bridges and routers. The latest versions, the 80960HA/HD/HT and the 80960RP, have targeted high-performance systems. For instance, the HA/HD/HT versions have a superscalar architecture can be clocked at 1X, 2X, or 3X the bus clock speed, respectively, delivering up to 150 MIPS. The RP version is more application optimized and has been crafted to bring intelligence to I/O support in client/server environments.

The Thumb variation from ARM, the StrongARM from DEC, the SH series from Hitachi, the ColdFire family from Motorola, the V800 series from NEC, and the Compact RISC from National Semiconductor, are some of the latest ground-up RISC architectures that designers can select from. The list continues to grow with the release of a 32-bit processor by Mitsubishi Electronics America Inc. (See "Combo RISC CPU and DRAM solves data bandwidth issues," Mar. 4, 1996, p. 67). SGS-Thomson has just released a totally revamped version of its Transputer architecture called the ST20. Next month (April, 1996), Sun Microsystems

will release the first Sun-created version of the MicroSPARC II architecture, the IIe, targeted at embedded control applications.

In addition to the traditional CPU suppliers, the embedded RISC field is drawing in new suppliers who feel they can offer some unique capabilities. For example, CSEM (the Centre d'Electronique Suisse et de Microtechnique), Neuchatel, Switzerland, has crafted a very-lowpower scalable RISC core dubbed CoolRISC. The core can be scaled from an 8-bit data-word width up to a full 32-bit architecture, yet consumes just a few milliwatts of power. Another company, Patriot Scientific, has developed a novel 32-bit processor called ShBoom. Capable of running at 100 MHz, the 32-bit ShBoom CPU is actually a dual-processor architecture consisting of a RISC CPU based on a zerooperand dual-stack architecture, and an I/O processor that performs timing, time-synchronous data transfers, bit outputs, and DRAM control.

Raw throughput of these latest RISC processors ranges from about 20 MIPS on the low end to well over 100 MIPS for the fastest RISC processors. About a dozen different architectures are now competing in this cost-sensitive arena to form the heart of products such as communication controllers, printers, video games, and industrial

**2.** AT THE HEART OF THE STRONGARM PROCESSOR developed by Digital Equipment is a high-performance Thumb-compatible core that can operate at clock rates as high as 200 MHz. The core's data path includes a simple five-stage pipeline, a five-port register file, and a high-performance multiplier that retires 12 bits every cycle.

10 • SUPPLEMENT TO ELECTRONIC DESIGN • MARCH 3, 1997

# It's tough

It's Pentura CompactPCI Solutions

I.\_

It's

easy

OMBINE THE RUGGED durability of the most innovative, industrial-strength embedded computer with the ease-of-use of a PC. The result is Pentura". A CompactPCI system that's quick, simple, consistently reliable, easily serviceable and very cost effective. It sports a high-powered Pentium processor, is fully compatible with Windows NT, supports standard networking environments and applications. Its Eurocard mechanics are perfect for harsh environments. Including I/O-intensive applications. It's the easy choice for tough demands. Get our CompactPCI white paper on our web site, or call 1-888-FORCEUSA.

www.forcecomputers.com READER SERVICE 105 RISC PROCESSORS

robots.

The surplus of choices makes the task of selecting the best processor for the job quite challenging, to say the least. Trade-off matrices can end up including many features, performance numbers, pricing data, software development tools, and so on. And when those matrices still don't come up with an answer, designers can "roll their own" CPU through the use of the available RISC cores and megacell libraries.

One high-interest area in which highly-integrated RISC chips look very attractive is in the hand-held personal digital assistant (PDA) marketplace, in which high throughput, low power and high integration must all come together. And as long as a good C compiler exists, it may not make much difference to the designer which CPU architecture (from among all qualifying candidates) is actually selected, since hardware compatibility and software compatibility are not as important in mostly-closed systems.

For that reason, the novel approach such as employed by Mitsubishi-integrating DRAM main memory onto the CPU chip-could provide a highperformance alternative to today's integrated CPUs. Unlike the high-integration processors now being offered by many suppliers, the M32R/D places lots of memory along with the CPU on a chip. Peripheral support functions are relegated to a separate peripheral chip, since most support functions don't require close coupling to the CPU, and can often run at clock speeds of less than 25 MHz. Memory, both DRAM main memory and SRAM caches, must be closely coupled to the CPU to let the processor deliver top performance. By integrating 16-Mbits of DRAM and 2-kbytes of SRAM cache along with a 32-bit RISC processor, wide, high-speed data buses can be used on the chip to provide high-bandwidth paths to move data and instructions.

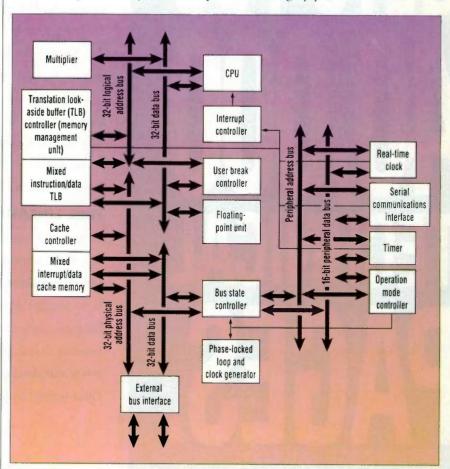

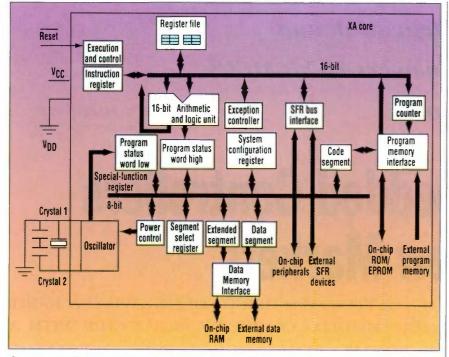

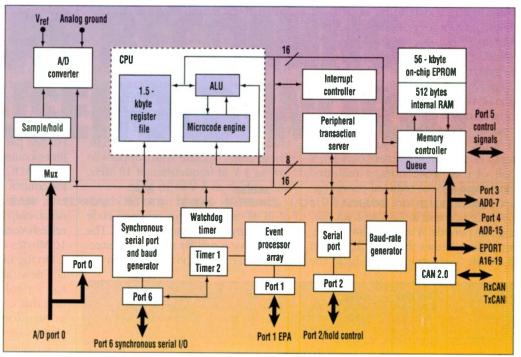

Staying with a more traditional approach, the recent release of a MIPS R3000-based design of a PDA on a chip by Philips Semiconductors—the PR30100—provides designers with a low-cost system building block (less than \$20 apiece in lots of 100,000 units) (ELECTRONIC DESIGN, Nov. 20, 1995, p. 55). To keep the chip's cost

low, Philips' designers integrated only 1 kbyte each of data and instruction cache, and did not include hardware support for multiply-and-accumulate operations in the R3000 core (*Fig. 1*). One area the designers didn't skimp on was the chip's 4-Gbyte address space. By keeping the address bus to a full 32 bits, the processor will be able to interface and control high-density CD and magnetic storage devices.

Rather than push for supercomputerlike speeds, designers at Philips optimized the chip for low power, with the CPU and bus interface operating at 18.432 MHz (a value derived from the 32-kHz low-cost watch-type crystal used for the PLL-based clock generator). Most instructions execute in a single clock cycle (except loads, stores, and branches), allowing the chip to deliver a throughput of about 15 MIPS.

Internal power-management logic helps keep the active power to just 150 mW when powered by a 3.3-V supply. Moreover, various operating modes allow power savings when all features aren't immediately needed at its lowest in the "coma" mode, standby current can drop to as little as 30 µA.

Preceding the Philips chip, of course, was Apple Computer Inc., Cupertino, Calif., who developed the Newton PDA based on the ARM RISC processor. The Newtons, however, use a standard ARM processor that's complemented with several custom chips that perform the rest of the system functions. ARM itself, though, has developed several highly-integrated processors. The ARM7100, for example, includes a power-reduced version of the ARM710 RISC core (the 710a), a large 8-kbyte four-way set associative cache (large for an ARM-family processor), an LCD interface, a DRAM interface that controls four 256-Mbyte banks of memory, and various I/O functions. Standby power for the chip is very low-with everything shut down, the current drops to less than  $10 \mu$  A, while running at full speed the chip consumes just 66 mW.

Some of the I/O functions included on the chip consist of a DMA controller for high-speed data transfers, a UARTstyle serial port, an infrared serial port (IrDA-compatible), a codec interface

with 16-byte FIFO buffers, and multiple 8-bit ports for general-purpose I/O support. The internal LCD controller delivers half-VGA screen images-640 by 240 pixels-and up to 16 levels of gray-scale resolution. Even with all these highly-integrated features, the small core area of the 710a allows the chip to sell for less than \$25 apiece in large volumes. ARM also offers another high-integration processor, the AMR7500, which includes multimedia support features-telephony or CDquality sound, a video output port capable of 120 MHz pixel data rates and direct drive of CRTs or LCDs, keyboard/mouse/joystick ports, and other I/O functions. This chip is based on the AMR710 core.

On the drawing boards at Advanced RISC Machines is the next-generation CPU, the ARM 8. Although not all features have been defined, this will be the first version to include some aspects of superscalar parallelism and a more heavily pipelined data path (five stages vs. three in previous chips) to further increase CPU performance. This processor-the ARM810-will deliver almost double the performance of the best ARM 7 (up to 80 MIPS), but at the same time, it requires double the chip area due to the morecomplex logic. That will cause the ARM 8 to consume about twice the power.

#### STRENGTHENING THE ARM

As one of the ARM licensees, Digital Equipment has undertaken the challenge of reimplementing the ARM instruction-set architecture on its highperformance 0.35-µm triple-levelmetal CMOS process. The result, described at the 1996 IEEE International Solid State Circuits Conference (ISSCC) in San Francisco, Calif., is a chip that delivers a throughput of over 200 MIPS when clocked at 200 MHz-close to a ten-fold performance improvement over the standard ARM processors. Though the advanced process may drive up processing cost, the resulting small chip will be very economical.

Dubbed StrongArm, the chip implements the recently-released Thumb instruction set (version 4 of the instruction-set architecture definition) (ELECTRONIC DESIGN, March 20, 1995, p.163). To get the high throughput, DEC's designers started with a

12 • SUPPLEMENT TO ELECTRONIC DESIGN • MARCH 3, 1997

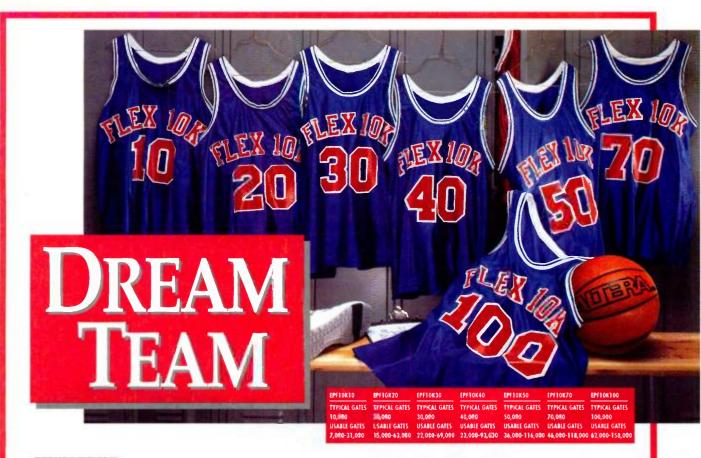

#### THE DESIGNER'S DREAM TEAM WITH UP TO 100,000 GATES.

The FLEX 10K Dream Team of programmable logic devices is a championship roster from Altera. With densities from 10,000 to 100,000 gates and up to 15 times greater memory efficiency than FPGAs, FLEX 10K can take on even the most aggressive gate arrays.

FLEX 10K offers all the benefits of programmability and features such as memory, incircuit reconfigurability, and built-in JTAG support. And, Altera's easy-to-use MAX+PLUS II development tools interface with all major CAE tools, giving you a team that will easily score against mid- to high-density gate arrays.

#### AN EMBEDDED ARRAY GAME PLAN.

The unique FLEX 10K architecture adds an embedded array to a logic array, so you can have up to 24K bits of RAM in a single chip, and megafunctions\*such as microprocessors, microcontrollers, DSP and PCI functions, and others.

#### THE ALTERA ADVANTAGE.

You need every advantage to compete in this league. Value, competitive pricing, high-performance technology, and comprehensive technical support — that's The Altera Advantage.

It's time to put the Dream Team to work for you. Call Altera today for your free FLEX 10K information kit. 800-9-ALTERA (800-925-8372), Dept. A165. Or, find us at http://www.altera.com on the world-wide web.

\*Developed through AMPP (Altera Megafunction Partners Program) Note: Individual family members available over the next 12 months. © Copyright 1996 Altera Corporation. Altera, FLEX, and MAX+PLUS are registered trademarks, and FLEX 10K, MAX+PLUS II, and specific device designations are trademarks of Altera Corporation. All rights reserved.

## SIEMENS

# Hard Wired.

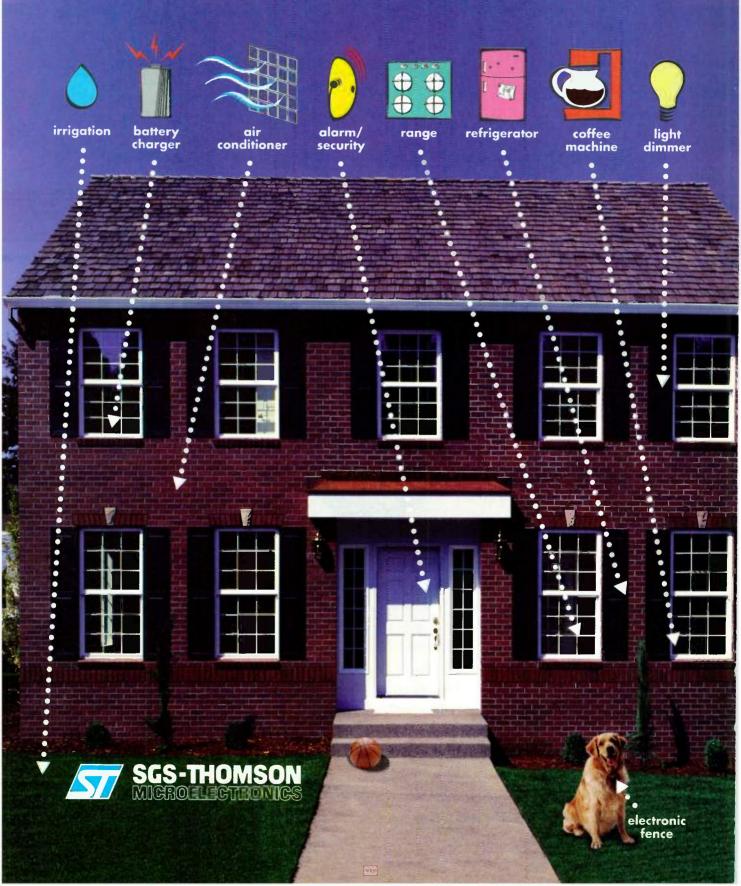

Simplify your life. Network your applications with Siemens microcontrollers and CAN 2.0B

Engineers around the world are discovering the power of Controller Area Network (CAN). And simplified wiring schemes are just the beginning. CAN also offers a host of other benefits, including 1 Mb/s speed over standard twisted pair, rock-solid data integrity in electrically noisy environments, even the ability to send data over AC wiring (great for factory automation). With so many advantages, it's no wonder CAN is rapidly gaining acceptance beyond the automotive market. And no other microcontroller manufacturer offers more CAN 2.0B solutions than Siemens.

# Easy Wired.

SIEMENS C167 CAN

#### 16-bit and 8-bit microcontrollers with CAN 2.0B. Plus, standalone solutions.

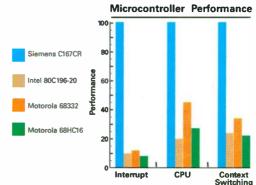

Siemens is your one-stop shop for CAN controllers. For 16-bit, we offer the SAB C167CR LM featuring the world's fastest 16-bit microcontroller architecture (see chart). Or choose the 8-bit SAB C515C LM. Both have CAN Version 2.0B, extending your system capacity to over 500 million different messages. We also have two stand-alone full CAN 2.0B passive products: the SAE 81C90 and the SAE 81C91 — both of which can work in CAN 2.0B active networks.

#### Volume deliveries today.

With fabs around the world, we have the capacity you need. You

also get local support and great third-party development tools.

To see how you can use CAN, call for a 16-bit Evaluation Kit. Ask for Ext. 4, Lit. Pack #M14A050. Plus, visit the CAN section on our Web site.

#### 1-800-77-SIEMENS http://www.sci.siemens.com/CAN.html

© 1996 Siemens Components, Inc; Complete CAN Capability is a trademark of Siemens Components, Inc.; Controller Area Network (CAN), License of Robert Bosch GmbH.

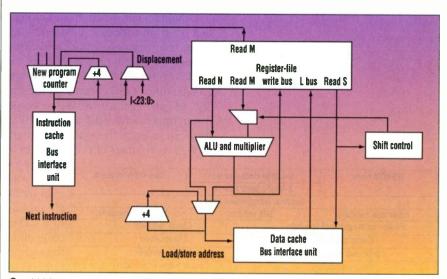

Harvard-style architecture with large instruction and data caches (16 kbytes each) that have independent buses (*Fig.* 2). That replaces the unified cache employed in previous ARM family members and provides more parallelism for read and write operations.

For faster matching, the caches are 32-way set-associative. Although that is a much higher degree of associativity than most CPUs, it is only half that of the 64-way set associativity used in the ARM 610 CPU. Supporting the caches are 32-entry memory-management units and an 8-entry write buffer (16 bytes per entry). The write buffer that allows the CPU to write results and then go on to another task without stalling if the memory subsystem is busy.

The CPU core is a single-issue design with a "classic" 5-stage pipeline. It can perform single-cycle branches and conditional execution of every instruction. Additional resources in the core include an in-line barrel shifter for shift/add and multiply/add operations, and a 32-word by 32-bit register file.

A multiplier-accumulator unit on the chip can perform 32- and 64-bit multiplication in three to six cycles (4.5 ns per cycle), retiring 12 bits at a time. That results in a fairly robust DSP-like processing capability for 12-, 24-, or 32-bit data words. In addition, the MAC includes leading 0 detection to allow for early termination of the multi-cycle computations. The fast computations suit the chip well for DSP algorithms typically encountered in PDAs-data communications (modems), handwriting recognition, and speech recognition and output are some of the key functions the processor can support.

Although high-speed CMOS typically has a reputation for consuming a lot of power, the StrongARM processor was designed for low-power operation, with an idle mode allowing the chip to dissipate just 20 mW, and a sleep mode that drops power to less than 200  $\mu$ W.

In the normal operating mode, the device consumes about 900 mW when clocked at 200 MHz and running from a 2-V supply. When the core is powered by a 1.65-V supply, it can still run at up to 160 MHz while the power drain drops to just below the 500-mW mark. At that speed and

#### RISC PROCESSORS

power, the chip delivers a MIPS/W ratio of 411.

Conditional clocking allows sections of the chip not being used during an operation to be turned off, thereby minimizing power. In addition, edge-triggered latches were used throughout most of the design to minimize gate loading on the clock lines. Power can also be further reduced by running the internal clocks off the slower bus clock during cache fills.

In addition to the highly-integrated ARM and StrongARM processors, many of the recent license agreements provide the various semiconductor partners with access to the ARM7TDMI Thumb processor core. One of the partners, Texas Instruments, has embedded the core into a TGC3000 series gate array that packs 100,000 gates in which users can integrate application-specific logic. The core that TI implemented will be part of the company's TMS 470 microcontroller series. The fully-static core delivers 36 MIPS when clocked at 40 MHz.

Another partner, VLSI Technology, not only offers the core CPUs as part of its megacell libraries, but has crafted several standard products that employ the processor core. Some of those products include the Ruby I and II communications controllers, and a two-chip GSM telephone. GEC Plessey has also used the ARM core at the heart of several communications controllers, while Sharp has developed a family of microcontrollers—the LH77790 series that includes on-chip LCD control.

Going after the PDA market with a PowerPC-based solution, Motorola has crafted a chip with a somewhat similar array of features to the ARM 7100 or Philips' PDA chip, but offers a much higher throughput than either of those CPUs-53 MIPS at 40 MHz. The MPC821 is the first result of Motorola's own use of the PowerPC core technology to create a highly-integrated processor targeted at portable computing/communications systems. When clocked at 25 MHz, the processor consumes less than 300 mW. Power consumption drops to less than 10  $\mu$ W in the low-power stop mode.

In addition to the PowerPC core, the chip includes instruction and data caches (4-kbytes each), a second RISCbased (proprietary) controller that manages many of the I/O support functions, a dedicated multiplier-accumulator, and bus interface logic. A system interface block included on the chip provides the host-system interface, memory-control support for DRAM, ROM, and other memory

**3.** THE FIRST SUPERSCALAR PROCESSOR CORE compatible with the R3000 and R4000 32-bit instruction sets employs an enhanced bardware architecture to provide a higher throughput than other MIPS-based cores. Developed by LSI Logic, the CW4010 core bas 64-bit memory and cache interfaces and can issue and retire two instructions per cycle thanks to the use of five independent execution units..

#### **GO AHEAD-KICK THE TIRES.**

## FOR EMBEDDED APPLICATIONS, THIS 486 COMES FULLY LOADED.

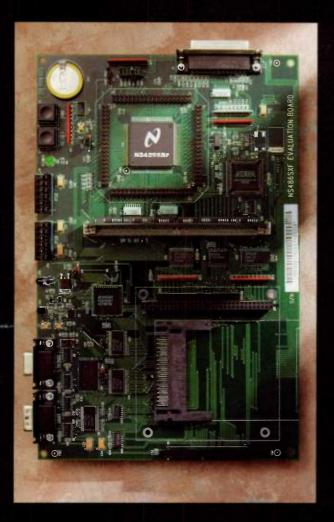

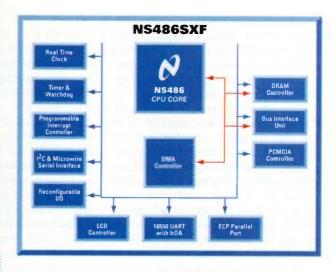

To reduce costs and time to market for your embedded 32bit application, the **NS486SXF** comes standard with all the features you could want.

With the industry's most complete set of integrated peripherals and on-chip service elements, the NS486SXF is the first true embedded 486 system on a chip. By eliminating costly desktop features, we've created the only 486 CPU core that is optimized for embedded applications.

The familiarity of the 486 architecture means you can develop with confidence. And NS486SXF is supported by the best compilers in the industry, and by tools and kernels from leading real-time operating system vendors.

The NS486SXF Evaluation Kit includes everything you need to generate and debug code and run benchmarks, including evaluation copies of industry-leading development tools and kernels from several world-class software vendors.

#### ENTER TO WIN A FREE EVALUATION KIT.

VISIT US: At the Embedded Systems Show East.

March 10-12 at the Hynes Convention Center

NS486SXF 25 Evaluation IT

in Boston; Booth #810. For more information contact us at: INFO CARD: Mail or Fax WEB: http://www.national.com./see/NS486

CALL: 1-800-272-9959 Ext. 757

#### types, and packs both a real-time clock and a two-slot PCMCIA interface. An LCD controller supports bit-mapped graphics, with monochrome (4/16 gray scale levels) or 16-color thin-film-transistor (TFT) active-matrix displays.

There are also two multiprotocol serial communication controllers that can implement Ethernet, HDLC/ SDLC, AppleTalk, serial infrared (IrDA-compatible), synchronous or asynchronous receiver/transmitters, and other protocols. Two more serial-management channels provide asynchronous serial communications and can be connected to the internal time-division multiplexed serial channels.

The same basic technology used in the MPC821 went into the creation of the MPC860, also known as the PowerQUICC. This chip is an enhanced version of the 68k core-based QUICC multi-channel data-communications controller ( ELECTRONIC DE-SIGN, Sept. 18, 1995, p. 175).

The PowerPC controller core, as in the MPC821, delivers 53 MIPS when clocked at 40 MHz and controls the activities of up to four on-chip Ethernet channels and HDLC communications support. Supporting the core are 4 kbytes each of instruction and data

#### RISC PROCESSORS

cache. Also included on the PowerQUICC chip is a second RISC engine—a dedicated 32-bit controller for the system interface functions such as timers, interrupt controllers, virtual DMA channels, parallel I/O lines, and other functions.

Motorola has also crafted a family of general-purpose embedded PowerPC controllers, the MPC-500 series, but since their introduction about a year ago, has not released any new general-purpose chips. The second half of this year should see several new family members unveiled. On the other hand, IBM, the originator of the PowerPC architecture, has been busy developing new family members for embedded applications, both in the form of embedded cores and highlyintegrated CPU chips.

#### PORTABLE MULTIMEDIA

IBM is also trying to attract designers of PDAs, set-top boxes, and other portable systems with a highly-integrated processor in its PowerPC 600 family, the 602. With a power consumption of 18 mW/MHz, and an upper clock limit of 66 MHz, the processor has a host of features that suit it well for PDAs, embedded multimedia support, video games, set-top boxes,

and other systems.

Implemented with a 0.5-µm fourlevel metal CMOS process, the superscalar processor packs 1 million transistors into a small, 7-by-7-mm chip. Dual 4-kbyte caches connect to a highspeed 64-bit internal bus, and separate execution units—floating-point, integer, branch, and load-store—allow two instructions to be issued every clock cycle.

Furthermore, the on-chip floatingpoint unit can assist in multimedia applications such as audio editing, since its single-precision 32-bit computations can readily provide a wide dynamic range when editing up to 12-bit audio data. For higher-resolution 16bit audio, the 72-dB dynamic range of the floating-point unit can be extended if software can handle the overflow conditions. Such support results in a 96-dB dynamic range (CD-quality) and only slightly slower throughput than when manipulating the 12-bit audio.

To minimize chip power consumption, the execution units are dynamically powered down. That allows the standby power to drop to less than 2 mW. When running at maximum speed, the typical operating power is about 1.2 W. In the envisioned appli-

### **Manufacturers Of RISC Chips**

Advanced Micro Devices Inc. Austin, Texas (512) 602-6237

Advanced RISC Machines Ltd. Los Gatos, Calif. (408) 399-5195

Asahi Kasei Microsystems San Jose, Calif. (408) 436-8580

Atmel Corp. San Jose, Calif. (408) 436-4243

Centre Suisse d'Electronique et de Microtechnique SA Neuchatel, Switzerland (41) 38-205-111

Cirrus Logic Inc. Fremont, Colif. (408) 623-8300

Digital Equipment Corp. Hudson, Mass. (508) 568-5856 ES2 (European Silicon Structures) Rousset, France (33) 42 33 41 50

Fujitsu Microelectronics Inc. San Jose, Calif. (408) 922-9000

GEC Plessey Scotts Valley, Calif. (408) 451-4700

Hitachi America Ltd. Brisbane, Calif. (415) 589-8300

IBM Microelectronics Corp. East Fishkill, N.Y. (914) 894-2121

Integrated Device Technology Inc. Santa Clara, Calif. (408) 492-8623

Intel Corp. Chandler, Ariz. (602) 554-8080 LG Semicon Co. Ltd. San Jose, Calif. (408) 432-5000

LSI Logic Corp. Milpitas, Calif. (408) 433-8000

Mitsubishi Electronics America Corp. Sunnyvale, Calif. (408) 730-5900

Motorola Inc. Austin, Texas (512) 891-8704

NEC Electronics America Inc. Mountain View, Calif. (415) 960-6000

National Semiconductor Corp. Santa Clara, Calif. (408) 721-5000

OKI Semiconductor Sunnyvale, Calif. (408) 720-1900 Patriot Scientific Corp. Poway, Calif. (619) 679-4428

Philips Semiconductors Sunnyvale, Calif. (408) 991-2000

SGS-Thomson Microelectronics Lincoln, Mass. (617) 259-0300

Samsung Semiconductor Corp. San Jose, Calif. (408) 954-7008

Sharp Corp. Camus, Wash. (206) 834-8700

Siemens Corp. Cupertino, Calif. (408) 777-4500

Silicon Graphics Corp. MIPS Technology Div. Mountain View, Calif. (415) 960-1980

Sun Microsystems Computer Co. Mountain View, Calif. (415) 960-1300 Symbios Logic Fort Collins, Col. (970) 226-9550

Teknema Inc. Menlo Park, Calif. (415) 833-7910

Texas Instruments Inc. Stafford, Texas (713) 274-3704

Toshiba America Electronic Components Inc. Irvine, Calif. (714) 455-2000

VLSI Technology Inc. Tempe, Ariz. (602) 752-8574

Winbond Electronics Corp. Santa Clara, Calif. (408) 982-0381

This list is only a guide; it is not a complete listing.

### ANY MORE INTEGRATED AND THIS 8-BIT MICROCONTROLLER WOULD BE DOING YOUR WORK FOR YOU.

Vcc

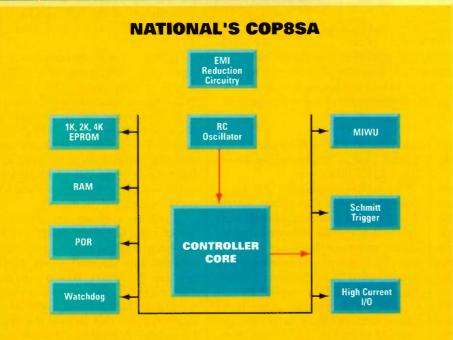

#### INTRODUCING THE COP8SA SINGLE CHIP SOLUTION.

Oh, sure, you'll still have to connect the chip to the ground and the Vcc. But after that, you're pretty much done.

and MOVING AND SILAPING THE FUTTRE are tradem

NICHALI

Illy month

Cortion

966

Ø

2

VATIONAL SEMICONDUCTOR

That's because the new **COP8SA** mid-range OTP microcontroller requires zero external components. Zip. Which means the R/C oscillator, power-on-reset (POR), pull-up resistors, schmitt-triggers, and protection diodes are all built in. Which means your life is instantly easier. There's even patented EMI technology, a latchup capability that meets stringent industry standards, and an ESD rating that's over twice the

GND

industry norm.

The result? The quality and reliability of a single-chip solution in an industry-standard footprint. Add easy-to-use development tools and an Evaluation

> and Programming Unit for under \$99, and your product will be in the market before you know it.

The COP8SA. You're almost done already.

COPESA

#### FREE INFO KIT-FAST.

To test the COP8SA, contact your local distributor. While you're waiting, give National a call and we'll get you started. **CALL:** 1-800-272-9959 Ext. 738. **WEB:** http://www.national.com/see/cop8sa

In Europe, fax us at +49 (0) 180-5-12-12-15; in Japan, call 81-43-259-2300, in Southeast Asia, fax us at 852-2376-3901.

RISC PROCESSORS

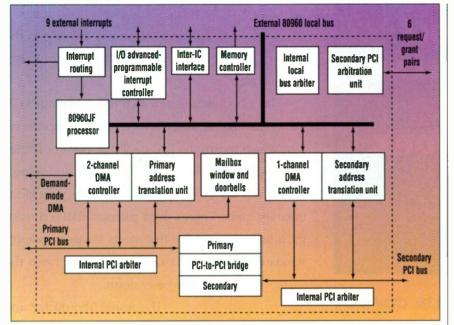

**4.** INTENDED TO SUPPORT HIGH-PERFORMANCE I/O operations, the 80960RP from Intel is also the first 32-bit embedded RISC controller to include dual PCI interfaces. Targeted at server network and storage support, the 80960RP provides an intelligent bridge to multiple network controllers or to a RAID subsystem.

cations, processor operation tends to be very bursty, thus average power will be much lower.

To tackle the low end of the embedded market, IBM designers have trimmed back on the complexity of the PowerPC 403 and 405 cores and created the 401, which occupies an area of just 5.5 mm<sup>2</sup>. The core can execute all PowerPC code, includes hardware support for unaligned data accesses, and includes big- and little-endian support. Such a core will be able to deliver embedded solutions that can cost as little as \$10 in large volumes.

Included in the basic core are robust debug capabilities--a critical feature as custom chips are integrated. Also embedded are both dynamic and static power-management facilities, a 32-word by 32-bit register file, and a dual-level interrupt structure. The reduced core leaves many features as options--instruction and data caches, coprocessors, memory management, interrupt control, and other functions. The powermanagement control allows the core to trim power consumption to about 50 mW when clocked at 25 MHz and powered by a 3.3-V supply. With a 2.4-V supply, the core's power drain drops to just 26 mW--some of the lowest power consumption levels for a 32-bit RISC core.

The growing availability of cores or licensable design files allows system designers and silicon suppliers to craft application-specific solutions. For instance, many core licensees are using the CPU cores to create commercial products that include significant intelligence and control capabilities.

Some prime examples of this trend can be seen with the various CPUs developed as part of Sun's SPARC family. Targeting the embedded control market based on the original SPARC I architecture, designers at Fujitsu Microelectronics created the SPARClite family, which includes over half-adozen CPUs, including the MB86934, 86933H, and 86936.

Both the 86934 and 936 are targeted at high-performance applications and pack floating-point coprocessors large on-chip caches, and Harvard-style architectures. The 86934 packs double the instruction cache of the 86936 (8 kbytes versus 4 kbytes), can access 247 different address spaces, with each containing up to 4 Gbytes, and delivering a sustained throughput of 55.5 MIPS when clocked at 60 MHz. The 86936 has a reduced address space and can access only 16 address spaces that each address up to 256 Mbytes. When clocked at 50 MHz, it delivers a peak throughput of 50 MIPS.

In some areas, the 86936 is a superset of the 86934, but in other areas, the 86934 is a superset of the 86936. For example, the 86936 device includes a video interface that can be used to drive printer/digital-copier engines/rasterizers, a pair of 24-bit timers, and a high-performance interrupt controller to list just a few of the distinguishing features. In contrast, the 86934 offers memory support for synchronous DRAMs and half-a-dozen on-chip FIFO buffers to help decouple the floating-point computations from the rest of the chip to achieve a floating-point throughput of 60 MFLOPS (peak).

Targeted at lower-throughput and lower-cost applications, the 86933H is a reduced-functionality CPU that can be clocked at just 20 MHz. The reduced clock rate limits the throughput to about 20 MIPS peak and 18 MIPS sustained. To trim the complexity and cost, the 86933H does not include a floating-point unit or extensive caches—only a 1-kbyte instruction cache is included on the chip.

In addition to extensions of original SPARC core, the MicroSPARC I design has been licensed by several companies that have released or will shortly release products based on the MicroSPARC I core. Some of those companies have crafted applicationtargeted chips that include the core. Companies that fall into this category include Matra-Harris, a division of Temic, Nantes, France, Hyundai Semiconductor, San Jose, Calif., and C-Cube Microsystems Corp., Milpitas, Calif.

Temic decided to employ the RISC core the same way as Motorola uses the PowerPC core in the PowerQUICC chip to implement a multichannel communications/network controller—the SPARCLET family (TSC701). Targeting multimedia applications, Hyundai employs the MicroSPARC core for use in products such as MPEG-2 decoders for set-top boxes, home theaters, and other applications. And in late 1995, Sun inked an agreement with C-Cube, which will

#### WWW.NATIONAL.COM

So you're trying to find the right part. You can hunt through databooks and app notes till you finally get somewhere. But now there's a fast, efficient way to get everything you need to work with: Datasheets. Application notes. Samples. Price/availability. **24 hours a day.**

Just bookmark **www.national.com,** and go straight to our web site. Where you're never more

than 4 clicks from the exact information you need. And to give you powerful, customized access to over 14,000 products, we've built in a parametric search engine. It's fast, simple, and totally up to date.

No wonder design engineers have called this one of the best sites in the industry. If

- PARAMETRIC

SEARCH ENGINE

- 4,000 DATASHEETS

- FREE SAMPLES

- 1,500 APP NOTES

- FREE ANALOG DATA BOOKS

- SOFTWARE-BASED DESIGN TOOLS

- PRICING ON

8,000 PRODUCTS

you haven't tried it yet, we think you should pay us a visit immediately. It's the best way there is to get some work done.

#### FREE LINEAR SEMINAR HANDBOOK.

As an extra reason to bookmark this site, we're offering our 350-page **Linear Seminar Handbook**. To prove how simple this site is to use, there's no business reply card to fill out. No 800 number to call. Just go to

**www.national.com/design**, and the book is free. Offer limited to first 10,000 visitors, so hurry.

National Semiconductor

Moving and shaping the future.<sup>TM</sup>

#### RISC PROCESSORS

license MicroSPARC core to be embedded in a forthcoming MPEG-2 encoder chip set and other products.

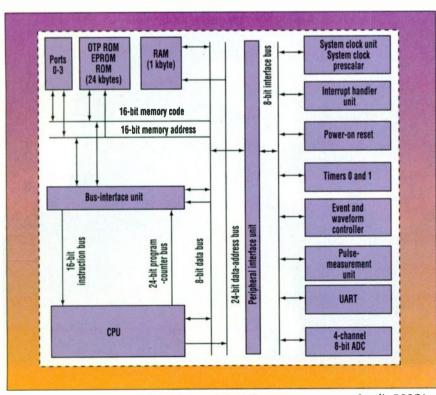

The interest in embedded versions of the SPARC has prompted Sun's SPARC Technology Business unit to create an embedded version of the second-generation MicroSPARC processor, the MicroSPARC IIe. Slated for release next month (April, 1996), the processor will include both integer and floating-point units, a DRAM controller, a memory-management unit, a ROM controller interface, and programmable "hooks" for the chip to tie into many industry-standard buses.

Focusing most of its efforts on variations of the MIPS R3000 core, LSI Logic, as a licensee of the MIPS architecture, has targeted several key application areas such as communications (network control, bridges, routers, ATM systems, etc.), set-top boxes, and industrial systems. Soon to be released is the next turn of the screw, the MiniRISC CW4010, the first superscalar core that will part of the design library.

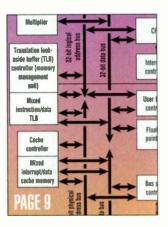

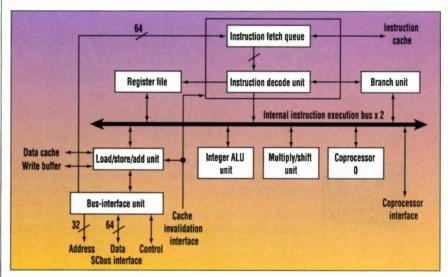

Based on the MIPS II superscalar core (R4000 32-bit-mode compatible), the CW4010 offers much higher performance than the company's previous MIPS-compatible miniRISC CPU core. the CS4001. The basic core includes the arithmetic and logic unit, a system control coprocessor, a bus interface unit, a load-store unit, and an instruction scheduling unit (Fig. 3). To complement the core, designers can add blocks from the CoreWare design library-blocks such as direct-mapped or two-way set-associative instruction and data caches, an MMU, a hardware multiplier-accumulator, and writeback buffers.

The core issues two instructions per clock and can achieve a peak throughput of 160 MIPS (110 MIPS sustained), when clocked at 80 MHz and powered from a 3.3-V supply. The core requires little chip area—in fact, less than many of the ground-up RISC designs—just 3 mm<sup>2</sup>. And the small area also translates into low power consumption—just 5 mW/MHz.

Another licensee of the MIPS architecture, Integrated Device Technology, has taken the MIPS architecture it licensed from MIPS and proliferated several families of embedded controllers—the 3050 and 3080 families targeted at communications control, industrial applications, and computer peripherals. In addition to those families, the 64-bit R4600 CPU, better known as the Orion, has also been optimized for embedded applications, in several new versions released by IDT in the last quarter of 1995. The chips include some enhancements over the R4600, providing more of a system solution at lower cost points than the original R4600.

Toshiba is also offering the 64-bit Orion processor, but has not released any offshoots focusing on the embedded control arena. As an alternative, Toshiba is offering the 32-bit R3900 processor core as a megacell that designers can access through the company's ASIC design tools and standardcell processing. When clocked at 50 MHz, the core consumes about 400 mW when powered by a 3.3-V supply. At that speed, the core can deliver about 52 MIPS. In addition, designers at Toshiba have crafted a slightlyhigher-integration option—the TMPR3901-F—that takes the previous R3900 core and adds to it a 4-kbyte instruction cache, a 1-kbyte data cache, a write buffer, and some additional logic.

Also playing in the MIPS camp, NEC has several high-performance MIPScompatible processors targeted at embedded applications such as set-top boxes, arcade games, network controllers, laser printers, and other systems. Able to clock at a top speed of 133 MHz, the V R4300 delivers 64-bit throughput of 170 Dhrystone MIPS. That high throughput is made possible thanks to a 16-kbyte instruction cache and an 8-kbyte data cache, a 32 double-entry translation look-aside buffer, a 4-word deep write buffer, and a five-stage pipelined arithmetic unit.

**5.** THE ADDITION OF A FLOATING-POINT coprocessor to the SH-3 RISC processor allows designers at Hitachi to use the SH-3E in compute-intensive 3D graphics systems. Also included on the chip are an integer multiplier, serial communications interfaces, a real-time clock, and 2 or 8 kbytes of cache.

## Control Everything...

## Well Almost.

If you think predicting the weather is tough, try controlling it! Z-World's versatile and powerful controllers can control most anything in your world—like the climate in your building. We control everything from laser surgical devices, to airframe riveting machines. And, we do it in 45 nations. Z-World's controllers interface easily with thousands of sensors, actuators and instruments. They can be networked using standard data communication protocols. Z-World's controllers are easy to program. Simply use your PC with our integrated Dynamic C<sup>TM</sup> software development system. If you need to get your product to market fast, we offer cost-effective, low-risk solutions for control applications. So, don't be left in the cold. **Call Z-World now.**

### NEW! PK 2300 From \$179

The **PK 2300**. 191 O (11 are user-configurable). Protected inputs. High-current outputs.RS-232/RS-485 serial ports. Panel or DIN-rail mount. Resistance measurement input. Rugged ABS enclosure.

IN

INNOVATION

Z-World, 1724 Picasso Avenue, Davis, CA 95616 USA Telephone 916-757-3737 • FAX 916-753-5141 • To place an order call 1-888-EMBEDUS (USA) For immediate information, use our 24 hour AutoFax 916-753-0618 or visit our Website http://www.zworld.com READER SERVICE 100

ORL

CONTROL TECHNOLOGY

For 32-bit processing needs, designers can also turn to NEC's VR4100, which when powered by a 2.2-V supply can deliver a peak of 815 MIPS/W. The 4100 can also operate at 3.3 V. At that voltage level, it delivers a MIPS/W ratio of 375.

NEC's proprietary RISC family, the V800 series, consists of over half-adozen members that deliver throughputs ranging from about 10 MIPS on the low end with the V805 up to about 100 MIPS for the best unit currently available. Plans are already in place to up the performance still further, with the goals of 1000 MIPS and beyond. The V810 series delivers about 18 MIPS at 25 MHz, consumes about 500 mW at 5 V and 25 MHz, and has options for operation at lower supply voltages-2.2 V for the V805 and 3.3 V for the V810. At the lower supply-voltage level, the V805 delivers a throughput of about 11.5 MIPS and consumes 100 mW.

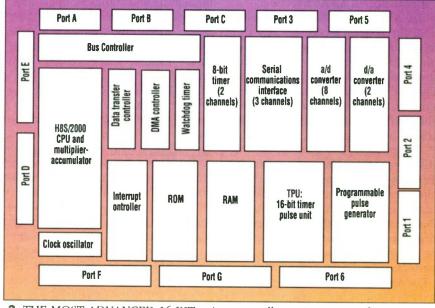

Additional family members increase the functional integration on the chip from the basic CPU-the V820 includes a 16-input interrupt controller, dual serial communication ports, a four-channel DMA controller, and a three-channel counter-timer unit. Containing many similar functions to the V820, the V821 adds a DRAM controller, but reduces the bus width to 16 bits, thus reducing the package pin count. Currently at the top of the performance curve is the V830, a 32-bit processor that delivers 118 MIPS when clocked at 100 MHz. At that clock frequency, the processor consumes about 500 mW when powered by a 3.3-V supply. Aimed at closed-loop control and signal-processing applications, the V830 also includes a high-speed multiplier-accumulator that can perform single-cycle (10-ns) multiplies.

Nestled between the 810 and 830 is the V850 series, which are more like single-chip MCUs and include on-chip RAM and ROM/PROM. The V851 and 852 also have 16-bit hardware multiplier-accumulators that can deliver a product in as little as 30 ns when clocked at 33 MHz. Overall throughput for the processors is about 38 MIPS for the 851 (at 33 MHz), and 29 MIPS for the V852 (25 MHz).

One of the longest-surviving 32-bit RISC families that has not lined up with

6. VARIABLE-LENGTH INSTRUCTIONS are used by the ColdFire processor core to minimize the amount of off-chip storage needed for the firmware. The first integrated version of the ColdFire-based processor developed by Motorola includes a 512-byte instruction cache, a 512-byte SRAM, dual asynchronous serial ports, an inter-IC port, a pair of timers, a DRAM controller, an interrupt controller, and eight parallel I/O lines.

an alternate supplier, the i960 from Intel provides designers with a wide range of CPU chips, from low-cost general-purpose devices that deliver 10 to 20 MIPS, to high-performance I/O controllers that have 40 to 150 MIPS of processing horsepower. One of the newest chips, the 80960RP, combines an 80960JF RISC core and is the only embedded controller to include a PCI-to-PCI bridge interface on the chip. Additional functions integrated on the chip include three chaining DMA controllers, a memory controller that supports DRAM, ROM and flash memories, many other features to support server networking and storage subsystems (Fig. 4).

Thanks to the on-chip PCI interface, I/O cards based on the controller can support multiple PCI peripherals on the board, while the board itself only occupies one PCI slot. That greatly reduces board complexity. Or, if added to a motherboard, it can offload the host CPU from control tasks and provide a secondary PCI bus that allows Ethernet communications cards or RAID storage subsystems to be connected.

Yet other proprietary RISC familiesthe SH series from Hitachi and the ColdFire family from Motorola-have taken cues from the other RISC families and offer unique solutions to both system integration and time-to-market pressures. Both families were developed with high code density in mind. Hitachi accomplishes that on the SH series by using a fixed, 16-bit instruction, while Motorola designers opted for a variable-length instruction approach to pack the code and minimize off-chip memory needs.

Hitachi has already released three generations of SH processors, the SH-

24 • SUPPLEMENT TO ELECTRONIC DESIGN • MARCH 3, 1997

# ENGARDE! DEVELOPMENT SUPBOR

### INTRODUCING A POWERFUL TEAM THAT CAN HELP YOU SLASH MPC 860 DEVELOPMENT TIME AND COSTS.

PowerP

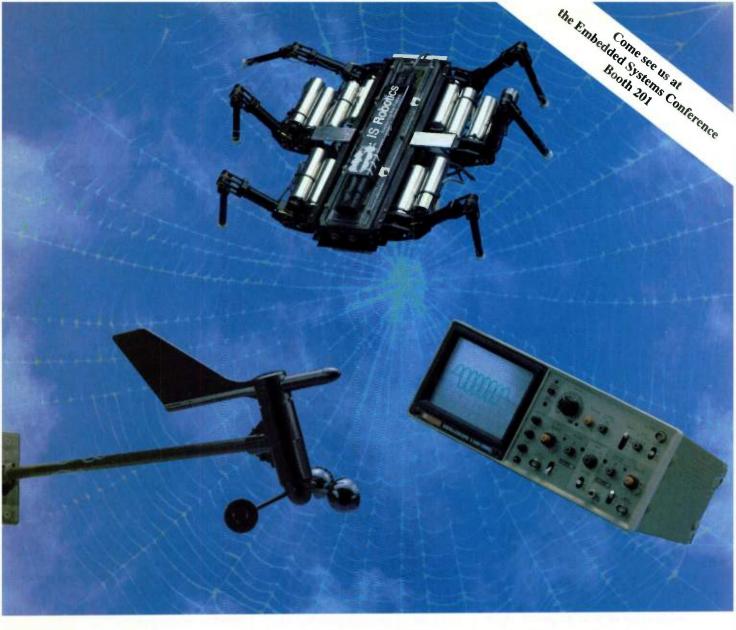

Applied Microsystems Corporation products and services cover the full development cycle for PowerPC. Applied expertise helps you pull it all together with seminars, training consulting and support.

Design: Speed up system partitioning with Egglet<sup>®</sup> and VSP-TAP Debugging: Accelerate software and hardware development with SuperTAP.<sup>®</sup> CodeTAP.<sup>®</sup> and NetROM.<sup>®</sup>

Testing: Improve software quality and performance with CodeTEST."

#### CALL Now 1-800-426-3925

for **FREE** White Papers on designing with the MPC 860, and on choosing design, debug and test tools. Or visit our home page at www.amc.com.

European Distributor: Applied Microsystems UK and Europe. Tel: +44 (0)1296-625462. Fax: +44 (0)1296-623460. Germany Tel: +49 (0)89-427-4030. Fax: +49 (0)89-427-40333. France Tel: +33 (0)1644-63000. Fax: +33 (0)1644-60760. PowerPC is a registered trademark of International Business Machines Corp and is used under license therefrom. Designated trademarks and brands are the properties of their respective owners.

READER SERVICE 82

1. -2 and -3, and within each generation there can be multiple iterations. The latest release, the SH-3, includes two versions, the SH-DSP and the SH-3E. These two chips share the same base architecture with a CPU that can min at 100 MHz and deliver a throughput of 100 MIPS when powered by a 3.3-V supply. The base SH-3 processor comes in two variations-one version packs an on-chip unified cache of 8 kbytes (the SH7708), while the other includes 2 kbytes of unified cache (SH7702). The cache can be directly addressed and thus can also serve as general-purpose RAM if needed.

At 100 MHz, the processors consume about 1 W. By backing off on the clock to 60 MHz, the MIPS rating and power consumption are proportionally reduced. A further the clock to 30 MHz trims the more significantly, reduces the outside world. the power consumption to iust 180 mW.

A very small CPU core is at the heart of the SH processors--the core area is just 2.1 mm<sup>2</sup> when fabricated with 0.35-µm design rules, thus keeping the total chip area to a minimum. On-chip peripheral support includes a real-time clock, three 32bit timers, a serial asynchronous, fullduplex communications port, an 8bit general-purpose I/O port, an interrupt controller, and a bus controller that can access seven physical address spaces of 64 Mbytes each. and can interface to DRAMs, SDRAMs, PSRAMs, ROM, and SRAMs. The bus controller also supports PCMCIA interfaces and includes a bus switch for big-endian/little-endian data formats.

The SH-3E processor has been optimized for consumer 3D graphics support and is the first SH family member to include single-precision floatingpoint math capability on the chip (Fig. 5). It is basically an SH-3 with an integrated FPU. Calculations are done in

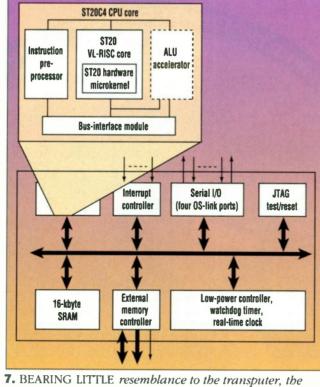

reduction in the power-sup- ST20-based RISC controller developed by SGS-Thomson conply level to 2.5 V and slowing tains a completely revamped data path and includes a 16kbyte SRAM for cache and data storage. Four 20-Mbit/s sethroughput to 30 MIPS, but rial OS-link ports provide high-speed communications to

a single cycle and the floating-point unit has a two-cycle latency.

Targeting DSP applications, the SH-DSP includes dual 4-kbyte RAM blocks for parameter storage and a program ROM to store constants or algorithms. In addition to the SH integer processor, the chip includes a DSP unit that packs a high-performance multiplieraccumulator and other support logic. A three-address-bus architecture allows the integer unit and the DSP unit to simultaneously access two operands and one instruction every cycle, thus permitting sustained single-cycle operations for on-chip memory accesses.

Currently in definition, the SH-4 generation will take advantage of superscalar-architectural improvements to achieve throughputs of 300 MIPS when clocked at 200 MHz and powered by a 2.5-V supply. The processor will initially be targeted at multimedia and graphics applications and will be implemented using the company's 0.35-µm CMOS process.

Targeting many of the same appli-

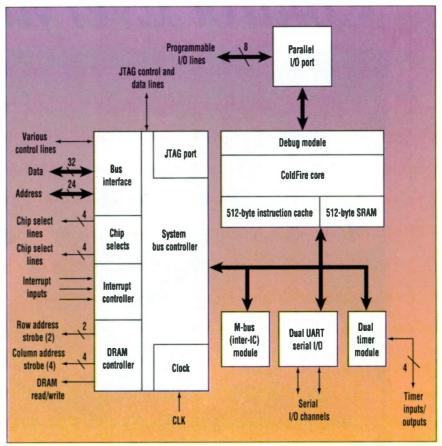

cations, from PDAs to communication systems, the ColdFire family from Motorola provides a scalable architecture based on a new RISC core. There are currently three versions of ColdFire available. The MCF5202 and 5203 are just CPUs with a 2-kbyte unified 4-way set-associative cache. a debug module, a bus controller, and a ITAG test port. The MCF5206 adds many peripheral support functions to the core to form a highly-integrated solution (Fig. 6).

Through the use of the variable-length instruction-set architecture, very dense code can be developed, thus reducing external memory requirements, allowing the use of slower and less expensive memories, possibly speeding up system throughput. When clocked at 33 MHz, the 5202/5203 can deliver a throughput of 25 MIPS.

The processor core consists of a simple arithmetic and logic unit with 16 user-

visible 32-bit-wide registers. The MCF5202 supports dynamic bus sizing for 8-, 16-, or 32-bit data interfaces. while the 5203 is limited to 8- and 16bit data widths since it uses a reduced bus interface that is only 16-bits wide.

The more feature-rich MCF5206 adds a DRAM controller, timers, parallel and serial interfaces, and all the benefits of the high level of integration. Like the 5202, the 5206 includes dynamic bus sizing for 8-, 16-, or 32-bit data widths and provides a glueless interface to DRAMs, SRAMs, ROMs, and I/O devices.

When clocked at 33 MHz, this version delivers a throughput of about 17 MIPS. The lower throughput could, in part, be due to the reduced cache size-this processor only contains a 512-byte direct-mapped instruction cache and a 512-byte SRAM.

Internally, the ColdFire core consists of two independent, decoupled pipeline structures-an instructionfetch pipeline (IFP) and the operand execution pipeline (OEP). The IFP is

#### **RISC PROCESSORS**

26 • SUPPLEMENT TO ELECTRONIC DESIGN • MARCH 3, 1997

### Don't Limit Your Product's Capabilities—Use Web Technology.

Visit us at http://smallest.pharlap.com to see how you can develop embedded applications that take full advantage of the web.

#### Making The Most Out Of Your Products

Phar Lap's TNT Embedded ToolSuite,<sup>®</sup> Realtime Edition, complete with Realtime ETS™ Kernel, now comes with our robust networking protocol—ETS TCP/IP! This cutting-edge feature allows your customers' mainframes, workstations, or PCs to communicate with products on the factory floor, in the lab, or at remote sites—all using Web technology!

As a result, electronic OEMs can use this technology to create intelligent machines

and instruments for an unlimited number of applications such as medical instruments, robotics, avionics equipment etc.

In addition, we support a variety of network protocols as well as industry standard tools such as Visual C++, Borland C++, CodeView, and Turbo Debugger.

Never Underestimate The Power Of The Web Because Phar Lap's TNT Embedded ToolSuite comes with development tools, a Realtime ETS Kernel and ETS TCP/IP, it is a one-stop shopping product with enormous power! To find out more, catch us on the "World's Smallest Web Server" today at URL <u>http://smallest.pharlap.com</u> or call a Phar Lap sales representative. Let your products realize the power of Web technology!

The 32-Bit x86 Experts

Embedded Development — Simply on Target™

Phar Lap Software, Inc. 60 Aberdeen Avenue, Cambridge, MA 02138 • Tel: (617) 661-1510 • Fax: (617) 876-2972 • http://www.pharlap.com

#### EMBEDDED SYSTEMS

a two-stage pipeline for prefetching instructions. Prefetched instructions are gated into the two-stage OEP, which decodes the instruction, fetches the required operands, and then executes the required function. The IFP and OEP are decoupled by an instruction buffer that serves as a FIFO queue. Therefore, the IFP can prefetch instructions in advance of their actual use by the OEP. That minimizes the time the CPU would be stalled waiting for instructions.

The DRAM controller on the chip supports up to 128 Mbytes of DRAM operating with either page-mode or extended-data-out interfaces. The serial interfaces include both a full-duplex dual UART and a separate Inter-IC-compatible Motorola bus (M-bus) interface.

For system debugging, all ColdFire processors include a debug interface that permits background mode debugging and real-time tracing.

Several other companies have developed proprietary 32-bit RISC processor cores that they plan to license. One such core is the CoolRISC processor developed by CSEM.

Designed to execute one instruction per clock cycle, the processor was optimized for low-power operation and can also be scaled for 8-, 16-, 24-, or 32-bit word sizes. Based on a threestage pipeline, the core includes an instruction set of 20 to 30 generic operations such as branch, call, return, load, store, and many others. With all the variations, the assembly-level command set contains a total of about 150 instructions.

Very efficient instructions give the CoolRISC much of its throughput by allowing various operations to take place in parallel. For example, two operands can be simultaneously addressed, whether they are stored in two registers, or one in a register and the other in the local RAM. Call and Return instructions can be executed with a hardware stack that contains as many program counters as desired (as determined by the ASIC designer). To avoid the growth of the chip's area in the event that many counters are needed, another software call operation can be used with a Branch and Link mechanism to form a stack in the integrated RAM.

#### **RISC PROCESSORS**

The processor core can be compiled with the design software tools for implementation in cell libraries with minimum features of 2, 1, or 0.7  $\mu$ m, and in the 1-µm process can achieve a throughput of about 20 MIPS when clocked at 20 MHz. The circuit is also very power efficient-an 8-bit version that employs an eight-word register file consumes just 0.3 mW/MHz when powered by a 3-V supply. Therefore, a 32-bit processor core might consume three to four times as much power, about 1 to 1.2 mW/MHz, depending on the additional logic added to the core.

#### **CONTROL IN REAL TIME**

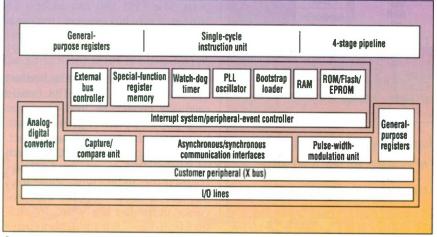

Additional RISC cores such as the ST20 from SGS-Thomson provide designers with a processor capable of delivering 40 MIPS with a 50-MHz clock. In addition to the basic processor functionality, the core has been designed with modularity in mind to achieve various levels of throughput (*Fig. 7*). Closely coupled to the RISC core is a hardware microkernel for real-time operations. The kernel provides multipriority process scheduling, trap/exception handling, I/O, DMA, interrupt, and timer support, as well as fast context switching (500 ns at 50 MHz).

Surrounding the ST20 core and microkernel to form the ST20-C4 core are an instruction preprocessor and an ALU accelerator. The accelerator includes an integer multiplier (up to 32by-32-bit multiplications in three cycles), a single-cycle barrel shifter, and single-cycle adder.

Another version of the core, the ST20C2, drops the ALU accelerator and merges some of the arithmetic functions into the ST20 core, thus reducing overall core area. SGS designers added a small register cache that makes up for some of the throughput lost by eliminating the accelerator. The register cache allows program variables to be cached, thus speeding up access to the variables as the executing software requires them.

The instruction preprocessor allows the core to use variable-length instructions that range in size from 8 to 32 bits. The variable-length commands are assembled by the preprocessor from the basic 8-bit commands, allowing programmers to minimize the amount of memory required to hold the application code, thereby reducing overall system cost.

Based on a VHDL model, the core and a companion VHDL-based macrocell library allow designers to configure an integrated processor very easily. An internal bus on the ST20-the OMI324 bus-allows simple interconnections of the blocks. The bus has been adopted by SGS-Thomson, Siemens, ARM, Matra, and Philips as a "standard" on-chip interconnect bus. The OMI324 bus permits high-speed communications between the core and peripheral blocks, with a latency of just two machine cycles and a 200-Mbyte/s bandwidth for access to onchip and off-chip memory.

Testability has also been integrated into the design process. The core includes a test access port that supports the IEEE 1149.1 JTAG test standard for boundary scan testing. The boundary scan capability can be used for boardlevel testing as well allowing the parallel scan-path testing of each block within the chip.

For even lower-cost applications, the company has stripped the core even more by eliminating many of the instructions, thus simplifying the logic and further reducing core area. The ST20-C1 is targeted at applications such as smart cards and other deeply embedded systems.

Testability has also been integrated into the design process. The core includes a test access port that supports the IEEE 1149.1 JTAG test standard for boundary scan testing. The boundary scan capability can be used for boardlevel testing as well allowing the parallel scan-path testing of each block within the chip.

Based on the ST20 core, the ST20450 processor is a more fleshed out CPU chip that designers can purchase. In addition to the ST20 core, the chip includes 16 kbytes of SRAM, a programmable memory interface, four high-speed serial communication links and the hardware microkernel. The integral microkernel reduces application development time, reduces memory requirements, and can eliminate the royalties typically paid for software kernels.

Originally published in the March 18, 1996 Electronic Design.

## SOME OF THE BEST NAMES IN THE BUSINESS WILL BE EXHIBITORS: AMD-Logic Products Division • Advanced

RISC Machines • AER Energy Resources • Analog Devices

Annabooks

Annasoft

AVX