A PENTON PUBLICATION \$10.00

APRIL 14, 1997

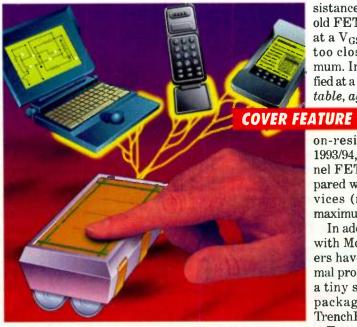

### **Dense MOSFET Enables Portable Power Control p. 45**

Display Works Conference Spotlights U.S. Manufacturing Advances p. 55 Analog/Mixed-Signal Standards Needed For Next-Generation Design Tools p. 65 Internet Protocols Migrate To Silicon For Networking Devices p. 87 FPGAs Take On The PCI Performance Challenge p. 111 The Ten Commandments Of Excellent Design: VHDL Code Examples p. 123 Merging Television With PCs—Which Display Is In The Picture? p. 141

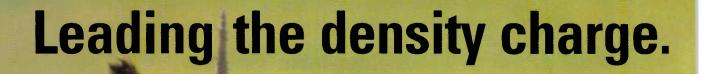

## Altera. The high-density programmable logic leaders.

With the largest programmable logic devices in the industry, Altera has charged ahead to provide you with the density to handle your

biggest designs. And we're committed to providing the greatest selection of high-density devices both now and in the future.

#### FLEX 10K. Leading the way.

Our FLEX 10K family broke the density barrier with the industry's first 100,000-gate programmable device. This family was also the first to feature an embedded array architecture. The fast and efficient FLEX 10K embedded array blocks let you pack up to 24K bits of RAM on-chip, with plenty of room to spare for complex logic functions.

Whether you use Verifog HDL or VHDL, the design flow is smooth and efficient — our MAX+PLUS II development tools are compatible with leading EDA tools. And the industry's largest selection of megafunctions is available to help speed your designs to market. From PCI functions to UARTs to FFTs, Altera's MegaCore functions and AMPP network combine to give you the building blocks you need to stay ahead with your designs.

| FEATURES      | 1910510 | EPP10020 | EFFICIESO | EPY109.40 | EPPIPICSO(V) | EFF10K70 | EPF10K100 |

|---------------|---------|----------|-----------|-----------|--------------|----------|-----------|

| TTPICAL GATES | 10 000  | 20 000   | 30,000    | 40,000    | 50,000       | 70,000   | 100 860   |

| MEMORY (Bits) | 6 144   | 12 288   | 12 288    | 16 384    | 20 480       | 18,432   | 24 576    |

#### Keep ahead of your competition.

To put high density and greater performance to work for you, contact Altera today. We'll send you our free megafunction technical literature package. Find out

how Altera can put you in charge of conquering your biggest design challenges!

www.altera.com) 1-800-9-ALTERA

Comparent 1997 Attent Corporation Altern ALX FLEK 10K MAX-PLUS & M-on-Cent AMPP Altera Magalunction Partners Program and specific dovice designations are trademarks and/or service marks of Altera in the United States and other countries All other trademarks and an interaction of their marks and other countries and other countries and the countries

READER SERVICE 96

## Fast IR. *Faster* delivery.

Count on volume shipments of HP's IrDA 4 Mbps IR module to build all the cableless applications your customers have been waiting for. Right away.

The next generation of IrDA - compliant modules has just arrived - and in the quantities you need. Introducing the 4 Mbps HP HSDL-1100.

Following on the success of our 115 Kbps module, HP has leveraged our proven R&D and high-volume IR module manufacturing expertise to deliver the new 4 Mbps product in quantity. That means you can now build products that enable access to LANs, fast graphics file transfer to and from computers and printers, transfer of digital camera imaging data to PCs and printers, and file transfer to and from phones and other mobile equipment. All without cables. HP designs products to the IrDA standard to ensure that your investment is protected through the past and future generations of IrDA products. What's more, HP cooperates with our partners to test our module with their interface ICs and software to guarantee full compatibility.

The result? Leadership you can count on for consistent quality, reliability and responsive service and support.

## Call 1-800-537-7715 ext.1058 for *free* product literature and our special offer for IR evaluation kits.

Call 1-800-450-9455 for a list of technical literature available by fax (U.S. and Canada).

Fast IR from HP– still easy to use. What are you waiting for?

**READER SERVICE 123**

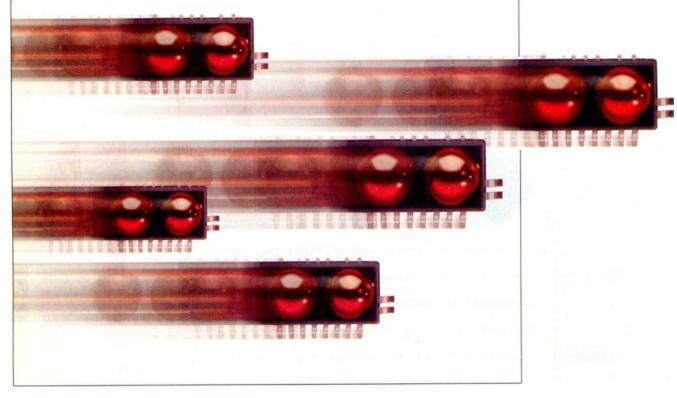

## WHAT'S OUR STRATEGY FOR DELIVERING THE BEST PROGRAMMABLE LOGIC? DIVIDE AND MULTIPLY.

Introducing Vantis", the programmable logic company from AMD that today delivers the most advanced and cost-effective programmable logic devices in the industry. The proof is in the product. Vantis MACH® devices

are the highest-performing family of CPLDs money can buy.

Armed with the world-class manufacturing might and global scope of its multi-billion dollar parent. Vantis is committed to be the world's best programmable logic company.

A tall order? Perhaps, but not when you consider all Vantis has to offer. Vantis knows more about PLDs than anyone. After all, we invented them.

Vantis. People you know. Technology you trust. Service you value. Get to market before your competition. Contact Vantis for more information. And watch your opportunities multiply. 1-888-826-8472 http://www.vantis.com

1 S

@1997 Vantis Corporation, Vantis is a trademark and AMD and MACH are registered trademarks of Advanced Micro Devices, Inc. All other product names are the property of their respective holders.

## 25 to 1910MHz SURFACE MOUNT VCO's from \$1395

Janini-Circuits

Mini-Circuits

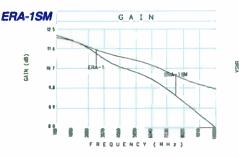

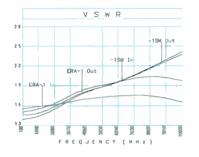

Time after time, you'll find Mini-Circuits surface mount voltage controlled oscillators the tough, reliable, high performance solution for your wireless designs. JTOS wide band models span 25 to 1910MHz with linear tuning characteristics, low -120dBc/Hz phase noise (typ. at 100kHz offset), and excellent -25dBc (typ) harmonic suppression. JCOS low noise models typically exhibit -132dBc/Hz phase noise at 100kHz offset, and phase noise for all models is characterized up to 1MHz offset. Miniature J leaded surface mount packages occupy

minimum board space, while tape and reel availability for high speed production can rocket your design from manufacturing to market with lightening speed. Soar to new heights...specify Mini-Circuits surface mount VCO's.

D.Mini-Circuits

| JTOS/JCOS SF                                                   | PECIFICATIO                                               | NS                                            |                                                 |                                 |                                                        |                                           |

|----------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------|-------------------------------------------------|---------------------------------|--------------------------------------------------------|-------------------------------------------|

| Model                                                          | Freq. Range<br>(MHz)                                      | Phase Noise<br>(dBc/Hz)<br>SSB@ 10kHzTyp      | Harmonics<br>(dBc)<br>. Typ.                    | V <sub>tune</sub><br>1V to:     | Current (mA)<br>@+12V DC<br>Max.                       | Price<br>\$ea.<br>(5-49)*                 |

| JTOS-50<br>JTOS-75<br>JTOS-100<br>JTOS-150                     | 25-47<br>37.5-75<br>50-100<br>75-150                      | -108<br>-110<br>-108<br>-106                  | -19<br>-27<br>-35<br>-23                        | 15V<br>16V<br>16V<br>16V        | 20<br>20<br>18<br>20                                   | 13.95<br>13.95<br>13.95<br>13.95          |

| JTOS-200<br>JTOS-300<br>JTOS-400<br>JTOS-535                   | 100-200<br>150-280<br>200-380<br>300-525                  | -105<br>-102<br>-102<br>-97                   | -25<br>-28<br>-25<br>-28                        | 16V<br>16V<br>16V               | 20<br>20<br>20<br>20                                   | 13.95<br>15.95<br>15.95<br>15.95          |

| JTOS-765<br>JTOS-1025<br>JTOS-1300<br>JTOS-1650<br>JTOS-1910   | 485-765<br>685-1025<br>900-1300<br>1200-1650<br>1625-1910 | -98<br>-94<br>-95<br>-95<br>-92               | -30<br>-28<br>-28<br>-20<br>-13                 | 16V<br>16V<br>20V<br>13V<br>12V | 20<br>22<br>30<br>30<br>20                             | 16.95<br>18.95<br>18.95<br>19.95<br>19.95 |

| JCOS-820WLN<br>JCOS-820BLN<br>JCOS-1100LN<br>Notes: *Prices fo | 780-860<br>807-832<br>1079-1114<br>r JCOS models          | -112<br>-112<br>-110<br>s are for 1 to 9 quar | -13<br>-24<br>-15<br>http://www.actionalization | 20V<br>14V<br>20V<br>ed to co   | 25 (@9V)<br>25 (@10V)<br>25 (@8V)<br>ver frequency ran | 49.95                                     |

Mini-Circuits

Mini-Circuits

See "RF/IF Designer's Guide" or "VCO Designer's Handbook" for complete specifications.

DESIGNER'S KITS AVAILABLE K-JTOS1 1 of each (10 pieces): JTOS-50, 75, 100, 150, 200, 300, 400, 535, 765, 1025, only \$149,95 K-JTOS2 1 of each (7 pieces): JTOS-50, 100, 200, 400, 535, 765, 1025, only \$99 K-JTOS3 2 of each (6 pieces): JTOS-1300, 1650, 1910, only \$114.95

Mini-Circuits®

P.O Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 INTERNET http://www. minicircuits. com For detailed specs on all Mini-Circuits products refer to • 740- pg HANDBOOK • INTERNET • THOMAS REGISTER • MICROWAVE PRODUCT DATA DIRECTORY • EEM

IA) SIZE

F 234 Rev Orig

CUSTOM PRODUCT NEEDS...Let Our Experience Work For You.

## ELECTRONIC DES

pril 14 1997 Volume 5. Number 8

#### EDITORIAL OVERVIEW

#### Dense MOSFET Enables Portable Power Control 45

- Display Works Conference Spotlights U.S. Manufacturing Advances 55

- Analog/Mixed-Signal Standards Needed For Next-Generation Design Tools 65

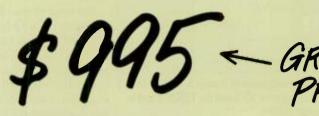

- Internet Protocols Migrate To Silicon For Networking Devices 87

- FPGAs Take On The PCI Performance Challenge 111

- The Ten Commandments Of Excellent Design: VHDL Code Examples 123

- Merging Television With PCs Which Display Is In The Picture? 141

#### TECH INSIGHTS

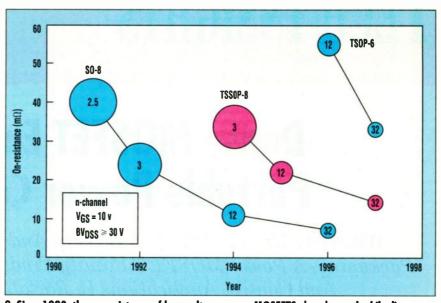

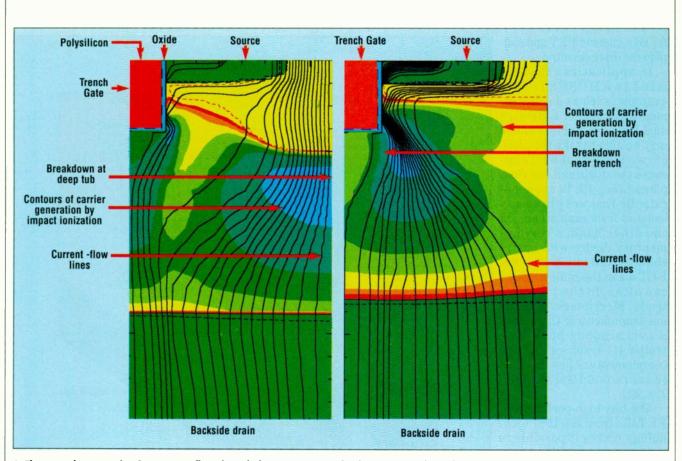

#### 45 Dense MOSFET Enables Portable Power Control

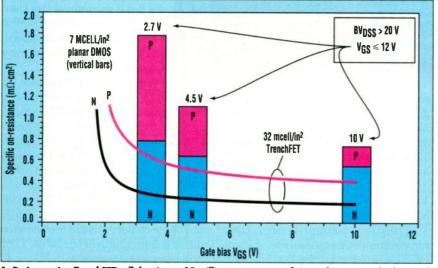

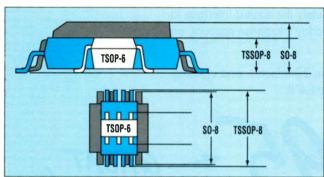

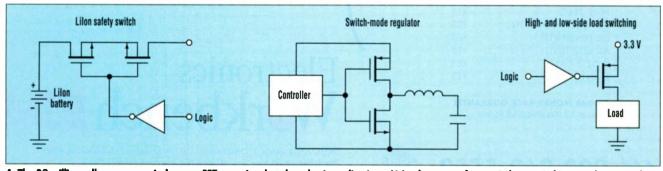

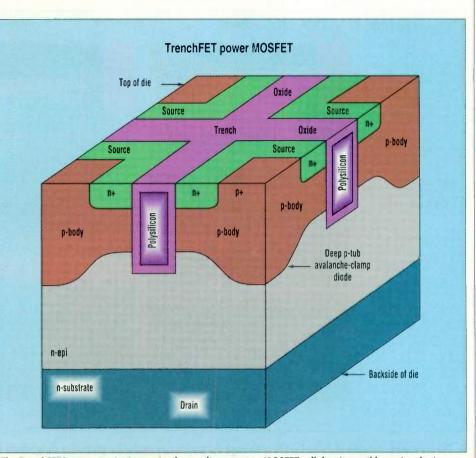

• With a 32 million cells/in.<sup>2</sup> density and new, space saving packaging, a power **MOSFET** family finds numerous switching and control applications

#### 55 Display Works Confab Details Manufacturing Advances

Advanced R&D funding in materials and tools allows domestic display makers to catch up with the competition.

#### **60** Product Features

in portable equipment.

#### EDA

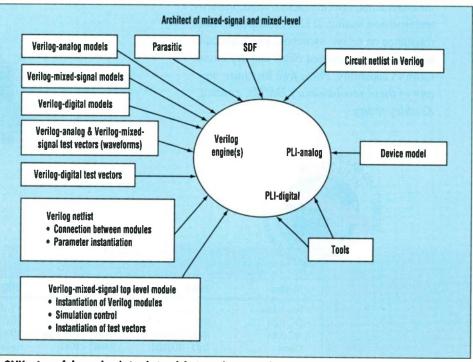

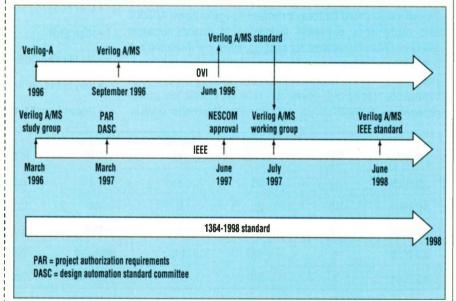

#### 65 Analog/Mixed-Signal Standards Needed For **Next-Generation Design Tools**

• Larger, more complex analog systems, coupled with the need for a common analog/digital design method, drives the development of a standardized mixed-signal language.

#### 76 EDA Watch

Block-based IP standards for chip design are merely the tip of the iceberg

**80** Product Features

#### EMBEDDED SYSTEMS

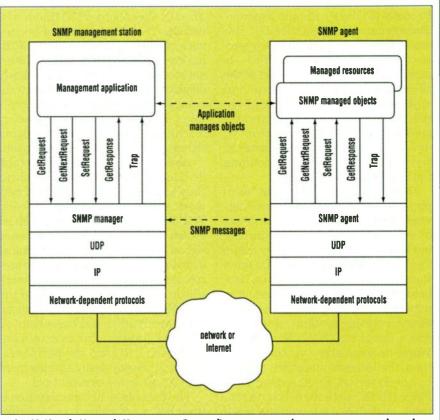

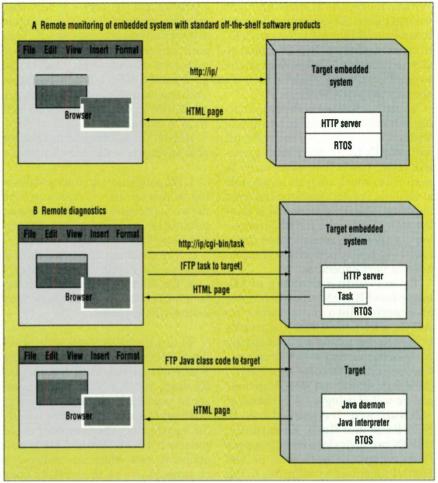

#### 87 Protocols Migrate For Networking Devices

Moving standards onto ASICs will bring "Net Toasters" to consumer applications.

ELECTRONIC DESIGN (ISSN 0013-4872) is published twice monthly except for 3 issues in May and 3 issues in October by Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543, Paid rates for a one year subscription are as follows: §105 U.S., \$185 Canada, \$210, \$255 International. Periodicals postage paid at Cleveland, OH, and additional mailing offices. Editorial and advertising addresses: ELECTRONIC DESIGN, 611 Route #46 West, Hasbrouck Heights, NJ 07604, Telephone (201) 393-6060. Facsimile (201) 393-0204. Printed in U.S.A. Title registered in U.S. Patent Office.

Copyright 1997 by Penton Publishing Inc. All rights reserved. The contents of this publication may not be reproduced in whole or in part without the consent of the copyright owner. For subscriber change of address and subscription inquiries, call (213) 696-7000. Mail your subscription requests to: Penton Publishing Subscription lockbox, P.O. Box 96732, Chicago, IL 60693. POSTMASTER: Please send change of address to ELECTRONIC DESIGN, Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543.

#### DEPARTMENTS

Upcoming Meetings .... 10 14, 16, 25, 30, 64EE, 64HH

Editorial .....18 • Embedded systems change the equation

Technology Briefing .....22 • The new EDA intellectual property

Technology

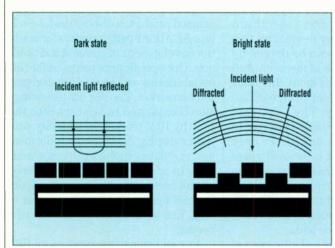

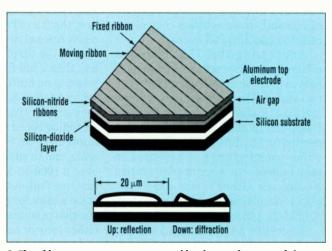

#### Technology Breakthrough ......33

• Development of digital MEMS-based display technology promises improved resolution, contrast, and speed

• Self-focusing infrared telescopic glasses may restore sight to millions

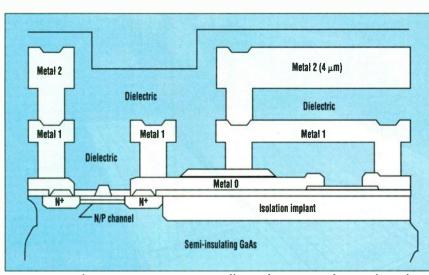

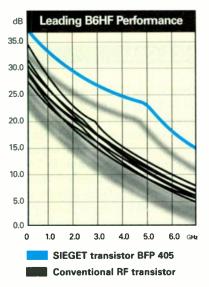

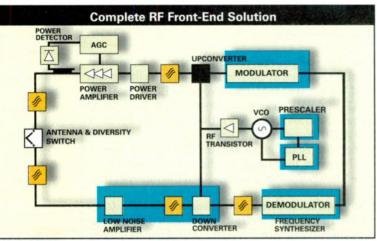

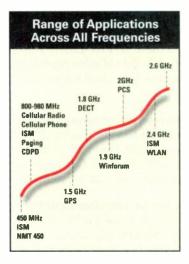

Advanced GaAs process integrates RF front-end functions

Info page ......8 (how to find us)

EE Currents & Careers . . 180

Index of Advertisers ... 192

Reader Service Card ..... 192A-D When you need a reliable source for IR components, QT Optoelectronics is hard to resist.

We have an extensive line of emitters, sensors, and switches. And if you can't find the component you need off-the-shelf, we can produce a custom IR product just for you.

Our technical support engineers can help you select the right component for your application. And our authorized distributors — in hundreds of cities around the world — can deliver that component on time and at a reasonable price.

How can you resist?

Call 800-LED-OPTO for more information and the phone number of your nearest QT Optoelectronics distributor, or see our on-line catalog at **www.qtopto.com**.

United States 800-533-6786 France 33 01/43.99.25.12 Germany 49 089/96.30.51 United Kingdom 44 [0] 1296/39.44.99 Asia/Pacific 603/735-2417

© 1997 QT Optoelectronics

# SIMPLY IRRESISTIBLE

## ELECTRONIC DESIG

April 14, 1997 Volume 45, Number 8

#### EDITORIAL OVERVIEW

#### EMBEDDED SYSTEMS

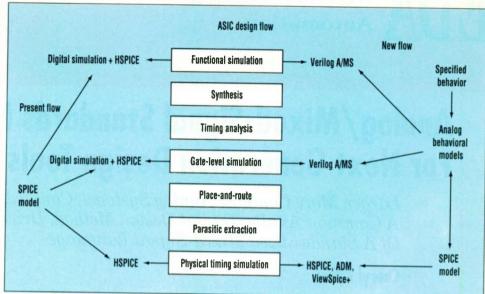

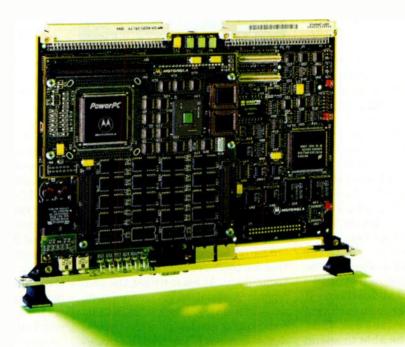

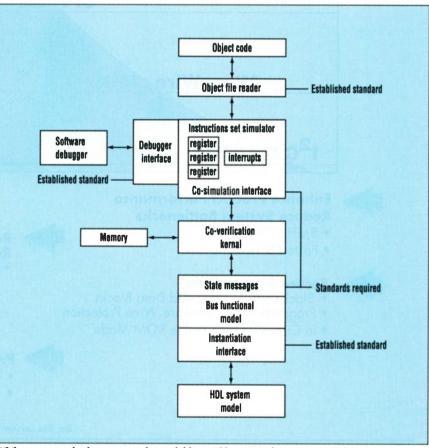

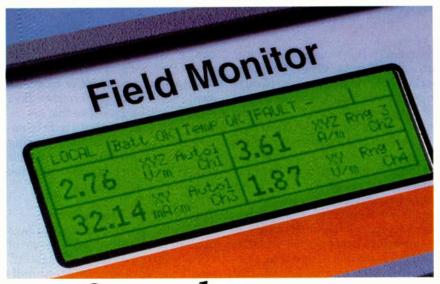

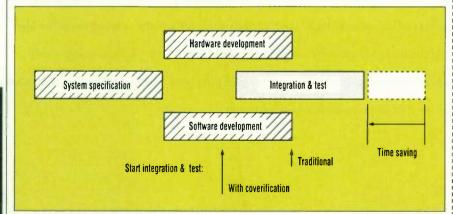

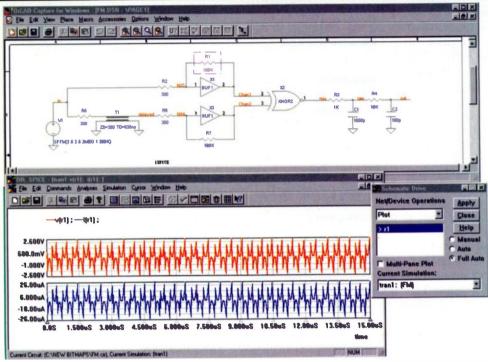

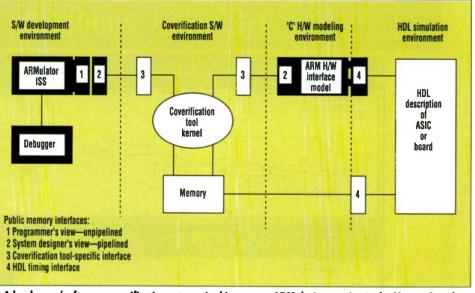

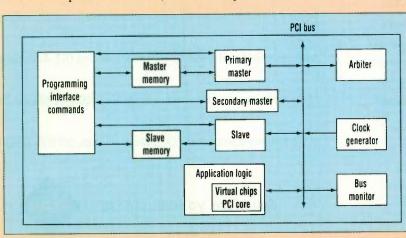

#### 96 Update On Coverification

• Coverification tools ease debugging of internal care-based ASIC code

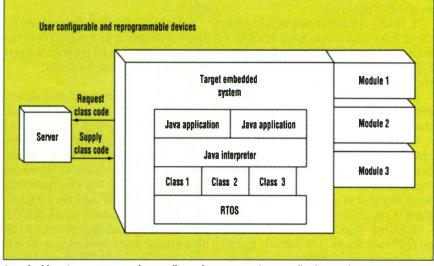

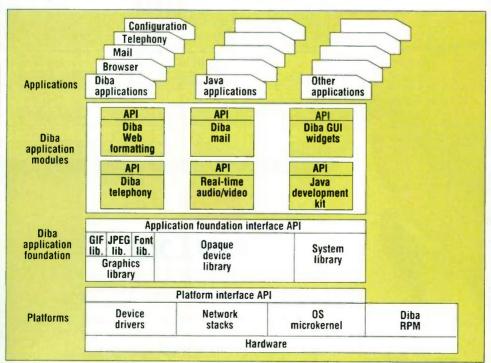

#### **102** Update On Modular Software

Modular software speeds development of web appliances for consumer use

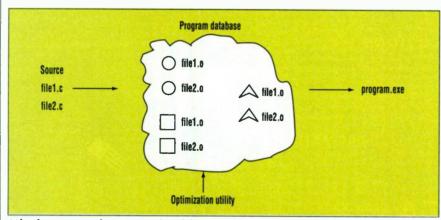

#### **108** Update On Code Optimization

• Profiling compiler automates code optimization process

#### **DIGITAL DESIGN**

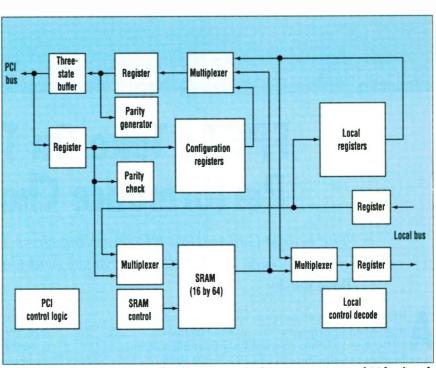

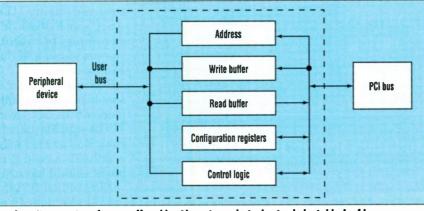

#### 111 FPGAs Take On The PCI Performance Challenge

• The latest generation FPGAs now have the density and performance to handle the speed and complexity of PCI.

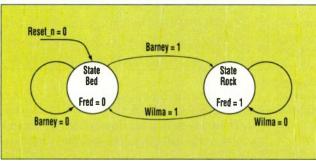

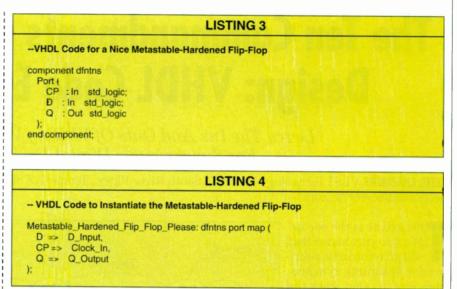

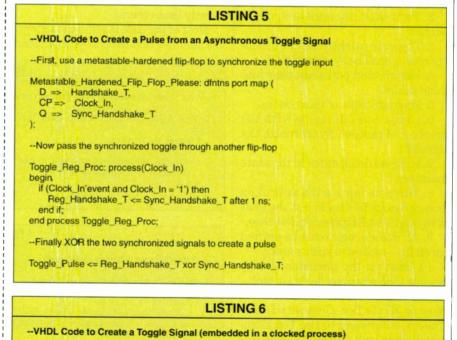

#### **123** The Ten Commandments Of Excellent Design: **VHDL Code Examples**

• Learn the ins and outs of writing VHDL code for synchronous digital designs.

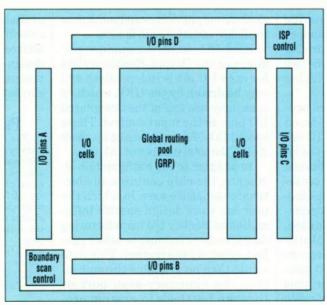

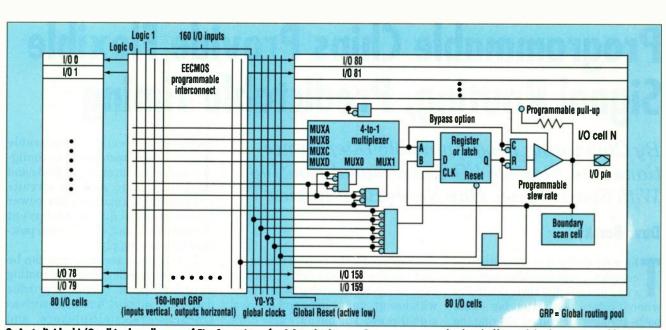

#### **129** Programmable Chips Provide Flexible Signal Routing, Predictable Timing

• By combining programmable interconnections and flexible I/O cells, signal routing with short delays has never been easier.

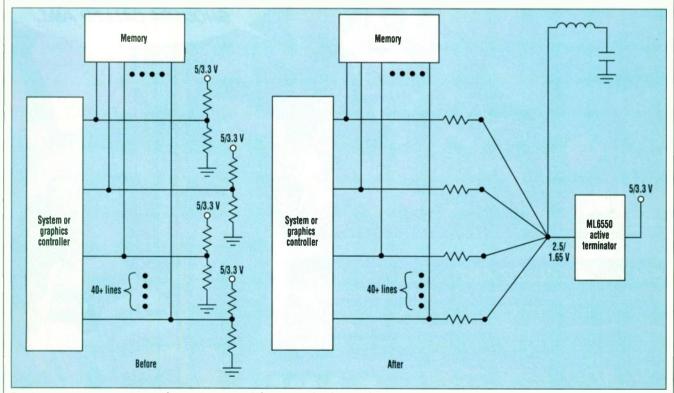

#### **132** Update On Active Termination Logic

• Logic protocol takes advantage of active memory bus terminator to speed data transfers

#### **134 Product Features**

#### **MULTIMEDIA**

#### 141 Merging Television With PCs — Which Display Is In The Picture?

• The battle for the home-viewing audience continues as PC monitors compete with the sharpness and quality of TV screens.

## Permission is granted to users registered with the Copyright Clearance Center Inc. [CCC] to photocopy any article, with the exception of those for which separate copyright ownership is indicated on the first page of the article, provided that a base fee of \$2 per covnership is indicated on the first page of the article, provided that a base teo 4 \$2 per copy of the article plus \$1.00 per page is paid directly to the CCC, 222 Rosewood Drive, Danvers, MA 01923 (Code No. 0013-4872/94 \$2.00 +1.00). Can. GST #R126431964. Canada Post International Publications Mail (Canadian Distribution Sales Agreement Number 344117). Copying done for other than personal or internal reference use without the express permission o<sup>f</sup> Penton Publishing, Inc. is prohibited. Requests for special permission or bulk orders should be addressed to the editor.

#### MULTIMEDIA

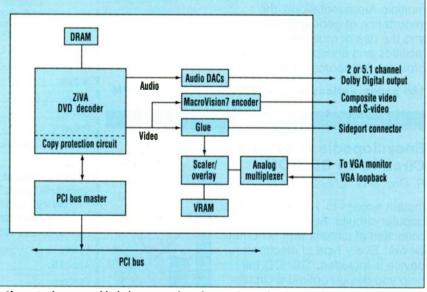

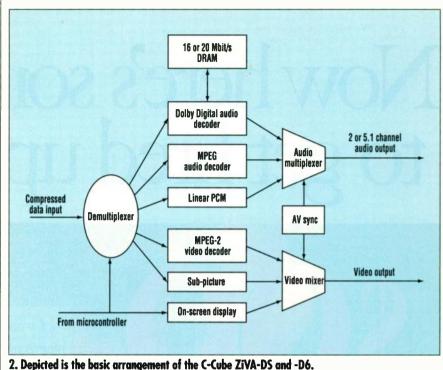

#### 148 Single-Chip DVD Decoders Permit User Customization

• A pair of DVD decoder ICs use microcoded architecture to give users a faster way to design, differentiate, and upgrade digital video consumer products.

#### **152** Product Features

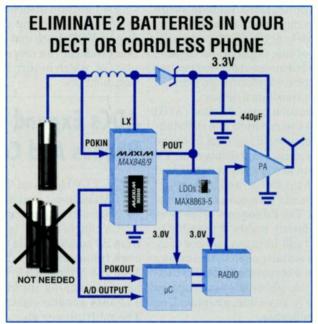

#### 155 Ideas For Design

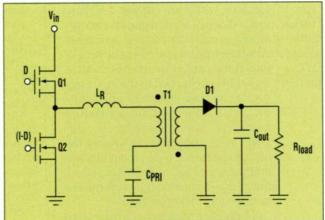

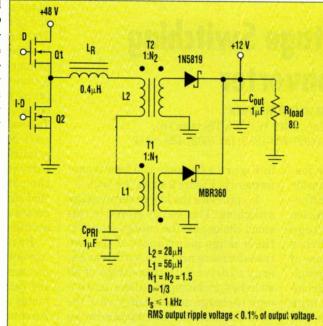

- Zero-voltage switching converter

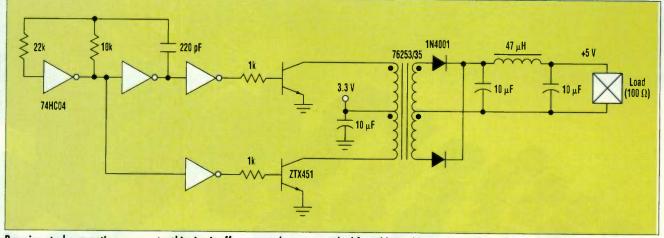

- Low-cost, isolated 5-V supply for 3.3-V logic

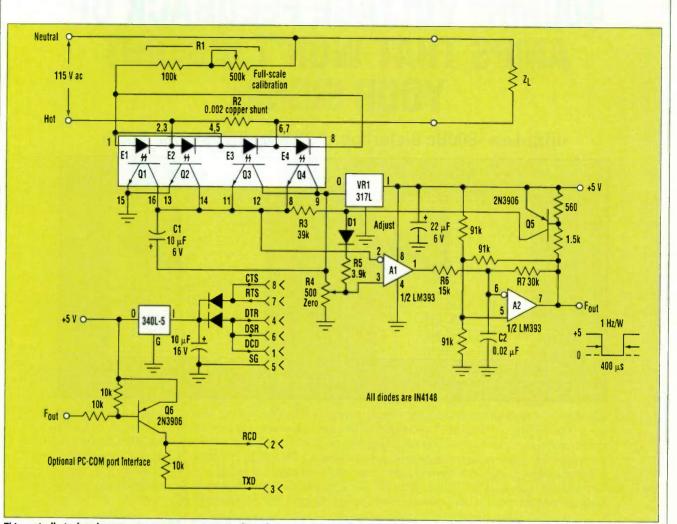

- Simple digital AC Wattmeter

- 163 Pease Porridge

- What's all this solution stuff, anyhow?

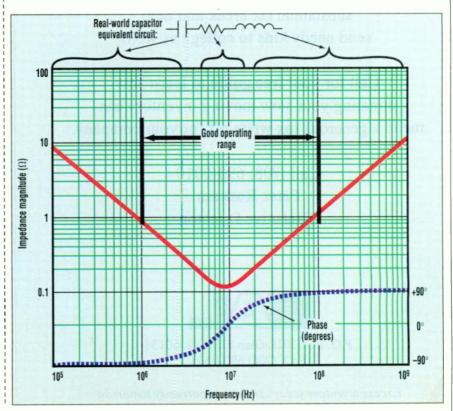

#### 167 Straight Talk For Serious Digital Designers

• Operating above resonance

#### 169 New Products

- Components

- Analog

- Instruments

- Software

- Digital ICs

- Communications—Focus On LAN/WAN

- **177** European Products

- **178 New Literature**

- **179** Designers Distributors Shelf

#### QUICKLOOK

| Market Facts63                                              |

|-------------------------------------------------------------|

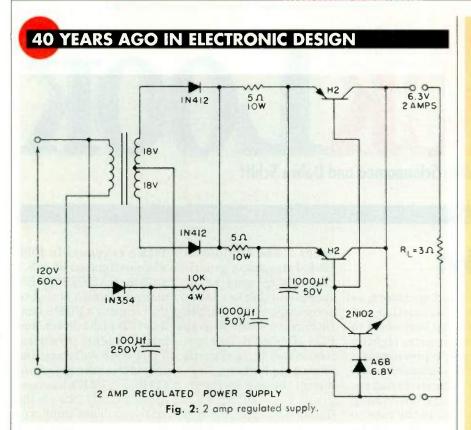

| 0 Years Ago64                                               |

| ye On ISO 900064                                            |

| he Internet Adds To<br>Nathematics Awareness<br>Veek        |

| ips On Investing64D                                         |

| adies And Gentleman,<br>harge Your Engines <mark>64E</mark> |

| he Envelope, Please64F                                      |

| nternet News64G                                             |

| wick News64H                                                |

| "Virtual" Face-To-Face<br>Neeting                           |

| rudel To Form64M                                            |

| off The Shelf64M                                            |

| nternet Rolodex64P                                          |

| ree Stuff64P                                                |

| onference Call64P                                           |

| etters From London64T                                       |

| ack To School64T                                            |

| ot PC Products64X                                           |

| COVER ILLUSTRATION BY:                                      |

BRUCE JABLONSKI

Jesse H. Neal Editorial Achievement

1967 First Place Award 1968 First Place Award 1972 Certificate of Merit 1975 Two Certificates of Merit 1989 Certificate of Merit 1976 Certificate of Merit

1978 Certificate of Merit 1980 Certificate of Merit 1986 First Place Award 1992 Certificate of Merit

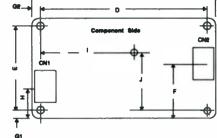

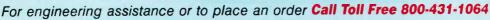

Low Profile .2" ht. Surface Mount Transformers & Inductors

All PICO surface mount units utilize materials and methods to withstand extreme temperature (220°C) of vapor phase, IR, and other reflow procedures without degradation of electrical or mechanical characteristics.

#### AUDIO TRANSFORMERS Impedance Levels 10 ohms

Impedance Levels 10 ohms to 10,000 ohms, Power Level 400 milliwatt, Frequency Response ±2db 300Hz to 50kHz. All units manufactured and tested to MIL-T-27.

#### POWER and EMI INDUCTORS Ultra-miniature Inductors are

Ultra-miniature Inductors are ideal for Noise, Spike and Power Filtering Applications in Power Supplies, DC-DC Converters and Switching Regulators. All units manufactured and tested to MIL-T-27.

#### PULSE TRANSFORMERS

10 Nanoseconds to 100 Microseconds. ET Rating to 150 Volt-Microsecond. All units manufactured

and tested to MIL-T-21038. Deliverystock to one week or send direct for Free PICO Catalog. Call toll free 800-431-1064 in NY call 914-738-14000 FAX 914-738-8225

43 Sparke Ave., Pelhem, N.Y. 10803-1889 E Mail-HLSC73A@prodigy.com

**READER SERVICE 161**

## ELECTRONIC DESIGN

#### NORTH AMERICAN EDITION

Executive Editor: ROGER ALLAN (201) 393-6057 rallan@class.org Managing Editor: BOB MILNE (201) 393-6058 bmilne@class.org

#### Technology Editors:

Analog: PAUL McGOLDRICK (San Jose) (408) 441-0550, ext. 113; 102447.346@compuserve.com

Analog & Power: FRANK GOODENOUGH (617) 227-4388 75410.2361@compuserve.com

Communications: LEE GOLDBERG (201) 393-6232 leeg@class.org

Power, Packaging, Components & Optoelectronics: PATRICK MANNION (201) 393-6097 pcmann@ibm.net

Computer Systems: RICHARD NASS (201) 393-6090 richnass@class.org

Design Automation: CHERYL AJLUNI (San Jose) (408) 441-0550, ext. 102; cjajluni@class.org

Digital ICs: DAVE BURSKY (San Jose) (408) 441-0550, ext. 105; dbursky@class.org

Embedded Systems/Software: TOM WIILIAMS (Scotts Valley) (408) 335-1509

tomwillm@ix.netcom.com

Test & Measurement: JOHN NOVELLINO (201) 393-6077 jnovelli@class.org

New Products: ROGER ENGELKE JR. (201) 393-6276 rogere@csnet.net

Contributing Products Editor: MILT LEONARD

Editorial Headquarters: (201) 393-6060 Fax: (201) 393-0204 E-mail: edesign@class.org P.O. Box 821, Hasbrouck Heights, N.J. 07604

Field Correspondents: West Coast Executive Editor: DAVE BURSKY (San Jose) (408) 441-0550, ext. 105; dbursky@class.org Western Regional Editors: CHERYL J. AJLUNI (San Jose) (408) 441-0550, ext. 102; cjajluni@class.org PAUL MCGOLDRICK (San Jose) (408) 441-0550, ext. 113; 102447.346@compuserve.com TOM WILLIAMS (Scotts Valley) (408) 335-1509 tomwillm@ix.netcom.com 2025 Gateway Place, Suite 354, San Jose, CA 95110 (408) 441-0550 Fax: (408) 441-6052

#### London: PETER FLETCHER

16 Maylons Road, Hextable, Kent, UK 44 1 322 664 355 Fax: 44 1 322 669 829 E-mail: panflet@cix.compulink.uk.co

Munich: ALFRED B. VOLLMER Eichenstr. 6, 82024 Taufkirchen (near Munich) Germany 49 89 614-8377 Fax: 49 89 614-8278 E-mail: 75162.1246@compuserve.com

Chief Copy Editor: MICHAEL SCIANNAMEA (201) 393-6024 mikemea@class.org Copy Editor: DEBRA SCHIFF (201) 393-6221 debras@csnet.net Consulting Editor: LISA MALINIAK

Ideas For Design Consulting Editor: JIM BOYD xl\_research@compuserve.com Contributing Editors: RON KMETOVICZ, ROBERT A. PEASE, WALT JUNG, HOWARD JOHNSON Production Manager: PAT A. BOSELLI, Production Coordinator: WAYNE M. MORRIS

Group Art Director: PETER K. JEZIORSKI, Associate Group Art Director: TONY VITOLO Staff Artists: LINDA GRAVELL, CHERYL GLOSS, JAMES M. MILLER Editorial Support Supervisor: MARY JAMES Editorial Assistant: ANN KUNZWEILER, BRADIE SUE GRIMALDO (San Jose)

Advertising Production:

(201) 393-6093 or Fax (201) 393-0410 Production Manager: EILEEN SLAVINSKY, Assistant Production Manager: JOYCE BORER Production Assistants: MYLAN CHU, BARBARA LATORRE, DORIS CARTER, JANET CONNORS, LUCREZIA HLAVATY Circulation Manager: BARBARA TILLETT (216) 931-9158 Reprints: ANNE ADAMS (216) 931-9626

#### Published by Penton Publishing

Electronic Design Information Group: Editorial Director: **STEPHEN E. SCRUPSKI** (201) 393-6070 Publisher: **JOHN G. FRENCH** (201) 393-6055

ELECTRONIC DESIGN / APRIL 14, 1997

Call, write, fax or yisit us on the Internet for your FREE CATALOG today!

CORPORATION

TSU

M CE

+85°C

TSU

M CE

+85 (

TSU

₩ r +85\*( 822K

100.E

**IN SCN**

C General Instrument

nicorductor

FAD

HOLT

Vellonal

0

0

0uF

(M)

υF

(M)

HAL

ONENTS

$\triangle E100\Omega s$

S

KTI 91

12.960 / CHI

Amph

AN

OT

U Technology, I

HEEGER

aghill

Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701-0677 Toll-Free: 1-800-344-4539 • Fax: 218-681-3380 Reader Service 112

Visit us on the Internet • http://www.digikey.com

## **Immediate Availability**

#### Sizes (brightness up to 250 nits):

- Modules: 7.8", 9.5", 10.4", 12.1"

- Full Monitors: 4", 5", 6"

Also, monochrome graphic, character and panel displays

## 408.523.8218

**READER SERVICE NUMBER166**

## **REACH THE MOST POWERFUL BUYING AUDIENCE IN OEM ELECTRONICS WORLDWIDE**

If you read Electronic Design and want to reach subscribers with a direct mail or telemarketing campaign, we can help. One of our in-house experts will work with you to select lists targeted especially for your products or services.

100% of Electronic Design subscribers are involved in the design and development of electronic products. Select Buyers and Specifiers in virtually every product category! Also select by Job Title, Employment Size, Job Function, Geography, Business/Industry.

BPA audited and guaranteed 99% deliverable. Call your advertising representative, or call 216-696-7000 and ask for the List Department. Fax requests to 216-696-6662. Ask for your FREE 74 page Penton Lists Catalog.

#### MEETINGS

#### MAY

**IEEE Vehicular Technology Conference** (VTC), May 5-7. Hyatt Regency at Civic Plaza, Phoenix, AZ. Contact Wendy Rochelle, IEEE Conference Services, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331; (908) 562-3870; fax (908) 981-1769; email: wrochelle@ieee.org.

International Test Synthesis Workshop, May 5-7. Santa Barbara, CA. Contact K. Wagner; (415) 694-4386; email: kwagner@symopsys.com.

IEEE Custom Integrated Circuits Conference (CICC '97), May 5-8. Santa Clara Convention Center, Santa Clara, CA. Contact Melissa Widerkehr, Widerkehr & Associates, Suite 270, 101 Lakeforest Blvd, Gaithersburg, MD 20877; (301) 527-0902; fax (301) 527-0994; e-mail: cicc96@aol.com.

Electronics Industries Forum of New England, May 6-8. World Trade Center, Boston, MA. Contact Summit Exhibition Management Inc., Norwalk CT; (800) 322-9332; (203) 855-3000; fax (203) 855-3003.

Ideas in Science & Electronics (ISE), May 6-8. Albuquerque Convention Center. Contact www.isetradeshow.com/ exhibit or call (505) 872-8020.

Nepcon Shanghai '97/Microelectronics Shanghai '97, May 6-9. Shanghai International Exhibition Centre, Shanghai, China. Contact Sarala Govindan, Export Div., Reed Exhibition Companies, 383 Main Ave., Norwalk, CT 06851; (203) 840-5355; fax (203) 840-9355.

**IEEE Power Industry Computer Applications Conference (PICA), May 11-16.** Contact T.C. Wong, American Electric Power, 1 Riverside Plaza, Columbus, OH 43215; (614) 223-2235; fax (614) 223-2205; e-mail: t.wong@ieee.org.

Third International Conference on Optical Fiber Submarine Telecommunication Systems (SubOptic'97), May 11-16. Contact Ida M. Espinoza, 340 Mt. Kemble Ave., S120, Morristown, New Jersey 07960; (201) 326-2119; fax (201) 326-2609; e-mail: iespinoza@attmail.com.

# It's no longer system-on-a-chip or time-to-market. With SPGAs, it's both.

#### System Programmable Gate Arrays...The new direction in high-level logic design.

Scream onto the new design highway called System Programmable Gate Arrays (SPGAs). Designing with programmable logic has never been like this!!

Talk about open road, SPGAs will begin at 50,000 gates and go up to 1,000,000. That's big enough to handle a complete system–logic, memory, and processor cores–on a single chip.

Take the express lane to fast time-to-market. SPGAs will be the most advanced, cost-efficient programmable targets for reusable soft IP blocks or hard-wired IP cores.

Drive your next system level design onto an SPGA. Feel the functionality, performance and cost-effectiveness never before achievable on a single programmable device.

Follow the signs to SPGAs. It's the high road to fast time-to-market *and* system-on-a-chip design.

To learn more about SPGAs, call 800-228-3532 or visit our web site.

WWW.ACTEL.COM

©1997 Actel Corporation. All rights reserved. Actel Corporation, 955 East Arques Avenue, Sunnyvale, CA 94086. Actel Europe Ltd. Daneshill House, Lutyens Close, Basingstoke, Hampshire, England RG24 8 AG. The Actel logo is a trademark of Actel Corporation.

Take it to a higher level

#### READER SERVICE 94

#### WE'LL TRY ANYTHING TO MAKE THINGS RUN WASTER.

TAKE OUR COMPANY UNIFORM, FOR EXAMP

Quick, list in order of importance the qualities in Synchronous DBAM, Speed, speed and h

Right. And everyone here at

which is now we're also sed with looking for

hew ways to speed thinks up.

Hybbbei's INNESERABLE achieve this goal. Not only to they make your applications run faster than EDO DRAMS, we make sure they get to you as

quickly as possible too. And because we spend 12% of

our revenues on R&D we're always going at full speed

in the race to develop newer, even faster memory chips. So, if you want 16M SDRAMs,

|      | SYNCHRO | NOUS  | DRAM MODULE  | S       |

|------|---------|-------|--------------|---------|

| Size | Config. | Volt. | Speed        | Refresh |

| 32MB | 4M x 64 | 3.3V  | 66/83/100MHz | 4k      |

| 32MB | 4M x 72 | 3.3V  | 66/83/100MHz | 4k      |

| 64MB | 8M x 72 | 3.3V  | 66/83/100MHz | 4k      |

and you want them in a hurry, call Hyundai Electronics

America at 408-232-8342, fax us at 408-232-8125, or visit us

at http://www.hea.com. The sooner the better.

Hyundai Electronics Industries Co. Ltd., Memory Business Division, Hyundai Building 140-2 Kye-Dong, Chongro-Ku, Seoul, Korea. Hyundai Electronics America, 3101 North First Street, San Jose, CA 95134

#### THE 16M SDRAM

#### MEETINGS

#### MAY

IEEE/IAS Industrial & Commercial Power Systems Technical Conference (I&CPS), May 12-15. Wynham Hotel, Philadelphia, PA. Contact Barry Hornberger, Philadelphia Electric Co., 2301 Market St., Bldg N3-1, Philadelphia, PA 19101; (215) 841-4619.

Fifth IFIP/IEEE International Symposium on Integrated Network Management (ISINM '97), May 12-16. Hotel Del Coronado, San Diego, CA. Contact Ann Marie Lambert, BBN Systems & Technologies, 10 Moulton St., Cambridge, MA 02138; (617) 873-3819; fax (617) 873-37776; e-mail: isinm97@bbn.com.

IEEE Particle Accelerator Conference, May 12-16. Vancouver, BC, Canada. Contact M.K. Craddock, TRIUMF, 4004 Wesbrook Mall, Vancouver, BC V6T 2A3 Canada; (604) 222-7341; fax (604) 222-7309; e-mail: craddock@triumf.ca.

Antennas: Principles, Design, and Measurements (Short Course), May 13-16. St. Cloud, FL. Contact Kelly Brown, NCEE, 1101 Massachusetts Ave., St. Cloud, FL 34669; fax (407) 892-0406.

IEEE Radar Conference, May 13-15. Sheraton University Hotel & Con ference Center, Syracuse, NY. Contact Michael Wicks, Rome Laboratory, 26 Electronics Pkwy., Rome, NY 13441; (315) 330-4437; fax (315) 330-2528; e-mail: wicksm@rl.af.mil.

Sensors Expo Boston, May 13-15. Hynes Convention Center, Boston, MA. Contact Expocon Management Associates Inc. (203) 256-4700; email: sensors@expocon.com; Internet: http://www.expocon.com.

47th Electronic Components & Technology Conference, May 18-21. The Fairmont Hotel, San Jose, CA. Contact Jim Bruorton, Electronic Industries Association, 2500 Wilson Blvd., Arlington, VA 22201-3834; (864) 963-6621.

Finishing '97 Conference & Exposition, May 19-22. Rosemont Convention Center, Rosemont (Chicago), IL. Contact Society of Manufacturing Engineers; (800) 733-4763. 19th IEEE International Conference on Software Engineering, May 19-23. Boston, Massachusetts. Contact W. Richard Adrion, Deptartment of Computer Science, University of Masachusetts/Amherst, 307 LGRC, Post Office Box 34610; Amherst, Massachusetts 01003-4610; (413) 545-2742; e-mail: adrion@cs.umass.edu.

IEEE Instrumentation & Measurement Technology Conference (MTC '97), May 20-22. Chateau Laurier, Ottawa, Ontario, Canada. Contact Robert Myers, Conference Coordinator, 3685 Motor Ave., Suite 240, Los Angeles, California 90034; (310) 287-1463; fax (310) 287-1851; e-mail: bob.myers@ieee.org.

**OEMed Midwest, May 21-22.** Rosemont Convention Center, Rosemont, IL. Contact Exposition Excellence Corp., 112 Main St., Norwalk, CT 06851; (203) 847-9599; fax (203) 854-9438.

**DEM Electronics Midwest, May 21-22.** Rosemont Convention Center, Rosemont, IL. Contact Exposition Excellence Corp., 112 Main St., Norwalk, CT 06851; (203) 847-9599; fax (203) 854-9438.

**Canadian Conference on Electrical & Computer Engineering, May 25-28.** Delta Hotel, Newfoundland, Canada. Contact David Collett, Newfound land & Labrador Hydro, P.O. Box 12400, St. Johns, NF, A1A 4K7, Canada; (709) 737-1372; fax (709) 737-1782; e-mail: t.d.collett@ieee.org.

Fifth IEEE International Conference on Properties & Applications of Dielectric Materials (ICPADM), May 25-30. Sheraton Walker Hill, Convention Center, Seoul, Korea. Contact Joon-Ung Lee, Department of Electrical Engineering, Kwangwoon University, 447-1 Wolgye-Dong, Nowon-Ku, Seoul, 139-701, Korea; (82)-2-910-5144; fax (82)-2-942-0107.

Next Generation Telephony West: Voice Over the Internet, May 28-30. Hotel Monaco, San Francisco, California. Contact (800) 822-6338 or (202) 842-3022 ext.317; Internet: http://www.brp.com.

#### JUNE

IEEE International Conference on Neural Networks, June 1-5. Houston, TX. Contact Nicolaos B. Karayiannis, Dept. of Electrical & Computer Engineering, University of Houston, Houston, TX; 77204-4793 (713) 743-4436; fax (713) 743-4444.

International Symposium on VSLI Technology, Systems, and Applications, June 3-5. Grand Hyatt Hotel, Taiwan, China. Contact T. P. Ma, Dept. of Electrical Engineering, Yale University, 15 Prospect St., New Haven, CT 06520-8284; (203) 432-4211; fax (203) 432-7769.

Mixed Signal Test Workshop; June 3-6. Seattle, WA. Contact M. Soma; (206) 685-3810; e-mail: soma@ee.washington.edu.

American Control Conference (ACC '97), June 4-6. Albuquerque Convention Center, Albuquerque, New Mexico. Contact Steven Yurkovich, Department of Elec. and Engrg., The Ohio State Univ., 2015 Neil Avenue, Columbus, Ohio 43210; (614) 292-2586; fax (614) 292-7596; e-mail: s.yurkovich@i.ee.org.

IEEE International Conference on Communications (ICC 97), June 8-12. Montreal, Canada. Contact Celia Desmond, Stentor, Fl. 6b, 33 City Center Dr., Mississauga, Ontario L5B 2N5, Canada; (905) 615-6507; fax (905) 615-8421; e-mail: celia.desmond@tc.resonet.com.

IEEE/MTT-S International Microwave Symposium (MTT 97), June 8-13. Convention Center, Denver, CO. Contact John Dunn, Dept. of Electrical & Computer Engineering, University of Colorado, Campus Box 425, Boulder, CO 80309; (303) 492-5920; fax (303) 492-5323; e-mail: dunn@boulder.colorado.edu.

IEEE International Symposium on Circuits & Systems (ISCAS 97), June 9-12. Hong Kong Convention & Exhibition Centre, Hong Kong. Contact ISCAS '97 Secretariat, Department of Electrical & Electronic Engineering, University of Hong Kong, Pokfalam Rd., Hong Kong; (852) 28592710; fax (852) 25598738; email: iscas97@hkueee.hku.hk.

### Today's SDH/SONET standards can be daunting. Tektronix introduces the light at the end of the tunnel.

The ST2400 – configurable, affordable SDH/SONET broadband testing from Tektronix.

The ST2400 provides the latest in SDH/SONET test requirements for your development efforts. OC-48/STM-16 bandwidths permit testing of the most current communications requirements. In addition, our industry-leading optics performance provides the tools needed for testing the latest WDM applications.

For a good look at the future of SDH/SONET development, call 1-800-426-2200, press 3 and request code 3002 today, or visit us at www.tek.com

#### MEETINGS

#### JUNE

34th Design Automation Conference (DAC '97), June 9-13. Anaheim Convention Center, Anaheim, California Contact MP Associates Inc., 5305 Spine Rd., Suite A, Boulder, CO 80301; (303) 530-4333; fax (303) 530-4334.

**ASIA TELECOM '97 (TIA), June 9-14.** Singapore, Asia. Contact (703) 907-7736.

IEEE International Conference on Consumer Electronics (ICCE), June 11-13. The Westin Hotel O'Hare, Rosemont, IL. Contact Diane D. Williams, 67 Raspberry Patch Dr., Rochester, NY 14612-2868; (716) 392-3862; fax (716) 392-4397.

Virginia Tech/MPRG Symposium on Wireless Personal Communications, June 11-13. Campus of Virginia Tech, Blacksburg, VA. Contact MPRG Conference Coordinator Jenny Frank (757) 686-3765, or Jack Lilly, (540) 231-4849. International Solid-State Sensors and Actuators Conference (Transducers 97), June 15-19. Hyatt Regency Hotel, Chicago, Illinois. Contact Kensal D. Wise, 1246 EECS Building, University of Michigan, 1301 Beal Avenue, Ann Arbor, Michigan 48109-2122; (313) 764-3346; fax (313) 747-1781.

IEEE Digital Cross Connect Systems Workshop VII (DCS 97), June 16-19. Banff Park Lodge, Banff, Alberta, Canada. Contact James H. Simester, Lucent Technologies, Post Office Box 3030, Room 4J-526, 101 Crawfords Corner Rd., Holmdel, New Jersey 07733-3030; (908) 949-7336; fax (908) 949-2724; e-mail: sims@bostare.ho.att.com.

Third Conference on Object-Oriented Technologies & Systems (Coots 97), June 16-19. Marriott Hotel, Portland, OR. Contact USENIX Conference Office, 22672 Lambert Street, Suite 613, Lake Forest, California 92630; (714) 588-8649; fax (714) 588-9706; e-mail:

conference@usenix.org; Internet: http://www.usenix.org.

IEEE International Conference on Systems, Man, and Cybernetics, June 16-20. Hyatt Orlando, Orlando, FL. Contact James M. Tien, Chair, DSES Department, Rensselaer Polytechnic Institute, Troy, New York 12180-3590; (518) 276-6486; fax (518) 276-8227; e-mail: tienj@rpi.edu.

IEEE/ASME International Conference on Advanced Intelligence Mechatronics, June 16-20. Contact Hideki Hashimoto, Institute of Industrial Science, University of Tokyo, 7-22-1, Roppongi, Minato-ku, Tokyo 100, Japan; (81) 3 3402 6231 ext. 2359; fax (81) 3 3423 1484.

IEEE Sixth International Fuzzy Systems Conference, June 20-25. Barcelona, Spain. Contact Ramon Lopez De Mantaras, IIIA-CSIC Campus U.A.B., 08193 Cerdanyola del Valles, Spain; (34) 3-580-95-70.

#### Advertisement

## Small Company's New Golf Ball Flies <u>Too</u> Far; Could Obsolete Many Golf Courses

Pro Hits 400-Yard Tee Shots During Test Round

Want To Shoot An Eagle or Two?

By Mike Hensen

YALESVILLE, CT - A small golf company in Connecticut has created a powerful, new ball that flies like a U-2, putts with the steady roll of a cue ball and bites the green on approach shots like a dropped cat. But don't look for it on weekend TV. Long-hitting pros could make a joke out of some of golf's finest courses with it. One pro who tested the ball drove it 400 yards, reaching the green on all but the longest par-four's. Scientific tests by an independent lab using a hitting machine prove the ball out-distances ten major brands dramatically.

The ball's extraordinary distance comes partly from a revolutionary new dimple design that keeps the ball aloft longer. But there's also a secret change in the core that makes it rise faster off the clubhead. Another change reduces air drag. The result is a ball that gains altitude quickly, then sails like a glider. None of the changes is noticeable in the ball itself.

Despite this extraordinary performance, the company has a problem. A spokesman put it this way: "In golf you need endorsements and TV publicity. This is what gets you in the pro shops and stores where 95% of all golf products are sold. Unless the pros use your ball on TV, you're virtually locked out of these outlets. TV advertising is too expensive to buy on your own, at least for us.

"Now, you've seen how far this ball can fly. Can you imagine a pro using it on TV and eagle-ing parfour's? He would turn the course into a par-three, and real men don't play par-three's. This new flypower forces us to sell it without relying on pros or pro-shops. One way is to sell it direct from our plant. That way we can keep the name printed on the ball a secret that only a buyer would know. There's more to golf than tournaments, you know."

The company guarantees a golfer a prompt refund if the new ball doesn't cut five to ten strokes off his or her average score. Simply return the balls-new or used-to the address below. "No one else would dare do that," boasted the company's director.

If you would like an eagle or two, here's your best chance yet. Write your name and address and "Code Name S" (the ball's R&D name) on a piece of paper and send it along with a check (or your credit card number and expiration date) to National Golf Center (Dept. S-375), 60 Church Street, Yalesville, CT 06492. Or phone 800-285-3900 anytime. No P.O. boxes. One dozen "S" balls cost \$24.95, two to five dozen are only \$22.00 each, six dozen are only \$109.00. You save \$40.70 ordering six. Shipping and handling is only \$4.50 no matter how large your order. Specify white or Hi-Vision yellow.

## Our new Flash DSPs can change as quickly as you do.

At Texas Instruments we understand your product designs and features are always changing. That's why we're introducing the TMS320F206, the first affordable fixed-point DSP with on-chip flash memory. Lower overall system costs and the flexibility of last-minute modifications or field upgrades are now possible due to the in-system programmability of the Flash DSP.

The 'F206 is a member of our new TMS320C2xx generation, which offers DSPs with five configurations of on-chip memory that include flash, RAM or ROM. These devices deliver up to 40-MIPS performance, low power dissipation and code compatibility with the 'C1x, 'C2x and 'C5x generations — all at a very affordable price. Also, most 'C2xx devices are pin-for-pin compatible to allow for easy upgrades.

When you have to make quick design changes, TI DSP Solutions, including the new Flash DSPs, are ready whenever you are.

#### TMS320 Flash DSP

- 40-MIPS performance

- · 32K x 16 words on-chip flash

- 4.5K x 16 words RAM

- 100-pin TQFP package

- 8-bit UART and 16-bit synchronous serial port

- Glueless interface to TLC320AD55 codec

Visit our DSP Selutions home page, http://www.ti.com/dsp/4060, or cell 1-800-477-8924, ext. 4060.

### ÿ

EXTENDING YOUR REACH"

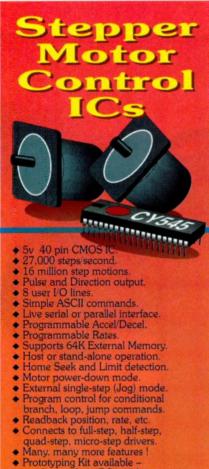

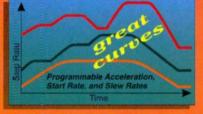

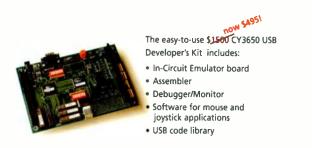

can be run from PC serial port.

The **CY545** is available from stock @ \$75/each, \$50/25, \$45/100, \$25/1k.

The **CY550** is similar to the CY545, with additional on-the-fly interactive control for systems requiring complex motions. Available from stock @ \$95/each. \$75/25, \$57/100, \$30/1k.

CYB-5xx prototyping kit is available starting at \$150. Add CY545 or CY550 chip. Wirewrap area for custom driver circuit. LEDs on motor signals and userbit outputs. Optional 8-character status display, memory, and serial cable available. Free catalog on Control ICs.

#### **ELECTRONIC DESIGN**

EDITORIAL

## **Embedded Systems Change The Equation**

While walking around the exhibitor booths at last month's Embedded Systems Conference East show in Boston, Mass., I couldn't help but notice the profound difference between how the electronics industry did business a couple of decades ago and today. Back then, the word "embedded" conjured up images of largely military applications; for example, a computer board embedded within a fighter aircraft's countermeasures electronics, or a microprocessor embedded in a tank's fire-control system.

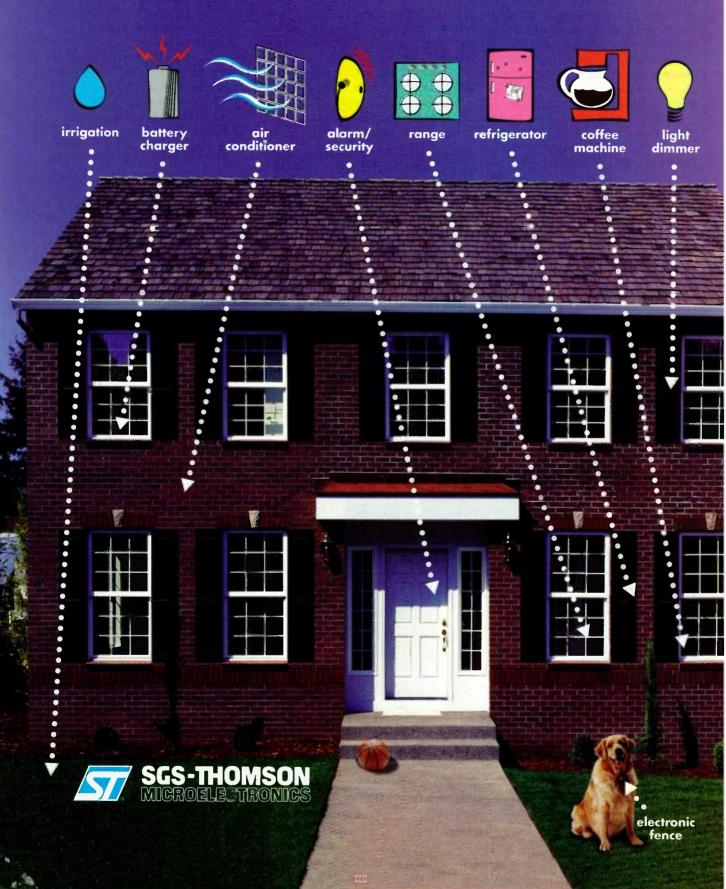

But with the continuous decline in the cost of hardware ICs and the increasing sophistication in the performance levels of these chips, new market opportunities have rapidly opened up in consumer, automotive, industrial, commercial, and communications sectors. This means that OEM designers must not only satisfy challenging technical performance requirements, they also must know their end-user applications that can be as varied as an office or home fax machine, a bank ATM, or a sophisticated factory floor controller. The home is seen as a potentially huge future market for embedded microcontrollers. For example, it is estimated that the average middle-class consumer household now has about 30 embedded microprocessors in various devices and appliances, a number that is projected to grow rapidly.

Electronics technology has thus become very pervasive. As a result, the design equation also has changed. It used to be that hardware engineers were mostly responsible for circuit designs. In some cases, one or two hardware engineers were all that were needed for a design. The challenge now is for both hardware and software designers to work closely together to come up with innovative solutions. No longer is electronic design a one-person show. It's truly a team effort, and a multidisciplinary one at that. Packaging, test, mechanical, and industrial designers are frequently involved.

Advanced 32- and 64-bit CISC and RISC processors, flash memory, and various forms of logic are readily available to suit many applications. But these advanced hardware devices can only work within the right software design environment. They're only as good as the software languages and programming techniques, the simulation and emulation tools, the operating system, and the development environment that make possible getting the most performance out of hardware components. On the other hand, software designers might just as well "sit on their hands" if they didn't have the latest hardware elements with which they can ply their magic. What all this means is that the average engineer today must have a wider view of issues that often go far beyond his or her primary areas of expertise. *rallan@class.org*

5V & 3.3V FCT LOGIC • 3.3V LCX LOGIC • QUICKSWITCH<sup>®</sup> PRODUCTS • CLOCK MANAGEMENT ANALOG PRODUCTS • QUICKSCAN<sup>®</sup> (JTAG) PRODUCTS • SPECIALTY MEMORIES • NETWORKING PRODUCTS

# FIFOS

## QSI — FIFOs for today's advanced applications!

Today's advanced computer and workstation designs require sophisticated solutions. QSI offers you a choice of advanced high-performance FIFO devices that will take you into the future — x9 asynchronous FIFOs, x9, x18, x36 Clocked FIFOs, and x36 Clocked BiFIFOs.

**Better Functionality**. QSI's advanced FIFOs offer unique functionality enhancements over others the fastest standard asynchronous FIFOs, clocked architectures, programmable flags, and 66-MHz operating frequency, plus state-of-the-art packaging.

Seeing is Believing. Call 1-800-609-3669, or fax today to 408-496-0773 for a copy of the FIFO data book.

QSI — your first choice for high-performance FIFOs.

| Device          | Description                                  | Pins     |

|-----------------|----------------------------------------------|----------|

| Asynchronous I  | FIFOs                                        |          |

| Q\$7201         | 512 x 9 with Buffer Memory                   | 32, 28   |

| Q\$7202         | 1K x 9 with Buffer Memory                    | 32, 28   |

| Q\$7203         | 2K x 9 with Buffer Memory                    | 32, 28   |

| Q\$7204         | 4K x 9 with Buffer Memory                    | 32, 28   |

| Clocked x9 FIF  | Os                                           |          |

| Q\$72211        | 512 x 9 Parallel Synchronous                 | 32       |

| Q\$72221        | 1K x 9 Parallel Synchronous                  | 32       |

| Q\$72231        | 2K x 9 Parallel Synchronous                  | 32       |

| Q\$72241        | 4K x 9 Parallel Synchronous                  | 32       |

| Clocked x18 FIF | FOs                                          |          |

| Q\$72215        | 512 x 18 Parallel Synchronous                | 68       |

| Q\$72225        | 1K x 18 Parallel Synchronous                 | 64       |

| Clocked x36 FIF |                                              |          |

| Q\$723611       | 512 x 36 x 2 Bidirectional Clocked FIFO      |          |

|                 | with Dynamic Bus Sizing                      | 144      |

| Q\$723620       | 1K x 36 Clocked FIFO with Dynamic Bus Sizing | 132      |

| Q\$723621       | IK x 36 x 2 Bidirectional Clocked FIFO       |          |

|                 | with Dynamic Bus Sizing                      | 144      |

| Q\$725420A      | 256 x 36 x 2 Bidirectional Clocked FIFO      | 132, 144 |

U.S.A. Headquarters: 851 Martin Avenue, Santa Clara, CA 95050, 408-450-8000, Fax: 408-496-0773, http://www.qualitysemi.com European Headquarters: Suite A, Unit 6, Mansfield Park, Four Marks, Hampshire, GU34 5PZ United Kingdom, 44-(0)1420-563333, Fax: 44-(0)1420-561142 U.S. and Canadian Distributors: Arrow Electronics, Bell Industries, Inc., Nu-Horizons, Zeus Electronics Ocopyright 1996 Quality Semiconductor, Inc. Q and QS are trademarks of Quality Semiconductor, Inc.

**READER SERVICE 191**

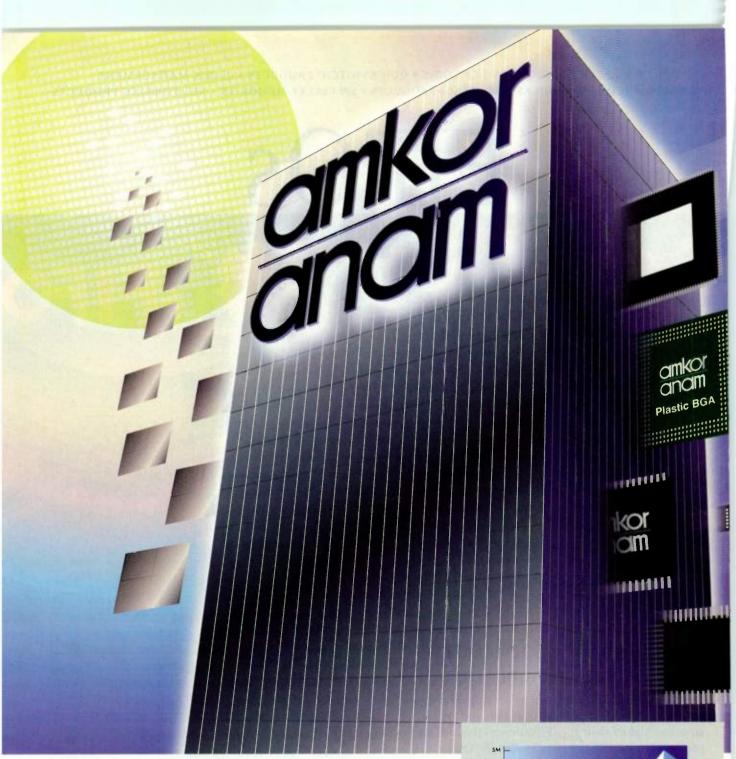

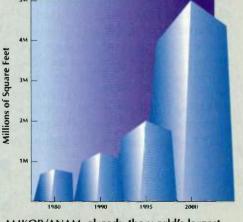

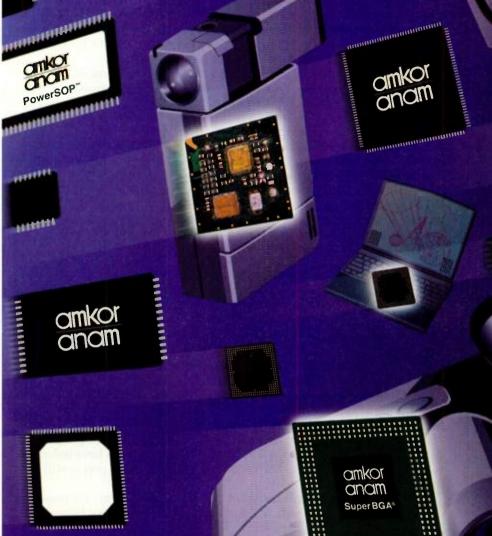

## WE'RE PACKAGING THE FUTURE

AMKOR/ANAM has been packaging the future for over 25 years. Today, more companies look to us for IC assembly, test and new package ideas than anyone else. That's because we've *always* been ready to do whatever it takes to earn and keep our customers' business. What about you? Need more IC packaging capacity right now, next year, five years from now? You can be sure we'll be your strongest supporter — regardless of market conditions. In fact, AMKOR/ANAM dedicates more state-of-the-art equipment per square foot of IC factory space

AMKOR/ANAM, already the world's largest IC package foundry will more than double its production capacity by the year 2000.

1111111

to you than anyone else in the world. And with the addition of new facilities in the Philippines, Korea and the USA, we're growing even stronger.

Need IC test services? From wafer probe to drop shipping no one is more capable or more thorough than AMKOR/ANAM.

And if you're serious about moving your products into the 21st Century, count on our design team to lead the way. Semiconductor manufacturers and OEMs already recognize powerful, patented *Super*BGA®, ultra-small Chip Scale and other AMKOR/ANAM package innovations as pathways to the future.

Whether you need extra IC production capacity, industryleading IC test services or cutting edge package designs, get in touch with the company that is packaging the future. AMKOR/ANAM. Visit our web site for the location of the service center nearest you: http://www.amkor.com or call: 602-821-2408, ext. 2000.

READER SERVICE 98

amkor anam

UBGAT

#### TECHNOLOGY BRIEFING

### Switch Mode Power Supplies

from

**\*at OEM quantities**

Tektris Electro Corp. designs and manufactures a full range of power supply products for computers thermal printers, office automation, telecommunications and industrial applications.

- Over 175 standard models available from 5 watts to 250 watts

- Delivery from stock to 6 weeks

- Modified standards available with 2 to 4 week turnaround

- A full range of custom capabilities from 5 watts to 750 watts

- Worldwide agency approvals

#### Call Today!

Tektris Electro Corp. 8130 La Mesa Blvd. La Mesa, CA 91941 TEL: 619-593-5000 FAX: 619-593-5014 http://www.tektris.com © 1997 Tektris Electro Corp.

## The New EDA Intellectual Property

verywhere I go, the topic of human resources, and its current role in business, comes up. At first, it seemed like an odd topic for the electronic design automation (EDA) industry, but at a recent press conference, Gerry Hsu, president and CEO of Avant!, said, "Technology is changing so quickly today there is not enough time or energy to spend on dealing with tough problems like employees that aren't performing. A number one company needs number one people. A high-tech company today must hire and retain the most talented people to keep turning out products that consumers will buy."

What he said represents a subtle shift in the high-tech arena, although the trend toward employees as a valued commodity is increasingly obvious. Qualified employees are now seen as a company's own "intellectual property," as opposed to worker bees. The workforce is now a vital link in the successful development and commercialization of technology. Who'd have thought 10 years ago that a point of differentiation between companies would be whose employees stay later at night to get more work done? Qualified employees are now bargaining chips, drawing large salaries, high sign-on and yearly bonuses, and other perks.

But if qualified employees are such a hot commodity, then why is it that the

EDA industry doesn't better meet the needs of its people? Ask any designer to list their biggest complaints, and guaranteed on the list will be that vendors do not provide them with tools that are flexible and simple to use, or even with tools that match current technology capabilities. While most vendors acknowledge this gap. I wonder if anyone is really listening.

While researching the analog/mixed-signal (A/MS) special report on the emergence of A/MS HDL standards in this issue's EDA section. I was confronted with a similar view of the industry. Many realize the benefits of standardizing A/MS HDL's, and are working to ensure that they will be available for use as current design solutions grow old. But, as Mentor Graphics, San

CHERYL AJLUNI DESIGN AUTOMATION

Jose, Calif., pointed out, when analog/mixed-signal HDL language standards do come out, designers will still use what they already have because it gets the job done, albeit the hard way. It seems that many people still miss the point.

The standards will bring benefits not previously possible with the free-style design approach used by many A/MS designers. But what seems to have been forgotten is how the designers will move from their current solutions to standards-based solutions. And what migration path has been set to ensure that this transition will be as painless as possible?

Mentor has the right approach to the issue. When asked what would happen to its HDL-A language once the standards become available, they said that HDL-A is just a temporary solution until the standards take effect. Mentor now has a clear migration path that will transition its current tool users to the standards when available. In effect, the company's HDL-A v3 will be the same as the VHDL A/MS standard. They understand its role to support the development of emerging standards, and to provide a migration path to its users.

The EDA industry can't just focus on the development of technology. Rather, it must seek ways to implement and transition designers to that new technology. Organizing study groups to evaluate the future needs of designers in the analog/mixed-signal area is only half the answer. Vendors need to plot out a migration path for designers that will enable a quick and easy transition from what they use today into what they will use tomorrow.

If someone tells you their company is number one because you'll see cars in its parking lot after 5 p.m., ask them to clarify. Are they working late because they're being productive, or because they can't figure out how to use their design tools to meet their tight product-cycle deadlines? cjajluni@class.org

## We Have Valuable Services For Our Customers!

24-Hour Modem Access 1-800-433-5003

Extended Sales Hours

### Internet Address: http://www.allied.avnet.com

## **Keeping In Touch With Our Customer's Needs!**

## Everything

we know about

on a

So, consider Micron when choosing a source for SDRAM modules. Micron puts a lot into SDRAM DIMMs, so you get a lot out of them.

| Configuration           | Package                       | Also available                                             |  |

|-------------------------|-------------------------------|------------------------------------------------------------|--|

| 2 Meg x 8<br>2 Meg x 64 | 44-pin TSOP<br>144-pin SODIMM | 256K/512K x 64 144-pin SODIMM                              |  |

| 2 Meg x 64/72           | 168-pin DIMM                  | (Graphics solution using our<br>256K x 32 SGRAM component) |  |

| 4 Meg x 64/72           | 168-pin DIMM                  |                                                            |  |

For additional information, visit Micron at www.micron.com/mti or call 208-368-3900.

#### MEETINGS

#### JUNE

**IEEE Power Electronics Specialist** Conference (PESC 97), June 22-27. Regal Riverfront Hotel, St. Louis, Missouri Contact Philip T. Krein, University of Illinois, 1406 West Green Street, Urbana, Illinois 61801; (217) 333-4732; e-mail: krein@uipesl.ece.uiuc.edu.

**IEEE International Symposium on In**formation Theory, June 29-July 4. Ulm, Germany. Contact Han Vinck, Institue of Experimental Mathematics, University of Essen, Ellernstr. 29, 45326 Essen, Germany; (49) 201 3206458; fax (49) 201 3206425.

Sixth IEEE International Fuzzy Systems Conference, June 30-July 5. Barcelona, Spain. Contact Ramon Lopez de Mantaras, IIIA-CSIC Campus U.A.B. 08193 Cerdanyola del Valles, Spain; (34) 3 580 95 70.

#### JULY

Fifth TCL/TK Workshop, July 14-17. Tremont House Hotel, Boston Massachusetts, Contact USENIX Confer- / fects Conference (NSREC '97), July 21- / 119260 Singapore; (65) 7727838.

ence Office, 22672 Lambert Street, Suite 613, Lake Forest, California 92630; (714) 588-8649; fax (714) 588-9706; e-mail: conference@usenix.org; Internet: http://www.usenix.org.

**IEEE Power Engineering Society Sum**mer Meeting, July 20-25. Intercontinental Hotel, Berlin, Germany, Contact Executive Office, IEEE Power Engineering Society, Post Office Box 1331, Piscataway, New Jersey 08855-1331; (908) 562-3864; fax (908) 981-1769.

**IEEE Signal Processing Workshop on** Higher Order Statistics, July 21-23. Banff Centre for Conferences, Banff, Alberta, Canada. Contact Keh-Shin Lii, Department of Statistics, University of California, Riverside, 900 University Ave., Riverside, California 92521; (909) 787-3836; fax (909) 787-3286; e-mail: ksl@ucrstat.ucr.edu.

**IEEE Nuclear & Space Radiation Ef-**

25. Snowmass Conference Center. Snowmass, Colorado. Contact Dennis B. Brown, Naval Research Laboratory, Code 6612, Washington, DC. 20375; (202) 767-5453; fax (202)404-8076: e-mail: dbbrown@ccfnrl.nvy.mil.

#### AUGUST

**40th Midwest Symposium on Circuits** and Systems, Aug. 2-6. Hyatt Regency Hotel, Sacramento, California. Contact Sharon Baumgartner, Department of E&CE, University of California, Davis, California 95616; (916) 754-6216; fax (916) 752-8428; e-mail:mwscas97@ece.ucdavis.edu.

**IEEE International Geoscience & Re**mote Sensing Symposium (IGARSS '97), Aug. 4-8. Singapore International Convention Exhibition Centre, Suntec City, Singapore. Contact Kwoh Leong Keong, CRISP, National University of Singapore, Faculty of Science, Lower Kent Ridge Rd., S

Grayhill front panel assemblies... complete with the components you need and the reliability you demand

Rotary switches, optical encoders, pushbuttons, indicator lights, displays, keypads, keypad graphics or contact systems...don't sweat the small stuff!

No Assembly Required

Let us put it all together for you in customized front panel assemblies. Made from your choice of a complete range of reliable Grayhill ISO-9001 quality components, and more:

- · Housings and actuators

- · Conductive rubber or hard-contact key input

- Overlays with embossing, windows or shielding

- Script, symbol or other legending, color combinations

- Integrated LED's, displays or backlighting

- Termination and mounting

- EL, incandescent or LED panel illumination

- · PC boards, board assemblies including decoding

It's never been easier to put it all together. For more information, call 708-354-1040 and request our Front Panel Bulletin #707. Or dial the DataXpress number for immediate product data. Or see us on the Internet. Grayhill is also a manufacturer of pushbutton switches, rotary switches, and encoder products.

**READER SERVICE NUMBER 121**

#### For more information contact us:

Internet: http://www.grayhill.com Phone: 708-354-1040 Fax: 708-354-2820 DATAX PRESS: 1-800-244-0559

#### HIGH POWER INTERNATIONAL TRANSFORMERS

Signal's HPI transformers incorporate unique coil construction that complies with international safety standards that results in smaller a and lighter

transformer. The HPI transformers operate from 2000 VA to 3500 VA, have dielectric strength of 4000 VRMS Hipot, and leakage current that meets medical applications.

The transformers are recognized to UL 506 and certified to CSA C22.2 #66, VDE 0550 and TUV IEC 950.

**CONTACT: Signal Transformer Co.,** Insilco Technologies Group, 500 Bayview Ave., Inwood, NY 11096-1792. Phone: (516) 239-5777; fax: (516) 239-7208. READER SERVICE 227

INTERNATIONAL PRINTED CIRCUIT **TRANSFORMERS**

Signal Transformerís One-4-All™ (14A) printed circuit mount transformers are designed for use in international low power applications. Recognized to UL 506 and certi-

fied to CSA C22.2 #66, VDE 0805 / EN 60950, and IEC 950, the transformers also have the creepage and clearance necessary to comply with international safety standards.

With an operating power range of 2.5 VA to 56 VA, the transformers are used in low power applications and provide high isolation of 4000 VRMS Hipot

CÓNTACT: Signal Transformer Co., Insilco Technologies Group, 500 Bayview Ave., Inwood, NY 11096-1792. Phone: (516) 239-5777; fax: (516) 239-7208. **READER SERVICE 228**

MORE-4-LESS<sup>TM</sup> INTERNATIONAL TRANSFORMERS

Signal's M4L Series highpower, isolation transformers UL, satisfy IEC, VDE, CSÁ and transformer requirements for low power

isolation in numerous applications.

The M4L Series transformers comply with UL 544, the standard for both medical and dental equipment, and UL 506, the standard for specialty purpose transformers with 250 volt or less input. They are available in models from 300 VA to 1,000 VA, are extremely compact, and lighter than conventionally wound transformers.

CONTACT: Signal Transformer Co., Insilco Technologies Group, 500 Bayview Ave., Inwood, NY 11096-1792. Phone: (516) 239-5777; fax: (516) 239-7208. **READER SERVICE 229**

#### MULTI-PURPOSE INTERNATIONAL TRANSFORMERS

They're taking over

the world.

ternational

ansformer

Signal Transformer's Multi-Purpose International Series (MPI) high-power transformers op-

erate from 200 VA to 900 VA and feature higher volumetric efficiency than conventional 50/60 Hz transformers.

Featuring unique coil construction and winding methods, the MPI transformers have exceptionally good isolation of 4000 VRMS Hipot and low leakage current. They also have a 5 mil thick copper Faraday shield to reduce common mode noise. Faston/screw type shock-proof terminals are used on the series. CONTACT: Signal Transformer Co., Insiko Technologies Group, 500 Bayview Ave., Inwood, NY 11096-1792.

Phone: (516) 239-5777;

**READER SERVICE 230**

fax: (516) 239-7208.

Industry standard pin to pin capability has just landed!

#### Signal's new Low Profile Transformers deliver all these additional benefits at no extra cost:

- · Construction designed to meet VDE/IEC/UL/CSA

- · Hermetically sealed for wave soldering processes

- Encapsulated design provides superior protection in harsh environments

- · Rigid pin construction for easier board insertion

- · Mounting holes for easier installation and greater shock/vibration resistance

- · Improved electrical characteristics including regulation, temperature rise, efficiency, etc.

- · Dielectric strength test ----4000 VRMS Hipot

Add it all up and you simply won't find a low profile transformer that delivers all the benefits that Signal's does. Whether your product is designed for domestic or international markets, Signal's new low profile transformers deliver lower initial cost, lower installed cost and superior performance. Signal Transformer. Your competitive edge ... around the world.

Call us for our detailed product literature and complete specs today.

#### Signal Transformer

Signal Transformer Co., Inc. Insilco Technologies Group

500 Bayview Avenue Inwood, NY 11096-1792 Call: 516-239-5777 Fax: (24 hrs) 516-239-7208

**READER SERVICE 173**

### TECHNOLOGY NEWSLETTER

## Laser Blasts—The Next Step For Smaller, More-Powerful Chips

The discovery of a new technique for processing ultra-high-density semiconductors could lead to a new generation of smaller, more-powerful and energyefficient microprocessors. The new method, which uses powerful laser blasts instead of a conventional heating process, is being developed at the Naval Research Lab, Washington D.C., in conjunction with physicists from Sam Houston State University, Huntsville, Texas.

Currently, microprocessors are produced from a single crystal of silicon that's manipulated by adding dopants, which transform the silicon's electrical properties, thus creating miniature transistors. These dopants are introduced to the silicon by a high-speed beam that penetrates the surface. What happens, though, is that during this process, the silicon crystal becomes damaged. To repair the damage and electrically activate the dopants, the crystal must undergo annealing, whereby atoms are, so to speak, forcibly repositioned. Annealing involves heating the dopant-implanted ("doped") silicon in high-temperature ovens. But, if the chips are small, they will diffuse during the procedure. This limits the size and density of transistors implanted on the silicon crystal, and, ultimately, the size of the computer chip. The annealing process also limits the number of chips that can be produced from a single silicon wafer.

The new laser-beam process repairs and activates the doped silicon crystal. According to Sam Houston physicist Billy Donnelly, "It's just like hitting it with a hammer." The atoms are literally rattled into proper alignment, correcting the defects and activating the chip's electrical properties. Such a process will allow much smaller, more densely packed transistors to be fabricated, leading to smaller chips requiring less power to operate. Less power means less heat generated, which means more transistors can be crammed into a smaller chip. Non-thermal annealing also could eradicate problems with heating larger silicon wafers, which could result in more chips being fabricated in considerably less time: The thermal process requires the silicon to bake about an hour in a high-temperature oven, while the non-thermal method involves only a 5-ns blast from a pulse laser.

For additional information, call (409) 294-1836; fax (409) 294-1834. RE

## ATP Announces Eight New Projects In Key Technology Areas

The U.S. National Institute of Standards and Technology revealed that eight research projects, costshared with U.S. industry under the Advanced Technology Program (ATP), will be undertaken to resolve issues revolving around economically important new capabilities in electronics, biotechnology, energy, and polymer recycling. The projects were chosen from the ATP 1996 General Competition, in which open proposals from any area of technology are put under peer review. The review considers each submission's technical and scientific merit, plus its potential benefits to the U.S. economy, and awards are made on those deemed most qualified.

The eight projects are:

• Direct oxidation of natural gas to methanol and transportation fuels

• Enabling large-scale recovery of plastics from durable goods.

• Programmable nanoscale engines for molecular separation.

• A portable genetic analysis system.

• Cost-effective planar solid oxide fuel cells for distributed power generation.

• High-performance sensor arrays for digital x-ray and visible light imaging.

• Color sequential imaging.

• Development of novel DNA binding proteins as antiviral therapeutics.

If carried through to completion, the eight projects will be valued at \$36.9 million, with approximately \$17.6 million in funding from private industry and \$19.3 million in ATP funding. To see more about these projects, check the ATP's web site at http://www.atp.nist.gov. RE

### Dual-Speaker 3D Sound Algorithm Provides 360°Field

A nother 3D sound algorithm, called the RSX 3D, has arrived that goes beyond most other positional sound 3D approaches by offering 360° lateral sound positioning as well as vertical positioning. Most other 3D schemes only offer a 180° sound plane plus vertical positioning. Employing just two speakers, the RSX (realistic sound experience) 3D software developed by Intel Corp., Hillsboro, Ore., incorporates 3D interactive positional sound that allows listeners to distinguish sounds as sources from above, behind, to the left, to the right, etc.

The algorithms employ transaural cross-cancellation technology, a scheme that allows the realistic sound to be produced by speakers as well as with headphones. Audio objects in RSX 3D can accept and process realtime data, and the software also can handle multichannel streams with multiple sample rates. In addition, the software has an interface that models room acoustics and simulates sound effects occurring in a confined space. Effects such as reverberation and doppler can readily be produced—the algorithms will automatically calculate the change in frequency of a soundwave resulting from the relative motion of the sound source and the listener.

When used with Internet applications, the RSX 3D

WRH

### TECHNOLOGY NEWSLETTER

software is VRML 2.0-compliant. It supports Internetbased streaming, including multichannel streams with multiple sample rates. Java applets running under Microsoft's Internet Explorer or Netscape's Navigator 2.0 and higher also can benefit from RSX 3D. Moreover, the software can accept MIDI-based applications.

For a free copy of RSX 3D or the software development kit, surf into http://www.developer.intel.com/ial.rsx. Or call (503) 264-1946. DB

### First Copper-Equivalent Wireless Local-Loop System On Trial

entury Telephone Enterprises Inc., Monroe, La., is conducting a trial in Marion, La., of the first copperequivalent, wireless local-loop system available in the U.S. Through the trial, the company hopes to determine feature and service transparency of switch-based services. It also will help Century evaluate the operational requirements associated with the deployment of wireless telephony on a larger scale, as well as identify potential bandwidth and service limitations.

The system delivers all of the basic and enhanced voice and data services of today's wired telephone service network with none of the costs for maintenance of copper or fiber connections. Installation of the entire system into a neighborhood can be accomplished in a few days.

Says Nick Bowman, Century's vice president of operations and network design for its telephone group, "The system will provide state-of-the-art wireline-quality telephony services on a real-time basis without immediate, large capital expenditures in copper and fiber facilities."

For more information, visit the company's website at: http://www.centurytel.com. RE

### Laser Emergency Kit Can Strap On Just Like A Backpack

The U.S. Air Force's Phillips Laboratory, located in New Mexico, has developed a laser medical pack that has the power to cut like a scalpel, coagulate bleeding, and close wounds. The pack is self-contained and fits into a space that's about the same as a backpack. The working tip of the instrument has the laser power delivered through a fiber-optic cable. The laser operates at 808 m with an output power of 8.5 W.

The fiber-optic system is pigtailed into the laser array. The complete system consists of a resonator exciting a small-diameter section of about 10 cm and a set of hot and cold exchangers to drive the magnet and piston at the tip. The intensity at the tip of the fiber can be as high as 1 kW/cm<sup>2</sup>. A rechargeable lead battery powers the system with a duration for the 12-V, 4.5-A/hr system of about 20 minutes between recharges. The laser is fully protected from overheating by thermal sensors and cut-offs. Also, the battery recharger includes a key lock to prevent access in a safety mode.

More information can be obtained through the Office of Public Affairs, Phillips Laboratory, Kirtland Air Force Base, NM 87117; (505) 846-1911. PMcG

## Chemistry Lab On A Chip Is The Goal of DARPA-Funded Project

chemistry laboratory small enough to fit on a microchip—that's the project the U.S. Defense Advanced Research Projects Agency (DARPA) has commissioned to the University of Cincinnati, Ohio. The focus of the \$2.8 million project is to develop handheld micro-electromechanical systems (MEMS) that can detect tiny quantities of a protein representative of a typical biological compound sampled or monitored by analytical chemists in medical, environmental, or industrial settings. It's expected that the design would be adaptable to a wide variety of chemical or biological applications.

The collaboration takes on significance simply because it, in essence, takes the expertise of research chemists and puts it in a form that can be used by almost anyone. Other advantages of "chemists-on-a-chip" is the fact that less material means lower cost. It's possible that the cost of some highly technical analyses could be reduced from \$10,000 to less than \$50 because large, expensive laboratory equipment would become obsolete. Smaller systems also can run much faster. Professor Thurman Henderson, one head of the university's research team, estimates that a reaction which typically takes 30 minutes in a lab might take only a few seconds on the chemistry chip.

Analysis will be very similar to what happens in a full-scale chemical laboratory—only that it happens on a microscopic scale. According to Chong Ahn, the other head of the research team, "We're going to have microvalves, micropumps, reservoirs, and controllers. We already have so many MEMS components on campus. We're simply putting them together in a new way for different applications."

Apparently, DARPA's original interest in microanalysis was to develop a battlefield sensor that soldiers could wear to warn them in case of an attack with chemical or biological weapons. But many other applications are possible: they could detect environmental pollutants; monitor the health of a premature baby; help control the delivery of drugs; and increase the safety of chemotherapy. And, by using smart technology, it's believed that implanted micro-machines could be adapted to send signals remotely to physicians, alerting them to problems.

For further details, contact the University of Cincinnati at (513) 556-3001; fax (513) 556-2340. RE

Edited By Roger Engelke

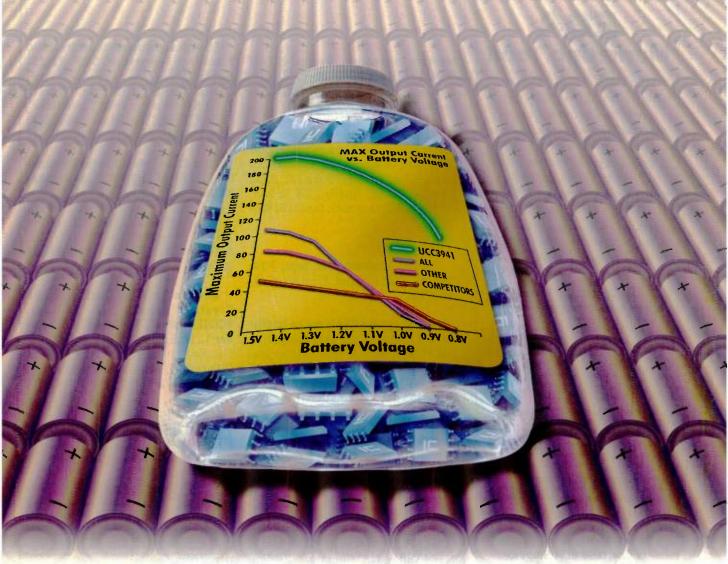

## Your Battery's R For A Long Life

Achieve the highest level of performance and life span for your battery with the new UCC3941 Integrated Synchronous Boost Converter. With only 1.0V of input, startup is guaranteed under full load with a blast of 500mW output power from just a single cell. Even in high current mode, its unique control scheme stops the life from draining out of your battery, and delivers the greatest efficiency.

Maximize the performance of your pager, PDA or portable Instrument power source by calling us today for FREE samples and application information.

#### The UCC3941 Advantage

- Integrated Synchronous Boost Converter with 500mW Output from a Single Cell

- 5.0, 3.3V or Adjustable Output Voltage

- 1.0V Startup Guaranteed Under Full Load

- Operation Down to 0.4V Input

- Output Fully Disconnected During Shutdown

- Additional 9V/100mW Supply

- Adjustable Power Limit Control

Im- The Linear IC Company Everyone Follows

#### TEL: (603) 429-8610

http://www.unitrode.com • FAX: (603) 424-3460 • 7 Continental Boulevard • Merrimack, NH 03054 READER SERVICE 183

## EDA Marketing Tool!

The 1996 Electronic Design Automation (EDA) Study sponsored by *Electronic Design* magazine, provides critical survey information with a focus on EDA marketing executives and user/ engineers. Conducted by the market research firm, EDA Today, L.C., results have been compared, compiled, and studied to serve as strategic marketing opportunities for suppliers.

## Survey results will present information on:

- Platform trends

- · Internet and web usage

- Spending patterns

- Design trends

- Cross tabulation results on issues occuring in the EDA industry

## **ELECTRONIC DESIGN**

| YES, send me copy(ies)    |

|---------------------------|

| of The 1996 EDA Study for |

| \$495.00 each + \$5.00    |

| S&H per copy.             |

| Amex        | U Visa                | Master Card    |

|-------------|-----------------------|----------------|

|             |                       |                |

| Card#       |                       | ——Exp. ——      |

| Account na  | me                    |                |

|             |                       |                |

| Name        |                       |                |

| Signature - |                       |                |

| Company -   |                       |                |

| Address -   |                       |                |

|             |                       | i              |

| City        |                       |                |

| State       | Zip                   |                |

| Phone       |                       |                |

| Fax         |                       |                |

| Fax this o  | rder form<br>201/393- | to Deborah Eng |

or contact EDA Today, L.C. at:

www.edat.com

MEETINGS

#### AUGUST

Memory Technology, Design, & Test Workshop, Aug. 11-12. San Jose, CA. Contact F. Lombardi; (409) 845-5464; email: lombardi@cs.tamu.edu.

**IEEE International Symposium on Electromagnetic Compatibility (EMC '97), Aug. 18-22.** Contact John Osburn, EMC Test Systems LP, 2205 Kramer Lane, Austin, TX 78758; (512) 835-4684 ext. 669; fax (512) 835-4729.

#### **SEPTEMBER**

**Telecom Interactive '97, Sept. 8-14.** Geneva, Switzerland. Contact (703) 907-7736.

Fifth European Congress on Intelligent Techniques and Soft Computing (EUFIT '97), Sept. 8-12. Aachen, Germany. Contact Promenade 9, 52076 Aachen, Germany; (49) 2408 6969; fax (49) 2408 94582; e-mail: eufit@mitgmbh.de; Internet: http://www.mitgmbh.de/elite/elite/eufit.html.

ICSPAT/DSP WORLD 1997, Sept. 14-17. San Diego Convention Center, San Diego, CA. Contact Denise Chan, Miller Freeman Inc. (415) 278-5231; e-mail: dsp@exporeg.com.

MCM Test Workshop, Sept. 14-17. Napa Valley, CA. Contact Y. Zorian, (408) 453-0146 ext. 227; e-mail: zorian@lvision.com.