THIS MINISUPER IS AIMED AT PARALLEL PROCESSING/56 HOW AI WILL ADD BRAINS TO OFFICE AUTOMATION/63

PUBLICATION

Electronics

A MICHAWHILL

PAGE 51

SIX DOLLARS OCTOBER 30, 1986

PARALLEL

**TO A 32-BI**

DESIGN

DOMPH

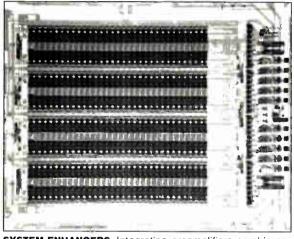

IDT'S CHIP PACKS SEVERAL FUNCTIONS.

GIVES

ONE CYCLE

It began with FAST. A Fairchild innovation that made the world of TTL a better place. Thanks to its higher speeds and lower power consumption.

Now, Fairchild continues its great work by adding PLA to this wondrous family of FAST.

FASTPLA is the onlý family of programmable logic array devices that meets the more stringent specs required of FAST. And it's the only family that offers programmable output polarity with 15ns propagation delay. That's the kind of flexibility that lets you stretch your design horizons...gives you greater design control...lowers your design costs...improves your design performance and reduces your design time from months to days. And when it comes to lightning fast delivery, nothing beats the computerized inventory of Schweber. One call to any Schweber location, coast to coast, gets you complete specifications (including MIL-SPEC) and instant, off-the-shelf delivery on all Fairchild FASTPLA parts.

FASTPLA from Fairchild and Schweber. A significant opportunity to enhance your own creativity. FASTPLA is a registered irademark of Farchied Semiconductor Collopitation

Northeast Bedford, MA 617/275.5100 • Manchester, NH 603/625.2250 • Rochester, NY 716/424-2222 • Danbury CT 203/748-7080 Mid-Atlantic Westbury, NY 516/334-7474 Fairfield, NJ 201-227.7880 • Horsham, PA 215-141.0600 Southeast Baltimore, MD 301/792-4025 • Gaithersburg, MD 301/840-5900 • Raleigh, NC 919/876-0000 Norcross, GA 404-149 9170 • Huntsville, AL 205-895 0/800 • Altamonte Sprindis, FL 305 331.7555 • Pompano Beach, FL 305 977-511 Midwest Pittsburgh, PA 412.782-1600 Beachiwood, OH 216 (464-970 • Luona, MI 331 525 8100 • Daylon, OH 513 439 1800 • Elk Grove, IL 312/364-3750 • Brooklield, WI 414/784 9020 • Cedar Rapids, IA 319/373-1417 St Louis, MO 314/739 0526 • Kansas City, KS. 913/492 2922 • Lidina, MN 612 941 5280 Southcentral Housen, TX 712/458.8253 • fulsa OK 918/622.8000 Northwest I nglewood, CO 303 799-0258 • San Jose, CA 408/946-7171 • Sacramento, CA 916/929-9732 Seattle WA 206/624-1183 Southwest Phoenix, AZ 602/997-4874 • San Diego, CA 619/450-0454 • Invine, CA 714/863-0200, 213/537-4321 • Gardena, CA 213/327-8409 Canoga Park, CA 818 999 4702

Circle 900 on reader service card

# ONLY HIGH

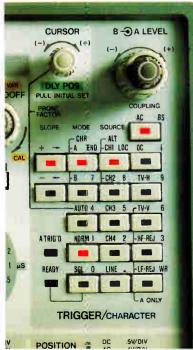

## And only Hitachi CRT Readout Scopes offer: $\Box$ ScreenWriter<sup>m</sup> $\Box$ CursorMeasurement<sup>m</sup> $\Box$ GroundReference<sup>m</sup> display $\Box$ EventCounter<sup>m</sup>

Exclusive ScreenWriter lets you write two 30-character lines of your own notes on the screen. Exclusive EventCounter digitally displays number of pulses within delay time or delayed sweep time. Built-in DVM and 5-digit, 0.1Hz resolution frequency counter display AC and DC voltage and frequency. Exclusive CursorMeasurement, with GroundReference level, displays values of all other important parameters. One Polaroid\* photo gives you a complete record of the measurement including your comments. Three-year warranty.

Hitachi offers 150MHz, 100MHz, and 60MHz Microprocessor based CRT Readout Scopes. Find out how much more scope you get for your money from Hitachi. Call 516-921-7200. Or write Hitachi Denshi America, Ltd., 175 Crossways Park West, Woodbury, NY 11797.

In Canada: Hitachi Denshi, Ltd., 65 Melford Drive, Scarborough, Ontario MIB2G6. Tel. 416-299-5900.

Circle 1 on reader service card

Model V1150: 150MHz 4 channels 8 traces delayed sweep. Mfrs. suggested list price: \$2950

Convenient front panel key pad allows you to input Hitachi ScreenWriter characters, and set trigger conditions.

\*Polaroid is a trademark of Polaroid Corporation

## At The Mitel CMOS Foundry You're Invited In

Customer input is an essential element at our foundry. You know why your circuit was designed, what performance is expected from it, what its cost-constraints must be and what deadlines must be met by our shipments of your wafers.

Mitel Semiconductor has an excellent customer interface along with first-rate foundry capabilities. Nothing is more frustrating than explaining your needs without receiving any response. Our tracking system produces weekly reports or you can get updates by phone or by electronic mail at any time.

Most Mitel customers have tried other foundries, then come to us because of our emphasis on customer liaison and support. This emphasis gets the results you expect within the time frame that we agree on – normally five weeks from PG tape to completed wafers. After all, it's speed with high-yield production that counts!

The Mitel foundry can be your one-stop North American resource for all CMOS fabrication services from mask-making to final shipment. It's financially stable, completely approachable and consistently accountable to its clients for timely, quality production.

### Mitel Foundry Delivers On Time – Every Time

UNITED STATES

San Diego, California. Telephone: (619) 276-3421. San Jose, California. Telephone: (408) 249-2111. Oakbrook, Illinois. Telephone: (312) 655-3930. Boca Raton, Florida. Telephone: (305) 994-8500. **CANADA** Kanata, Ontario. Telephone: (613) 592-5630. UNITED KINGDOM Portskewett, Gwent, South Wales Telephone: +44 291-423355. ASIA Tsuen Wan, Hong Kong. Telephone: +652 0-463641. EUROPE Denmark. Telephone: +45 1-612566. Milan, Italy. Telephone: +45 2-8245222/8245177. West Germany. Telephone: +49 711-7701522.

#### PUBLISHER'S LETTER

### Electronics

EDITOR-IN-CHIEF Robert W. Henkel

EXECUTIVE EDITORS Samuel Weber (technical), Arthur Erikson (news)

> MANAGING EDITORS GROUP Bernard C. Cole, Tom Manuel, Benjamin A. Mason, Jonah McLeod, Howard Wolff, Jeremy Young

> > ART DIRECTOR Fred Sklenar

#### DEPARTMENT EDITORS

Communications: Robert Rosenberg Computers & Peripherals: Tom Manuel Government & Military: Jerry Lyman Industrial & Consumer: Wesley R. Iversen (Chicago)

Packaging & Production: Jerry Lyman Semiconductors: Bernard C. Cole (San Mateo) Software & Microsystems: Alexander Wolfe Special Projects: George Sideris (San Mateo) Test & Measurement: Jonah McLeod (San Mateo)

#### NEWS DEPARTMENT

Front of the Book: Jeremy Young Probing the News: Howard Wolff New Products: Jack Shandle Assistant News Editor: Rick Elliot

**EDITORIAL PRODUCTION & COPY DESK** Benjamin A. Mason (Director) Production

Charles D. Ciatto (Mgr.), Kathy O'Neill

Copy Editors Larry King (Chief), George Ellis, Nancy J. Erickson

#### ART

Sachiko Soskin (Associate Director)

#### NEWS BUREAUS

Boston: Craig D. Rose (Mgr.), Debra Michals Chicago: Wesley R. Iversen (Mgr.) Dallas: J. Robert Lineback (Mgr.) Los Angeles: Larry Waller (Mgr.), Ellie Aguilar New York: Tobias Naegele (Mgr.) San Mateo: Clifford Barney (Mgr.) Frankfurt: John Gosch (Mgr.)

London: Steve Rogerson Paris

Tokyo: Charles L. Cohen (Mgr.), Ayako Hayashihara Michael Berger (World News Chief), Amy Borrus

EDITORIAL ADMINISTRATION Laura Aspery (Administrative Assistant). Lisa Costenbader, Ina Gruber

#### PUBLISHER

Laurence Altman

Director of Operations: Thomas E. Vachon Circulation Manager: Leon Irgang Production Director: Thomas Egan Manager of Sales Administration: Evelyn Schmidt Research Associate: Diane Breder

There have been 11 Electronica shows, and John Gosch, our man in West Germany, has covered all but the first one. in 1964. So when he writes about the 12th edition of the big international components exposition in Munich, as he does in this issue on page 83, John brings to the table the depth of background that only two decades on the job can provide—and that only Electronics share with you.

Electronica, which is

held in even-numbered years, has always been a good indicator of the industry's direction. At his first one, John says, "I reported, 'The trend toward solid-state applications is gaining momentum in Europe despite grumblings by some old-time designers who still cling to engineering practices of the past." And, quoting a German engineer, I cabled New York, 'By and large, European integrated-circuit manufacturing methods are at best what can be termed large-scale laboratory production. And that will be the case for some time to come' The big issue in those days was Europe's growing technology gap vis-àvis the U.S.-no word of a Japanese threat back then. How things have changed."

Probably the most interesting thing about Electronica is how the show got started and how fast it has grown, says John. It began in the early 1960s, when

can GOSCH: Recalling the early days and Miss Electronica.

American electronics companies operating in Germany were looking for a forum where they could display their wares. They were turned down by the Hanover Industrial Fair, so they approached a number of cities, among them West Berlin, Munich, and Frankfurt, to organize an exhibition devoted solely to components. Munich was the first to say yes.

"The first show," says John, "was a regional affair, and it was given little

chance of being repeated. There were around 100 companies (not only American, but many small German outfits that also couldn't get into Hanover), and they didn't even fill three exhibition halls. On their stands they displayed products from an additional 300 companies. Total attendance was 13.400." This year, there will be 2,284 exhibiting companies from 36 countries, with 125,000 visitors expected.

John finds Electronica an exciting event, but he misses the good old days when it was like a club where the competitors were also friends. "In fact, in 1968 it was decided to name a Miss Electronica-a woman working at the stand of a UK company won. But at the next show, when the big German companies came aboard, it became a no-nonsense, strictly professional and businesslike affair. No more Miss Electronica contests after that."

Anne

October 30, 1986 Volume 59. Number 34 107,225 copies of this issue printed

October 30, 1986 Volume 59, Number 34 107,225 copies of this issue pnnied Electronics (ISSN 0883-4989), Published bweekly by McGraw-Hill Inc. Founder: James H. McGraw 1860-1948. Publication office. 1221 Avenue of the Americas, N.Y. N.Y 1020; second class postage paid at New York, New York and additional maining offices. Postage paid at New York, New York and additional maining offices. Postage paid at New York, New York and additional maining offices. Postage paid at New York, New York and additional maining offices. Postage paid at New York, New York and additional maining offices. Postage paid at New York, New York and additional maining offices. Postage paid at New York, New York and additional maining offices. Postage paid at New York, New York and patholic transmitter of the Americas. New York, N.Y. 1021bi. Additional Carculation. and advertising addresses: Electroncs. Subscriptions limited to polessional persons with active responsibility in electronics technology. No subscriptions accepted without complete iden-tion supplied. the publisher reserves the right to reject nonqualified requests. Subscription rates: the United States and possession \$32 one year, S51 two years, S71 two years, S78 three years. Curope \$50 one year, S51 two years, S240 three years, laustial and New Zealand S95 one year, S170 two years, S240 three years, including air freight; all other countries \$50 one year, S51 two years, S78 three years. Limited quota of subscriptions available at higher-tham-basic rate for persons allied to field subscriptions available at higher-tham-basic rate for persons illed to field subscriptions available at higher-tham-basic rate for persons allied to field subscriptions available at Negres. Karding and Communications information Group. Auseal C. White, Computers and Communications information Group. J. Thomas Phyan, Markeling and International. Senor Vice President. Francis A. Shinal, Contoler, Senor Vice President. Frains A. Shinal, Contoler, Senor Vice Presidents. Publishers. Laurence Aliman, Elect

McCuen, Communications.

Wice Presidents: Fred O. Jensen, Planning and Development: Michael J. Koeller, Human Resources, Talat M. Sadg, Systems Planning and Technology. Vice President-Publisher. Paul B. Beatty. Architectural Record and Office Condecise.

Michael M. McGraw J. C. Charman: Joseph L. Dionne. President and Chief Executive Officer: Robert N. Landes, Executive Core President and Chief Executive Officer: Robert N. Landes, Executive Core President and Chief Executive Officer: Robert N. Landes, Executive Core President and Chief Executive Officer: Robert N. Landes, Cerestent, Ranulactrumg, Rabp H. Schulz, Senor Vice President, Finance and Manulactrum, Robert J. Banash, Senor Vice President, Efformance and Manulactrum, Robert J. Banash, Senor Vice President, Evidente Vice President, Manulactrum, Robert J. Banash, Senor Vice President, Evidente et al. 1998. Distribution of the spublication may not be reproduced in whole or in part without the consent of copyright owner for the base fee of SUSD per copy of the article plus SUS 25 per page. Payment should be sent directly to the CCC. Copying of Claraw-Hill so rohibited. Requests for special permission of McGraw-Hill is prohibited. Requests for special permission proce applying to copes not yet mailed. Please send change-of-address notices or complaints to Fulfilment Manager. Subscription argue code stata doffeess head bits and to a special perconset and the special doffees notices and Jana Manuscher. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:1064. 2019 19:106

Editorial department phones: Administration (212) 512-2645, News and New Products (212) 512-2685, Technology (212) 512-2666. Bureaus: Boston (617) 262-1160, Chicago (312) 751-3811, Dallas (214) 458-2400, Los Angeles (213) 480-5234, New York (212) 512-3322, San Francisco/San Mateo (415) 349-4100, Washington (202) 463-1650, Frankfurt 72-5566, London 493-1451, Paris 42-89-03-80, Tokyo 581-9816, Business departments: (212) 512-6435 (Business departments follow the Advertisers' Index).

# Electronics

#### NEWS

#### Newsletters

#### **Electronics**, 19

TI enlists Video-7 to help develop graphics interface

AMD and Siemens schedule a

With investors frightened off by

suit, Lattice skips payday

#### International, 48

• European co-operative will spend billions on submicron technology

• British aim to double ionimplanter throughput

• Japanese cut back on chip production

#### Military, 29

The race is on to develop microwave GaAs ICs for the Department of Defense

IBM hits the 1-µm level on Phase 2 VHSIC chips

#### International trade, 30

Equipment makers bid to modify the U. S.-Japanese semiconductor trade pact

The trade pact sparks a thriving gray market

#### Data processing, 32

A new way to tighten security in personal-computer networks

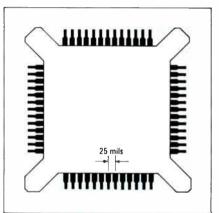

**Packaging, 36** High-pin-count ASICs may get new JEDEC package

**Networking, 36** Software makes network transparent to users

**Consumer, 38** In 1,500 centuries, this clock will lose only 1 second

**AI, 44** NTT builds a Lisp machine

#### INSIDE TECHNOLOGY

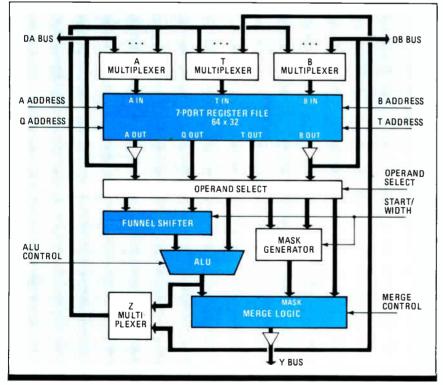

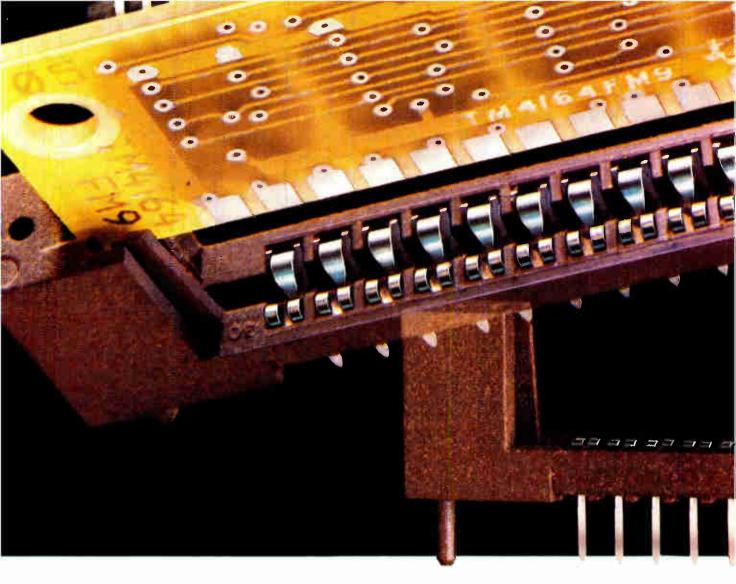

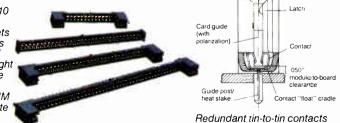

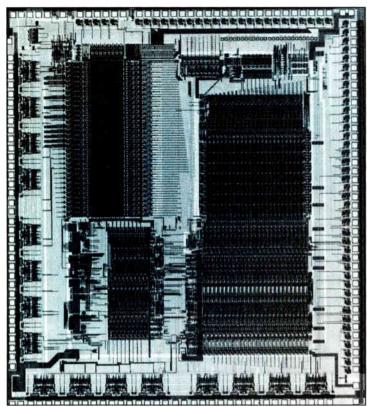

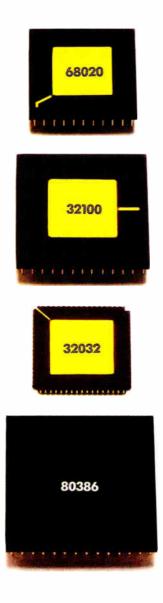

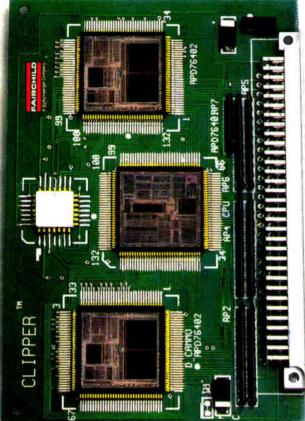

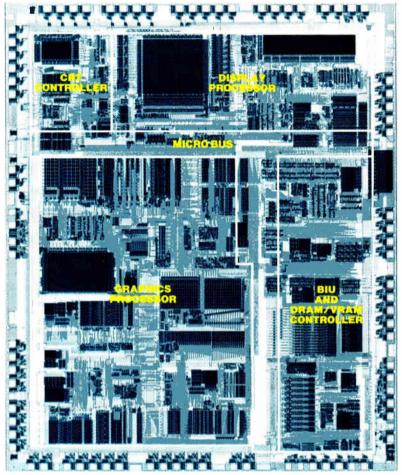

#### COVER: Parallel design gives oomph to a 32-bit slice, 51

A powerful 32-bit-slice processor from Integrated Device Technology Inc. can perform several operations simultaneously in one clock cycle. It can yield highly parallel system designs that boost throughput 4 to 20 times over other 32-bit slice chips

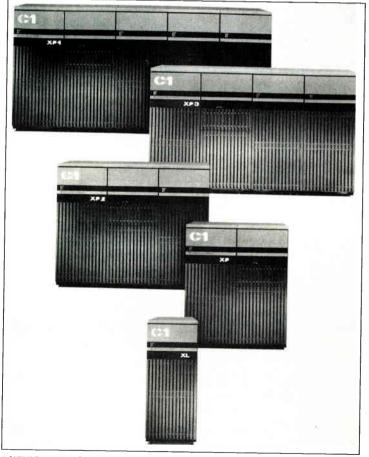

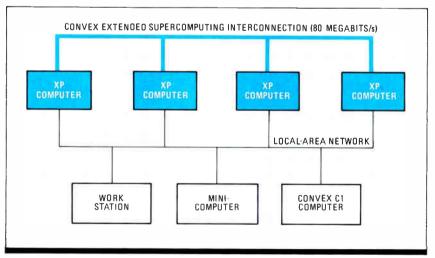

#### This minisuper is aimed at parallel processing, 56

For less than \$1 million per machine, Convex Corp.'s C1 minisupercomputer family features upgraded processors and memory along with a high-speed fiber-optic interconnection system

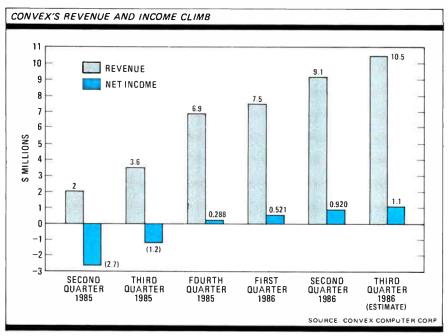

#### Convex has a master plan to be king of the hill, 59

The company will use its new computers to separate itself from a growing crowd of competitors, as well as to serve as a wedge into parallel processing

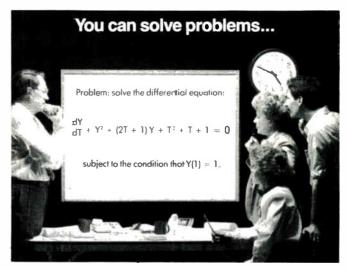

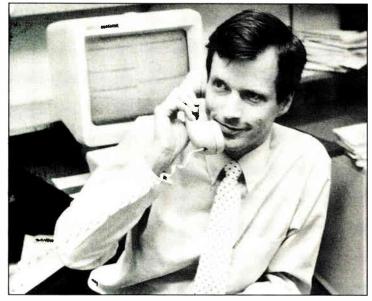

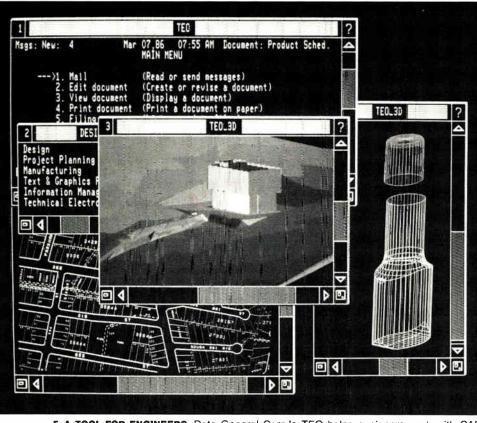

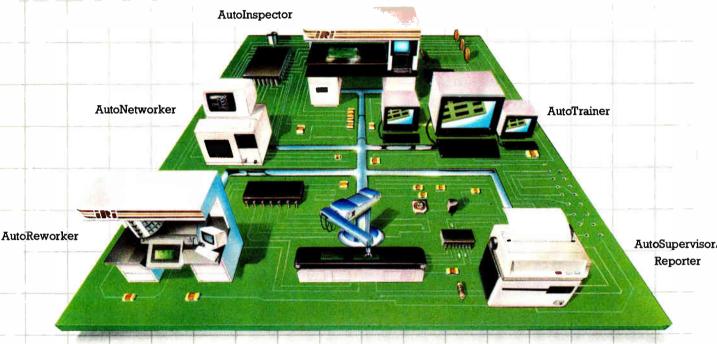

#### SPECIAL REPORT: How AI will add brains to office automation, 63

Artificial intelligence is getting ready to move into the mainstream of information management in the workplace. In development are systems that do such tasks as centrally organize knowledge in engineering projects, distribute messages in line with users' interests, and juggle a work group's schedules.

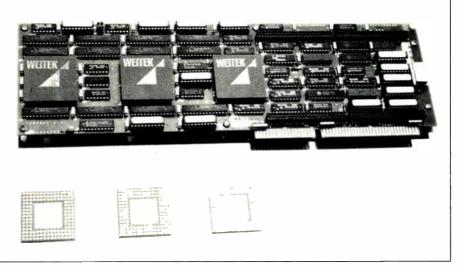

#### How Weitek's chips run Fortran and C at 25 megaflops, 69

Three new processor sets combine optimizing compilers for high-level languages with a hardware architecture that incorporates the best features of reduced-instruction-set computers

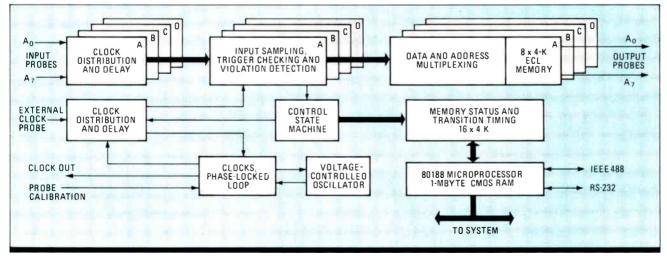

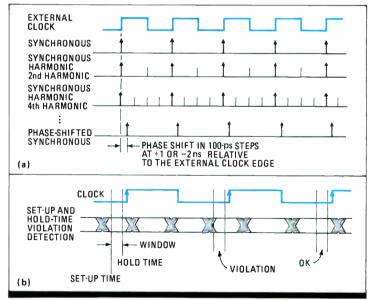

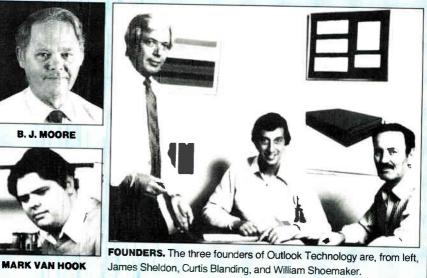

#### Logic timing analyzer has 100-ps resolution, 72

With new equivalent time recording and synchronous harmonic sampling modes, Outlook Technology's instrument speeds debugging of systems with clocks to 200 MHz

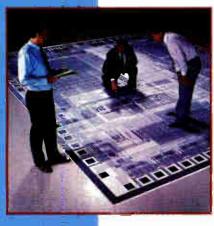

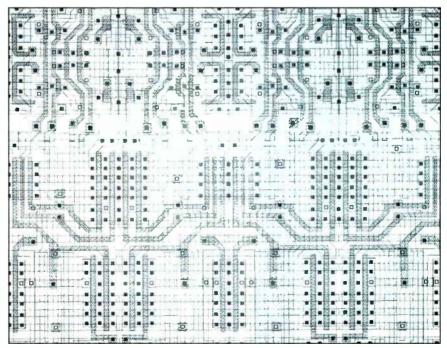

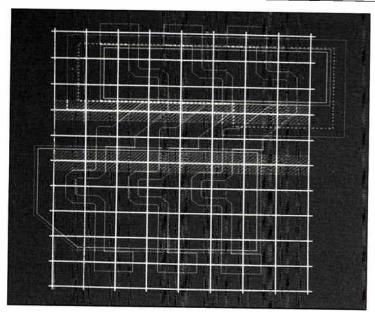

#### How designers can save time in laying out a sea of gates, 77

California Devices' software slashes turnaround time by running on a work station instead of a mainframe computer to place and route 10,000-gate channelless arrays

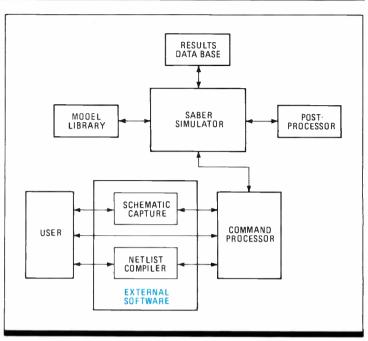

#### Saber cuts Spice out of analog simulation, 80

Based on a library of behavioral models, Analogy's new software tool can simulate any physical system and is faster, more flexible, and easier to use

#### PROBING THE NEWS

#### Munich's microelectronics conference takes a new tack, 83

The meeting that runs concurrently with Electronica—a show that is bursting its seams—has decided to aim at technical executives and beginning engineers. The theme of this year's papers is competition

#### VOLUME 59. NO. 34

COVER: ART DIRECTOR FRED SKLENAR

#### DEPARTMENTS

#### **Publisher's letter, 3**

Our man in West Germany, John Gosch, has watched the Electronica show grow up

#### **FYI, 8**

Wyle's Clough is also an optimist: 'If my assumptions are right, we're looking at a good, strong, up year in 1987 for the U.S. semiconductor business

#### Meetings, 12

#### People, 16

A "crazy idea" wins the Nobel Prize in Physics for IBM's Gerd Binnig and Heinrich Rohrer

#### **Electronics Week**, 104

- IBM pulls out of South Africa • Siemens produces its first 1-Mb

- random-access memories

• Siemens and BASF join in a mainframe marketing venture • Brazil cracks opens the door to

- its computer-service industry

- RCA Astro-Electronics Division signs a \$200 million deal to build direct-broadcast satellites

**NEW PRODUCTS**

#### Newsletter, 25

• Two CMOS versions of the 1750A microprocessor bow • Design tools for low-density gate arrays run on IBM PC AT • Reactor promises \$75 epitaxy

cost for GaAs wafers

#### Semiconductors, 91

• Honeywell Inc.'s analog-todigital flash converters operate at 125 megasamples/s by clipping the drive requirement and the kickback current

• Winchester-drive controller chips from Cirrus Logic Inc. outperform the industry standard and add a customization option

#### **Computers & Peripherals, 94**

• Micro-Term Inc.'s black-on-white screen rivals letter-quality printing, thanks to high-resolution characters and a flickerless background

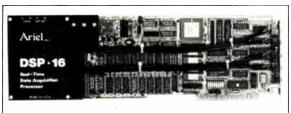

• Ariel Corp.'s data-acquisition board achieves real-time operation by incorporating TI's TMS32020 digital signal processor

#### Design & Test, 98

• Quadtree Software Corp.'s simulation models for the Motorola 68000 family execute the chips' full instruction set • Four oscilloscopes from Tektronix Inc. offer high resolution and bandwidth

#### **Production Equipment, 99**

• A metal-organic chemical-vapordeposition system from Spire Corp. that targets the laboratory research market yields high performance while operating at atmospheric pressure

(C) Advanced Micro Devices, Inc. 1986

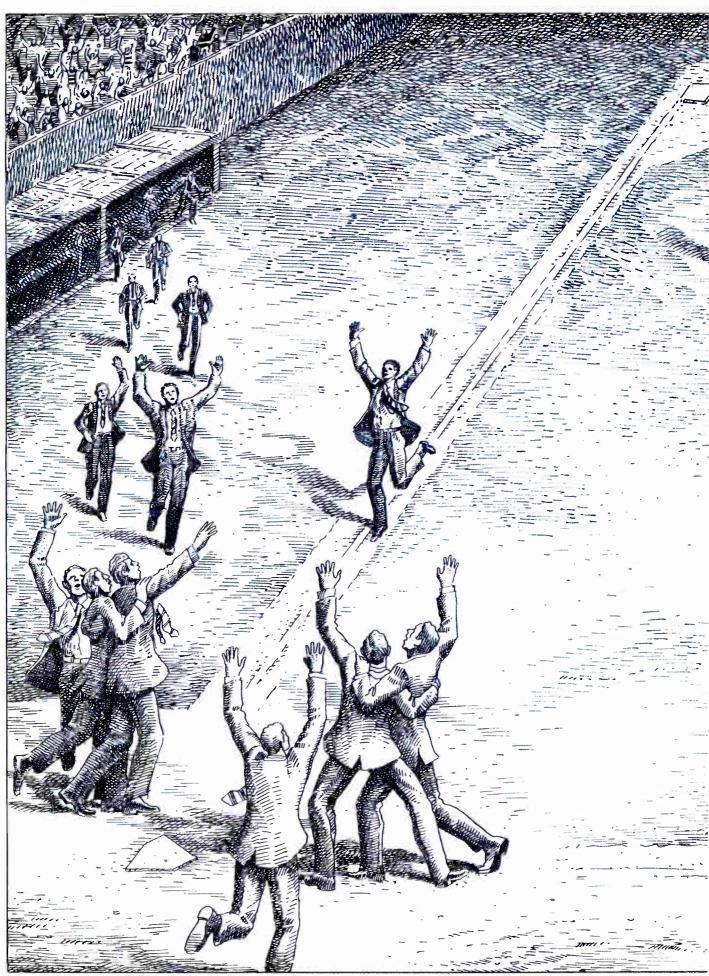

What a season!

Advanced Micro Devices has delivered sixtyfour new products in fifty-two weeks. At least one a week every week. On the shelf. In volume.

32-bits. CMOS. Peripherals. ISDN. Microprocessors. Graphics. Networking. EPROMs. EEPROMs. Super-fast RAMs.

How did we do it?

We took a group of gifted, motivated people. Gave them a nearly impossible goal. Then backed them with the R&D dollars needed to get the job done.

And luck? Sure. You don't go sixty-four for fiftytwo without luck. But as Branch Rickey used to say, "Luck is the residue of design."

Circle 7 on reader service card

## Quality Price Availability

Venus Scientific offers over 400 power supply systems; from 5 to 30,000 volts, up to 2,500 watts. Venus has the power supply solution for:

#### Lasers

- Military

- Communications

- Aerospace

- Electronic Displays

- Research Labs

399 SMITH STREET FARMINGDALE, N.Y. 11735 (516) 293-4100 TWX 510 224 6492 Wyle's Clough is also an optimist: 'If my assumptions are right, we're looking at a good, strong, up year in 1987 for the U.S. semiconductor business

One more optimist has checked in to support our Sept. 4 column. We had stuck out our neck to declare that every time we heard grim forecasts for the semiconductor industry, it would end up bouncing back higher than ever. And that this was going to happen once again. "In every past cycle, the gloom and doom is at its deepest level just before the upturn," reminds Charlie Clough, president of Wyle Laboratories, the El Segundo, Calif.-based semiconductor distributor. A long-time industry watcher, Char-

lie makes a strong case for a big 1987 for the U.S. semiconductor industry. "If my assumptions are right," he maintains, "we're looking at a good, strong, up year in 1987 for the U.S. semiconductor business—on the order of 30% to 35% industry growth." Here is how Charlie dopes it out:

The primary reason for his bullishness is the extremely low level of semiconductor inventories at U.S. equipment makers. As these companies burned chip inventory in 1985 and again in 1986, they caused the deepest decline in semiconductor history. Inventories fell more than \$3 billion, and they are still dropping. They had doubled from \$3 billion in 1983 to \$6 billion in 1984, the single largest factor driving the chip market to a record high that year.

"We are now at the same point in the semiconductor cycle that we were in early 1982," Charlie figures. The industry then had just gone through the first wave in a cycle that was later called the "false blip." The error signal had come from the small-to-medium equipment builders who had finally balanced their semiconductor inventories after a long and deep recession. When distributor orders started soaring as a result, in April of that year, chip makers turned euphoric and believed their recession was over. But an eight-month period of discouraging decline followed, Charlie reminds us, because the large mainframe makers didn't return to the market until the end of 1982.

"Now I believe we are approaching a point where the large electronics manufacturers will have their inventories below their end-equipment run-rate requirements, just as happened at the small-to-medium size electronics company in the first quarter of 1986," Charlie says. And when that happens, "their return to the marketplace after a two-year absence will cause a very sudden and high demand on the semiconductor industry." **ROBERT W. MENKEL**

## INFINITELY FASTER WAVEFORM RECORDING

## **1.3 GIGASAMPLES/SEC!**

INTRODUCING THE WORLD'S FASTEST SOLID-STATE WAVEFORM DIGITIZER...THE AWARD-WINNING LeCROY 6880 = 1.3 GIGASAMPLES/SEC! = 8-BIT RESOLUTION = 250 MHz BANDWIDTH = TRUE, SOLID-STATE A/D CONVERSION

**SEE MORE** LeCroy's new 6880 is the first, and the only, all-solidstate digitizer that accurately captures complex, single-shot phenomena within a 250 MHz bandwidth at a stunning 1.35 gigasamples/sec! What's more, the 6880 achieves this spectacular speed with true precision solidstate A/D conversion, yielding a resolution of 8 bits with exceptional dynamic performance.

**STORE MORE** Your signals are digitized to a deep 10,000 sample point memory providing a long recording window on fast signals and events. Up to 100% pretrigger and 1.5 msec post-trigger delay assures a flexible time window for capturing, viewing, and comparing complex waveforms or random transients.

**DISPLAY AND ANALYZE MORE** Display and analyze captured waveforms on a video monitor or with LeCroy's WAVEFORM-CATALYST Digital Storage Oscilloscope Software and an IBM-PC. And of course the Model 6880 is fully programmable over GPIB (IEEE-488) and RS-232-C providing friendly remote control and high speed data transfer.

#### CAPTURE YOUR HIGH SPEED WAVEFORMS BETTER, FASTER, AND FOR LESS.

For more information simply circle the reader service card or call (914) 578-6038

#### 700 SOUTH MAIN STREET, SPRING VALLEY, NY 10977 TWX: 710-577-2832

Circle 127 For Demonstration

6880 MEMORY

LeCroy 6880

OTHERS

# At last, the ordinary microprocessor can take its rightful place in history.

It had to happen—the conventional microprocessor has had its day. Relegated to the ranks of yesterday's devices by the new transputer family from INMOS. It's history in the making.

The IMS T414 transputer is a fast, easy-to-use VLSI component, integrating a 32-bit processor, four intertransputer communication links, 2K bytes Static RAM, 32-bit memory interface and DRAM controller. All on a single CMOS chip—offering execution rates up to 10 MIPs.

While transputers excel in single-processor systems, their real power can be unleashed by connecting any number of transputers together via the high-speed serial links. Multi-transputer systems can deliver the performance you need today, and can be easily expanded in the future as your processing requirements increase.

And there's more. Programming multiprocessor systems has never been easier. The Transputer Development System (TDS) supports C, Fortran, Pascal and OCCAM, providing a complete software development environment, and is available for a number of popular hosts. Software developed on the TDS can be executed on one or more transputers, enabling cost-performance tradeoffs to be made.

INMOS transputers are available now and have already found their way into companies who are evaluating, prototyping and manufacturing transputerbased systems. Applications include supercomputers, DSP, graphics, robotics, AI, distributed control systems, PC's, engineering workstations and many others.

Write or phone for more information on the transputer family and start making history yourself.

|                   | TRANSPUTER PRODUCTS                                            |  |

|-------------------|----------------------------------------------------------------|--|

| IMS T414          | 32 bit Transputer—2Kbyte —4 links                              |  |

| IMS T212          | 16 bit Transputer-2Kbyte —4 links                              |  |

| IMS M212          | 16 bit Disc Processor—1K byte—2 links                          |  |

| DEVELOPMENT TOOLS |                                                                |  |

| IMS D701-2        | IBM PC—Transputer Development System.                          |  |

| IMS D600          | VAX/VMS—Tronsputer Development System.                         |  |

|                   | EVALUATION BOARDS                                              |  |

| IMS B002-2        | Double Eurocard + IMS T414 + 2Mbyte DRAM + 2 x RS232.          |  |

| IMS B003-1        | Double Eurocard + 4 x IMS T414 + 4 x 256Kbyte DRAM.            |  |

| IMS B004-2        | IBM PC Format + IMS T414 + 2Mbyte DRAM.                        |  |

| IMS B006-2        | Double Eurocard + 9 x IMS T212 - 128Kbyte SRAM.                |  |

| IMS B007-1        | Double Eurocard + IMS T414 + 0.5Mbyte DRAM + 0.5Mbyte VideoRAM |  |

|                   | HIGH PERFORMANCE VLSI MEMORIES                                 |  |

|                   | 16K CMOS SRAM, 25-45ns, 64K CMOS SRAM, 35-70ns                 |  |

|                   | 256K CMOS DRAM, 60-100ns                                       |  |

INMOS, P.O. Box 16000, Colorado Springs, CO 80935, Tel. (303) 630-4000; Bristol, England, Tel. 454-616616; Paris, France, Tel. (14) 687-2201; Munich, Germany, Tel. (089) 319-1028; Tokyo, Japan, Tel. 03-505-2840.

World Radio History

Circle 11 on reader service card

PEARSON Wide Band, Precision CURRENT MONITOR

With a Pearson current monitor and an oscilloscope, you can measure pulse or ac currents from milliamperes to kiloamperes, in any conductor or beam of charged particles, including those at very high voltage levels.

This monitor is physically isolated from the circuit. It is a terminated current transformer whose output voltage precisely follows the current amplitude and waveshape. A typical model gives an amplitude accuracy of +1%, -0%, 20 nanosecond rise time, droop of 0.5% per millisecond, and a 3 db bandwidth of 1 Hz to 35 MHz. Other models feature 2 nanosecond rise time, or a droop as low as 1% per second.

Whether you wish to measure current in a conductor, an electron device, or a particle accelerator, it is likely that one of our off-the-shelf models (ranging from 1/2" to 1034" ID) will do the job. We also provide custom designs to meet individual specifications.

Contact us and we will send you engineering data.

#### PEARSON ELECTRONICS,INC.

1860 Embarcadero Road Palo Alto, Calif. 94303, U.S.A. Telephone (415) 494-6444 Telex 171-412

#### MEETINGS

Sensors '86 and Autofact '86, Society of Manufacturing Engineers (One SME Drive, P.O. Box 930, Dearborn, Mich. 48121), Westin Hotel, Dearborn, Mich., Nov. 11-13.

Electronica '86 and 12th International Microelectronics Conference, Munich Fair and Expositions GmbH, *et al.* (Postfach 12 1009, D-8000 Munchen 12, West Germany), Munich Trade Fair Center, Munich, Nov. 11-15.

International Workshop on Moisture, Measurement, and Control for Microelectronics, National Bureau of Standards, *et al.* (Dr. Didier Kane, Rome Air Development Ctr., Griffiss AFB, N.Y. 13441), NBS, Gaithersburg, Md., Nov. 12-14.

**International Electronics Packaging Conference,** International Electronics Packaging Society (114 N. Hale St., Suite 2B, Wheaton, Ill. 60187), Sheraton on Harbor Island-East, San Diego, Calif., Nov. 17-19.

**Conference on Magnetism and Magnetic Materials,** American Institute of Physics, *et al.* (Diane S. Suiters, Courtesy Associates, 655 15th St., N.W., Suite 300, Washington, D.C. 20005), Hyatt Regency, Baltimore, Md., Nov. 17-20.

Scientific Software for Supercomputing, National Bureau of Standards (Francis Sullivan, A151 Technology Building, NBS, Gaithersburg, Md. 20899), NBS, Gaithersburg, Md., Nov. 17-20.

**Plastics in Electronics,** Business Communications Inc. (9 Viaduct Rd., Stamford, Conn. 06907), Crowne Plaza Holiday Inn, Stamford, Conn., Nov. 18-19.

Wescon '86, IEEE (Electronics Conventions Inc., 8110 Airport Blvd., Los Angeles, Calif. 94303), Convention Center, Anaheim, Calif., Nov. 18-21.

**PRONIC '86:** International Exhibition of Equipment and Products for Electronics, Société de Diffusion des Sciences et des Arts (20, rue Hamelin, F 75116 Paris, France), Porte de Versailles Exhibition, Paris, Nov. 18-21.

Microcontamination Conference and Exposition, Microcontamination Magazine (Expocon Management Associates Inc., 3695 Post Rd., Southport, Conn. 06490), Santa Clara, Calif., Nov. 18-21.

MIL-STD-1553B: Applications, Developments, and Components, ERA Technology, Ltd. (Laura Christie, Seminar Organiser, ERA Technology Ltd., Cleeve Road, Leatherhead, Surrey KT22 7SA, UK), Regent Crest Hotel, London, Nov. 25-26.

**Power Electronics and Variable-Speed Drives '86,** Institution of Electrical Engineers (Savoy Place, London WC2R OBL, U.K.), National Exhibition Centre, Birmingham, England, Nov. 25-27.

**Electronicom '86,** IEEE (Richard Brostrom, Berger & Associates Canada Inc., 133 Richmond Street W., Suite 203, Toronto, Ontario M5H 2L5), Toronto Convention Centre, Toronto, Canada, Dec. 1-3.

**GLOBECOM '86:** Global Telecommunications Conference 1986, IEEE (Ross Anderson, Southwestern Bell, Room 706, 3100 Main Street, Houston, Tex. 77002), Westin Galleria Hotel, Houston, Tex., Dec. 1-4.

National Database and 4th Generation Language Symposium, Digital Consulting Associates, Inc. (6 Windsor St., Andover, Mass. 01810), Ritz Carlton Hotel, Boston, Dec. 2-5.

**2nd International Conference on Artificial Intelligence,** Institut International de Robotique Et d'Intelligence Artificielle de Marseille (Viviane Bernadac, IIR-IAM, 2 Rue H. Barbuss, 13241 Marseille Cedex 1, France), Marseilles, France, Dec. 2-5.

**Controls West '86,** Tower Conference Management Co. (331 W. Wesley St., Wheaton, Ill. 60187), Long Beach Convention Center, Long Beach, Calif., Dec. 3-5.

**IEDM '86:** International Electron Devices Meeting, IEEE (Melissa Widerkehr, Courtesy Associates, Inc., 655 15th St., N. W., Washington, D. C. 20005), Westin Bonaventure Hotel, Los Angeles, Calif., Dec. 7-10.

International OEM, Penton Exhibitions (Bill Little, Penton Expositions, 122 E. 42nd St., New York, N. Y. 10168), Jacob Javits Convention Center, New York, Dec. 9-11.

Microcomputer Graphics Show and Conference, Expoconsul International Inc. (3 Independence Way, Princeton, N.J. 08540) Jacob Javits Convention Center, New York, Dec. 17-19.

International Winter Consumer Electronics Show, EIA Consumer Electronics Group (2001 Eye St., N. W., Washington, D. C. 20006), Las Vegas Convention Center, Las Vegas, Nev., Jan. 8-11.

LBO-518 100-MHz Four Channel Oscilloscope

> LFG-1310 0.01 Hz-10 MHz

## Sweep-Function Generators

Leader 10-MHz and 2-MHz Sweep-Function Generators are exceptionally durable and versatile. They have every important feature, and every required waveform including: • Sine, square, triangle, sawtooth, ramp, pulse and TTL outputs • 1000:1 and 100:1 ranges • Adjustable waveform symmetry • AM or FM modulation • VCO and GCV • Linear and log sweep • Plus CW, triggered, gate and burst modes (1310 only) • And lots more!

#### Call toll-free (800) 645-5104 In NY State (516) 231-6900

Request an evaluation unit, our latest Test Instrument Catalog with over 100 outstanding products, the name and address of your nearest "Select" Leader Distributor, or additional information.

380 Oser Avenue Hauppauge, New York 11788 Regional Offices: Chicago, Dallas, Los Angeles, Boston, Atlanta In Canada call Omnitronix Ltd. (514) 337-9500

Circle 80 For Product Demonstration

Circle 13 For Product Information

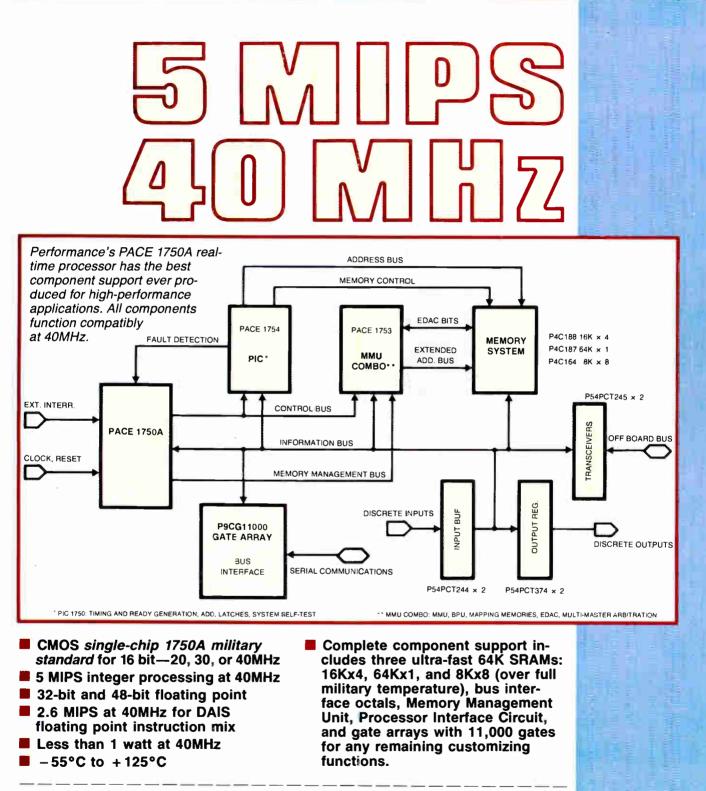

#### WORLD'S FASTEST CMOS REAL-TIME CPU

| NAME                 | Send me information on:          |      |

|----------------------|----------------------------------|------|

| TITLE                | PACE 1750A and component support | 1.00 |

| COMPANY              | PACE Bus Interface Octals        |      |

| ADDRESS              |                                  | 8    |

| CITY/ST/ZIP          |                                  |      |

| PHONE                | Immediate G months G Longer      | 18   |

| Electronics 10/30/86 |                                  | 11.  |

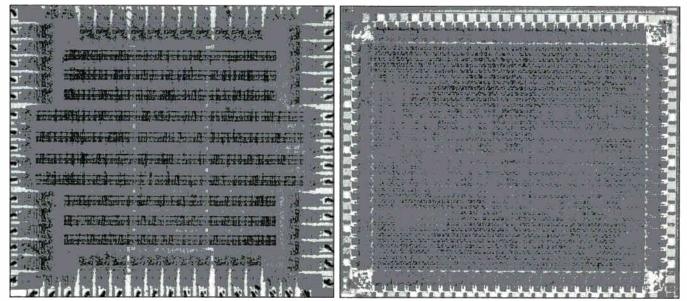

### THE MAKING OF A BREAKTHROUGH

1750A. 40MHz. Single-chip CMOS implementation of the military standard. Pretty impressive specs, and no small feat. Why did we do it? Because we knew you needed it. How did we do it? The unusual way. We planned and managed for early success.

We started by creating a fresh new conceptual architecture and logic design; it improved the chip's performance by a factor of 2.

We put the chip through its paces against the 1750A instruction set in exhaustive ATP tests.

We pushed our advanced CAE tools to the limit, and debugged them designing Performance static RAMs and logic circuits. Then we put the tools to work on the 1750A.

> Thousands of man days later, we achieved a complete chip layout verification on the computer against the circuit schematic. An impressive feat in itself.

#### PACE TECHNOLOGY

As a designer, you know that you can't create advanced products without advanced manufacturing methods. That's why our process people built a Class-2 facility to process 6-inch wafers, and developed PACE Technology, the most advanced CMOS technology available today: 0.8 micron effective channel

lengths, 2.75 micron metal pitch, and internal loaded gate delays of 500 picoseconds. PACE Technology made it possible to achieve a 40MHz clock rate on the 1750A.

We debugged PACE Technology on a 400,000 transistor 64K SRAM, a good test prior to processing the 200,000 transistor PACE 1750A.

But advanced technology alone cannot assure success. That's why we depended on the ideas and skills of our managers. Our top fifteen managers each have an average of over fifteen years of semiconductor industry experience.

It was gratifying to watch 1750A chips from the very first wafers pass Sentry test.

Our Class-2 facility produces

6-inch wafers with 0.8 micron

CMOS technology.

The payoff? Working chips in the first wafers of our first pass of silicon.

The 1750A passed the full 100,000 vector test program, over the full military temperature range, 5 volts  $\pm$  10%.

PACE Technology is a trademark of Performance Semiconductor Corporation. 1986 Performance Semiconductor Corporation

Performance engineering put 200,000 transistors in just 52,000 square mils.

610 E. Weddell Drive, Sunnyvale, CA 94089 Telephone: 408-734-9000 Telex: 6502715784

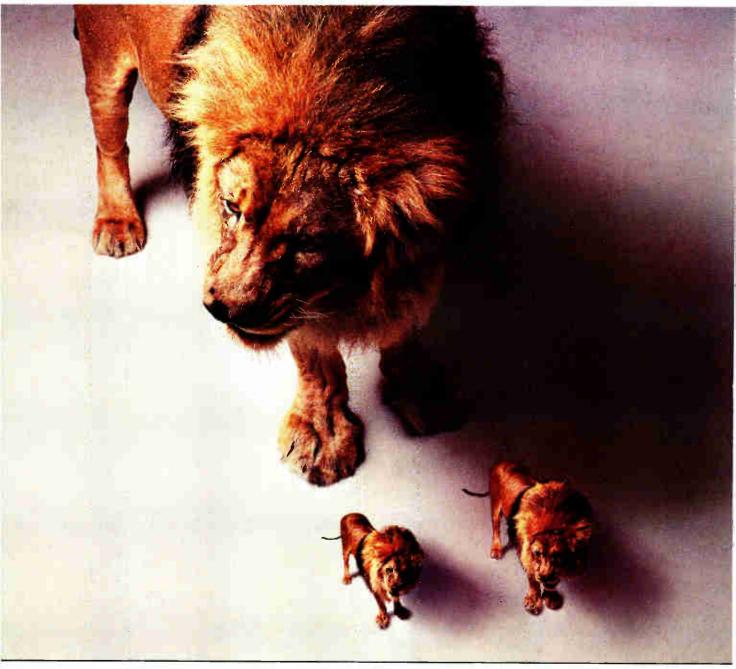

## We let the cat out of the bag.

Millions of children might never have met Dr. Seuss and his famous Cat had it not been for The New York Public Library. That's because our renowned children's librarian, Anne Carroll Moore, gave his first book an outstanding review. He became famous overnight, and Dr. Seuss himself credits her with his success.

Others too, credit our librarians. "The people who work here," says author David McCullough, "provide a service to the whole of society that's never sung enough." Indeed, the librarians are the very heart of the Library.

They are the ten librarians who answer five million telephone inquiries a year. They are the librarians who introduce children to the magic of literature and help adults find employment through our Job Information Center. They are also the librarians who select and preserve books for users of tomorrow.

The Library can help just about anyone with anything. Even a Doctor with his Cat.

The New York Public Library where the future is an open book

## **'CRAZY IDEA' WINS NOBEL FOR BINNIG AND ROHRER**

#### NEW YORK

PEOPLE

When Gerd Binnig and Heinrich Rohrer set out eight years ago to build a device that could see individual atoms, their colleagues told them they were "completely crazy." On the other hand, Rohrer recalls, "they also said that if we succeeded we would win the Nobel Prize."

Now the prophecy has come true. The researchers, both career staff members at IBM Corp.'s Research Laboratory in Zurich, will share the 1986 Nobel Prize in Physics with 79-year-old Ernst Ruska, who developed the scanning electron microscope in 1931. Binnig and Rohrer

croscope in 1931. Binnig and Rohrer are credited with developing the scanning tunneling microscope, which allows scientists to study the surface of materials in atomic detail. Their invention has already found wide application in materials research at IBM and other electronics companies, and the scientists believe it is also well-suited for biological studies on viruses, cancer, and DNA.

Rohrer sees some important applications for the technology, especially in next-generation computing, which will require submicron geometries and ultrahigh levels of integration on complex silicon and gallium arsenide substrates. "There is already talk of doing lithography with

ready talk of doing lithography with this technique," he says. The technology may eventually be used to make physical changes to a material, he says.

Binnig, a native of West Germany, and Rohrer, a Swiss, will share their half of the \$290,000 cash prize; Ruska will collect the rest. But Binnig, 39, and Rohrer, 53, say they have not thought much about what they will do with their cash award. Rohrer says that he might build a new house.

When news came earlier this month that they had won, the two were swamped with congratulations from their 120 colleagues at the Zurich labs, and by phone calls from news organizations and friends. "I never experienced anything in my life like this," says Binnig, who joined IBM in 1978 after earning his PhD in physics from Johann Wolfgang Goethe University in Frankfurt, West Germany. "It was really something, all this excitement and all these people coming to shake hands."

The research project was not the result of years of academic contemplation, but rather the fruit of a short discussion on the physical phenomenon of tunneling, in which electrons will jump from one surface to another when the two surfaces are held close together and a current is applied. Still, it took 30 months before Binnig and Rohrer saw their first pictures.

"When we started, I was personally convinced that it would work, but when it did, it really surprised me," says Rohrer, who joined IBM in 1963 after earning his PhD at the Federal Institute of Technology in Switzerland. "It's so amazing that such a primitive instrument could work. Really—it's like a rusty nail you drag across a surface."

which will require submicron geometries and ultrahigh levels of inte-Binnig share the 1986 Nobel Prize in Physics.

The microscope is not that simple. The primary components are a tiny tungsten probe, so fine that its tip is a single atom, and a small clamp to hold the material under study. A small current is applied, creating an electric field between the probe and the material surface, and the probe slowly scans the surface, following its contours atom by atom.

The result is a TV-like image that maps the landscape on the material's surface; each hill is an atom. The technique allows researchers to actually see how atoms bond. Moreover, Rohrer says that the design has been refined so that now resolution is between  $0.7A^{\circ}$  and  $0.8A^{\circ}$  "Now you can actually see the shape of individual atoms," he says.

The most difficult development challenge may have been finding a way to keep the material and probe completely free of vibration. The probe and the material must stay within 5A to 6A of each other for the phenomenon to work, so scanning tunneling microscopes consist primarily of shock-absorbing equipment. The systems, which can be about as small as a grapefruit, must be operated in a vacuum. *—Tobias Naegele*

## ALLOTHERS PALE BEFORE US.

No other color graphics terminal can compare to the GR-1105. In fact, you'd have to spend an extra five or ten thousand dollars to get something even close.

The GR-1105's screen is brighter than anything else in its price class. It's also sharper. With three times the resolution of similarly priced terminals. And sixty times more addressable points (32K x 32K). Plus the GR-1105 is perfect for people who hate to wait. It's twice as fast as its price competitors. And updates over one and a half times more data. So look into the GR-1105. You'll see it's the one terminal that makes all others look pale.

Call Martin Nelson at (408) 943-9100 today.

Circle 17 on reader service card

You're looking at an image on the GR-1105's 14," 1024 x 780, 60Hz non-interlaced monitor. Image produced with Vectart Software from Prosperity Systems.

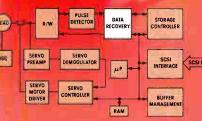

## Now. A FAMILY OF "HDD" DATA RECOVERY CHIPS — EACH WITH A FULL SPECTRUM OF FEATURES.

2,7 ENDEC 15 MBITS/SEC 15 MBITS

For mass storage disk drive electronics - Silicon Systems supports you best with total "head to host" IC solutions. Example: the Silicon Systems Data Recovery IC family. The flagship of this exciting new series is the SSI 532-the industry's most advanced single chip solution integrating data synchronization and ENDEC functions. Designed as a companion device to the SSI 452 and AIC 010 families of controllers, the 532 is destined to become the industry standard. And for good reason: it offers the type of raw performance and exclusive enhancements that really can separate your hard disk drive from the rest.

Just look at what this space-saver offers: 2,7 RLL encoding/decoding; window symmetry control with  $\mu$ P port for enhanced HDD testability; internal timing elements with a single external resistor to set the data rate; a precision decode window without the requirement of an accurate 1/4 cell delay; 15Mbits/sec. operation; fast acquisition PLL; plus a host of other dynamic features that will give your product the competitive edge.

But the SSI 532 is just one chip in Silicon Systems family of five Data Recovery IC's. Each is optimized for a specific type of drive—one is right for your type of drive. In addition to data recovery, Silicon Systems also offers broad IC families to cover virtually all other functions in HDD and FDD disk drive electronics.

For more information on the SSI 532 and other exciting product families in the SCSI chip set, contact Silicon Systems today.

Silicon Systems, 14351 Myford Road, Tustin, CA 92680, (714) 731-7110, Ext. 575.

OCTOBER 30, 1986

## ELECTRONICS NEWSLETTER

#### TI ENLISTS VIDEO-7 TO HELP DEVELOP GRAPHICS INTERFACE

There's a war raging in the 32-bit graphics-processor market between Texas Instruments Inc. and Intel Corp. as each tries to get makers of graphics products to use its chip. In the latest round, TI has signed up Video-7 Inc. to help it develop a standard interface, based on the TI TMS34010 Graphics System Processor chip, for the IBM PC and PC AT. The work will include both silicon and software that will be made available as part of the TMS 340 family. Video-7, Milpitas, Calif., is already a major player in the market for Enhanced Graphics Adapter cards; it says that it will be the first to incorporate the new Microsoft Windows driver of the TMS34010 into a highresolution graphics product. TI's chip was announced last January [*Electronics*, Jan. 27, 1986, p. 67]. Intel's, the 82786, came out in the spring [*Electronics*, May 19, 1986, p. 57].

#### AMD AND SIEMENS SCHEDULE A PIXEL-CONTROL CHIP

■ I and Intel are pushing complete graphics coprocessor ICs, but others play on a lower level of integration by developing chips to be used as parts of coprocessors. One of those players, Advanced Micro Devices Inc. of Sunnyvale, Calif., says it will begin shipping samples of its own graphics chip, the Am95C60 quad pixel dataflow manager, in the first quarter of next year. Siemens AG of Munich will second-source the chip in Europe. AMD, now in beta test, promises full production by the second quarter of 1987.

#### WITH INVESTORS FRIGHTENED OFF BY SUIT, LATTICE SKIPS PAYDAY

he patent infringement suit brought against Lattice Semiconductor Corp. by Monolithic Memories Inc. apparently has indirectly dealt a powerful blow to the 31/2-year-old Portland, Ore., firm. Lattice said last week that because of the suit, several current investors had refused to take part in its \$10 million fifth round of financing. In order to keep afloat, Lattice stopped paying its professional employees, offering them stock and bonuses instead if they stayed on. Nevertheless, 33 of the 176 people in the company's total workforce quit their jobs rather than wait, the company says. The salary holdup may last as long as three months, an internal memo said. Secretaries and employees covered by minimum-wage laws are being paid. The company also persuaded its suppliers to accept deferred payments. "We haven't run out of money," a spokesman says. "However, we are paying essential bills only." Meanwhile, the investment house of Drexel Burnham Lambert is trying to recruit more investors to complete the financing. In its suit, Monolithic Memories, of Santa Clara, Calif., charged that the programmable logic circuits made by Lattice and Altera Corp. were infringing on its programmable array logic patents [Electronics, Sept. 18, p. 23]. Lattice has since filed a \$100 million countersuit. A Lattice spokesman says that bookings remain high, with the largest single-day bookings, \$1.8 million, occurring this month.

#### MOTOROLA TO STAGE SRAM SPEED RACE AT WESCON

Notice of the fierce competition in fast static randomaccess memories with a whimsical marketing gimmick. The Austin, Texas, operation, which offers 64-K parts with speeds of 25 ns, will challenge its SRAM competitors to an access-time race on the floor of next month's Wescon '86 in Anaheim, Calif. Motorola managers in Austin, Texas, plan to have a high-speed tester installed in their booth to measure the speed of parts submitted by customers and competitors. The stunt will be called "The Motorola Shmoo-out at the Wescon Corral." Test programs will record each chip's access time on a Shmoo plot. **OCTOBER 30. 1986**

## **ELECTRONICS NEWSLETTER**

#### UNIVERSITY OF ILLINOIS FINALLY GETS PLATO'S PRICE DOWN...

Plato, the computer-based instruction system that has always been too expensive to fulfill its once-heralded potential, is about to get significantly cheaper. Researchers at the University of Illinois, where Plato was developed 26 years ago, have come up with an approach that relies on new, inexpensive computer hardware as well as satellite transmission to deliver instructional materials more cost-effectively from a central mainframe to remote terminals. Conventional Plato systems rely on older computer hardware and landbased phone lines, and can cost a user around \$60 per month per terminal in long-distance charges. The so-called NovaNET system can run for one-tenth that price, says an official. Control Data Corp. of Minneapolis, which has rights to market Plato, has chosen not to license the satellite-based technology. So NovaNET will will be marketed by a university spin-off company, University Communcations Inc., in Urbana, Ill.

#### ... BUT CONTROL DATA SAYS IT HAS A BETTER IDEA

Now that it has decided not to license the NovaNET technology for Plato, Control Data Corp. says it plans to pursue an even less-expensive approach for low- to medium-volume users, one that does away with mainframe communications costs—which can be as much as 50% of delivery cost. The first example is at an American Airlines training facility, where CDC is installing a Plato system that uses IBM PC AT-compatible work stations teamed with central file servers. CDC has offered work-station-based Plato before, but never on such a powerful machine and always for stand-alone use. The installation is the first Plato from CDC to rely on a local-area network.

#### BUILT-IN SELF-TEST EASES CHECK OF ASIC-EMBEDDED MEMORY

Testing the memories embedded in application-specific integrated circuits may be one of the most time-consuming and expensive tasks an ASIC user encounters while building custom parts into a system. AT&T Co. is taking aim at that problem with built-in self-test circuitry, which makes testing embedded random-access memories almost automatic. At a cost of about 3% of the chip's total area for each on-chip memory block, it can track memory faults to a single pin or gate and can study bridging faults and pattern sensitivities, says David Aadsen, the Bell Laboratories staffer who incorporated this approach into AT&T's ASIC compiler. Aadsen estimates that this self-testing can cut development costs by 10% or more, but he points out that there may be a more significant advantage to the added circuitry: system designers can use it in system-level testing.

#### GaAs MARKET ESTIMATES ARE CALLED OVERLY OPTIMISTIC

Those market studies that several years ago predicted gallium arsenide chip sales would soon amount to billions of dollars missed the mark badly, says a new report by The Information Network. The San Francisco market researcher says the main reason is that the low levels of integration of initial GaAs chips did not provide enough functionality to be cost-effective to customers. "Suppliers are wasting their time trying to establish an MSI and SSI [medium- and small-scale-integration] standard," says Robert N. Castellano, who wrote the report. Also, the suppliers underestimated the lead times from design to chip insertion for military equipment, which drives the GaAs market (see p. 29). As a result, the worldwide market for GaAs devices will not reach the billion-dollar level until 1991, when sales will be \$1.184 billion, he says. Analog integrated circuits will have the lion's share, some \$667 million, compared with \$85 million in 1986.

### A totally integrated development system for software engineering projects of any size.

Now there's a way you can meet software development challenges from integrated circuits to satellites within a single programming environment. It's Digital's integrated set of software tools with third-party applications, all running on our VAX station<sup>TM</sup> family.

For microprocessor applications, use LANDS from Tektronix<sup>®</sup> and software tools from B.S.O. For analysis and design of larger software projects, choose SA/SD Tools from Tektronix CASE Division and DesignAid<sup>®</sup> from Nastec. Add VAXset<sup>™</sup> software – Digital's own integrated coding, testing and implementation tools – to complete the development cycle. To find out more,

write: Digital Equipment Corporation, 200 Baker Ave., West Concord, MA 01742. Or call your local sales office.

© Digital Equipment Corporation 1986 The Digital logo, VAXstation and VAXset are trademarks of Digital Equipment Corporation. Tektronix is a registered trademark of Tektronix, Inc. DesignAid is a registered trademark of Nastec Corporation.

At 11:40 p.m. on April 14th 1912, the *RMS Titanic* struck an iceberg some 400 miles off the coast of Newfoundland. In less than three hours, the 'unsinkable' luxury liner had sunk to the sea bottom in one of the worst maritime disasters of the century. Finding her became a commitment by oceanologists and technologists alike.

Several tried. All failed. For the problems, like the tragedy, were on a grand scale. The North Atlantic is not known for its hospitality. And the freezing waters are nearly 2.5 miles deep. To add to these difficulties, not only was *Titanic's* last radio position known to be inaccurate, but fierce currents had also swept her away in a south-easterly direction.

Last year, however, after the French ship *le Suroît* had covered 80% of the target zone, the French-American expedition team embarked on the high-technology research ship *Knorr*.

This high-technology included a pair of MAGNAVOX\* satellite navigation receivers - one providing highly accurate position information by tracking satellites of the new global positioning system, the other providing periodic position updates from transit satellites. With these two receivers onboard, the *Knorr* was equipped with the most precise and sophisticated marine navigation system available.

The MAGNAVOX receivers were used to criss-cross the remaining 20% of the search area, working to a position accuracy of just 35 meters. Even in heavy seas. Then, starting from the most likely spot, the underwater search vehicle *Argo* was lowered to begin close-up investigation.

At 1:05 a.m. on September 1st, 1985, her video cameras recorded the eerie outline of one of *Titanic's* mighty boilers. The seventy-three year search was over.

Little wonder that our satellite navigators are used aboard thousands of offshore platforms, rigs and ships - including *Queen Elizabeth II* - and that our global positioning system receivers are leading the way in precise navigation, on land, at sea and in the air. Because no matter where you look, you won't find anything better.

# The secret of finding is know

© WOODS HOLE OCEANOGRAPHIC INSTITUTION

# wing where to look. Philips.

From the depths of the ocean to the depths of space. One of the most demanding endeavours is the scientific exploration of the sun - a research programme conducted by NASA in collaboration with the European Space Agency, ESA.

Key to this research is SPACELAB 2; fifteen tons of advanced space technology launched in August 1985. The problem was how to ensure that, once in orbit, SPACELAB 2's platform, with the powerful telescope, could be manoeuvred under remote control without any sensitivity to the shuttle motions.

The solution was provided by three SODERN\*\* SED 04 star trackers integrated by Dornier in the Instrument Pointing System responsible for positioning the platform. Each of these electronic sensors operates to an accuracy of 0.75 seconds of arc - which is roughly equivalent to a golf ball seen from 10,000 meters. Distance, however, is no problem, for the platform responds perfectly to every command from mission control some 300 km below. Which is hardly surprising, for similar SED trackers have been operating on EXOSAT for over 3 years.

In fact, SODERN, as world leader in attitude measurement and star tracking, has been involved in major European and U.S. space programmes, providing over 90 opto-electronic systems with more than 200 years of operation without a single failure.

A convincing record of technology at the highest possible level.

#### Philips. The sure sign of expertise worldwide.

\* MAGNAVOX – a bigb tech North American Philips research company. The operations of Magnavox Government and Industrial Electronics Company (MAGIEC) and its subsidiaries are conducted on a substantially autonomous basis. The stock of MAGIEC has been placed in a voting trust to facilitate MAGIEC's industrial security clearance with the U.S. Department of Defence.

"SODERN - a bigb-tech French Philips research company specializing in e.g. attitude sensors for satellites and spacecraft; positioning and alignment of inertial platforms; rendezvous and docking; remote sensing of Earth resources, etc.

Circle 23 on reader service card

Philips Corporate Marketing Communications, Eindhoven, the Netherlands.

# Here comes the most amazing data acquisition board in the VME world.

The DT1401 gives you all major input/output functions on one board - so it's literally four boards in one. You get up to 32 channels of analog input for measurement, two digital-to-analog converters, and 16 digital I/O lines for control. There's even a real-time clock for controlling the A/D sampling rate.

This amazing board gives you different A/D options for different applications. 12 or 16 bit resolution. Differ-

Data

16 Digital 1/O Lines

Acquisition

Module

ent gains for different input ranges. Simultaneous sampling. High speed. If you need it, this board delivers it.

For example, if you need flexibility of A/D operation, this board gives you single channel sampling or channel scanning with triggering by program control, by clock tick, or by an external event. It even has interrupt with seven-level priority.

Of course, we realize that

not all of you will need the best data acquisition board in the world, so for you we also designed the widest selection of VME data acquisition boards in the world. Call today. As a further convenience to our

customers, Data Translation provides the fastest delivery in the world.

See our new 646 pg. catalog/ handbook or see us in **Gold Book** 1986. Or call for your personal copy today.

VMEbus P1 Connector

Call (617) 481-3700 DATA TRAN 5L/

World Headquarters: Data Translation, Inc., 100 Locke Dr., Marlboro, MA 01752 (617) 481-3700 Tix 951 646 European Headquarters: Data Translation, Ltd., 13 The Business Centre, Molly Millars Lane, Wokingham Berks, RG1120Z, England Tix 851849862 (#C) International Sales Offices: Australia (61) 2-6635289. Belgium (32) 2-7352135; Canada (416) 625 1907; Chile (2) 2-253689; China (408) 727-8222, i86) 87214017; Denmark (02) 137188; England (44) 0734 793838; Finland (358) 0-372 144; France (33) 146306839; Greece (30) 031-527039, (30) 13-614300, (30) 95 14944; Hong Kong (852) 3-324563; India (91) 2-231040; Israel (972) 3-324298; Italy (39) 2349751; Japan (81) 3 502-5550, (81) 3-336-8301, (81) 3-355-1111; Korea (82) 753-3101; Malaysia (60) 3-36299; Morocco (21) 9 30-6949; Netherlands (3 70996360; New Zealand (61) 2 663-5289; Norway (47) (02) 559050; Peru (51) (14) 31-8060; Philippines 818 0103: Portugal (351) 1545313; Singapore (65) 271 3163; South Africa (27) 12469221; Spain (34) 14558112; Sweden (46) 87617820; Switzerland (41) 17231410, (41) 22360830; Taiwan (86) 2-721-7864, (86) 2-531-2434; West Germany (49) 89809020. nds (31) **OCTOBER 30, 1986**

## **PRODUCTS NEWSLETTER**

#### TWO CMOS VERSIONS OF 1750A MICROPROCESSOR INTRODUCED

Squaring off in toe-to-toe competition for the military digital avionics microprocessor market, Performance Semiconductor Corp. and LSI Logic Corp. have each announced CMOS chips functionally equivalent to Performance's 1750 bipolar device. Performance, of Sunnyvale, Calif., calls its 1750A the world's fastest single-chip implementation of the MIL-STD-1750A instruction set. Available in 20-, 30-, and 40-MHz versions, the fastest version executes the complete Digital Avionics Information System benchmark at 2.6 mips and consumes less than 1 W. LSI Logic's 1750A implementation is rated at 25 MHz and is available as a single device or as a cell in a larger chip. The Milpitas, Calif., company will introduce it at the 1750 users conference next week in New Orleans. □

#### DESIGN TOOLS FOR LOW-DENSITY GATE ARRAYS RUN ON IBM PC AT

**M** onolithic Memories Inc. is pegging its move into the low-density gatearray market to a set of menu-driven design tools that execute all design functions, including simulation, on IBM Corp. PC AT and compatible computers. Monolithic Memory's gate-array family, built in a sub-2- $\mu$ m twin-well, double-layer CMOS process, has eight members ranging from 720 to 6,000 gates. The Santa Clara, Calif., company offers an integrator module that converts PAL designs to gate arrays, and a library of 200 TTL macros. The complete system, with the PC AT, costs \$30,000.

#### **REACTOR PROMISES \$75 EPITAXY COST FOR GAAs WAFERS**

Grystal Specialties Inc. should draw a lot of attention at Semicon in Tokyo this December. Its Model 411 metal-organic chemical-vapor-deposition reactor offers the promise of a seven-fold cut in the cost of growing epitaxial layers on 3-in. wafers in production volumes compared with molecular-beam epitaxy. Claiming a yield of 1,000 wafers a month in continuous operation, the Portland, Ore., company estimates an average epitaxy cost of about \$75 per wafer, compared with \$500 per wafer using MBE. A producer of laboratory epitaxy equipment for 12 years, Crystal claims its \$350,000 Model 411 yields research-grade results in high-volume production—specifically, high uniformity and precise junction lines for gallium arsenide and other III-V and II-VI materials. □

#### FIBER-OPTIC MODEM MULTIPLEXES TO GET 19.2-K-BYTE/S DATA TRANSFER

A new fiber-optic modem from AT&T Technology Systems Inc. transmits data in full duplex over a single strand of fiber, multiplexing fast enough to be fully transparent to the user while maintaining the 19.2-kilobyte/s rate called for by the RS-232-C standard. Designed to replace the standard RS-232-C connector, the asynchronous RS-232-2 has two control lines and two data lines. It costs \$105 in 100-unit quantities; \$85 in orders of 1,000.

#### **INMOS CASCADABLE DSP RUNS AT 320 MILLION OPERATIONS/S**

By combining thirty-two 16-by-16 multipliers and thirty-two 36-bit adders on a single CMOS chip, Inmos Corp. has attained processing speeds of 320 mips in its IMS A100 cascadable digital signal processor. The Colorado Springs subsidiary of the Bristol, England, company is aiming the device toward high-speed communications, radar, speech processing, and image processing. The chip will be shown at Wescon in Anaheim, Calif., Nov. 18-22 and at Electronica in Munich Nov. 11-15. The IMS A100 costs \$406 each in 100-unit lots.

## This is a Motorola semi-custom chip.

Our Application Specific Integrated Circuits offer an economical path to a wide variety of devices. Using Computer Aided Design, our customers can develop instructions that we can transform into fully-tested prototype chips in as little as three weeks.

## It counts. res. Ŋ nost thin ks. t a **KPS** 12 **ICts** nd **lore** he 1 IS, sa 62 ρ 'ORO LA **Advanced Electronics for** a More Productive World.

# EVERY BUSINESS NEEDS AN IBM-PC WHO WANTS TO PAY IBM PRICES? WE HAVE A SOLUTION!

<u>isk \$1399.00</u>

\$950.00

**Compatible PC-X**

LEASE

Our **PC-XT SUPER TURBO COMPUTER** runs all the popular Business Programs, like Lotus 1, 2, 3, Word Perfect, Wordstar, dBase III, Homebase, Sidekick, and Flight Simulator. In addition to running the programs at the standard IBM clock speed of 4.77 Mhz, it also runs at 8 Mhz — **almost twice as fast as IBM**.

BASE

With 20 M

ACS has developed the fastest, most powerful XT and AT computers available today. We have also researched the numerous software programs available to automate your office. If you are considering buying a computer, call ACS. We can recommend the software and hardware system that will best solve your business needs.

#### HERE'S WHAT YOU GET

ACS-Turbo Mother Board 4.77/8.0 Mhz 640K of RAM Two 360K Floppy Drives Heavy Duty 135 Watt Power Supply Keyboard New ''AT'' Type with Large Enter Key Parallel Printer Port Monochrome Graphics Display Card High Resolution Mono Monitor with Swivel Base and Anti-Glare Screen

#### **OPTIONS**

| 20 MEG Hard Disk             | \$449.00 |

|------------------------------|----------|

| 20 MEG Tape Back-Up          | \$595.00 |

| Clock/Calendar               | \$ 59.00 |

| Internal Modem 300/1200 BAUD | \$199.00 |

| Okidata 192 Printer          | \$399.00 |

#### **PROGRAMS INCLUDED**

Included in the purchase price is MS-DOS, the standard IBM operating system. With our Hard Disk Computer, you also get HOMEBASE, a general purpose multi-function program to perform word processing, electronic filing, and data base management. HOMEBASE has a built-in calendar, with monthly, weekly, and daily scheduling. The Homebase Calculator lets you perform calculations on the monitor and the ability to print a paper tape if desired. HOMEBASE also includes a communication program with autodialer for communication with other computers (requires a modem).

STANDARD

MODEI

**Upon Approved Credit**

SE\$56/

#### 5 YEAR WARRANTY AVAILABLE

#### **GUARANTEE & WARRANTY**

We guarantee you will be delighted with our ACS-Turbo Computer or return it within 30 days for a refund (less shipping charges). We warranty our Turbo Computer 100% Parts & Labor for 1 year. We believe our computer is even more reliable than IBM — that's why we're offering a five-year extended warranty for only \$30.00 a year. Order early for the holidays — delivery may take over 30 days.

#### HOW TO ORDER

Call us at (818) 889-1092. We have experienced salespeople to advise you with your computer requirements. Ask for our experts — ask for Department FD.

You can charge our **ACS-Turbo Computer** with a VISA or MasterCard. We also have a lease plan available for qualified businesses, with payments from 36 months to 60 months.

\*IBM is a registered trademark of International Business Machines.

5311 Derry Avenue, Suite A, Agoura Hills, CA 91301 Phone: 818/889-1092 Fax: 818/889-5605 Telex: 299 353 POST UR EASY LINK Mailbox: 62941735 Telex: 5106018224 ACS AGRA HILLS UQ

## **Electronics**

## THE RACE IS ON TO DEVELOP **MICROWAVE GaAs ICs FOR DOD**

#### MIMIC COULD DO FOR GAAS WHAT VHSIC IS DOING FOR SILICON

#### WASHINGTON

dozen or more contractors submit-A dozen of more concrete jor new military development program that could do for gallium arsenide what VHSIC is doing for silicon technologyvastly accelerate the technological learning process. Called MIMIC, for microwave and millimeter-wave monolithic integrated circuits, the effort should give the U.S. a big boost in an area where experts say Japan currently leads.

While VHSIC (for very high-speed integrated circuits) aims primarily at logic circuitry such as microprocessors and other computational elements, MIMIC aims at producing a reliable and afford-

able supply of complex GaAs chips for the next generation of communications and weapons-sensor hardware. As Kenneth Entwistle, contract officer for the MIMIC effort, says, "VHSIC is the brains, while MIMIC is the eyes and ears.'

Such GaAs devices are not being produced commercially because of excessive costs and technology limitations. DOD planners concluded last year that these parts might never surface without a program to encourage their development.

Procedurally, MIMIC resembles the VHSIC effort, which was launched for similar reasons more than five years ago ers. And as MIMIC picks up

momentum, the tie between the two will become closer, since they will be run by the same officials, according to a spokeswoman in the VHSIC office. Lead agency for MIMIC is the U.S. Army's Electronics Technology and Devices Laboratory in Ft. Monmouth, N.J., which received last week's industry bids for the initial Phase 0 stage.

The reliability goals of MIMIC are much more stringent than for previous GaAs chips. Failure rates for packaged chips cannot exceed 0.006% per 1,000 hours, at a 60% statistical confidence level, operating over the full military

temperature range of  $-55^{\circ}$  to  $\pm 125^{\circ}$ C. The Army document that seeks Phase 0 proposals is called a Broad Agency Announcement and is considered by military contractors to be a way of streamlining initial procurement. About 300 announcements went out, and-based on the DOD's experience-up to 15 contractors, most of them working in teams. are likely to respond. The VHSIC office plans to issue a formal request of its own for proposals later this year, but contractor sources say that the same companies will likely take part, and the Army and VHSIC-office MIMIC programs would essentially merge.

Among the teams bidding on MIMIC

are GM-Hughes Electronics and General Electric, Texas Instruments with Ravtheon, Westinghouse Electric and Rockwell International, and TRW with Honevwell.

The word among contractors is that perhaps nine will be chosen around late January for the 12-month Phase 0. Follow-on Phases 1 and 2 will likely run 36 months each, and Phase 3 will be carried out in parallel with them. DOD is asking for upwards of \$135 million to fund MIMIC for the 1987 fiscal year.

Although the Phase 0 announcement asks prospective suppliers only for a

"technology road-map/plan" leading to building devices in Phases 1 and 2, the outlines of the entire program are clearly visible. Besides calling for the expected requirements for computer-aided design techniques, circuit layout, and testing, MIMIC also emphasizes the need to improve materials and manufacturing processes in order to achieve higher-volume production and reasonable yields, both of which are major problems for GaAs chip makers. Phase 3 sets up research programs at industry and university labs at the same time as the Phase 1 and 2 devices are developed.

Volume "is the key issue for the kinds of very complex circuits MIMIC

needs," says Robert N. Castellano, a San Francisco-based market analyst. "Not enough experience has been gained so far in turning out large-scale GaAs ICs. Everybody is still at the SSI and/or MSI level." Castellano, president of The Information Network, recently completed an extensive study of the GaAs business. He says that only the U.S. military has the buying clout to spur GaAs development.

The small circle of GaAs chip makers is enthusiastic about MIMIC, which can foot the bills for expensive, and heretofore largely neglected, research. "There's a trementechnology across the board.' says Hughes Aircraft Co.'s

Eugene H. Gregory, in a typical view. He agrees that yields and volume have high priority, but he says the basic materials step—growing better GaAs crys-tals—is a key job. Gregory heads Hughes' MIMIC effort for the Radar Systems Group, El Segundo, Calif., where he also is chief scientist of the Rf System Laboratory.

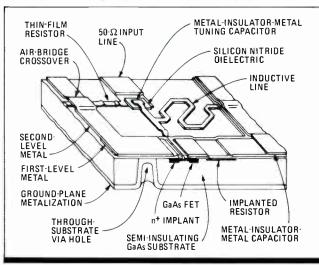

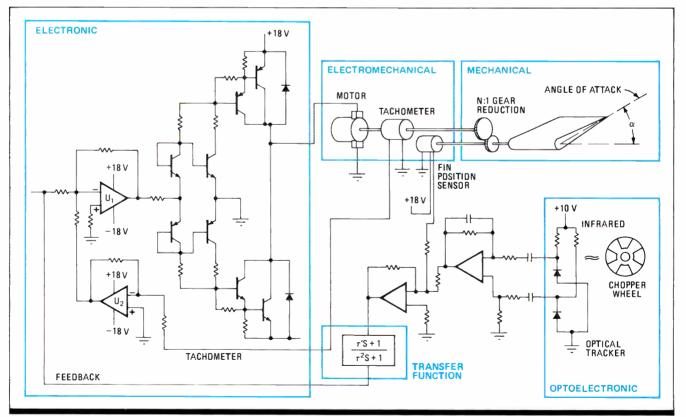

The types of circuits sought by MIM-IC typically operate above 2 GHz, combine digital and analog functions, and integrate a number of passive and active components (see figure). Castellano points out that their complexity makes

them very difficult to build—they require up to 11 mask levels, including a metal-semiconductor FET structure.

But the GaAs performance is indispensable for transmitter and receiver modules in new phased-array radar systems, satellites, and avionics packages. Such top-priority programs as the Milstar satellite program and radar for the Strategic Defense Initiative are among

#### many potential applications.

Because speed is inherent in GaAs devices, MIMIC does not emphasize performance, as does VHSIC, but it does require substantial radiation hardening. The MIMIC circuits must operate in a radiation environment of at least  $10^6$  rads, compared to the total-dose requirement of  $5 \times 10^4$  rads for VHSIC Phase 2 devices. *-Larry Waller*

#### MILITARY

### **IBM HITS 1-MICRON LEVEL ON PHASE 2 VHSIC CHIPS**

#### NEW YORK

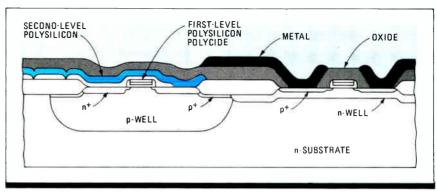

The race to produce 0.5- $\mu$ m chips for Phase 2 of the Defense Department's Very High Speed Integrated Circuits program is tightening up. IBM Corp. revealed last week that it has produced functional prototypes of two 1- $\mu$ m chips for Phase 2. It says it will have first silicon of 0.5- $\mu$ m parts by mid-1987.

The other two competitors in the hard-fought race, TRW and Honeywell, also have recently delivered test chips to the DOD. All three companies are proving out their technology.

To meet the requirements of the fouryear Phase 2, the contractors must produce working chips with 0.5-µm design rules by 1988. The three are following different strategies—IBM, for example, is using CMOS for its five-chip set, and Honeywell is using bipolar technology to produce its five devices. TRW plans a set of six "superchips," which will incorporate features such as self-configuration, a triple-redundant bus, and automatic repair using on-chip spare components. Four of them will be built in CMOS, and the other two will use triplediffusion bipolar technology [Electronics, July 10, 1986, p. 49].

IBM's Federal Systems Division, Manassas, Va., appears to have a slight edge over TRW and Honeywell with its new 1-µm prototypes. Shrinking the designs to the required  $0.5 \ \mu m$  is still a major challenge, but the company has processed some test devices at 0.5 µm. GOING FOR BROKE. Honeywell, however, is the surprise contender. It is pushing directly from the 1.25-µm technology of Phase 1 to the 0.5-µm requirements of Phase 2. George A. Anderson, VHSIC submicron program director for Honeywell's Solid State Electronics Division in Plymouth, Minn., says the company expects to send its first 0.5-µm circuit design, a bus interface unit, to the foundry before the year's end.

The bus-interface chip, which is scheduled for September 1987 delivery, will be joined on the line by an array processor unit, the largest of the set with about 30,000 gates, and an 18,000-gate array processor controller. The final ICs in Honeywell's set are two 50-MHz memories built with Phase 1 technology: an 18-K random-access memory and a 144-K read-only memory.

The Honeywell bus-interface chip will integrate about 16,000 gates. It will eventually be enlarged to encompass about 28,000 gates for use in a brassboard demonstration of an electro-optic signal processor scheduled for October 1988. Honeywell, which is using electron-beam technology for 12 of the 14 production steps, will get first-pass parts on the other two logic circuits late in the third quarter of 1987, according to Anderson.

TRW Inc., meanwhile, is developing and testing its technology piecemeal, producing devices that incorporate only elements of the circuits it hopes to produce. This approach tests the macrocell architecture of TRW's superchips. TRW says it has a 750-K memory now in fabrication using both the 1.25-µm CMOS design rules developed under Phase 1 and some 1-µm features.

#### INTERNATIONAL TRADE

One reason for IBM's two-tiered approach of first proving designs at 1  $\mu$ m and then shrinking them by half may be a switch in tactics—though Big Blue isn't offering an explanation. In Phase 1, it used n-MOS technology to produce its 1.25- $\mu$ m parts. Now it is switching to CMOS, essentially starting over. Bob Estrada, VHSIC program manager at the Federal Systems Division, says IBM shifted because "we believe CMOS is really a preferred technology for DOD systems."

CMOS technology's small appetite for power makes it ideal for military systems that often rely on battery or generator power, Estrada says. Moreover, "the real benefit of CMOS is that it is also attractive from a radiation-hardening point-of-view," an important consideration since such hardening is mandated in the VHSIC contract. CMOS also offers very good performance and density profiles when contrasted with competing technologies, he says.

**GROUNDWORK.** In proving its 1- $\mu$ m CMOS process, IBM is laying the groundwork for what it hopes will be an easy migration to smaller line widths. The 1- $\mu$ m technology supports between 20,000 and 50,000 equivalent gates on each chip. So far, it has produced functional 1- $\mu$ m devices for its bus interface unit and an 18-K configurable static RAM chip, which carries some logic in addition to memory. IBM's other three parts are on the 1- $\mu$ m pilot line now.