### NCR

ASICs have become an integral part of today's automotive products.

Improving performance.

Increasing reliability.

Enhancing driver safety and convenience in ways unimaginable just a few years ago.

In this very demanding industry, on the most unforgiving proving grounds, NCR has earned an enviable reputation for first-pass success, responsive service and high quality.

Today, we have a solid track-record of successful ASIC programs with all the major U.S. automotive corporations spanning initial design to high volume production—including "Just In Time" delivery and dock-to-stock QA programs.

And NCR design tools are becoming the choice of fast-track ASIC designers. With NCR Design Synthesis<sup>™</sup> and Design Advisor<sup>™</sup> expert system, designers can spend more time creating, less time bogged-down in minute details.

To kick the tires on our automotive, commercial and military ASIC libraries, call today: 1-800-334-5454.

NCR Microelectronics, 1700 South Patterson Blvd., Dayton, Ohio 45479.

# Style & Silicon.

#### **Electronic Instrument Cluster**

Mixed mode system-on-a-chip replaces traditional 2-to-3 chip discrete implementations. Includes a 68HC05 microprocessor core, plus memory, analog functions and digital glue logic. Design Turn: 26 weeks.

#### Light Controller Chip

Single chip solution includes all the digital, analog and memory functions to control headlights, parking and fog lights. Provides exit delay timer and allows manual control of exterior lights from driver door. Design Turn: 14 weeks.

#### **Keyless Entry**

Chip contains EEPROM supercell that provides direct write capability for flexible security code generation. Ten years data retention and 10,000 read/ write cycles for harsh automotive environment. Can be configured for dual or single supply programming. Design Turn: 14 weeks.

© 1989 NCR Corporation. Design Advisor and Design Synthesis are trademarks of NCR Corporation.

Circle 1

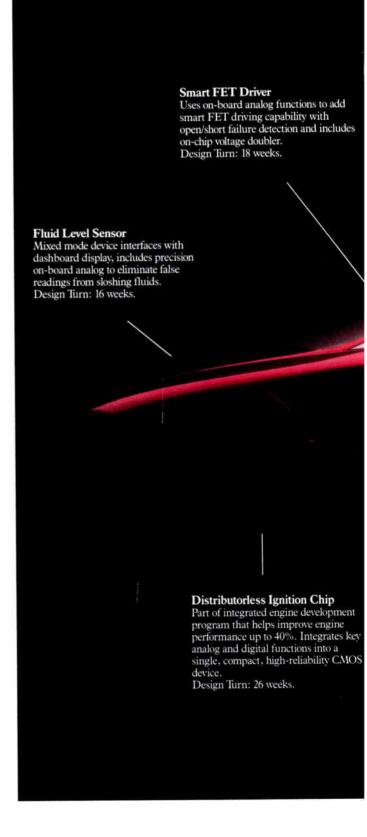

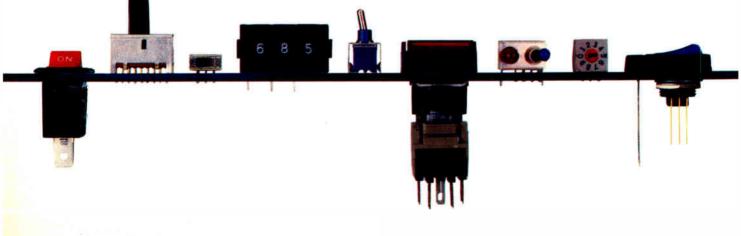

## SIMPSON UNIVERSAL FREQUENCY COUNTERS. COUNT ON US FOR ACCURACY.

Simpson's new high precision, eight digit frequency counters give you an eye into the world of critical clock signals, RF oscillators and data communications.

Readings of frequency (to 1.3 GHz), frequency ratio (A/B), period, time interval (A to B) and totalized count combined with multi-channel triggering let you find circuit problems that might otherwise go unnoticed.

Simpson's *Professional Series* frequency counters allow for accurate measurements to be

taken on complex and noisy wave-forms by using the variable trigger controls and built-in, low pass filter. One model even offers you selectable attenuation and

AC/DC coupling, allowing the inputs to accommodate a range of signal characteristics. For more complex measurement situations involving two interdependent frequencies, an external clock can be substituted for the internal oscillator. This feature enables you to investigate a wide spectrum of frequencies—from computer circuitry to satellite communications.

Try the new lineup of *Professional Series* frequency counters from Simpson. It all adds up to accuracy and reliability.

Circle 2

Simpson Professional Series products are made in USA

Simpson Electric Company 853 Dundee Ave., Elgin, Illinois 60120-3090 312/697-2260 FAX: 312/697-2272

### **Electronics**

EDITOR-IN-CHIEF Robin Nelson

#### EXECUTIVE EDITORS Jeremy Young

Beniamin A. Mason (Special Projects)

MANAGING EDITOR Howard Wolff

EDITOR-AT-LARGE Samuel Weber

SENIOR EDITORS Bernard C. Cole, Tom Manuel, Jonah McLeod

#### DEPARTMENT EDITORS

Component Technology: Bernard C. Cole (San Jose) Communications: Jack Shandle Computers & Software:

Tom Manuel Industrial & Consumer Markets: Wesley R. Iversen (Chicago) Military & Aerospace Markets: Tobias Naegele (Washington) System Technology: Jonah McLeod (San Jose)

> **NEWS ANALYSIS** Howard Wolff, Larry King

**EDITORIAL PRODUCTION** Charles D. Ciatto (Manager) Elsa M. Pecoroni

COPY EDITORS Jacqueline Damian (Chief) Mary K. Caulfield

ART Mark Montgomery (Associate Director)

Janet Kroenke (Technical Illustrator)

#### NEWS BUREAUS

West Coast Executive Editor: Dave Bursky (San Jose) Boston: Lawrence Curran, Manager Chicago: Wesley R. Iversen, Manager Los Angeles: Larry Waller, Manager Mid-Atlantic: Jack Shandle, Manager Washington D.C.: Tobias Naegele Tokyo: Charles L. Cohen, Manager Frankfurt: John Gosch, Manager UK Correspondent: Peter Fletcher

> EDITORIAL DIRECTOR Stephen E. Scrupski

EDITORIAL PRODUCTION DIRECTOR Anne Gilio Turtoro

> GROUP ART DIRECTOR Peter Jeziorski

EDITORIAL ADMINISTRATION Tina A. Montone

Director of Sales: Tim 1 Tobeck **Regional Sales Managers** John R. Carroll (East/Midwest) Thomas A. Conway Jr. (South/Southwest) Director of Circulation: Barbara Freundlich Manager of Circulation: Cindy Stump Reader Service Manager: Paula Greenleaf Production Director: Aldo F. Ullio

VNU BUSINESS PUBLICATIONS INC. President: Robert J. Lydon Group Publisher: Paul Mazzacano Publisher: James C. Uhl

#### **CAN HARDWARE ARTISTS LEARN TO CODE?**

The new era of product design will have hardware people doing something suspiciously like programming—and many may resist

ey, I've been called a wirehead myself, and taken it as a compliment, too. But I've also dabbled in software, just to see.

The time has come, however, for hardware-oriented wirehead engineers to do more then dabble in code. You've heard it before: hardware is software. This time it's coming true, though-hardware design is fast becoming a coding exercise. Engineering work for most circuits above the transistor level can be done by writing lines of code that look just like lines of C or Ada.

It wasn't hard to predict, as computer-aided engineering grew in popularity, that eventually the computers would give up the pretense of being drafting tables and demand to be fed not diagrams but modules, procedures, lines of code. Now the hardware-is-software crowd has gotten together on a language standard: VHDL. (That's V as in VHSIC, for the Pentagon's Very High Speed Integrated Circuits program, and HDL for hardware description language.) Last year the IEEE set its stamp on a version of the DODmandated language, and now CAE's biggest gun, Mentor Graphics Corp., San Jose, Calif., has jumped into the game (see p. 77).

It's time for hardware engineers to start learning to write VHDL code. There are very few now who can, say participants in the still small VHDL-simulator market. Some observers are very doubtful about the ability of most system engineers to make so radical a change in their way of thinking. Vantage Analysis Systems Inc. of Fremont, Calif., for example, has gone to great lengths in its VHDL simulation product to hide the language from the user. Vantage's simulator presents him with familiar schematic views and a library of VHDL function models. If he should need a new one, says Vantage, he'll commission it from specialists.

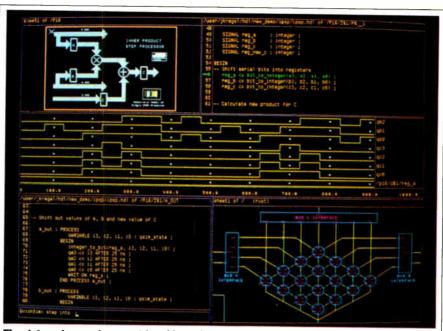

The approach would appear sensible at a time when next to no engineers are competent in VHDL, and while satisfying Uncle Sam with VHDL documentation is the main aim. But in the long run, Mentor's courageous position promises the industry a bigger payoff. Mentor's new VHDL tools draw the CAE user into the language; to get any real leverage from them, the user must learn how to write code. But once he does, he can do things he never did before. He can play around with simulations of his system using high-level behavioral descriptions, finding flaws and bottlenecks in an architecture before fixing them means murdering the schedule.

The people at Mentor know that there's but a handful of engineers who can use their tools; that's why they're setting up a big training program. Until engineering schools get geared up, Mentor must educate every new user. It's going to be a hard row to hoe.

It is a giant leap. Many engineers won't make it. But I'm convinced that system builders who move fast to build a cadre of VHDLliterate engineers will win a valuable time-to-market edge. Tell your wireheads a secret: writing code can be fun! JEREMY YOUNG

February 1989 Volume 62, Number 2 108,608 copies of this issue p Electronics (ISSN 0883-4989), Published monthly by VNU Business Publications inc. Publication office. Ten Holland Drive, Hasbrouck Heights, N. J. 07604; second class postage paid at Hackensack, N. J. 07602 and additional maing offices Executive, editorial, circulation, and advertising addresses: Electronics, Ten Holland Drive, Hasbrouck Heights, N. J. 07604, Telephone (201) 393-6000, Facsmile (201) 393-6386. TWX 710-990-5071 (HAYDENPUB H9H1), Cable Haydenpubb; Title registered in U.S. Patent Office Copyright 1989 by VNU Business The reproduced in whole or in part without the consent of the copyright owner. February 1989 Volume 62, Number 2 108,608 copies of this issue printed

Where necessary, permission is granted by the copyright owner for ibraries and others registered with the Copyright Clearance Canter (CCC), 21 Congress Street, Saler Mass, D1970, to photocopy any article herein for for a fee of \$5.50. Payment should be sent directly to the CCC. Copyrig done for other than personal or internal reference use without the express permission of VNU Business Publications Inc. is prohibited. Requests for special permission or builk orders should be addressed to the editor. ISSN 0883-4989/89 \$0.50 + 25. For subscriber change of address and subscription inquiries, call 215-630-4277. POSTMASTER: Please send change of address to FLECTRONICS.

POSTMASTER: Please send change of address to ELECTRONICS, P.O. Box 1092, Southeastern, Pa. 19398.

# **Electronics**

#### NEWSLETTERS

#### **Electronics**, 17

- A graphics system for Apollo's desktop supercomputer, finally

Here's a peek at Motorola's microcontroller plans

- OSF delivers a user-interface technology—and it's on time

#### **Products to Watch, 23**

• Heurikon's VME board does bitblock transfers twice as fast as the competition

• Data-compression software doubles capacity of quarter-inch tape drives

Data General shifts OSI interoperability into high gear

A 32-megaflops compute server for Macintosh networks arrives

#### Washington Insider, 65

• Equipment makers are asked to stimulate U. S. DRAM production . . .

... and, with chip makers, may have a new solution for pricing

Will Congress take on some risk in the HDTV gamble?

Regulating DOD consultants: how much disclosure is enough?

#### Pacific Rim Trends, 69

NTT reports dramatic advances in optical data transmission

A new Japanese consortium plans to develop fuzzy computers

IBM and DEC subsidiaries in Japan get a foothold with NTTsponsored project

#### European Observer, 71

Europeans hammer out the financial details for Jessi

Another alliance: Siemens buys majority share in France's IN2

Intermetall's new audio chip set lures a major U. S. carmaker

#### FEATURES

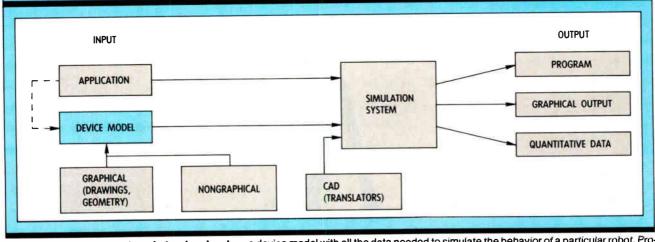

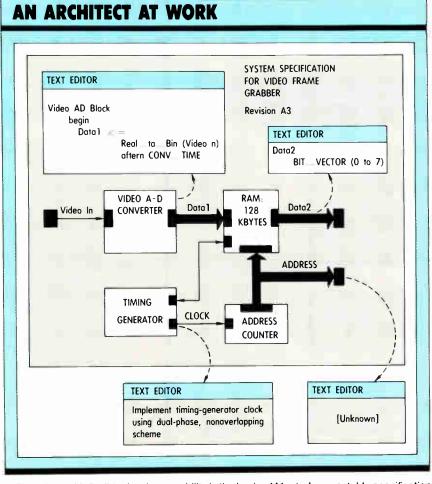

#### **COVER: A giant leap for simulation, 73**

CAE vendors are pulling system builders toward VHDL, the hardware description language spun out of the Defense Department's Very High Speed Integrated Circuits program; design simulation will never be the same

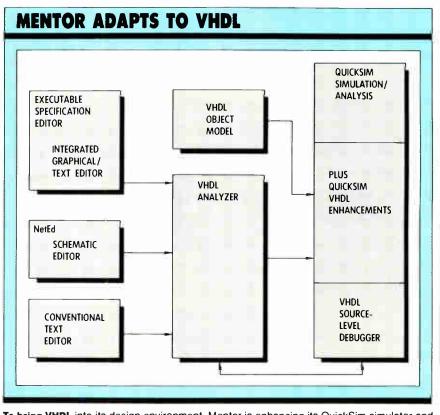

Mentor Graphics bites the VHDL bullet, 77

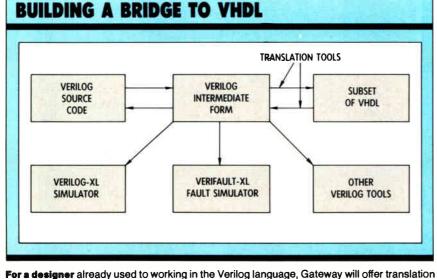

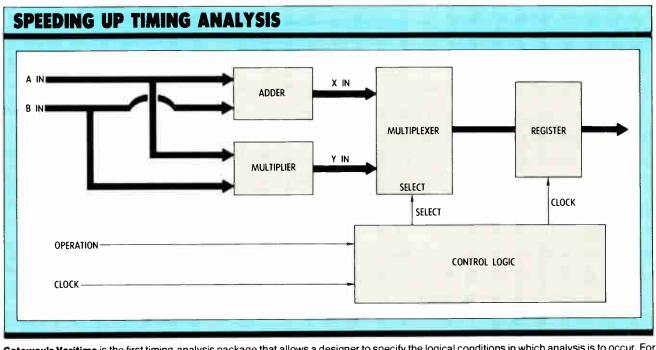

The language is the centerpiece of its new CAE strategy • Gateway's simulator improves its timing, 80

It's working on a VHDL strategy; in the meantime, the company is rolling out a high-speed timing analysis tool

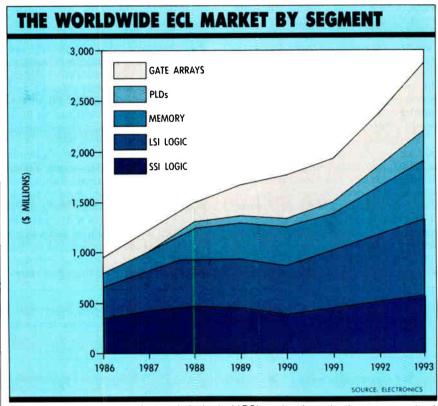

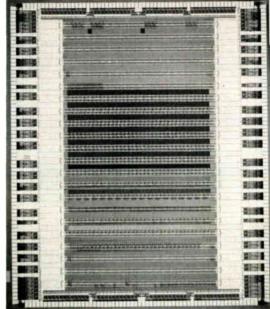

#### The new race in fast logic, 84

Fast integrated circuits are no longer enough in the ECL arena; now ICs have to offer lower cost, higher density, better noise immunity, and lower power consumption—which is why GaAs, CMOS, and biCMOS chips are appearing in ECL-compatible form

- Aspen shows biCMOS can yield fast static RAMs, 88

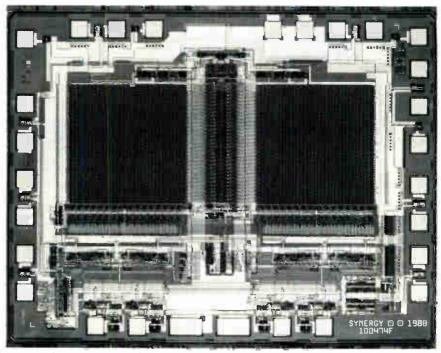

- Synergy taps isolation instead of shrinking geometries, 89

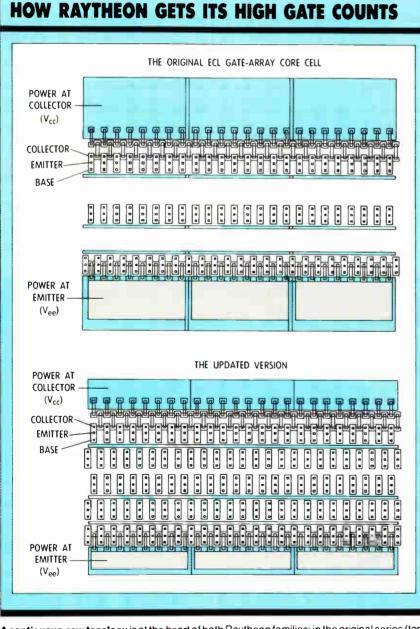

- Raytheon boosts density in a 2.0-micron process, 90

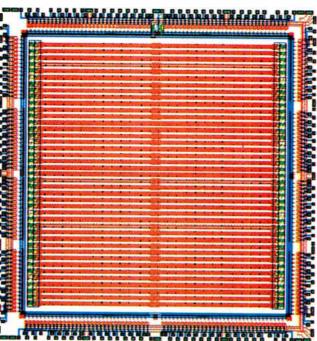

- Vitesse's gallium arsenide equals ECL's density, 92

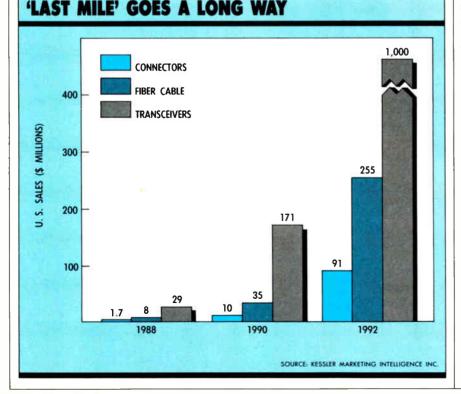

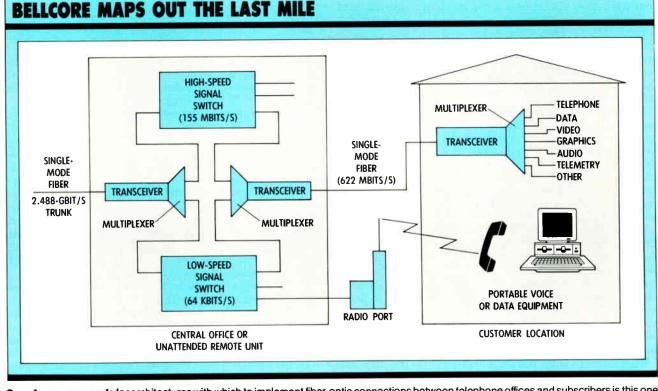

In fiber optics, the battle to close the local loop begins, 94 Phone companies vie with cable-TV firms to string lines linking customers with local branch exchanges

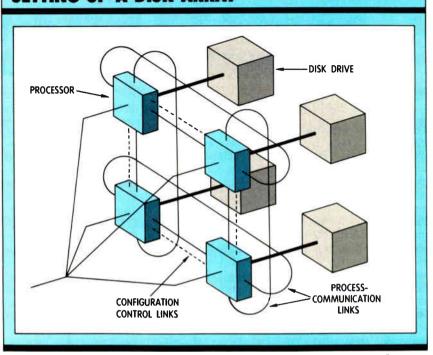

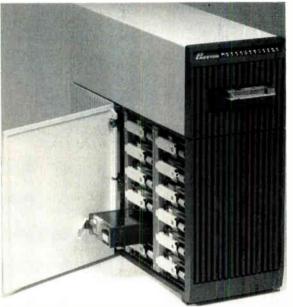

Arrays of disk drives break the data-transfer logjam, 97 Parallel-processing architectures for disk subsystems could boost data-transfer rates enough to match high-speed processors

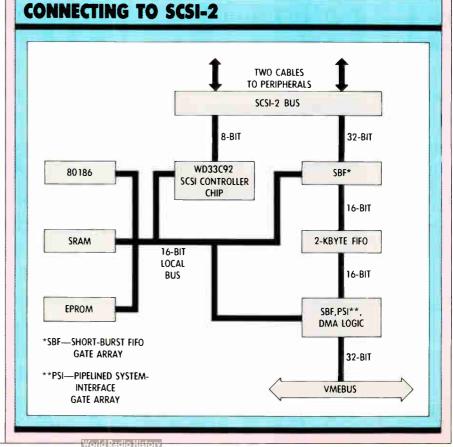

The high-performance son of SCSI is coming soon, 104 After seven revisions, the SCSI-2 peripheral-interface standard is about to emerge, and products are coming

Hunting for opportunities in the rebuilt space program, 108 NASA is back on its feet, but that doesn't mean the money is flowing freely—most of it is going to entrenched programs

**Zilog hits back in serial communications controllers, 112** The once-dominant supplier hits the market with a new line of general-purpose controller chips

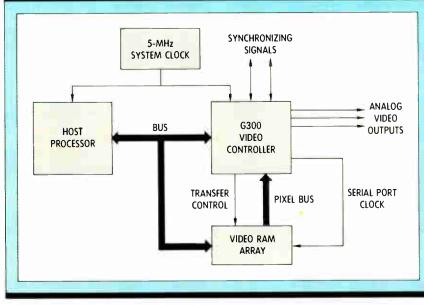

A one-chip solution boosts high-end desktop graphics, 114 Inmos's video controller puts work-station-quality graphics on business users' machines

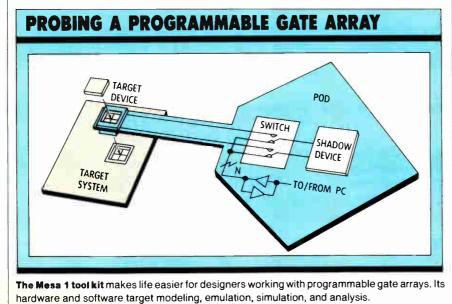

**Finally, programmable arrays make sense, 116** Data I/O's new tool speeds in-circuit verification and debugging

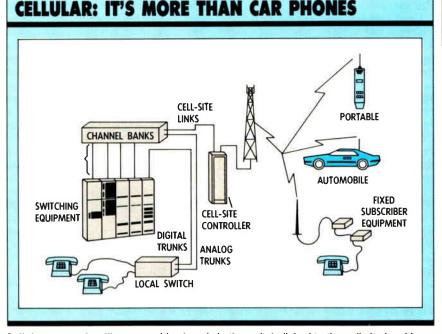

**EXECUTIVE BRIEFING: Cellular phones are going digital, 120** Some systems are hitting capacity; digital technology is the answer

#### **VOLUME 62, NO. 2**

COVER: FRANK AIELLO

#### **PROBING THE NEWS**

#### Government, 29

How will technology fare under the Bush administration? Important budget decisions are on the way

#### Takeovers, 31

The GEC-Plessey duel: jousting for companies, with major markets in the balance

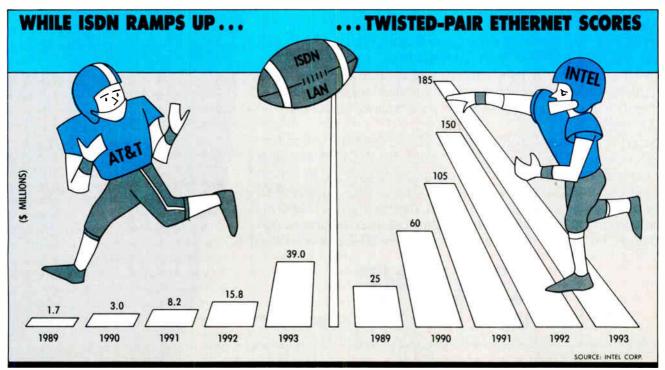

#### **Communications**, 37

Why AT&T and Intel are teaming up on ISDN and twisted-pair Ethernets

#### **Robotics**, 39

It may get easier to program robots off line, thanks to the efforts of the Robotic Industries Association

Work stations, 49 DEC lets the RISC genie out of the bottle—and poses a challenge to Sun Microsystems

Military, 53 Renewing a resource: old parts spring anew

**Instruments, 56** The fastest microprocessors won't faze this emulator

#### Interactive video, 57

Digital Video Interactive may be programmers' next gold mine, if they can learn some new tricks

**Consumer, 60** The gray market is open for digital-audio-tape machines

#### COMPANIES

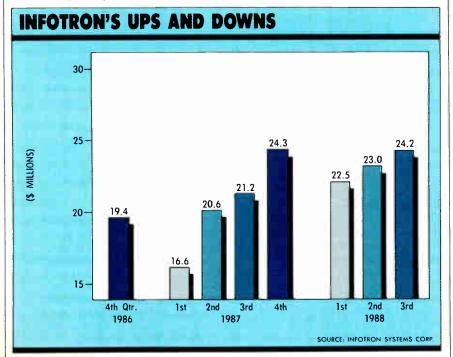

**Infotron Systems Corp., 128** The telecom vendor is going for the gold overseas

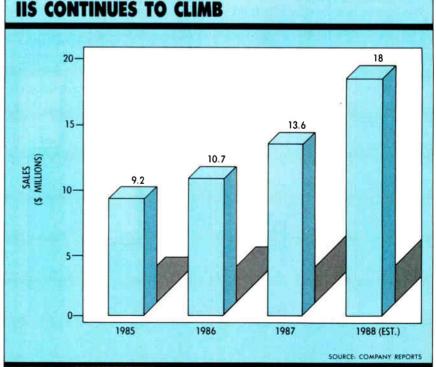

**IIS Inc., 129** Israeli firm beats the big boys with R&D

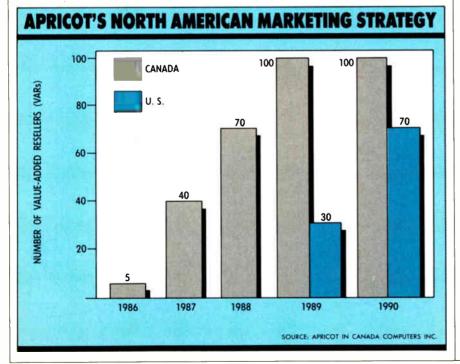

**Apricot Computers, 130** This microsystem maker likes anonymity

Multiflow Computer Inc., 131 Shed no tears for Multiflow

#### PEOPLE

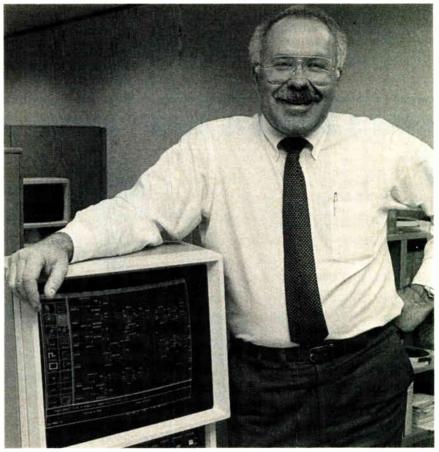

James D. Bowen, 132 Is Rockwell's Bowen the new look in IC executives? A chipequipment expert takes on the Semiconductor Products Division

David A. Hytha, 133 AT&T's Hytha is ready to sell chips in Japan

Robert Johnson, 133 A commodities man turns to ASICs

#### DEPARTMENTS

**Up Front, 3** Hardware people are going to do something that looks suspiciously like programming—whether they like it or not

**Letter from Arizona, 8** They're doing some serious soul-searching in the Cactus State

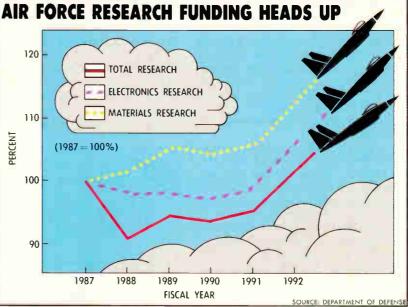

**Indicators, 124** Where Air Force research funds are going

**Book Review, 125** How secure is Unix? You'd be surprised

#### Management Edge, 126

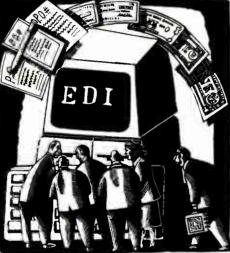

High-tech companies finally go high tech

Interested in modern manufacturing? See it in action

#### **Readers Report**, 135

**Update, 140** Ailiant FX minisupers are winners—and the company surely can use them

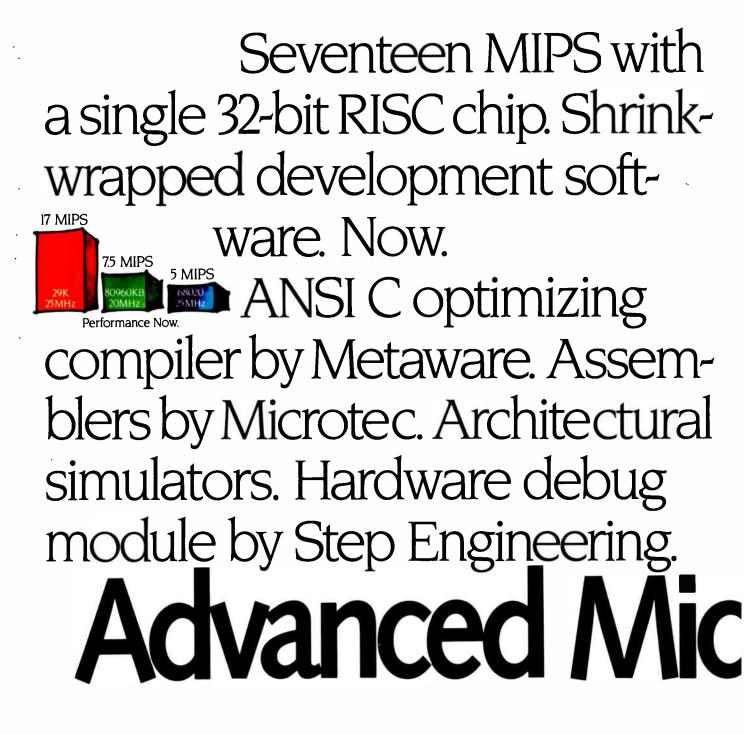

Call toll free (800) 222-9323. Advanced Micro Devices, Inc., 901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088.

Circle 5

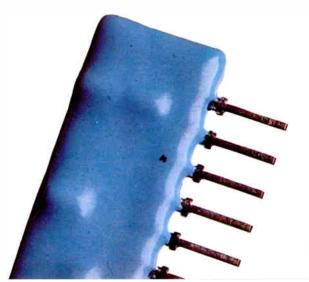

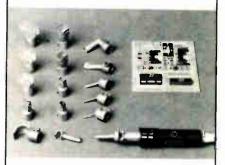

### PICO ULTRA-MINIATURE DC-DC Converters

Low Profile .5"×.5"×.3" ht.

Actual

Size

DELIVERY-STOCK TO ONE WEEK

PICO's high reliability DC-DC Converters are produced in an ultra-miniature encapsulated package  $(.5'' \times .5'' \times .3''$  ht.). Over 80 different models operating over the temperature range of  $-25^{\circ}$ C to  $+70^{\circ}$ C ambient without derating.

- 16 new high voltage models 100-250 volt output

- Up to 1.25 watt output at -25°C to +70°C ambient

- Ultra-miniature size (0.3" Height)

- 5 input voltage ranges 5, 12, 24, 28 and 48V DC

- 28V Input/Output now standard

Input/output isolation

- 100 megohm @ 500V DC

- Single and dual output

- No heat sink required

#### OPTIONS AWAILABLE

- Expanded operating temp

- (-55°C to +85°C ambient)

- Stabilization Bake (125°C ambient)

- Temperature Cycle (-55°C to +125°C)

- Hi Temp, full power burn in (100% power, 125°C case temp)

Over 500 miniature *low profile* standard models deliver *up to 20 watts power.*

### A DAD VEAD MAUEC

### A BAD YEAR MAKES ARIZONA SEARCH ITS HIGH-TECH SOUL

#### PHOENIX

A fter four decades of steady growth, Arizona's electronics industry hit some snags last year. Now executives and government officials around the state are wondering if the setbacks were precursors of tough times to come in the years ahead.

The first of two major disappointments

came early in 1988 when Sematech, the in-

dustry's manufacturing research consor-

tium, chose Texas over Arizona (and the

other contenders) as the site for its head-

quarters and research facility. Then, in

November, the federal government decid-

ed not to base its superconducting-super-

collider project, a mammoth program

slated to last for the next decade, in the

by overly optimistic expectations. Many

of the state's industry figures and politi-

cians believed they would land one or

both projects. Some of them still cling to

the notion that Texas won out through

Besides losing the plums they hoped to

get, Arizona's electronics executives also

lost some things they already had. The

semiconductor market slumped and de-

fense-related orders dropped in the sec-

ond half of 1988. And in a crowning blow,

IBM Corp. announced that during 1989 it

would take some 2,800 jobs away from its

mainframe plant in Tucson and consoli-

**STILL STRONG.** But the setbacks of 1988 do not mean the electronics industry in Arizo-

na is on the brink of disaster. Despite them,

it remains very healthy. Statewide statis-

tics are hard to come by, but the Arizona

council of the American Electronics Associ-

ation estimates that revenue from aero-

space and electronics was about \$6 billion

last year, which means they've doubled

since 1982. Total employment in the indus-

date them in a plant in San Jose, Calif.

underhanded politicking.

The Arizonan dismay was exacerbated

state. The winner, again, was Texas.

try reached some 70,000 people, about half of Arizona's manufacturing jobs, with an annual payroll of about \$1.9 billion. Electronics has now, for the first time, leapfrogged tourism and construction in annual revenue.

Such growth is what Arizona has come to expect ever since World War II. The first high-tech companies started moving in then, lured by the climate and the state's ferociously pro-business environment. General Electric, Hughes Aircraft, Motorola, and Sperry were among the first; since then, they've been joined by other giants like Honeywell, IBM, and Intel, plus a host of smaller companies.

The climate and the pro-business attitude remain potent lures. Added to them is a favorable economy, one that benefits both employers and employees. The cost of doing business is some 20% cheaper than it is in Southern California, according to an Arizona Department of Commerce study. Similarly, a house in Arizona costs less than half the price of a comparable house on the West Coast.

The year-round sunshine, healthy economy, and laid-back lifestyle have attracted a competent and stable labor force. Few people who put down roots ever leave, says Richard G. Loeb, chairman of Optifab Inc. in Phoenix. He tells the occasional defecting employee, "you'll be back." The same holds true for companies: those that have established themselves seldom leave. Generally, they expand. Motorola, for example, is putting its world-class MOS 6 dynamic-randomaccess-memory facility in Mesa, an investment representing upwards of \$100 million. And Intel continually stepped up activities at its Chandler complex during the recent chip boom.

But the events of last year made industry executives aware that they couldn't rely on the natural advantages of Arizo-

#### **IT'S CHEAPER IN ARIZONA**

|                   | SOUTHERN                      | ARIZONA                      |                      |

|-------------------|-------------------------------|------------------------------|----------------------|

|                   | L.A./Long Beach<br>Metro Area | Santa Ano/<br>Newport/Irvine | Estrella/<br>Phoenix |

| Total labor costs | 10.7                          | 10.1                         | 9.2                  |

| Electric power    | 0.4                           | 0.4                          | 0.3                  |

| Occuponcy         | 2.0                           | 1.9                          | 1.2                  |

| Totol*            | 13.1                          | 12.4                         | 10.7                 |

SOURCE: ARIZONA DEPARTMENT OF COMMERCE

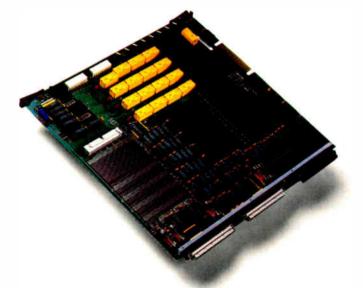

# When it comes to high performance data acquisition for the PS/2, were the only act in town.

A bold claim that happens to be true. It's our all new DT2901 Analog and Digital I/O Board for the IBM PS/2. We say "all new" because we developed our board from scratch, unlike other developers who have been content to simply modify their "old designs."

So, how does that make our I/O board better?

We built our board around two custom-designed chips. Our data transfer chip permits A/D, D/A and Digital I/O operations to occur simultaneously and without data gaps. Our custom MCA Interface Chip does the work of several conventional chips, permitting high performance operation while saving valuable space and power.

Add to this its *fast* 50kHz throughput, flexible channel and gain selection, and you've got yourself performance like no other data acquisition board on the market today.

You can get all of this, including our FREE ACQUIRE software, for under \$1,000! Think about it, and we think you'll agree ... our *all new* high performance I/O board isn't just the only act in town, it's also the best.

So act now. Call (508) 481-3700 In Canada, call (800) 268-0425.

FREE 1988/89 Data Acquisition Handbook.

| Model  | Analog<br>In | Resolution | Programmable<br>Gains             | Throughput      | Analog<br>Out | Resolution | Throughput  | DIO      | Pacer<br>Clock | Price  |

|--------|--------------|------------|-----------------------------------|-----------------|---------------|------------|-------------|----------|----------------|--------|

| DT2901 | 16SE/8DI     | 12 bits    | 1,2,4,8,16                        | 50kHz           | 2 chans.      | 12 bits    | 50kHz/chan. | 16 lines | 2              | \$995  |

| DT2905 | 16SE/8DI     | 12 bits    | 1,2,10,20<br>100,200,<br>500,1000 | 50kHz<br>2.6kHz | 2 chans.      | 12 bits    | 50kHz/chan. | 16 lines | 2              | \$1095 |

DATA TRANSLATION

World Headquarters: Data Translation, Inc., 100 Locke Drive, Marlboro, MA 01752-1192 USA, (508) 481-3700 Tlx 951646 United Kingdom Headquarters: Data Translation, Inc., 1100 Locke Drive, Marlboro, MA 01752-1192 USA, (508) 481-3700 Tlx 951646 West Germany Headquarters: Data Translation Chtt, The Mulberry Business Park, Wokingham, Berishire RG11 2(1), U.K. (0734) 793838 Tlx 94011914 West Germany OFI42-54025 International Sales Offices: Australia (2) 662-4255; Belgium (2) 735-2135; Canada (800) 268-0427; Chile (2) 25-3689; China (408) 727-8222, (1) 868-721; Denmark (2) 274511; Finland (90) 372-144; France (1) 69077802; Greece (1) 951-4944, (31) 527-039, (1) 361-4300; Hong Kong (5) 448953; India (22) 23-1400; Israel (3) 5401524; Italy (2) 824701; Japan (3) 348-8301, (3) 522-5550, (3) 355-1111; Korea (82) 756-9954; Morocco (9) 30-4181; Netterlands (70) 99-6360; New Zealand (9) 5004759; Norway (2) 5312 50; Peru (14) 31 8060; Philopenes 818-0103; Portugal 545313; Singapore 7797621; South-Africa (12) 8037680/93; Spain (1) 455-8112; Sweden (8) 761-7820; Switzerland (1) 723-1410; Tawan (2) 918-4740; United Kingdom (0734) 793838; West Germany 07142-54025. Data Translation is a registered trademark of Data Translation, Inc. All other trademarks and registered trademarks are the property of the respective holders.

# NINE MONTHS FROM CONCEPT TO FINISHED PRODUCT.

Matty Goldman Baby Girl 8 Lbs., 2 oz. Natural Childbirth 2 Sisters

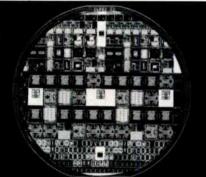

Schlumberger needed a big chip. They needed it in a big hurry. And they needed it to work the first time.

Thanks to VLSI's Datapath Compiler and Logic Synthesizer, they got what they needed.

Our ASIC tools let them design at a high level. And in just four short months, Schlumberger had a data processor for a mil std 2179 recorder that packs 385,000 transistors in 460 square millimeters.

That's one big baby.

#### OUR LIBRARIES EASE THE GENERATION GAP.

Once you design a chip with VLSI, our Portable Library<sup>™</sup> icons let you slide right into your next generation chips.

You can add new features, or try our new 1-micron CMOS technology for high-speed, high-density designs.

You can choose cell-based or gate array chips. You can take advantage of the custom foundry services at our new Class 1

# FOUR MONTHS FROM CONCEPT TO FINISHED PRODUCT.

Circle 11 World Radio History

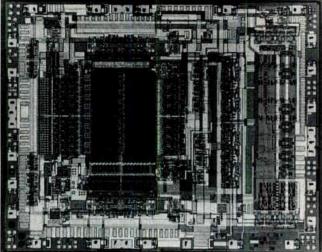

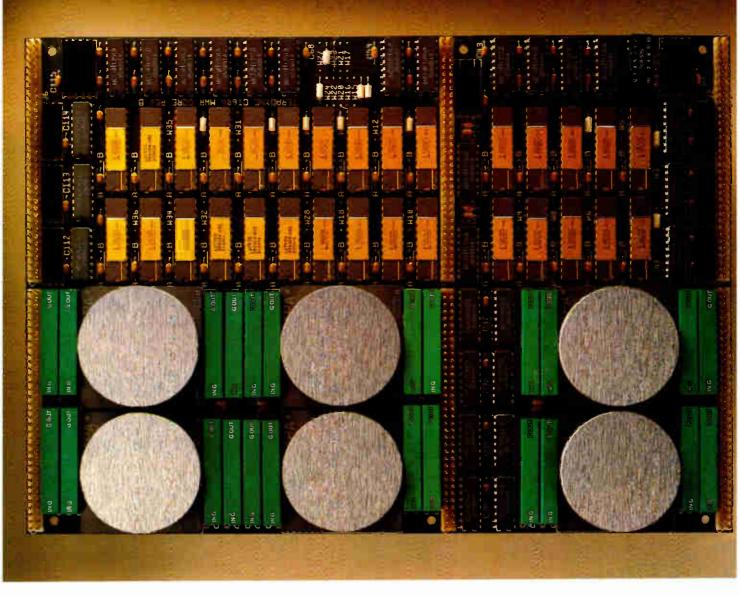

Schlumberger Data Processor for Mil Std 2179 Recorder 68-pin Ceramic Pin Grid Array Cell-Based, 1.5-Micron CMOS 385,000 Transistors

wafer fab in San Antonio, Texas.

You can even switch to Gallium Arsenide or rad-hard CMOS and keep most of your original design work.

#### WE WEREN'T BORN YESTERDAY

VLSI Technology has produced more high-integration cell-based CMOS ASIC designs than anyone else. We're not strangers to gate arrays, either.

We can help you through every step of

your design at one of our many ASIC Technology Centers around the world. Call 1-800-872-6753. Or write us at 1109 McKay Dr., MS32, San Jose, CA 95131. We will help you design the ASIC you want faster than you ever thought possible. More importantly, we'll do it faster than your competition ever thought possible. And isn't that an interesting concept?

PICO transformers ... small size ...big specs

- size variations of .25" dia. x .25" to .75" dia. x 82" ht.

- MIL-T-27E (PICO is QPL source)

- 20Hz —250KHz

- pulse applications .05μs to 100μs prim. and sec. impedances

- 2 ohms to 250K ohms

- power to 3 watts

- inductors to 80 henries

- plug-in construction, surface mount, or flying leads

- extreme resistance to thermal shock MIL-STD-202F, method 107(25 cycles). Special designs for 300 cycles.

standard DC-DC Converiers and over 2500 Miniature Transformers and inductors.

na to guarantee continued growth. In fact, a number of them had already come to that conclusion; 1988 simply added a sense of urgency to plans they were starting to make.

These executives belong to a loosely organized network revolving around the state AEA council. They have set themselves an ambitious task: to define their goals for growth and how they can best reach them. The group began its work when the members started to realize that some kind of statewide planning couldn't be put off any longer. "We're at a decision point-how we mature," says Terry Bibbens, chairman of the council and a senior vice president at Loral Corp.'s Defense Systems in Litchfield Park.

The first concrete action focuses on the state legislature—the group is trying to get it to set up a high-tech committee that can help guide state policy. "We recognize that companies will come and we'll get growth, no matter what," says Optifab's Loeb. "The trick is to manage it

Can the state shake its

cooperative planning?

rather than react to it."

Part of the problem is that years of easy growth have made the frontier mentality to start state's leaders complacent, a growing number of executives think. Experience in states like

Texas and Massachusetts shows that landing Sematech-type projects demands a well-organized, well-financed effort that draws on the resources of the entire state. By all accounts, nothing of this sort has ever happened in Arizona. Unlike a number of other states, Arizona has no high-tech advisory groups.

The setbacks therefore also jolted at least one state agency, Arizona's Department of Commerce, whose charter includes luring new industries. The department just didn't have a mechanism in place for coordinating the state's major players, says its director, David P. Jankofsky. That's always been a weakness, he says, and last year it proved disastrous. But it did teach a school-of-hardknocks type of lesson, says Jankofsky, namely, the need for local economic development groups (notably in Phoenix and Tucson), state authorities, and companies "to speak with one voice." Now Jankofsky's chief goal is to put together a mechanism, backed by the state, for this purpose. While the task amounts to "a delicate balancing act," due to egos and divergent interests, he expects to have something organized by spring.

Meanwhile, the AEA activists are wary. Even though they're pitching in, in the knowledge that the state has to lend a hand, past disappointments have made them skeptical of promises such as Jankofsky's. One reason is that historically, knowledgeable industry types have seldom been consulted by the state. So if a

state development plan is unveiled soon, as promised, its fate will be determined by who's behind it. "Watch for the names," says one executive. "If it's the same old vested interests in banks and real estate, then it won't work."

In short, Arizona does not have an effective "old-boy network," that confederation of bankers, industry heavyweights. real estate interests, and old money that makes things happen. Rather, it runs on a frontier mentality, says R. Dale Lillard, the president of Lansdale Semiconductor Inc. in Tempe. "This remains a very conservative state.'

**NO WONDER.** Given the prevalent attitudes, says one observer, it's no wonder Arizona lost Sematech and the collider project. "It is painfully obvious that Arizona is not yet in a position to attract these world-class projects," says Walter J. Schuch, editor of the Southwest Technology Report, a widely read newsletter. Texas, by contrast, "has statewide depth in technical and scientific competence; it

has a stable, broadbased, high-tech industry; and it has strong local financial resources. Arizona does not.'

Finances are a particular sore point for hightech businesses, espe-

cially the startups and small companies in need of local financing. The problem lies with Arizona's bankers. They are for the most part a play-it-safe breed, who neither understand high-tech businesses nor appreciate their importance to the state. They prefer real estate loans, industry veterans sav.

"If you don't go in there pushing a wheelbarrow, you come right back out, says David R. Buchanan, a veteran startup and venture-capital executive who is president of Three-Five Systems Inc. in Phoenix.

The bankers' tunnel vision exemplifies a more general lack of appreciation for technology, says Schuch: "People don't know the difference between a semi truck and a semiconductor." He proposes putting more emphasis on helping existing companies grow and on developing a "high-tech master plan that includes specific goals and objectives, that involves all facets of the community.

Which is more or less what the state's electronics executives are thinking these days. Arizona has seen its technology growth pause and then take off again without intervention, but few of them believe they can make further headway without planning and support at the top levels of state government.

The AEA group is trying to get that. Bibbens and his colleagues realize they are charting new territory. "But if we don't develop the right goals," he says, "others will [step in].' -Larry Waller

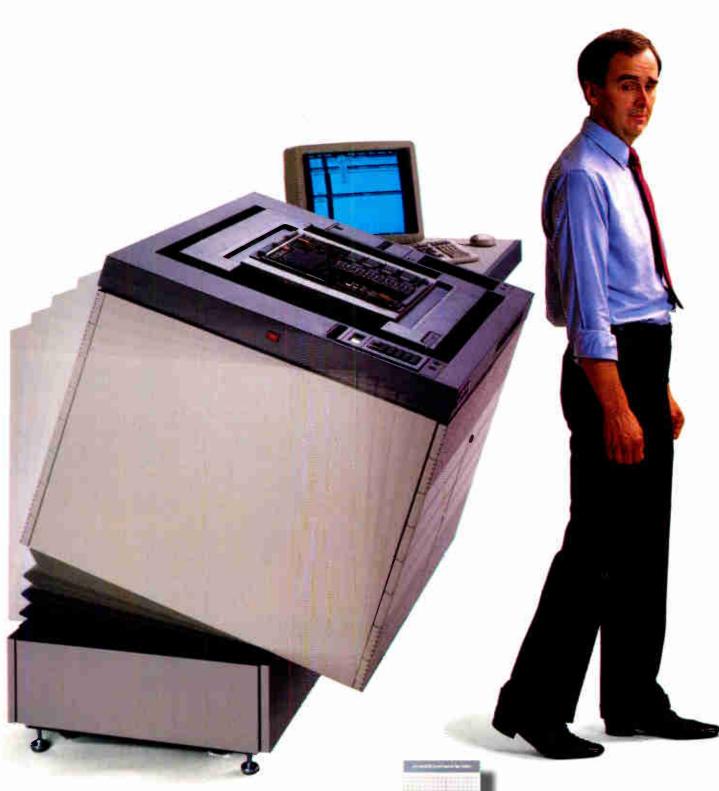

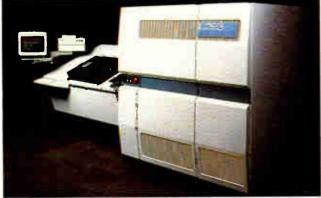

# Great things happen when you come to GenRad for board testers... you get choices!

You shouldn't have to compromise your budget or test criteria to fit an ATE manufacturer's product offerings.

At GenRad you get a family of testers to choose from in price/performance ranges that give you freedom of choice. A choice of the industry's marketleading board test systems with the superior software that has kept GenRad the leader for 20 years. Software that features industry-standard Automatic Test Generation for fast in-circuit program preparation. And speed and accuracy in program preparation translate into dramatic savings in this most costly aspect of ATE. GenRad testers will handle your newer, more complex boards with ease, whether your choice is an in-circuit or combinational strategy. For even greater freedom of choice, GenRad's Environment for Strategy Independent Software, GENESIS,<sup>™</sup> lets you go beyond ordinary combinational testing. This means you can select the strategies best suited to your application. You are no longer restricted by a pre-determined tester strategy.

For more about the board test choices we offer, call 1-800-4-GENRAD.

The difference in software is the difference in test<sup>™</sup> Circle 13

# Introducing two ways VME single bc

### CPU-37. The workhorse of VME.

Now you can harness all the power of VME and the 68030 with our new, low-cost single board computer.

The new VME/PLUS<sup>™</sup> CPU-37 comes with either a 16.7 or 25 MHz 68030, SCSI and floppy disk controllers, VMEPROM and 1 MB of memory. Options include an Ethernet controller and up to 4 MB of memory. With the CPU-37, you now have the power of four boards in one.

Thus reducing your system cost, weight and space requirements.

In addition, software products such as UNIX, PDOS, MVXWorks, OS-9, pSOS, VRTX32 and C EXECUTIVE will be available. Plus our development package will let you start writing your applications quickly-under UNIX, PDOS or MS-DOS.

So if you need lots of horsepower without the thoroughbred price, hitch up with CPU-37.

Running Start<sup>™</sup>

C 1988 Force Computers, Inc. VME/PLUS and Running Start are trademarks of FORCE COMPUTERS INC. UNIX is a trademark of AT&T PDOS is a trademark of Fyring Research Institute. Inc. VXWorks is a trademark of Wind River Systems. Inc. OS 9 is a trademark of

# to get horsepower in ard computers.

### CPU-30. The pacesetter of VME.

Our new CPU-30 shares all the hardworking virtues of the CPU-37, plus it's faster on its feet.

In fact, it offers the highest level of performance and functionality in a 68030 single board computer. And just like CPU-37, our single slot CPU-30 has multiple configurations that meet your exact needs. The real reason the CPU-30 is such a winner is our 280-pin gate array

with 22,000 gates. It handles interprocessor communication and high speed data transfers much more efficiently. The result is significantly increased system throughput in multiprocessing applications like factory automation, simulation,

test and instrumentation.

It all adds up to the highest VME system performance you can get. So if that's what you want, why horse around? Call us at (800) BEST-VME for CPU-37 and CPU-30 Data Sheets and our 1988 Data Book. Count on Force for your total VME solution.

VME at its best.

FORCE COMPUTERS INC. 5165 Winchester Blvd. Campbell, CA 95008-6557 Telephone (408) 370-6300 Telefax (408) 374-1146 FORCE COMPUTERS GmbH Daimlerstrasse 9 D-8012 Ottobrunn Teleton (089) 600 910 Telex 524190 forc-d Telefax (089) 609 7793

Microwave Systems Corporation pSOS is a Prademark of Software Components Group. Inc. VRTX32 is a trademark of Ready Systems. Inc. C EXECUTIVE is a trademark of IMI Software Consultants. Inc. MS DOS is a registered trademark of Microsoft Corporation

Circle 15 World Radio History

#### THE VG-1281 GRAPHICS PROCESSOR

- 1280 × 1024 display resolution

- Fastest TMS34010-based design 12.5 million pixels/sec. PIXBLT 125,000 vectors/sec. 30,000 characters/sec.

#### 256 colors from 16.7 million

- 2K × 1K or 2K × 2K read/write area

- 1 megabyte display list RAM

- Supports X/Y devices, keyboards

- Real-time zoom/smooth pan

Super officient prophics

- Super-efficient graphics library

- Flexible, expandable instruction set

- Hardware graphics cursor

Contractory of

## Fast-track graphics for the VMEbus.

Build high-resolution graphics with flat-out speed into your process control, simulation, instrumentation or training systems using the Matrox VG-1281 display processor. Designed specifically for high-performance workstations and backed by Matrox's outstanding reputation, it has all the power and flexibility you need for the most demanding applications.

The VG-1281. It takes the checkered flag.

In Canada, call (514) 685-2630. Matrox is a registered trademark of Matrox Electronic Systems Ltd.

ELEC-VG / 289

## THE LEADER IN VIDEO MICROTECHNOLOGY

**FEBRUARY 1989**

## ELECTRONICS NEWSLETTER

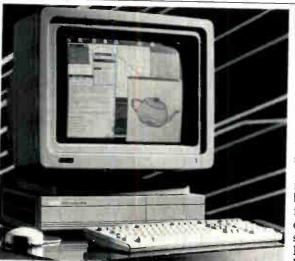

#### **GRAPHICS SYSTEM FOR APOLLO'S DESKTOP SUPERCOMPUTER FINALLY DEBUTS**

Apollo Computer Inc. finally has some good news. After two profitless quarters, the Chelmsford, Mass., work-station pioneer finally introduced its graphics subsystem for the Apollo Series 10000 desktop supercomputer—several months late. Apollo expects the Series 10000, which uses reduced-instruction-set computing, to lead the company back into the black. A server version of the 10000 [*Electronics*, March 3, 1988, p. 69] began shipping last fall. The enhanced version is designated Series 10000VS to denote the visualization system. Tight coupling of its drawing engine to as many as four central-processing units over a 64-bit-wide, 150-Mbyte/s bus enables simultaneous intensive number crunching and 3-d graphics rendering. Delays in laying out the 22,000-gate CMOS arrays used in the RISC drawing engine caused a slippage of about four months in the subsystem's introduction. □

#### HERE'S A PEEK AT MOTOROLA'S MICROCONTROLLER PLANS

ew details of what Motorola Inc. is planning for its microcontroller family are leaking out. The broad outlines of the company's next-generation microcontroller-the MC68HC32-were sketched last month at a special session for university teachers and researchers in Tempe, Ariz. Scheduled for introduction later this year, if is a radical departure from the original concept, a 16-bit or mixed 8- and 16-bit design that was compatible with the existing 8bit MC68HC11 family. Instead, Motorola is going for a design that combines an internal 32-bit central-processing unit with an external 16-bit data and address bus. Code-compatible with the 68000, its instruction set also includes selected commands from the MC68010 and the MC68020. The new controller will be fabricated with a 1.0-µm CMOS process. In addition to 1.5 Kbytes of on-chip standby static random-access memory, it sports 12 independently programmable chip selects, a bus response-time monitor, a double bus-fault monitor, and a software watchdog system. Other features include a spurious interrupt monitor, a periodic interrupt monitor, and a programmable on-board phase-locked loop for system clocking.

#### OSF DELIVERS A USER-INTERFACE TECHNOLOGY-AND IT'S ON TIME

he Open Software Foundation has pulled off its first success—and in doing so has gained some welcome early credibility. The foundation, which was so has gained some welcome early credibility. The foundation, which was set up by a number of computer vendors early last year to develop alternative open-system software standards based on AT&T Co.'s Unix operating system, has announced its selection of a user-interface technology combining elements contributed by Digital Equipment, Hewlett-Packard, and Microsoft. Almost as important as the announcement itself is that OSF did what it said it would do when it said it would do it-in the face of industry skepticism about the ability of its open selection process to produce technical developments at all, let alone in the time set by the organization. The process involved detailed evaluation of 23 of the 39 responses to its July request for technology. The user interface, called OSF/Motif, consists of DEC's Application Program Interface and the HP/Microsoft Window Manager, providing a look compatible with Microsoft's Presentation Manager (the user interface for OS/2) combined with a 3-d appearance from HP, and icon grouping from DECWindows. The industry consensus is that the OSF staff has probably zeroed in on the best possible combination-one that could garner industry-wide acceptance and eclipse the OpenLook user interface being offered by AT&T. OSF/Motif will be available for several operating-system environments, including the forthcoming OSF/1 and Unix System V.4. The next milestone awaited by the industry is the development and release of the OSF/1 operating system itself, which is expected in the second half of the year.

**FEBRUARY 1989**

## **ELECTRONICS NEWSLETTER**

#### HEWLETT-PACKARD SETS A NEW PRICE/PERFORMANCE STANDARD FOR BOARD TESTERS

ewlett-Packard Co. is breaking the \$1 million barrier for automatic testers that can handle dense boards with lots of application-specific integrated circuits and surface-mounted devices mounted on both sides. The Palo Alto, Calif., company has come up with a combination in-circuit and functional tester that sets a new low in price and a new high in performance for combinational testers. Designated either the HP3070AT or HP3070SMT, it costs \$301,000 to \$778,000. It allows unattended automatic testing, tests two-sided boards, and increases the probe-placement accuracy by a factor of 10. Also, the design decreases the error rate to 48 parts per million—currently available models achieve only 465 ppm. While other testers add lots of random-access memory to hold all the patterns needed to perform a test, HP's comes with powerful pattern-generation capability.

#### STARTUP DEVISES MICROPROCESSOR FOR FUZZY LOGIC

An Irvine, Calif., startup is almost ready to unveil a standard microprocessor dedicated to so-called fuzzy logic, which may be the key to computers that "think" more like humans than machines. If Togai InfraLogic Inc. succeeds, the device could be just the ticket to bring this infant technology into the reach of commercial users. The firm's FC110 Digital Fuzzy Processor provides on-chip algorithms that work in concert with a separate 128-Kbyte electrically programmable read-only memory containing the knowledge base necessary for a specific task. Together they offer the simplest approach yet to getting the benefits of fuzzy logic, which is being billed as the best way to implement both artificial-intelligence packages and neural-network technology. The Togai development is one of several fuzzy-logic efforts now under way, including one in Japan (see p. 69).

#### **CERAMIC PIN-GRID-ARRAY PACKAGES RACK UP HUGE SALES**

he beat goes on for ceramic pin-grid arrays in the packaging business, with the technology dwarfing other segments of the materials industry. Sales of the packages zoomed to \$1.7 billion in 1988, based on some 173 million units, says consultant Daniel J. Rose, an authority on materials. That tops silicon's \$1.5 billion intake (as a raw material), he says. Because of their high gold content, and the upward spiral of nickel and copper prices, the packages are expensive—about \$10 each. But their popularity is fed by the increase in high-pin-count chips, such as top-of-the-line microprocessors and gate arrays, for which they are uniquely suitable, says Rose, who was a speaker at last month's annual seminar of the Semiconductor Equipment and Materials International trade group at Newport Beach, Calif.

#### **RESEARCHERS USE MICROSCOPIC WIRES TO CREATE A QUANTUM DEVICE**

Many experts believe the answer to getting the fast, dense superchips of the next decade lies in structures taking advantage of quantum effects [*Electronics*, October 1988, p. 143]. So researchers at the University of California at Santa Barbara have created what they call a quantum-wire superlattice, which in the active region of a device employs millions of parallel 50-by-50-A wires fabricated of gallium arsenide. Building the superlattice wire structure, which the developers say is the first of its type, will enable them to determine whether wires are more efficient in moving electrons because they offer less resistance than solid material, as theory predicts. Other quantum approaches, such as the one reported by Texas Instruments Inc. of Dallas, use thin layers of material in a well structure to get the wavelike quantum effect of electrons moving through the transistor wall.

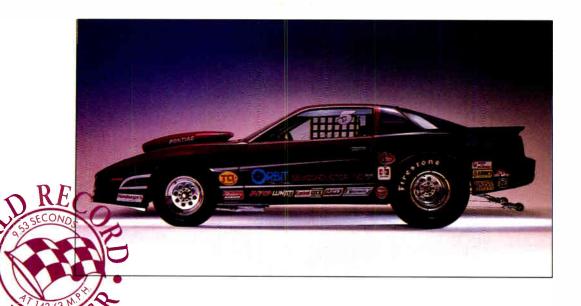

# Record Time.

#### Orbit Captures World Record.

Quality equipment. Commitment and teamwork. Extraordinary skill. These are the ingredients for record performance. Like the world record the Orbit Semiconductor-sponsored Trans Am captured on the drag strip.

And like the delivery schedules we guarantee our customers on a daily basis.

#### A Winner on the Toughest Tracks.

Orbit Semiconductor routinely meets the toughest challenges:

- quick-turn engineering prototype runs

- hi-rel volume runs

- specialized MOS processes such as CCD, Readout, Detector, or MUX with feature sizes down to 1.5 microns

- process emulation and custom process development

On-site CAD, quick-turn maskmaking, test facilities, and packaging help speed your products to timely delivery. And our quality procedures monitor every step of the fabrication process.

#### To Set Records Get the Record Setter.

Whether you're racing towards an early market entry, or maximizing engineering time; Orbit Semiconductor is ready to provide the fastest, most comprehensive semiconductor manufacturing services available. Get on the right track. Contact Technical Marketing today. Orbit Semiconductor. 1230 Bordeaux Drive. Sunnyvale, CA 94089. TWX: 910-339-9307, FAX (408) 747)1263. Or call (800) 331-4617, in California (800) 647-0222, (408) 744-1800.

What others promise, we guarantee.

REGIONAL REPRESENTATIVES: East Coast (609)428-6060, - Midwest [801] 261-0802 (612)854-7550, (303)530-4520 - West Coast (408)241-8111, (714)253-4626, (602)996-0635, (602)293-1220, (505)888-0800.

INTERNATIONAL REPRESENTATIVES: Canada (514)431-3313 - U.K. Phone (0372) 376953, Thx 897628 S.G. U.K.-G, Fax (0372) 376848 - Europe Phone (D6031) 61076, Thx 6031 948, FAX (D6031) 61788 - Iarael Phone (052) 551313, Thx 342541 CANER IL, Fax (052) 543890 - Australia Phone (8) 223 5802, Thx UNIVAD AA89141, Fax (8) 224 0464.

# A GENTLE REMINDER ON THE IMPORTANCE OF LOOKING AROUND.

ombinational Testers. Technically speaking, it's no longer a question of if or when you'll need one. But which system to choose.

Loyalty may take you first to the manufacturer of your present board testers. Logic should take you further.

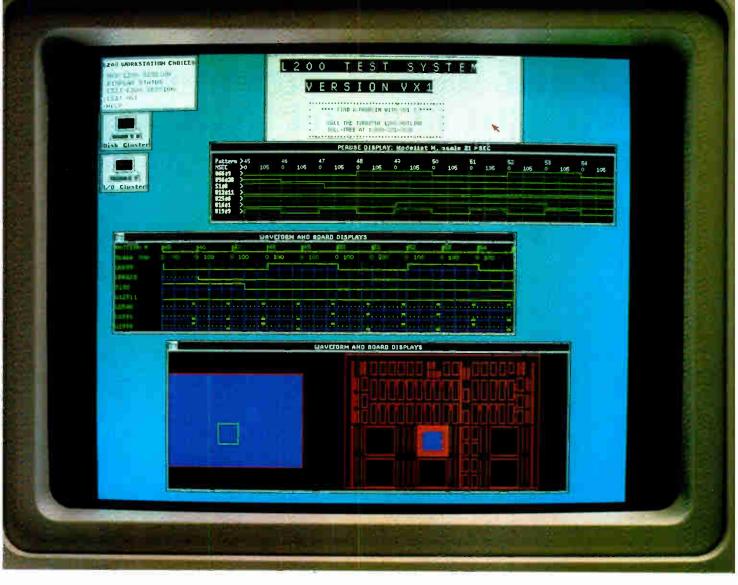

Because the Zehntel 8000 holds a number of pleasant surprises for you —in power, flexibility, and price. BY ALL MEANS, COMPARE. To appreciate its performance fully, it's only fair to judge the 8000 by comparable systems: those costing much more.

The 8000's open architecture, for example, can greatly reduce overall testing costs. Using the Functional Interface Board pictured above, you can place your own hot-bed test directly into the 8000 system. The 8000 is the only combina-

tional tester with 2,048 fully-hybrid,

non-multiplexed test points. Each node has a driver/receiver behind it; each can be used for either functional or in-circuit testing. All of which helps reduce the

cost of programming and implementing engineering changes.

The 8000's digital test subsystem truly warrants the term "high performance," with 10 MHz pattern rate, 8Kx4 RAM per node, programmable slew rates and 10ns programmable edge placement.

The menu-based, mouse-driven interface simplifies programming, with multiple windowing capability, integrated logic analyzer and graphic quality analysis tools.

> A GENTLE REMINDER Where to Look.

For complete information on the Zehntel 8000, call or write today. To help, we'll send you a specially-created reminder pad for your desk, inspired by the 8000's elegant industrial design.

Offer expires

July 31, 1989

#### Free Reminder Pad

For your free notepad, call (800) 457-8326 or attach your business card here and send to:

ELEC/2-89

2625 Shadelands Drive Walnut Creek, CA 94598

# than dots-per-inch.

from the protocol is blobing a 300dpl color printer. Even us. But once you look past the spec almed you see which reprinters Solito from the thundering herd.

It is difference to registration. That is, putting dots precisely where they're supposed to be. Cately point, the new Midul CH-500 Series. They're built with our exclusive Plastiframe" chustis and integrated Direct Drive Madia Transport System." And they provide the most chustis and integrated Direct Drive Madia Transport System." And they provide the most chustis and integrated Direct Drive Madia Transport System." And they provide the most chustis and integrated Direct Drive Madia Transport System." And they provide the most chustis and integrated Direct Drive Madia Transport System." And they provide the most chustis for the second Direct Drive Madia Transport System." And they provide the most chustis and integrated Direct Drive Madia Transport System." And they provide the most chustis and integrated Direct Drive Madia Transport System." And they provide the most chustis and integrated Direct Drive Madia Transport System." And they provide the most chustis and integrated Direct Direct Drive Madia Transport System." And they provide the most chustis and integrated Direct Drive Madia Direct System." And they provide the most chustis and the provide the most of the second Direct Direct System." And they provide the most chustis and the second Direct Direct System in a color printer.

So what's really important to you? If it's consistent, accurate, realistic output, look at the Seiko Instruments color printer

For more information, call Martin Nelson at (408) 943-9090. Orcle 22

#### Seiko Instruments

The second s

**FEBRUARY 1989**

### **PRODUCTS TO WATCH**

#### HEURIKON'S VME BOARD MOVES BLOCKS TWICE AS FAST AS THE COMPETITION

P integrating National Semiconductor Corp.'s newest graphics chip set into its VMEbus HK85/VRGP board, Heurikon Corp. is doubling the boundarybit-block-transfer (BitBLT) rates of comparably priced VME boards, claims the Madison, Wis., company. Based on National's DP85XX chip set, the HK85/ VRGP includes 1 Mbyte of video random-access memory, 512 Kbytes of program memory, 64 Kbytes of electrically programmable read-only memory, and support for both the X-Windows and Graphical Kernel System standards. It also provides maximum resolution of 1,024-by-1,024 pixels by 8 bit planes. The board's processing power comes from the DP8500 Raster Graphics Processor, a 20-MHz programmable device working with a set of DP8511 BitBLT processors, one per plane, but expands to 24 with a second card. It will be available next month for \$3,220 in 100-unit guantities.

#### DATA COMPRESSION DOUBLES CAPACITY OF QUARTER-INCH TAPE DRIVES

System integrators can double the capacity of ¼-in. tape drives—the current crop of backup tape drives for IBM Corp.'s Personal Computers, Personal System/2, and compatibles—at no additional cost by switching to Colorado Memory Systems Inc.'s QFA-500 drive. The Loveland, Colo., company uses a 2 : 1 data-compression algorithm developed by STAC in Pasadena, Calif., in the drive's control software. Boasting 500 Mbytes of storage and a 5.25-in. form factor, the QFA-500 can achieve data-transfer speeds of up to 2 Mbytes/ min for backing up hard disks in PCs based on Intel Corp.'s 80386 microprocessors. Since the data compression is done in software, data-transfer rates drop with less powerful machines. The drive's bit-error rate is 10<sup>-15</sup>. STAC will offer a single-chip hardware implementation of the algorithm later this year. Prices for the QFA-500 start at \$1,395.

#### DATA GENERAL SHIFTS ITS OSI INTEROPERABILITY IMAGE INTO HIGH GEAR

Continuing its product strategy of gearing up for international communications standards, Data General Corp. has rounded out its software offerings that completely implement the International Standards Organization's sevenlayer Open Systems Interconnection reference model. The Westboro, Mass., computer maker's three newest packages let customers link Data General and non-Data General computers into interoperable networks. One of the latest packages, called DG/FTAM, enables Data General users on an OSI network to perform file transfer and file management with other computers that comply with the OSI specifications for those functions. The DG/OAPI tool kit helps users create OSI applications that can operate on heterogeneous networks. The DG/OTS is a complete OSI communications platform. Available in the fourth quarter, low-end systems begin at \$1,500 for DG/FTAM, \$2,500 for DG/OAPI, and \$900 for DG/OTS.

#### 88000 RISC PROCESSOR IS AVAILABLE, MOTOROLA SAYS

The Microprocessor Products Group of Motorola Inc., Austin, Texas, has begun accepting orders for its widely publicized 88000 reduced-instruction-set microprocessor. More than 50 customers have sampled the two-chip set since early last year. Broader sampling is now under way, with full production scheduled for the second quarter. The 88100 central-processing unit integrates integer and floating-point execution, while the 88200 cachememory-management unit offers a single-chip approach to cache-memory design. The 88000 performance is rated at 14 to 17 VAX-equivalent mips at 20 MHz. Each chip is housed in a 180-pin grid array. Samples of the 88000 cost \$494 and the 88200, \$619.

**FEBRUARY 1989**

### **PRODUCTS TO WATCH**

#### JUPITER ATTACKS THE LAN-SERVER MARKET WITH A USER-CONFIGURABLE SYSTEM

By slimming down its System 1000, Jupiter Technology Inc. of Waltham, Mass., has conjured up a user-programmable data-communication computer to compete in price with single-function devices. The \$8,500 System 100 can be configured to control a remote site in large networks or as a network server and a gateway device between networks. When used as a local-area-network server or a multiaccess-terminal-cluster controller, it competes with nonprogrammable single-function boxes, such as protocol converters, which sell in the \$6,000 range. It interconnects systems using many incompatible communications standards, including Ethernet, TCP/IP, and CCITT's X.25 packet-switching protocol. The System 100 serves from four to 384 communications lines and can accommodate up to eight Motorola 68000based microprocessors.

#### VERDIX MAKES WRITING ADA CODE FOR REAL-TIME CPU BOARDS EASIER

A real-time Ada development system from a duo of small software companies breaks new ground by letting software engineers working at a Unix work station develop Ada code for central-processing-unit boards. The software, VADS/Works, combines Verdix Corp.'s Ada Development System with a real-time operating system from Wind River Systems of Emeryville, Calif. By performing most of the basic conversion work between Unix and Ada, it saves time and money compared with development environments now in use that have to be tacked together in-house, says the Chantilly, Va.-based Verdix. Now available for Motorola 68020 boards from Heurikon Corp. of Madison, Wis., the system is in beta test with boards from Force Computer Corp., Los Gatos, Calif.; Motorola Inc., Phoenix, Ariz.; and others. VADS/Works pricing ranges from \$27,500 to \$100,500, depending on the work station on which it will run. □

#### NEC BOOSTS ITS V70 MICROPROCESSOR'S CLOCK RATE 75%

Scaled-down versions of NEC Corp.'s V70 microprocessor that boost clock speeds by 75% will be available this year, and even faster versions are waiting in the wings. The Tokyo-based company is speeding up its present 20-MHz CMOS chip to 33 MHz by going from 1.2- $\mu$ m design rules to the 0.8- $\mu$ m design rules that NEC developed for its forthcoming 4-Mbit dynamic random-access memories. The new chip features a silicide overlay on the polysilicon gates to maintain low-resistance first-level interconnection despite the fine pattern. Chip size is cut almost in half, raising hopes for both lower pricing and the possibility that it could be used as a core in future application-specific integrated circuits. Samples will be available this autumn, with 40-MHz and higher-speed versions to follow.

#### HERE'S A 32-MEGAFLOPS COMPUTE SERVER FOR MACINTOSH NETWORKS

igh-end processing has arrived for networks of Apple Computer Co.'s Macintosh machines with Chorus, a supercomputer designed by Human Devices Inc. Containing up to 16 high-speed floating-point processors, Chorus connects Macintoshes to form a multiuser desktop-computing environment boasting performance that ranges from 8 to 32 million floating-point operations/s, depending on the number of processors. The compute server opens new vistas for the Macintosh in engineering simulations, financial modeling, and photorealistic graphics, says New York City-based Human Devices. Available now, base configurations go for \$9,700 for a single-processor version to \$25,500 for a four-processor version. Additional four-processor add-on modules cost \$16,800. □

# Total Depend ility

#### THE SOURCE OF PROFESSIONAL ELECTRONICS

**World Radio History**

"The total dependability of aircraft flight systems is something we all accept."

In the design, development and manufacture of electronic and electromechanical components and sub-systems, AB Electronic Products Group PLC also provides total dependability.

Dependability in product performance. Dependability in quality standards. Dependability in customer service.

Today, AB are found in the aerospace, defence, data processing, telecoms, automotive and consumer industries wherever dependability is important.

AB works with its customers at any stage of a project, from initial design and development to procurement of component parts, prototype manufacturing and full scale production. Investment in CADCAMICAE, a Group Technology Centre and extensive surface mounting facilities has taken AB to the forefront of electronic design and product technology.

A manufacturing policy of 'zero defects' is enforced in all AB manufacturing operations. Supported by investment in automatic test and burn-in equipment, this ensures standards essential to the achievement of total dependability.

The AB Group employs over 5,000 people in 22 operating locations worldwide. To find out how your business could benefit from the total dependability of AB Group products and services, contact us today.

AB ELECTRONIC PRODUCTS GROUP PLC ABERCYNON, MOUNTAIN ASH, Mid Glamorgan, CF45 4SF, TEL: 0443 740331 Fax: 0443 741676

Circle 25

# An idea this small

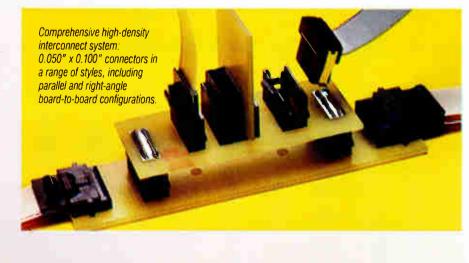

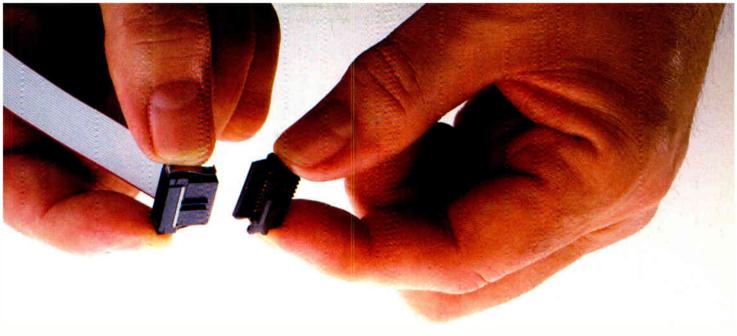

This is the AMPMODU System 50 connector.

Definitely worth getting close enough for a good look.

It comes in a comprehensive system. Everything you need for a 0.050" x 0.100" grid. Board-to-board, stacking, or mother/daughter. FFC to board. 0.050" CL flex etched circuitry to board. 0.025" CL ribbon cable to board. Special design innovations (such as putting the latch hardware on the *cable* side) shrink our System 50 line to the least board space of any connector in this class. Even  $0.050'' \ge 0.050''$  types.

# no small idea.

Example: 2x25 position shrouded headers occupy 1.5" x 0.284" of

board surface. And parallel boards mount with inside faces a mere 0.450" apart.

Along with density, you also get the productivity you expect from AMP: simple mass termination,

robotic handling features, high-temp housings, selective gold plating. And of course, outstanding quality and reliability.

AMPMODU System 50 connectors are available in selected sizes of 4 through 30 single row positions, 8 through 100 in dual

row, with shrouded or unshrouded headers. With all

those variations, you could do almost anything your design requires.

Which is our whole idea.

to ask about our AMPMODU System 50 line. For characterized backplane assemblies, contact AMP Packaging Systems Inc., P.O. Box 9400, Austin, Texas 78766, (512) 244-5100, or your AMP Sales Engineer. AMP Incorporated, Harrisburg, PA 17105-3608.

#### **IP** Interconnecting ideas

Circle 27

# Real-Time Math. PC-Compatibility. Disk Storage.

# No Problem!

The Nicolet 4094C Digital Storage Oscilloscope gives you the maximum versatility and value with software solutions beyond locked-in front panel functions.

#### Real Time Functions

Nicolet Test Instrument Division

Functions such as FFT, MIN/MAX, Summation, Virtual or Exponential Averaging are available with the 4180 and 4570 plug-ins, providing you with live, real time display of your waveform data.

#### PC Software

Nicolet also has four software packages available which allow you to transfer, display and manipulate 4094 data on your PC. There are also over 100 disk-downloadable programs available for the 4094.

#### External Control

With programs like Waveform BASIC, you can even create your own custom programs for data manipulation and external control of the 4094C. IEEE (GPIB) and RS232 interfaces are included for easy communications with a PC.

ucord

NICOLEC

Nicolet

#### Programming Support

Nicolet's application support can make all the difference. Our application engineers are a phone call away and are always ready to help you.

For more information, call or write:

# Nicolet

5225-2 Verona Road, Madison, WI 53711 • 608/273-5008 or 800/356-3090

Circle 28

# Electronics

### HOW WILL TECHNOLOGY FARE UNDER PRESIDENT BUSH?

#### This will be a key year for budget decisions as megaprojects eat up billions

#### WASHINGTON

Now it's all up to George Bush. President Reagan, in the waning days

President Reagan, in the waning days of his administration, submitted a budget to Congress that most experts agree was dead on arrival, a document that at best could serve as a springboard for Bush to establish his own science and technology agenda. How Bush modifies that budget in the coming weeks will tell the story of federal science and technology spending for years to come.

Make no mistake about it—fiscal 1990 will be a key year for science and technology investment. Funds that in the coming year are sunk into expensive projects like the superconducting super collider, the space station, and the National Aerospace Plane will commit the U.S. to spend billions more over the next decade just to complete them. And with such megadollar commitments, funds may be scarce for the less glamorous researchand-development programs that many critics believe could revitalize U.S. technological competitiveness.

LINE FORMS. That worries some in Congress, who point to a spate of industry groups that, emboldened by the apparent success of the Sematech chip-making consortium, are seeking federal support for their own critical research initiatives. High-definition TV, X-ray lithography, and precision optics are just three areas in which various groups and government agencies are now clamoring for dollars.

The optimistic Reagan budget seeks \$315 billion for the military—that's inflation plus 2% real growth over 1989. It includes a \$2 billion increase in spending for the Strategic Defense Initiative and hundreds of millions more for the other budget-eating pet projects.

So now comes the hard part: waiting for the changes. Bush will surely submit a budget revision, although no one knows exactly when it will come or how drastic it will be. Congress will just as surely make changes of its own. The overriding question is, just how different will President Bush be from Vice President Bush—how closely will he hew to the Reagan line?

With the federal government facing a number of crises—the deficit and the high-priced bailout of failing savings and loan institutions, to name just twofunds will be tight for at least the next decade. So no one in Washington thinks Reagan's plan for 2% real growth in defense spending is even plausible. "The \$315 billion in there for defense is hopelessly optimistic," says John Mancini, vice president of domestic affairs at the American Electronics Association. "I don't think anyone thinks they'll do better than keep pace with inflation over the next five years." Even Bush has acknowledged a willingness to keep the Pentagon on a zero-growth budget plan.

In other areas, the questions center less on how much money to spend than on how to spend it. If any of the plans to have federal v assisted research programs akin to Sematech pan out-and if Congressional goals to boost military investment in its technology base are met-cuts, delays, or even cancellations may hit those big-ticket programs: SDI, the super collider, the space station, and the National Aerospace Plane, a joint effort by the Air Force and the National Aeronautics and Space Administration to develop a hypersonic spacecraft that could take off and land like a conventional airplane. That program alone will cost \$426.7 million in 1990, according to the Reagan plan. of which roughly two thirds will be paid for by the military.

Then there's the National Science Foundation, which is on the path to doubling its 1987 budget by 1993, assuming its planned 14% hike for 1990 goes through. Much of that growth is being channeled into a major initiative in education, which NSF director Erich Bloch calls "one of the most persistent and limiting problems this country faces." But in the basic sciences, where NSF's charter lies, more growth is needed, he says: "The average grant today is about \$75,000. We've got to get that up to \$100,000 or \$120,000."

**NOTHING FOR NIST.** In contrast to the sexy megabuck projects, the Reagan budget seeks no funds whatsoever for the new technology-base responsibilities of the National Institute of Standards and Technology, the rechristened National Bureau of Standards. The Omnibus Trade Bill of 1988 renamed the agency and gave it a mandate to fund regional manufacturing-technology centers; advanced R&D in preproduct commercial technology; and small companies seeking to capitalize on inventions. The idea was to help struggling industries compete with foreign competitors, who often are government-subsidized.

Other projects, such as the space station, will have significant long-range costs. NASA, for example, says that it will have to double its 1990 budget—set by Reagan at \$5.75 billion—by the year 2000 just to maintain ongoing programs such as the space shuttle and the space station. An exploratory mission to Mars or other science programs in space would

#### THE PENTAGON'S BIG R&D PROGRAMS

|                                        |       | (\$ Millions)                 |       |  |

|----------------------------------------|-------|-------------------------------|-------|--|

| Project                                | 1988  | 1989                          | 1990  |  |

| Strategic Detense Initiative           | 3,553 | 3,627                         | 5,591 |  |

| Space Station                          | NA    | 900                           | 2,050 |  |

| National Aerospace Plane               | 300   | 426                           | 556   |  |

| Superconducting Super Collider         | NA    | 100                           | 160   |  |

| Sematech                               | 100   | 100                           | 100   |  |

| Remotely Piloted Vehicles              | 46    | 40                            | 123   |  |

| Joint Surveillance/Target Attack Radar | 337   | 236                           | 153   |  |

| Electronic Warfare Development         | NA    | 97                            | 150   |  |

| Mimic                                  | 49    | 67                            | 82    |  |

|                                        |       | SOURCE: DEPARTMENT OF DEFENSE |       |  |

add to that cost, NASA says.

This leaves little money for the kind of investment in the technology base that many in industry, Congress, and the government believe is essential for U.S. business. "It's the Reagan view of science-it's Big Science," says an aide to Jeff Bingham (D., N. M.), the outspoken chairman of the Senate Defense, Science, and Technology Subcommittee and a prime architect of Sematech. He maintains that these programs cost too much and benefit too few, and that federal dollars would be better invested in developing technologies, such as semiconductors and computers, that hold the key to U.S. technological competitiveness in the 1990s and beyond.

Take the superconducting super collider, for example. The Reagan budget seeks \$250 million for the Texas-based facility in 1990, \$160 million of which is earmarked for construction. Under the current plan, that \$160 million investment would pave the way for as much as \$5.9 billion by the time the project is completed in 1998. "The key thing is to get some construction funds," says a DOE official. "That's a commitment, because you don't start building something you don't intend to finish."

Last year saw several top-level reports emerge from both inside and outside the government on the need to revitalize the struggling U.S. technology and industrial base, and yet another is expected shortly, this time from the Congressional Office of Technology Assessment. But this interest is not reflected in the Reagan administration's budget plan. Rather than providing more money for such initiatives, it provides less.

For example, the Defense Advanced Research Project Agency, the Pentagon's

#### Decisions that Bush makes now will set technology policy for at least five years

chief research arm, faces a \$260 million cut in 1990, and almost all of that comes from its technology-base account. Darpa's budget will drop from about \$1.3 billion this year to \$1.1 billion in 1990, followed by a modest 4% increase in 1991. Other technology-base investments, including advanced military research in universities, would suffer losses in excess of \$100 million. By contrast, the Reagan proposal seeks nearly \$2 billion in spending increases for SDI in 1990 and an additional \$1.1 billion in 1991, by which time SDI would cost \$6.7 billion a year using the current five-year defense plan as a guideline. (That includes a combined \$689 million for initial deployment of the technology in 1990 and 1991.)

Ironically, the Pentagon officials announcing the budget took pains to credit the Reagan administration with dramatically increasing R&D expenditures over the last eight years-despite the impending 13% drop in Darpa funding. The increases in R&D spending during the Reagan years are indisputable-defense R&D has almost doubled since 1982 and nondefense R&D is up 50% since then. But critics argue that these increases largely represent spending on SDI, the stealth bomber, and other big-scale programs, while strategic and tactical technologies, such as surveillance and smart weapons, have suffered.

Darpa's 1990 budget plan would cut strategic technology programs by more than \$130 million and tactical programs by almost \$25 million. Smaller line items would also suffer. The Consolidated DOD Software Initiative, for example, is being cut back 10%, or \$3.75 million, to \$32.4 million in 1990. As of 1988, it combined DOD's Joint Ada Program Office, the Software Technology for Adaptable, Reliable Systems program, and the Software Engineering Institute into a single Darpa-controlled program.

In addition materials and electronics technology, which includes advanced semiconductor research, is being cut back

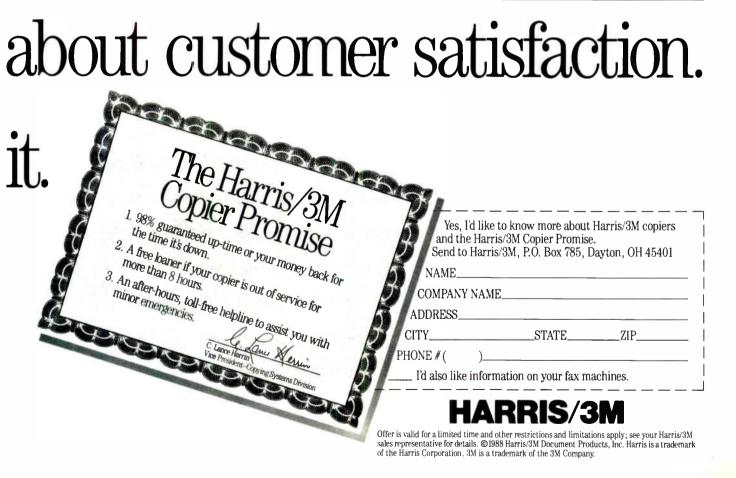

# Every copier company talks

# We're doing something about

Choosing a new copier isn't easy. You look at copiers, you listen to promises. It all gets very confusing.

Now, you don't have to listen to a lot of talk about promises. You can read ours. Because we put it in writing. If you try to compare it to other copier guarantees, you'll find there's no comparison. Suddenly, a difficult decision becomes a very easy choice to make.

Look at the certificate above. Nobody offers you as good a copier guarantee as Harris/3M. So, while

copier salespeople are all giving you a lot of talk, ours will give you something great to read.

Send in the coupon. Or give us a call at 1-800-TLC-COPY. (In Canada, 1-519-668-2230.) We'll send you our 8-page *Consumer Guide to Copiers*. Then, we can talk about it.

Harris/3M copiers have features for all sizes of offices. That includes the 6070. Seventy copies a minute, guaranteed.

by more than \$2 million, or roughly 6%.

That doesn't mean Darpa won't seek any new programs in 1990. For the third year running it is trying to get its Infrared Focal Plane Array program off the ground. Darpa sought \$45 million in 1989 for the program, which is aimed at dramatically reducing the cost of the IR arrays by developing new manufacturing technologies. It had to settle for less than \$9 million when Congress refused to fund it without a more detailed development plan. This year, Darpa is seeking \$33 million for the project.

Not surprisingly, virtually the only Darpa programs to have survived unscathed are its high-profile stars: Sematech and the Microwave/Millimeter Wave Integrated Circuits Program. The administration tried to cut both back in 1989 and failed. "I think they learned that we're committed to these programs for the next five years or so, and that we're not going to play any games," says one congressional aide.

In total, the Reagan budget would spend \$455 million on semiconductor and fiber-optics research in 1990. The superconductor research total for the year is \$287 million, including \$47 million from the Department of Energy and another \$26 million from the National Science Foundation for high-temperature superconductor work. *-Tobias Naegele*

#### TAKEOVERS

### THE GEC-PLESSEY DUEL: JOUSTING FOR COMPANIES

#### LONDON

The struggle between Plessey Co. and General Electric Co. is looking more and more like one of those confusing religious wars that made the Middle Ages such a trial. Lords and knights are launching attacks, defending their realms, signing up and abandoning allies, and just generally thundering about the landscape.

What it all will mean for the map of England is exceedingly difficult to say. But clearly, what began as a straightforward takeover bid has turned into transatlantic combat. Depending on who gets what, the end of hostilities could see vast changes in the British electronics industry, and possibly some significant rearrangements among Continental companies, as well.

The tussle began simply enough. In November, GEC and Siemens AG, the West German electronics giant, formed a joint venture called GEC Siemens plc, which attacked Plessey in a hostile takeover attempt. As each side maneuvered, though, other companies in Europe and the U.S. smelled opportunities. They started lining up to support one or the other combatant—or even to make their own takeover moves.

A key move came on Jan. 15, when Plessey counterattacked against an unguarded GEC flank—GEC Plessey Telecommunications Ltd., London. The telecom company is a joint venture between the two that dates back to a more peaceful era (March 1988). Plessey announced that it is beginning legal maneuvers to take over full ownership. It charges that the GEC-Siemens takeover attempt violates certain provisions of the agreement setting up the joint venture, and that GEC is therefore obligated to sell its 50% share to Plessey.

The counterattack came at the opportune moment, tactically speaking. The GEC-Siemens attack had stalled, thwarted by the intervention of the British government's Monopolies and Mergers Commission on Jan. 12. The commission is evaluating the proposed GEC-Siemens takeover to determine whether it would be against the national interest, a process

ke three months. The Euronic Community is also invesee whether the deal violates ions intended to promote

The move against GEC's share in GEC-Plessey Telecommunications should, if nothing else, buy Plessey even more time. GEC presumably will resist the Plessey buyout attempt, in which case the issue will be tossed into the courts.

The delays appeared to be crucial. After GEC and Siemens made their move against Plessey, a consortium of other companies banded together and announced on Jan. 7 that it would try to take over GEC. If the consortium had succeeded, GEC would of course have been in no position to take over anything, since it would no longer have existed.

But two weeks later, the consortium, called Metsun Ltd., canceled that plan after some major defections. Among them: STC plc, another British company, and General Electric Co. of Fairfield, Conn. This alone would not have been fatal to the consortium's efforts; AT&T Co. and Northern Telecom Ltd. were reported to have been discussing joining Metsun. As telecommunications companies, both would seem to be most interested in owning GEC-Plessey. This might have complicated Plessey's own effort to buy out GEC, but war is a brutal business. GE's defection was more serious. It didn't just drop out of the battle for GEC, it switched sides. On Jan. 13, GE announced that it would merge with GEC its interests in Europe in consumer products, medical equipment, and some power-generation equipment. (Beyond the coincidence of their names, the two companies are not related.) A combined GE-GEC would have been in a far better

An anti-GEC consortium fell apart as a key member quit and another switched sides

position to fight off Metsun.