**CIRCUITS CIRCUITS** for electronics **aineers**

**Edited by Samuel Weber** Executive Editor. **Electronics**

> Electronics Magazine ook Series

#### **ELECTRONICS BOOK SERIES**

Also published by Electronics

- Microprocessors

- Large scale integration

- Data communications

- Applying microprocessors

Library of Congress Catalog Card No. 76-57777

Copyrighte 1977 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

McGraw-Hill Publications Co. 1221 Avenue of the Americas New York, New York 10020

M. L. WILLIAMS

World Radio History

# **CIRCUITS CIRCUITS CIRCUITS CIRCUITS CIRCUITS CIRCUITS** for electronics **Ineers** endineers **iineers**

**Executive Editor,**

ectronics. Magazine **Book Series**

# table of contents

#### 1. Amplifiers

- Single preamplifier/isolator drives If and vIf receivers

- 2 Unity-gain stage is 50-ohm driver

- 3 Eliminating offset error in sense amplifiers

- Dc restorer for video use offers ultra-stability

- CATV transistors function as low-distortion vhf preamplifier

- High-speed voltage-follower has only 1-nanosecond delay

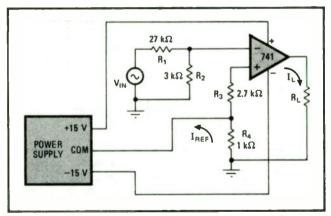

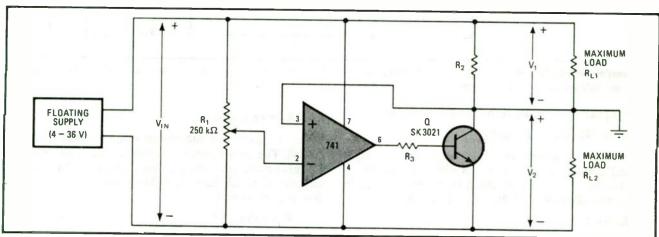

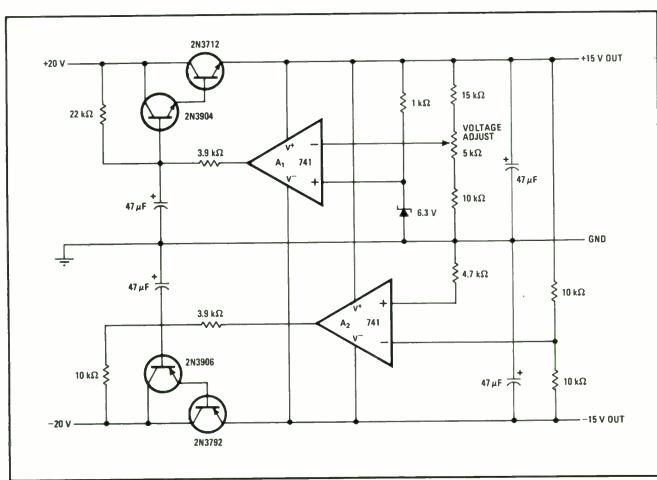

- Getting power and gain out of the 741-type op amp 7

- High-gain triple Darlington has low saturation voltage

- Transducer preamplifier conserves quiescent power

- 10 Two ICs make low-cost video-distribution amp

#### 2. Analog-digital converters

- 12 Adding automatic zeroing to analog-to-digital converter

- 13 Logic system checks out analog-to-digital converter

- 14 Height-to-width converter digitizes analog samples

- 15 Current source and 555 timer make linear v-to-f converter

- 16 Analog-to-digital converter produces logarithmic output

- 17 Comparators and resistors form clockless a-d converter

- 18 Comparator IC forms 10-bit a-d converter

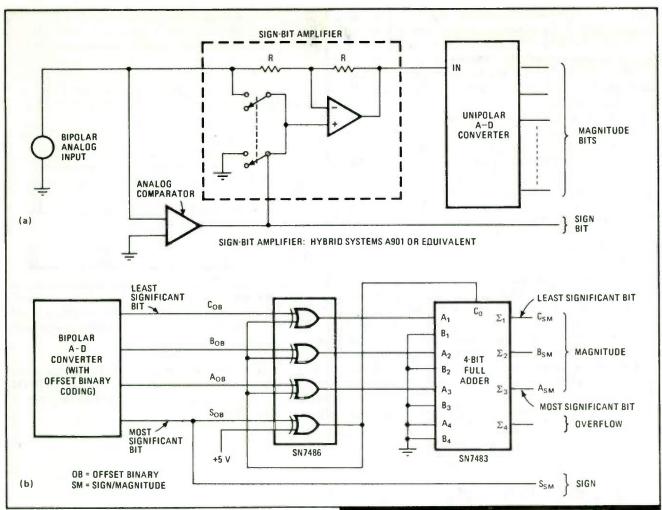

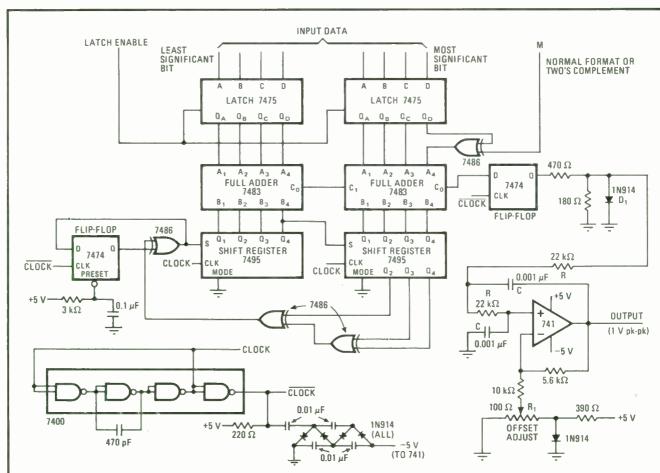

- 19 Coding a-d converters for sign and magnitude

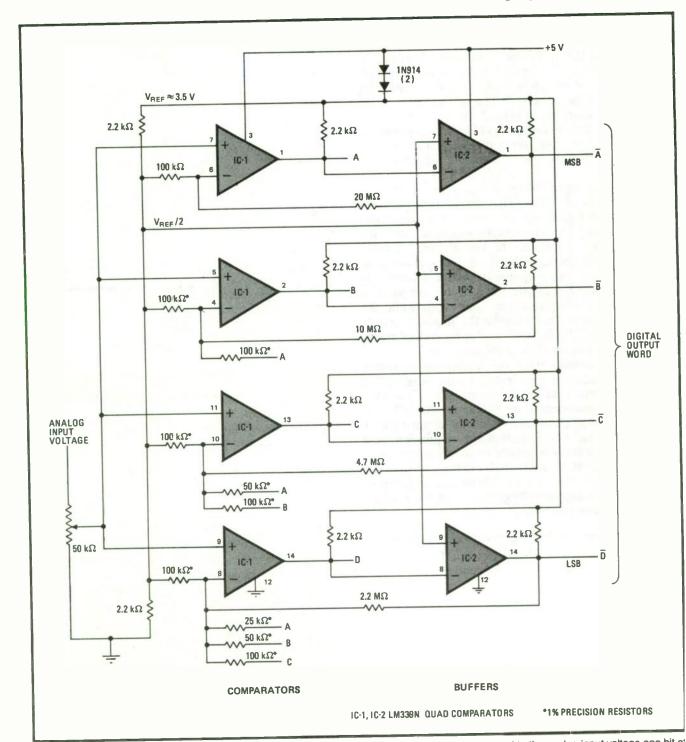

- 21 Four-bit a-d converter needs no clock

#### 3. Analog signal processing

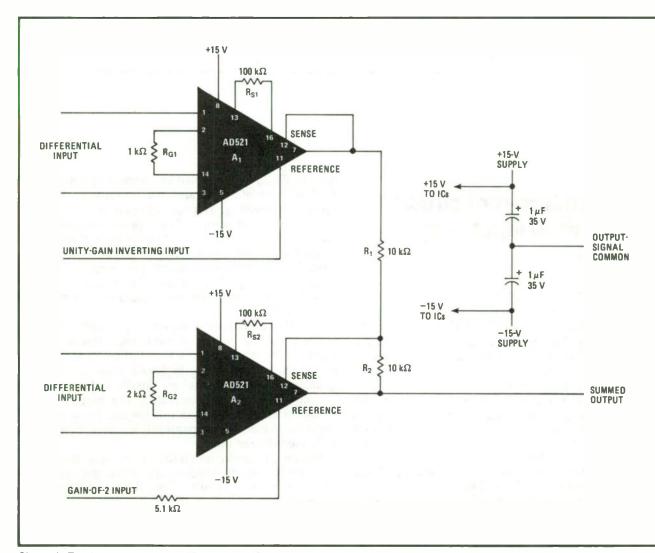

- 23 Two instrument ICs sum six inputs

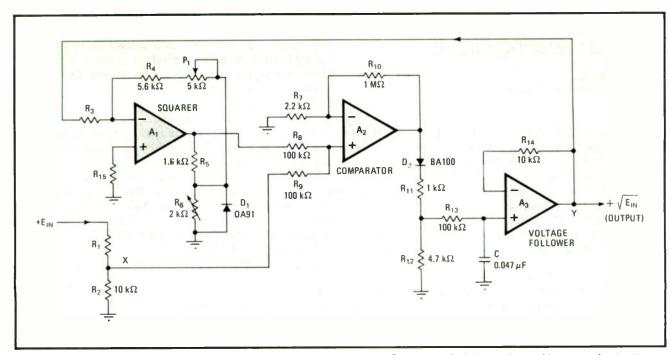

- 24 Analog square-root circuit handles wide input range

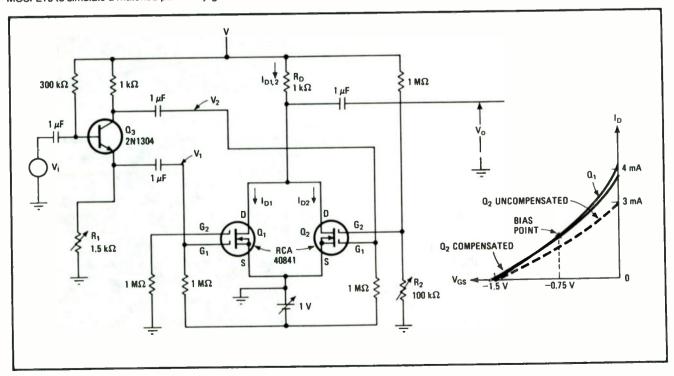

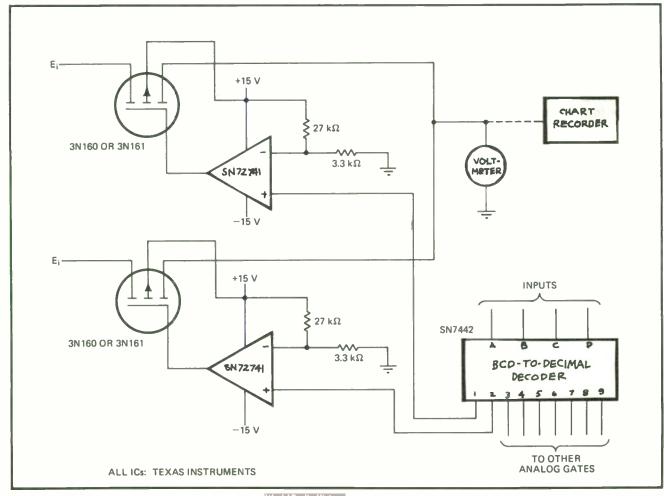

- 26 Quasi-matched MOSFETs form filterless squaring circuit

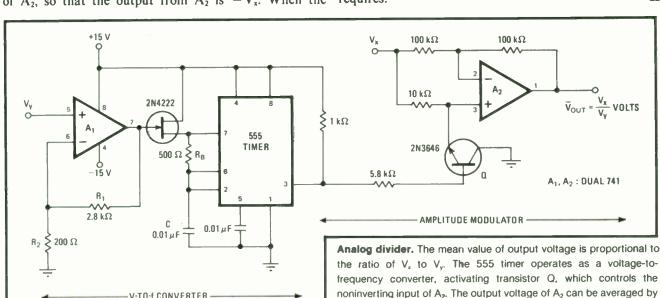

- 27 Timer IC paces analog divider

#### 4. Audio circuits

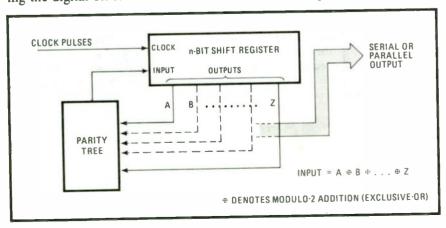

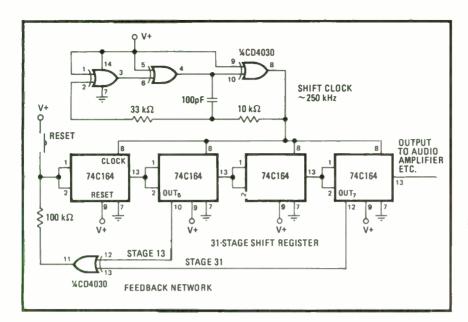

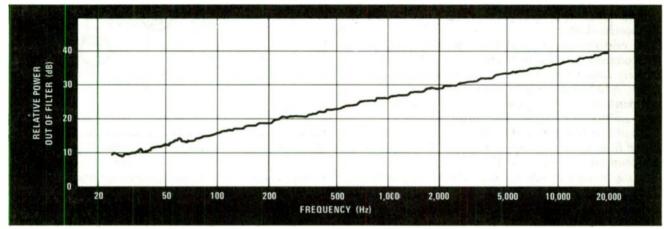

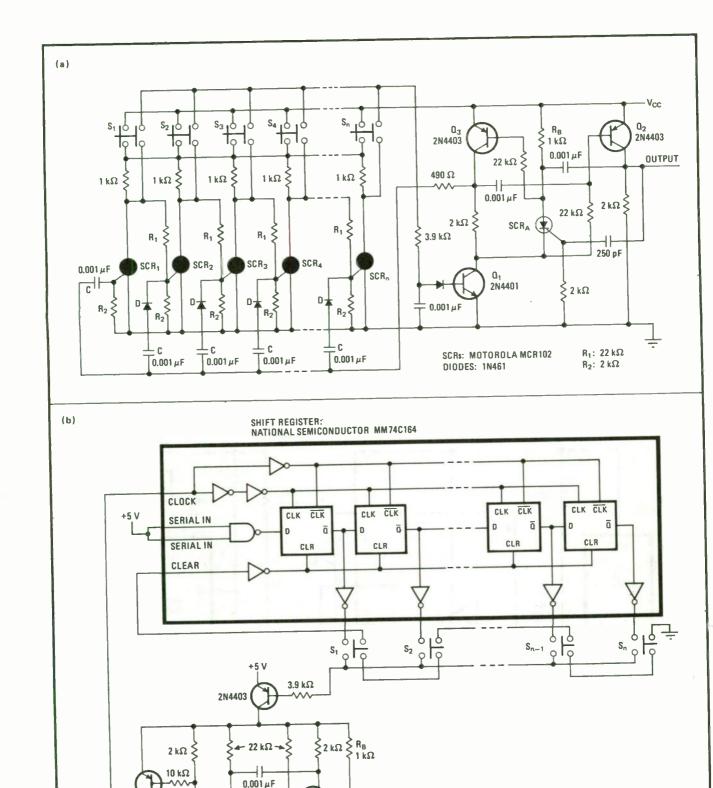

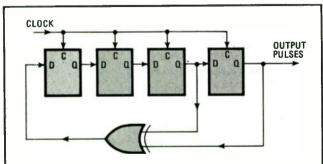

- 28 Shift register with feedback generates white noise

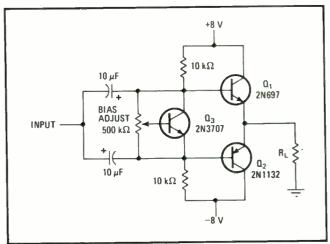

- 30 One-transistor regulator minimizes amplifier distortion

- 30 C-MOS sums up tones for electronic organ

- 32 Handy audio amplifier minimizes power drain

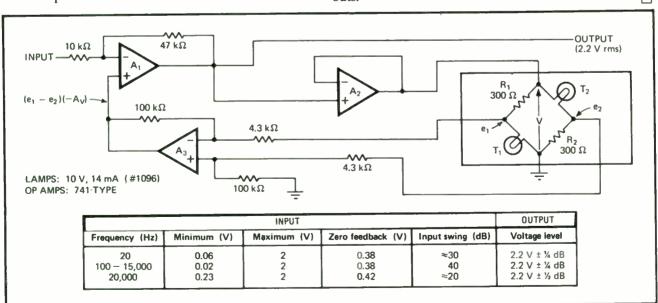

- 34 Audio amplitude leveler minimizes signal distortion

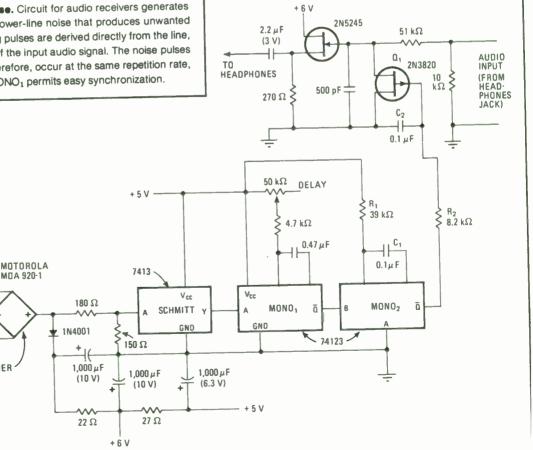

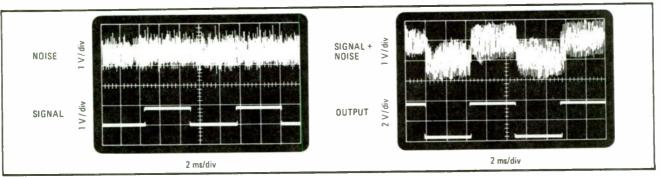

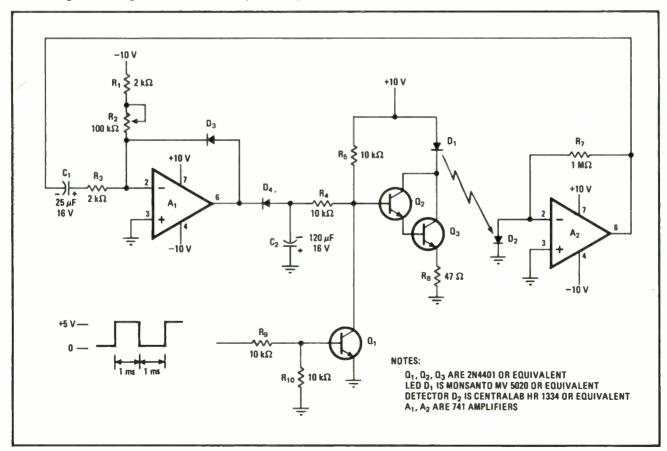

- 35 Synchronous noise blanker cleans up audio signals

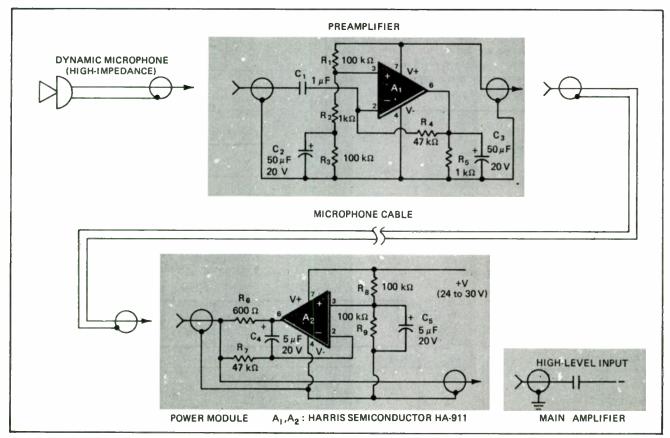

- 36 Microphone preamp gets power through signal cable

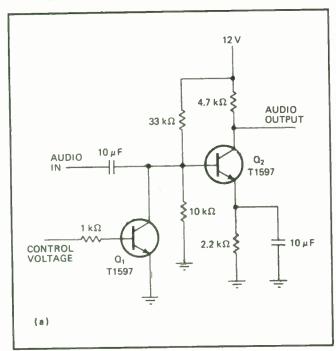

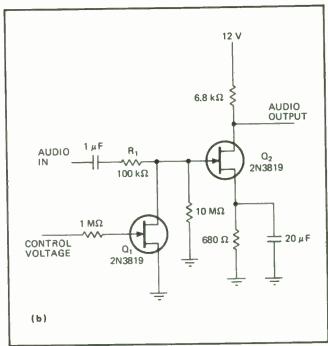

- 37 FETs remove transients from audio squelch circuit

#### 5. Automatic gain control

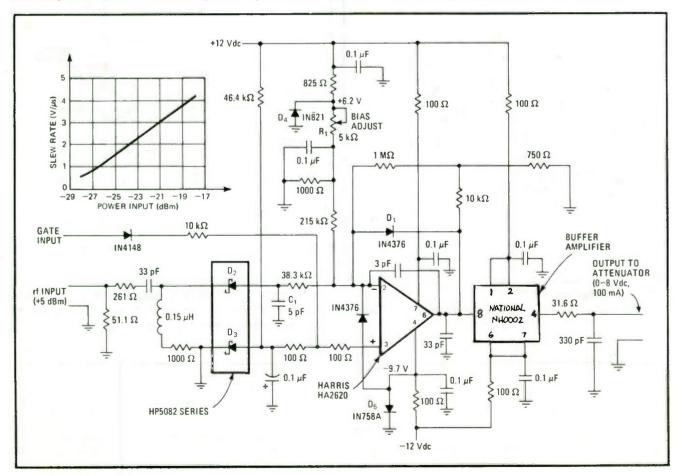

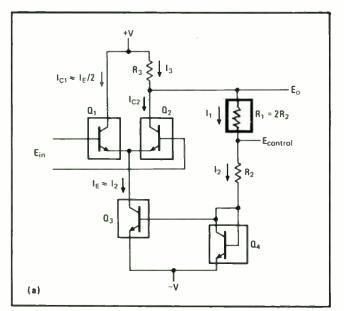

- 38 Agc threshold detector provides fast slewing

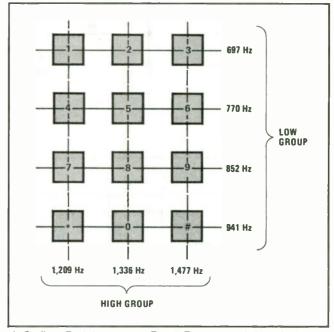

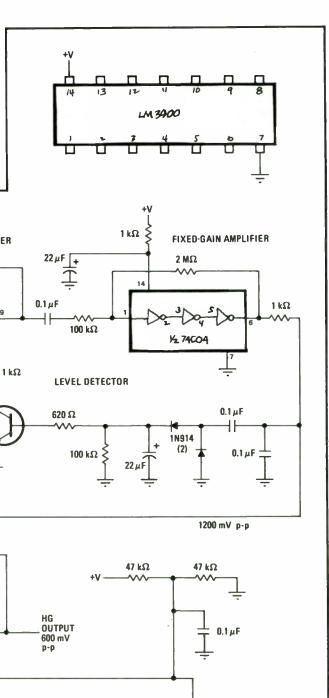

- 39 Touch tone receiver front end provides ago and filtering

- 41 Varistor voltage divider improves receiver agc

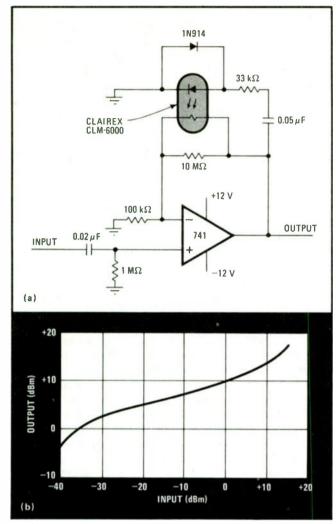

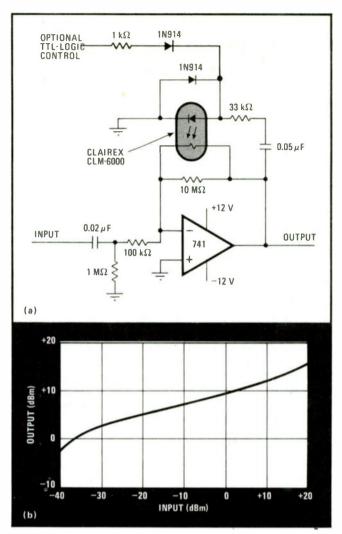

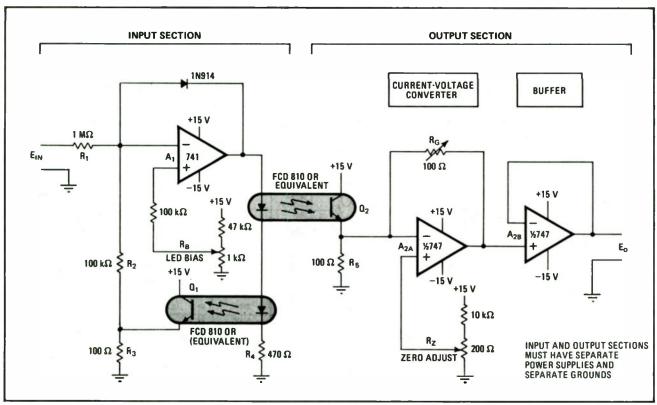

- 42 Photocoupler provides agc for audio communications

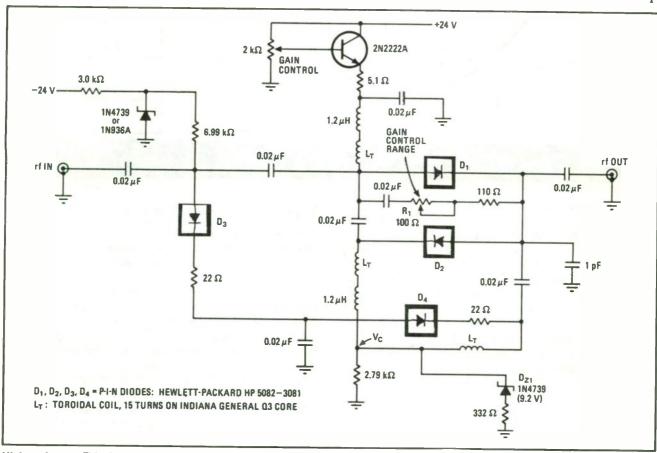

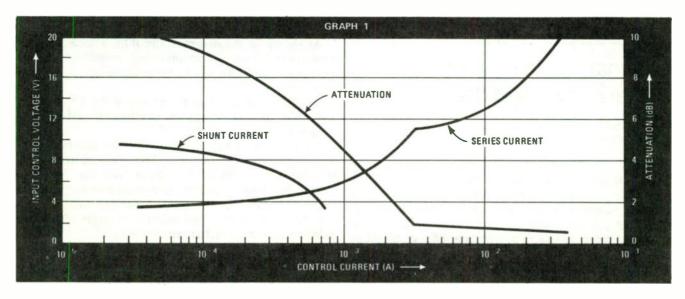

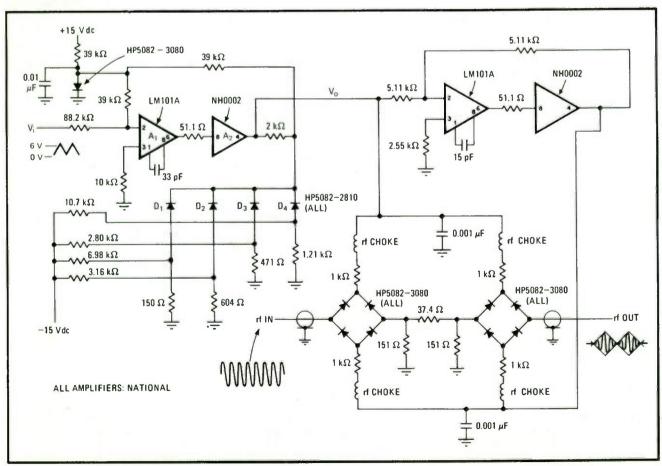

- 43 Broadband p-i-n attenuator has wide input dynamic range

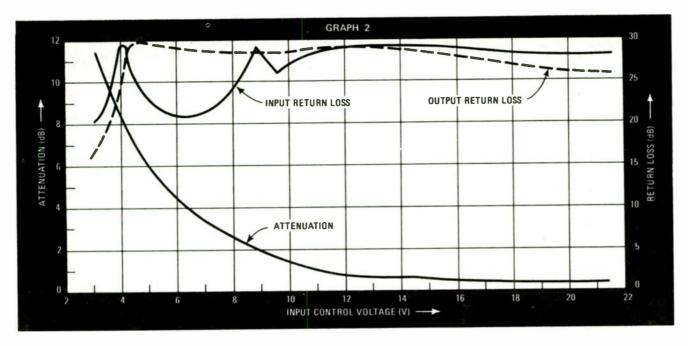

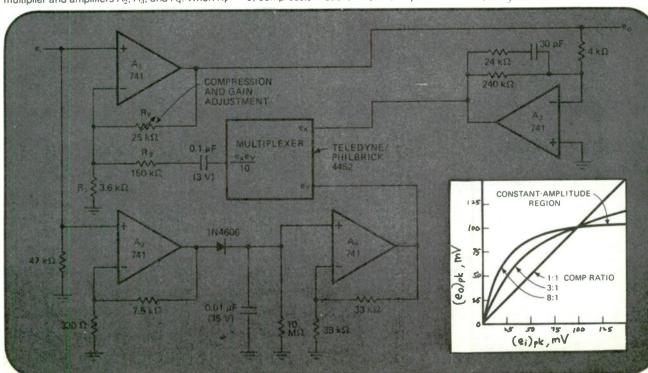

- 44 Automatic gain control operates over two decades

- 45 Automatic gain control quells amplifier thump

#### 6. Automotive circuits

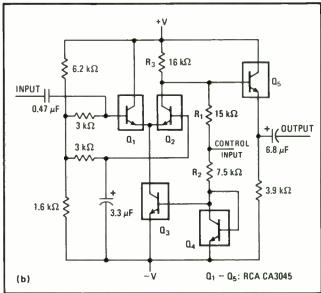

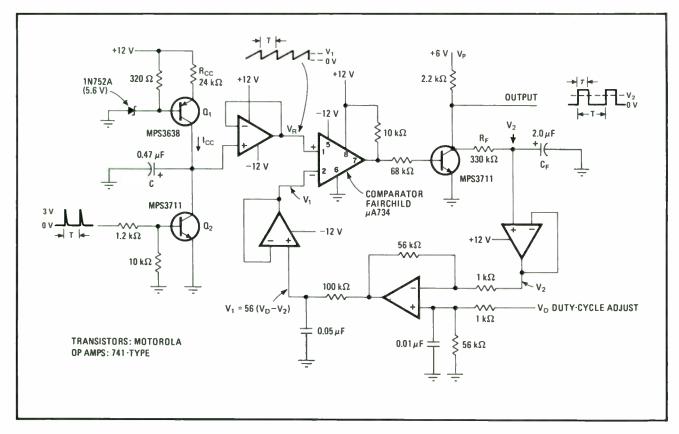

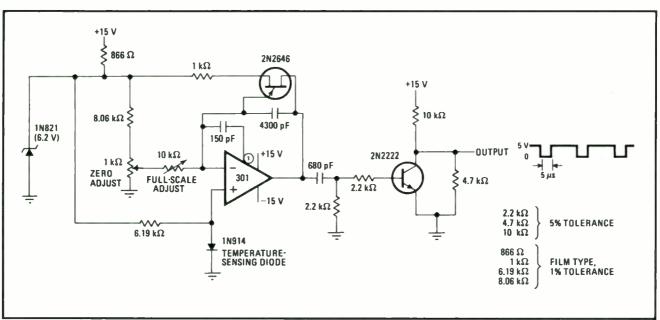

- 48 Precision auto tachometer squelches point bounce

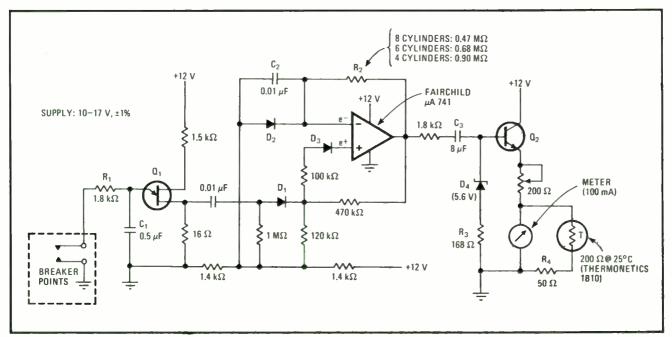

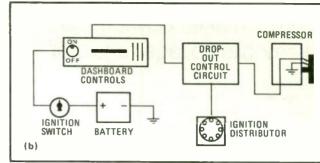

- 49 Sure-fire ignition system safely limits engine rpm

- 50 Ice warning indicator monitors road conditions

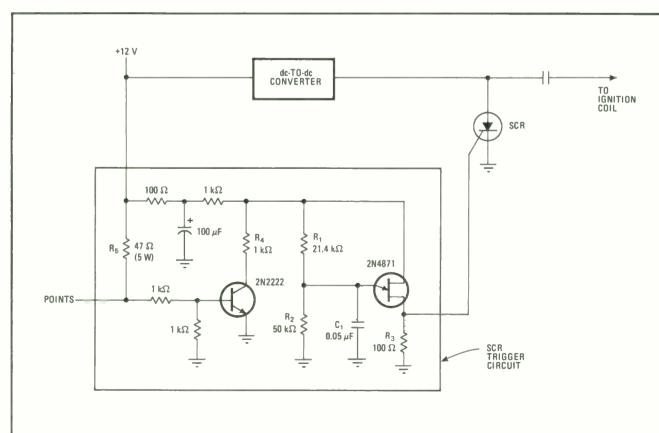

- 51 IC boosts starting energy for solid-state ignition 52 Electronic switch controls automobile air conditioner

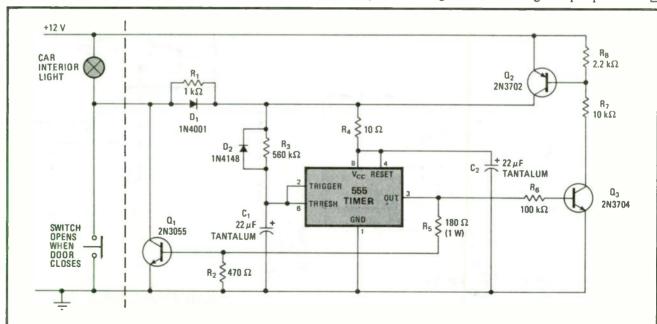

- 53 Tail-biting one-shot keeps car-door light on

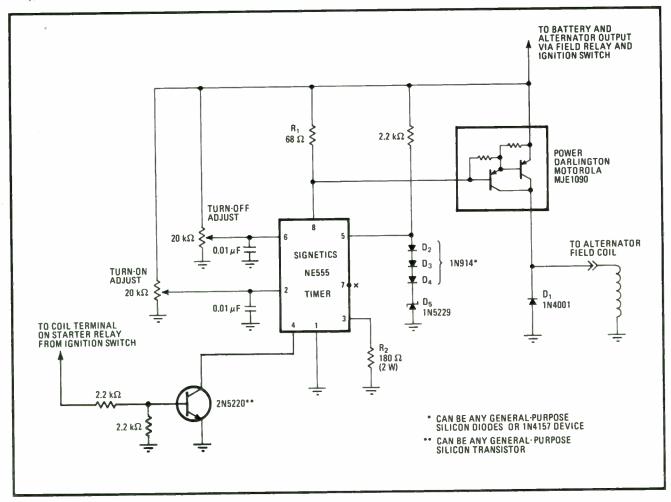

- 54 IC timer makes economical automobile voltage regulator

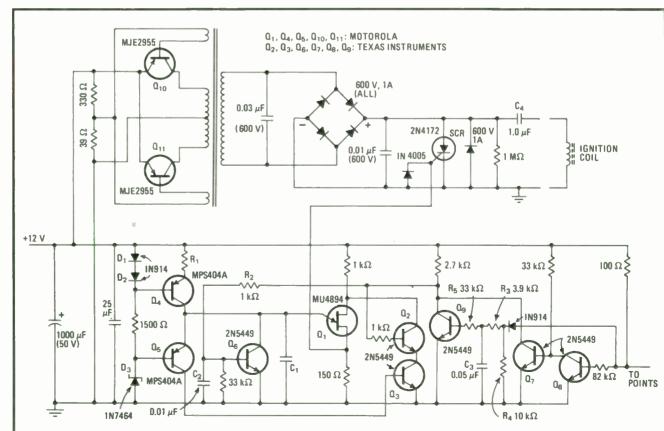

- 55 Automobile ignition system is rugged and reliable

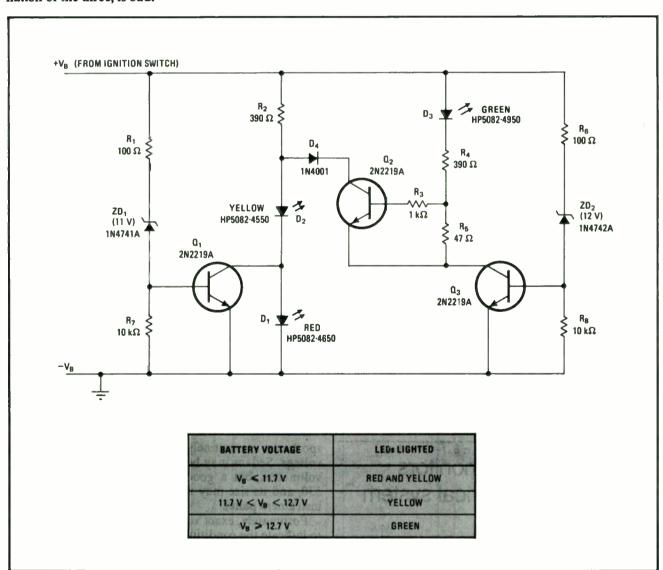

- 56 Tri-level indicator monitors automobile's electrical system

#### 7. Bridge circuits

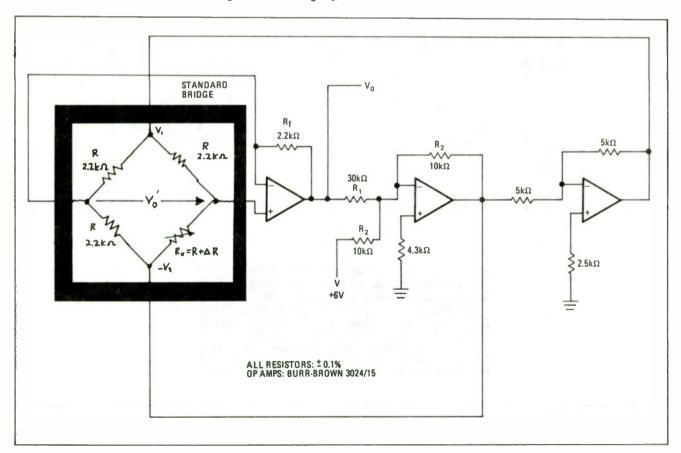

- 58 Feedback linearizes resistance bridge

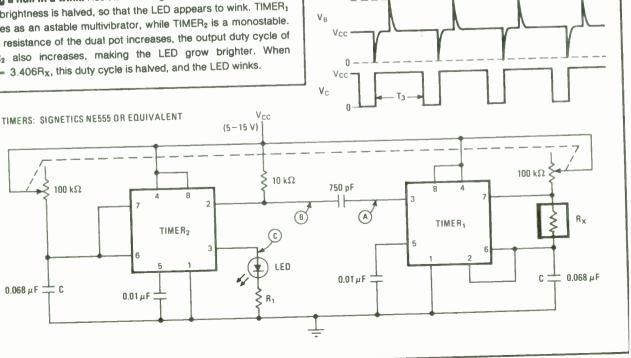

- Winking LED notes null for IC-timer resistance bridge

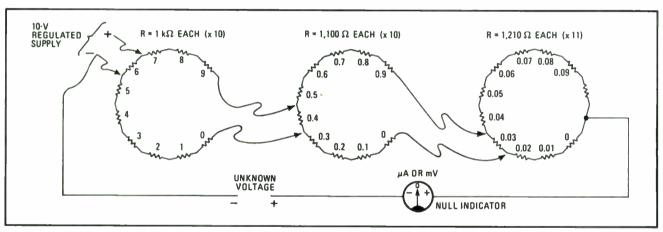

- Circular voltage divider needs fewer resistors

#### Clock circuits

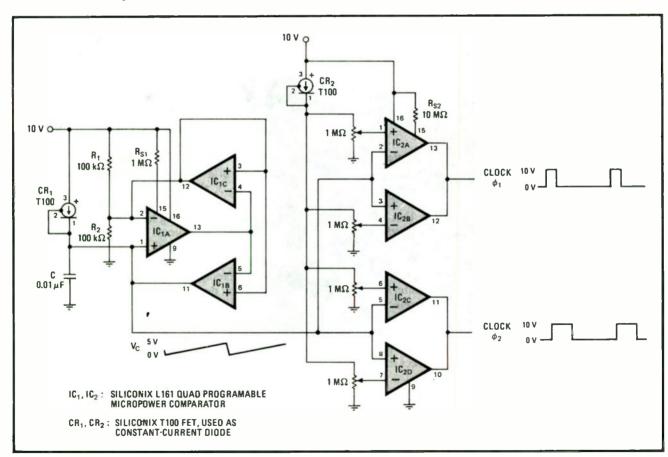

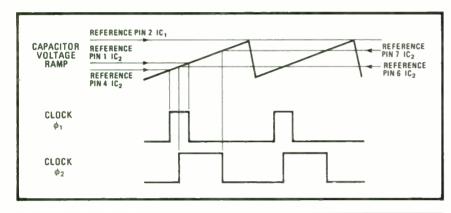

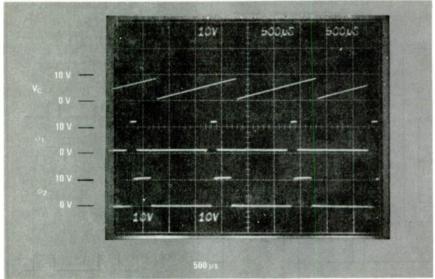

- 61 Micropower comparators generate 2-phase clock

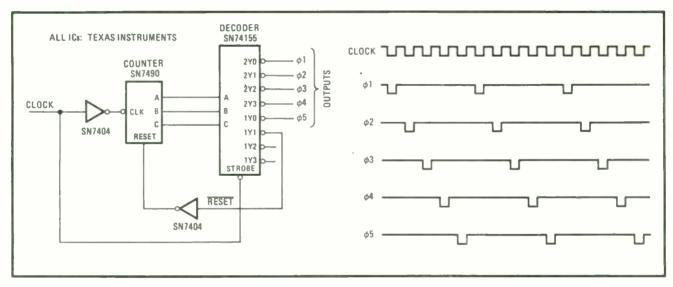

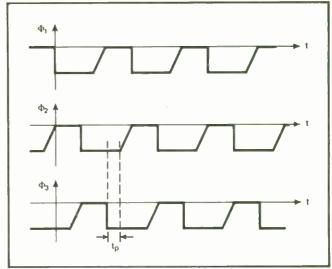

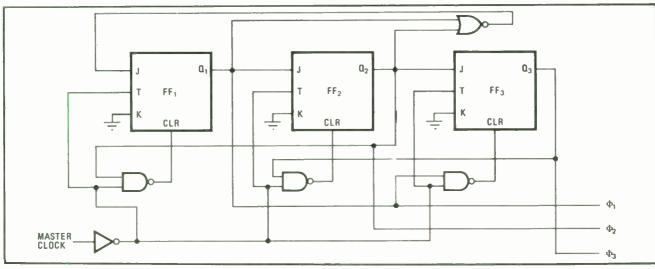

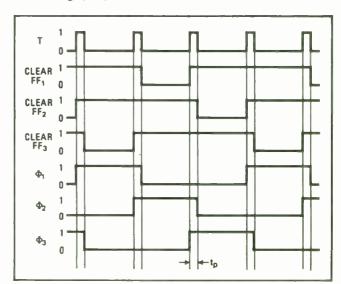

- 63 Multiphase clock produces nonoverlapping pulses

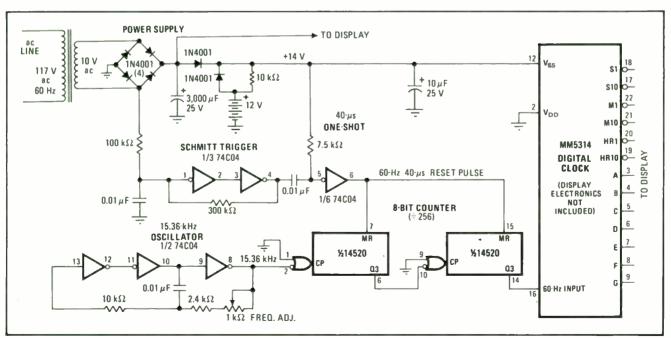

- 63 Oscillator drives digital clock when ac power fails

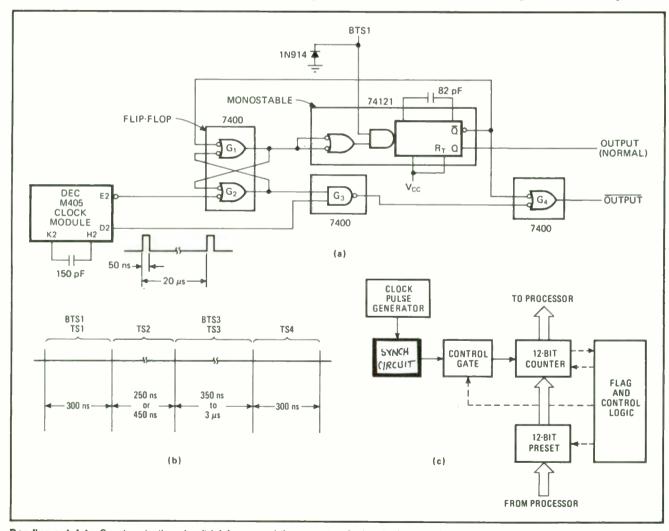

- TTL interface circuit synchronizes computer clock

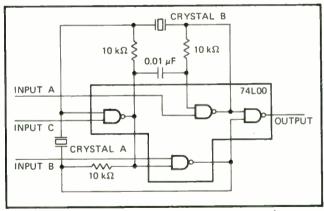

- 66 Quad NAND gate package yields two-frequency clock

- Generating overlapped clock phases for CCD array

#### 9. Comparators

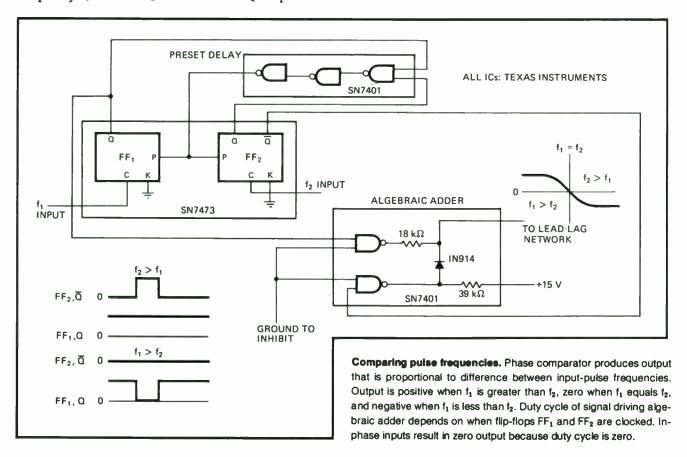

- 68 Phase comparator for servo loops

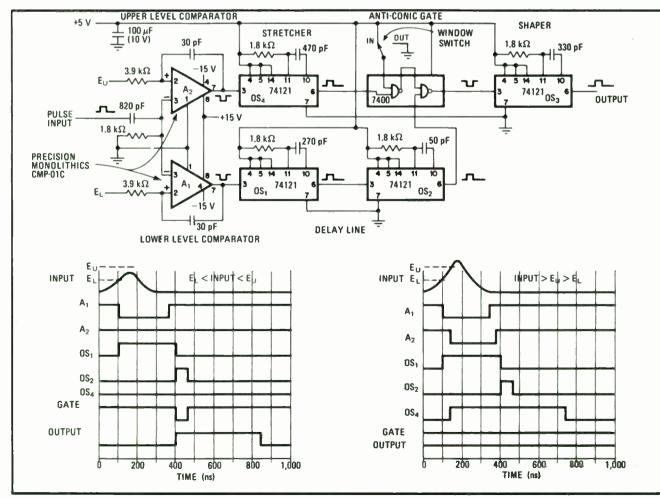

- 69 TTL gates speed up pulse-height analysis

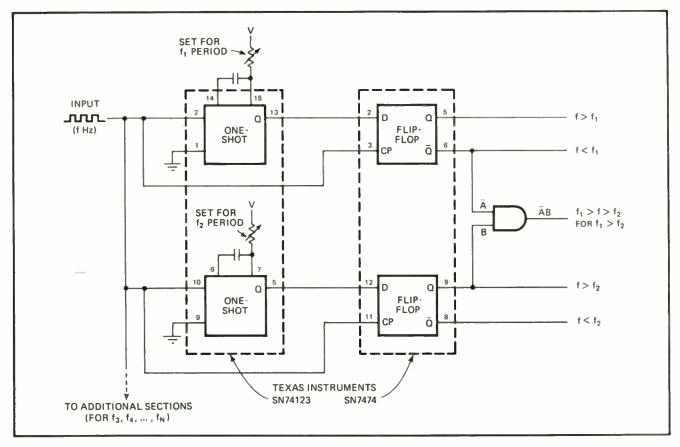

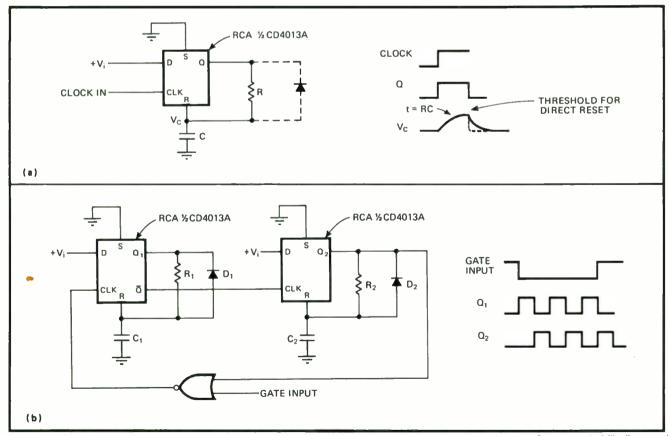

- One-shot/flip-flop pairs detect frequency bands

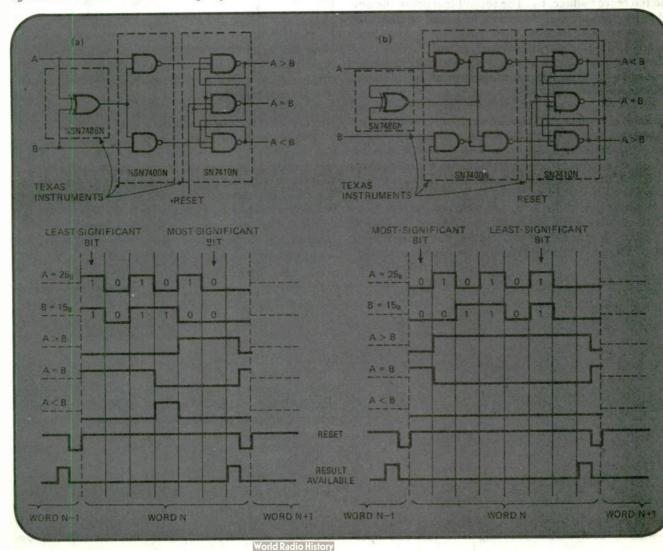

- Simple logic circuits compare binary numbers

- 72 Varying comparator hysteresis without shifting initial trip point

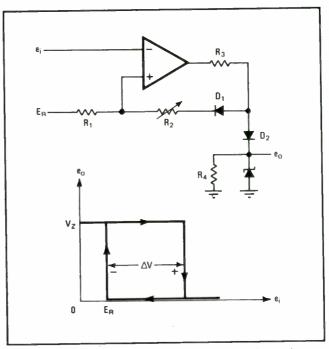

- 72 Window comparator needs only one op amp

- 74 Single op amp compares bipolar voltage magnitudes

- 75 Logic circuit selects most intense signal

- Modified window comparator compensates for temperature

#### 10. Control circuits

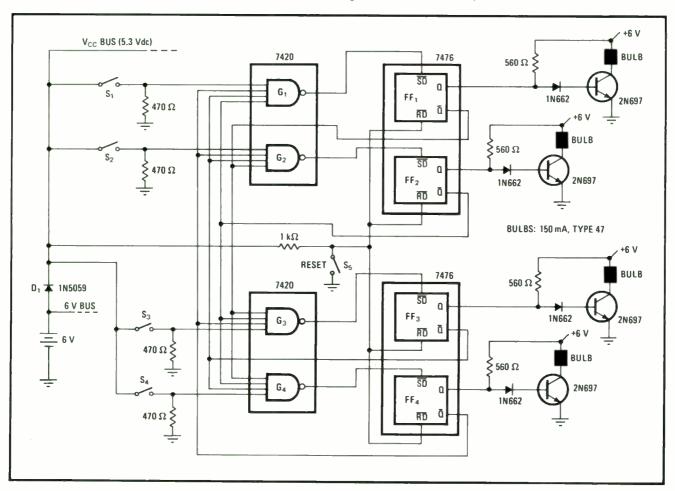

- 78 Complementary lighting control uses few parts

- Precision triac trigger has wide dynamic range

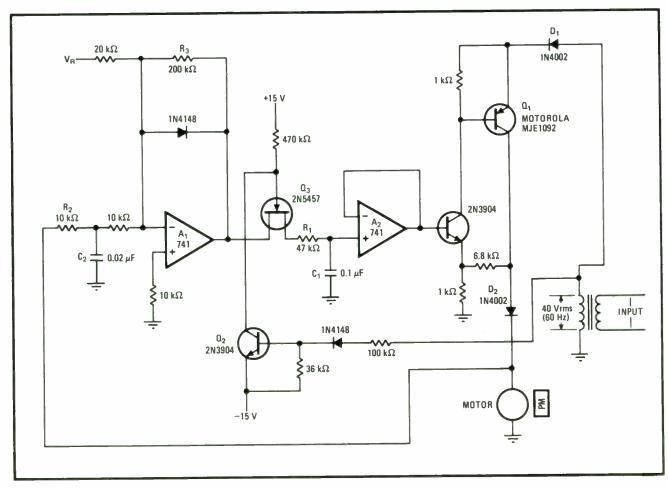

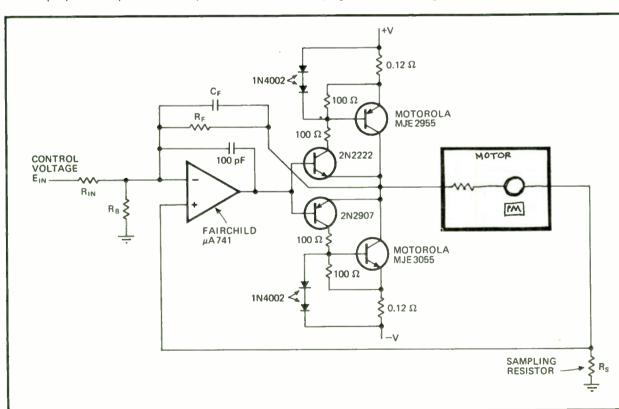

- 80 Sampling regulator controls motor speed

- 81 Dc motor control circuit cancels armature resistance

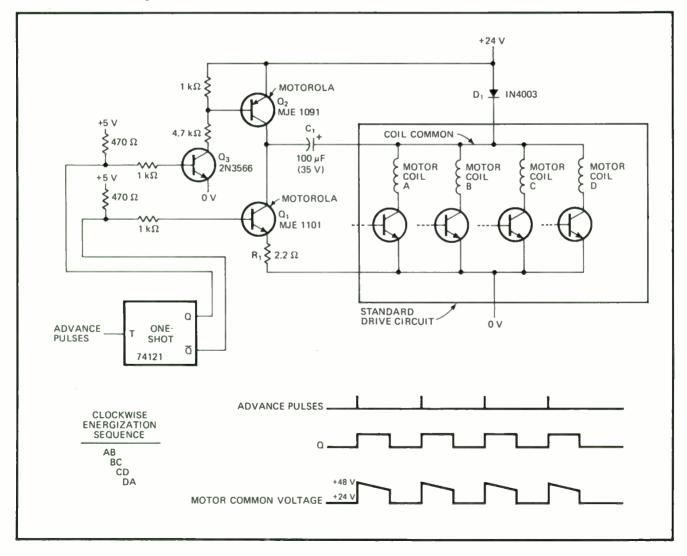

- Stepper drive circuit boosts motor torque

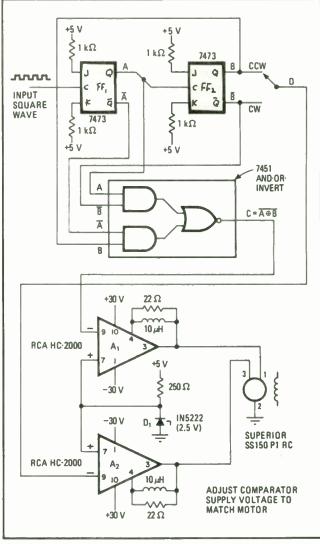

- Logic circuit converts synchronous motor to stepper

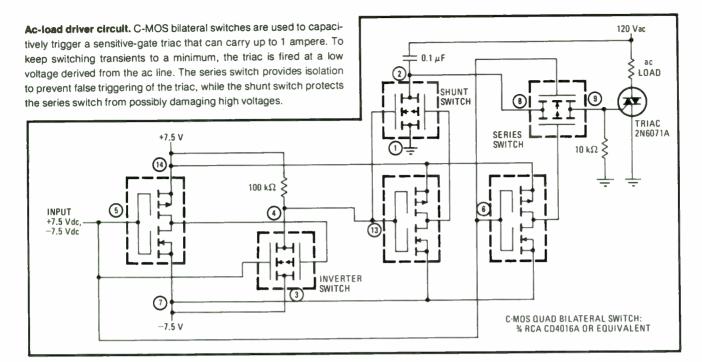

- 83 Controlling ac loads with C-MOS bilateral switches

#### 11. Counters

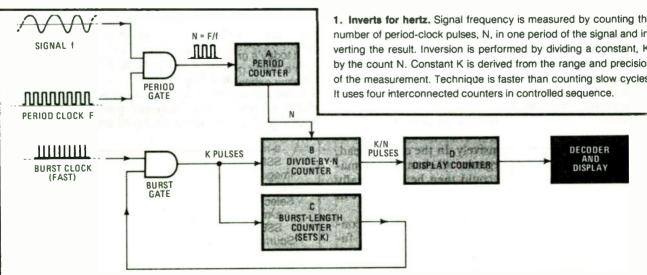

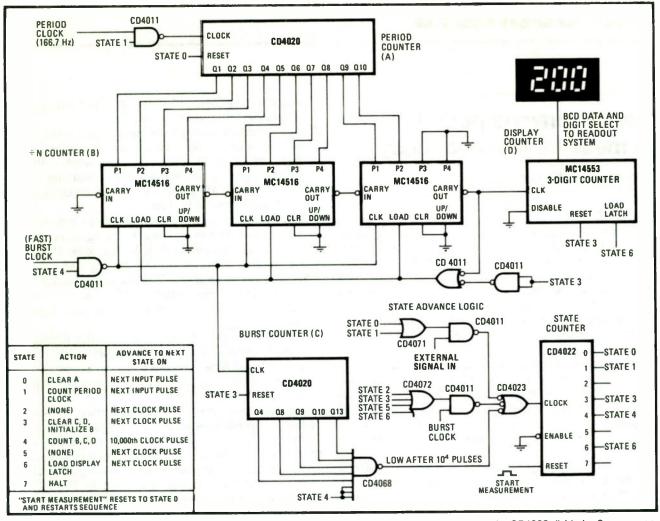

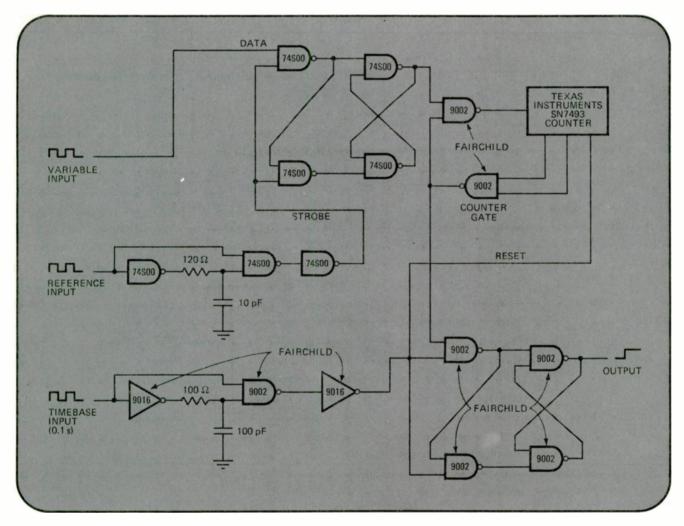

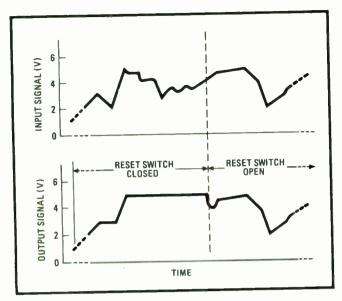

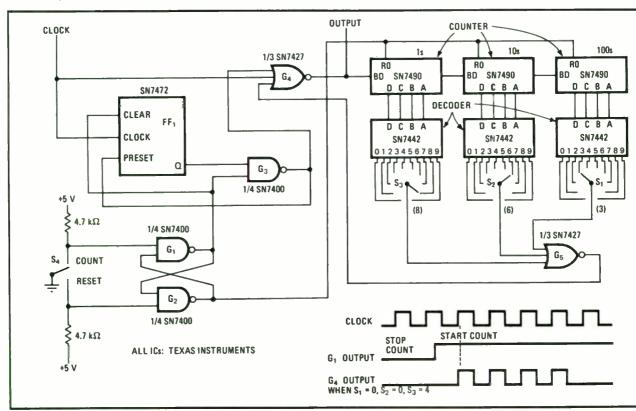

- 85 Counter inverts period to measure low frequency

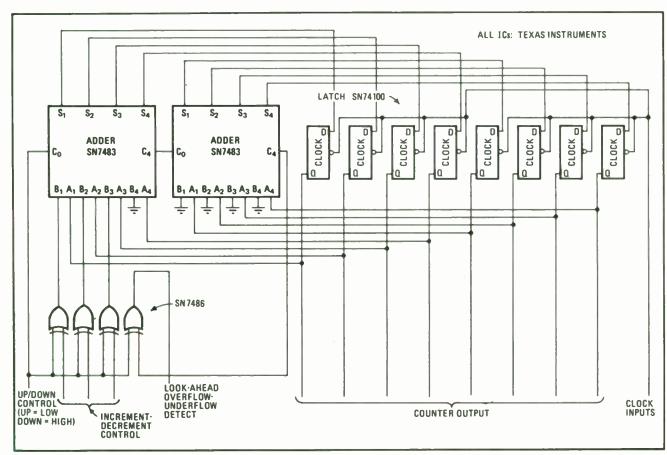

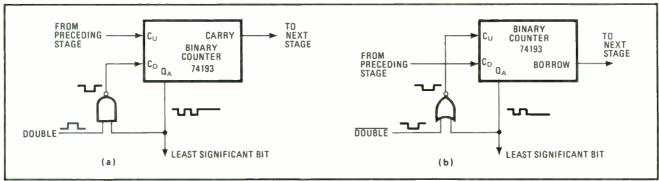

- Up/down synchronous counter takes just four MSI packages

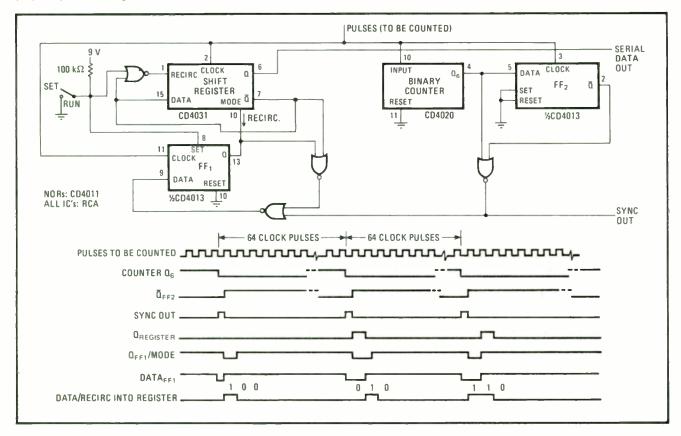

- 88 C-MOS counting circuit accumulates 270 pulses

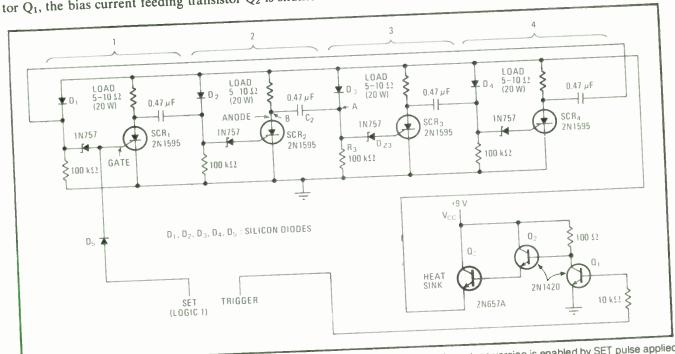

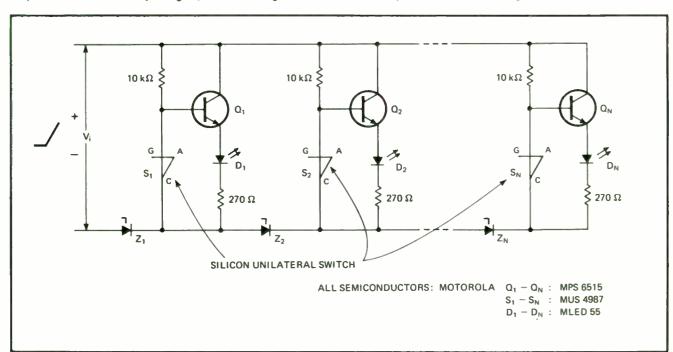

- 89 High-power counter drives 20-watt loads

- 90 Transistor array converts to fast-switching thyristors

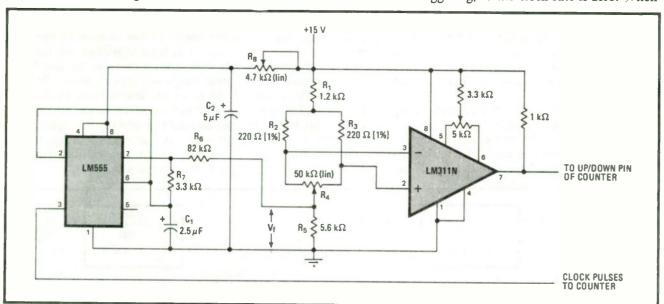

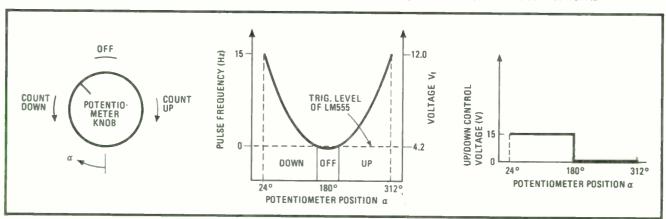

- 91 Potentiometer and timer control up/down counter

- 92 External gate doubles counter speed

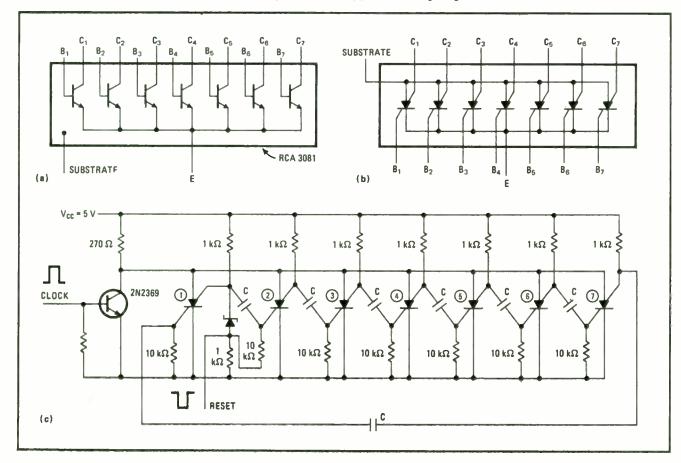

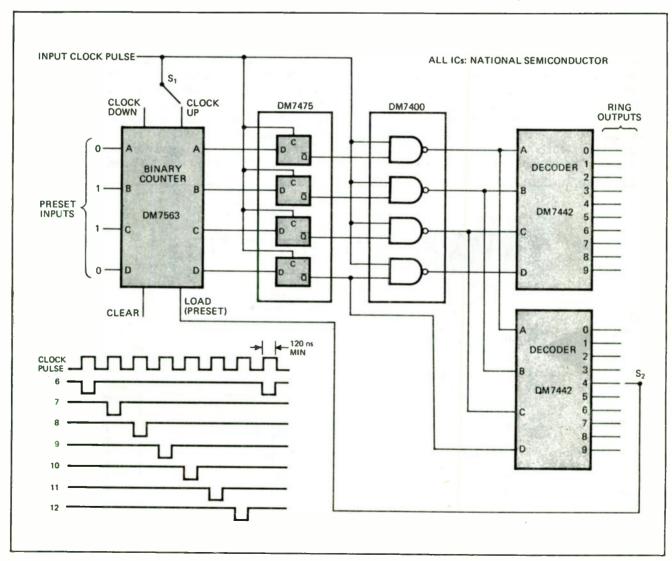

- 92 Ring counter eliminates false gating signals

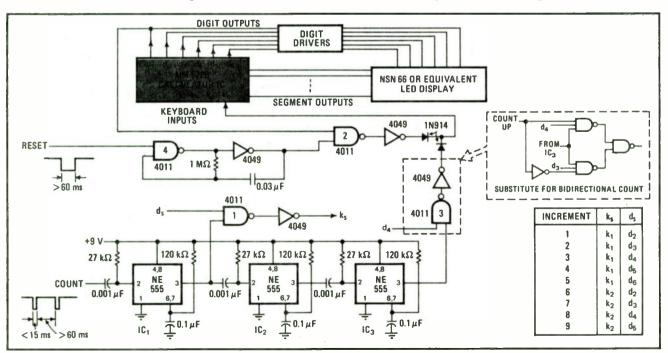

- 94 Low-speed counter uses low-priced calculator chip

#### 12. Current sources

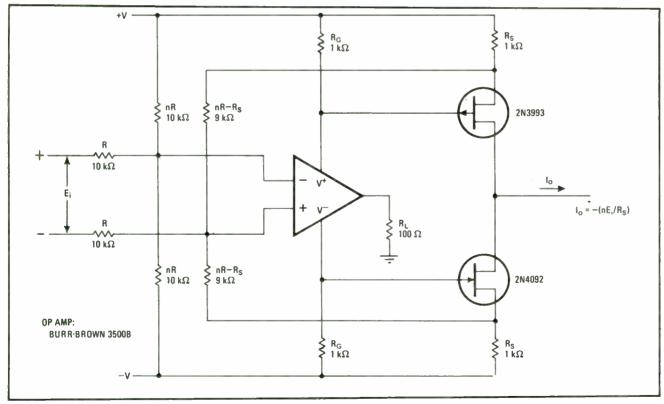

- 96 Controlled current source is versatile and precise

- Bilateral current source is digitally programable

- 98 Controllable current source eliminates matched resistors

#### 13. Detectors

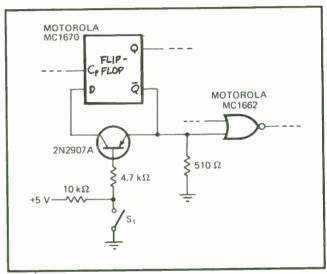

- 99 Simple gating circuit marks both pulse edges

- 100 Differentiate and count to find frequency error

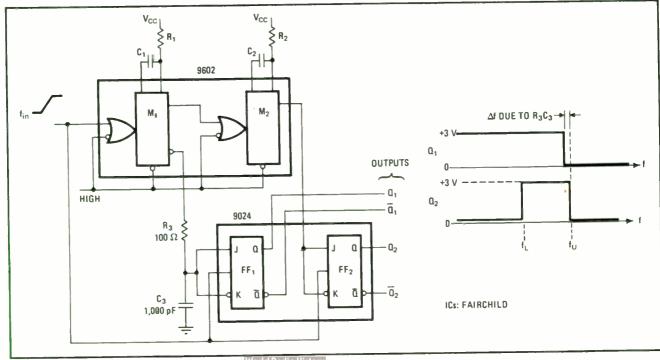

- 101 Frequency discriminator uses one-shot and flip-flop

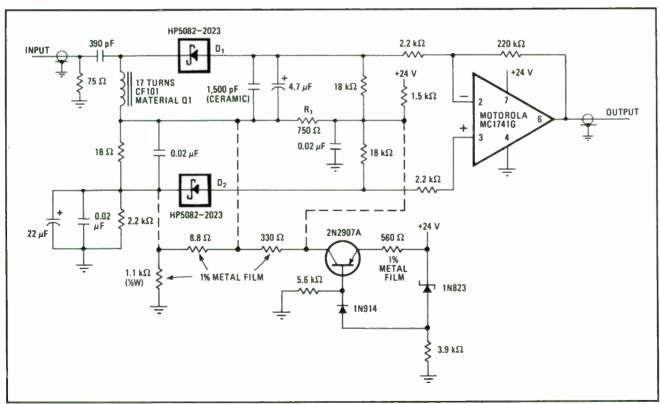

- 102 Schottky diode pair makes an rf detector stable

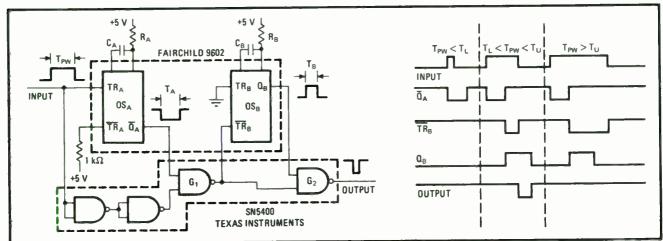

- 103 Temperature-stable decoder for modulated pulse widths

- 104 Video detector stores peak for minutes

- 105 LED display shows beat frequency

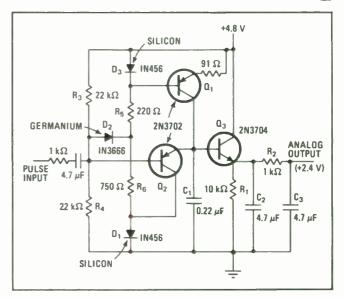

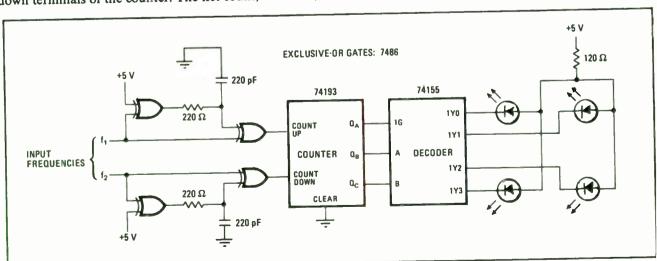

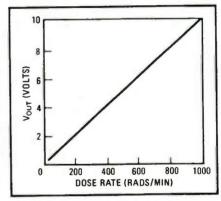

- 106 Radiation monitor has linear output

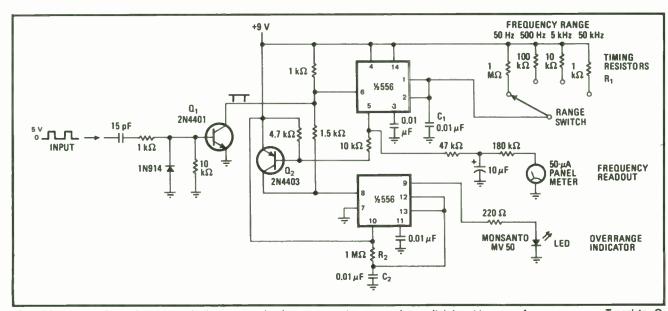

- 106 Overrange indicator can enhance frequency meter

#### 14. Digital-analog converters

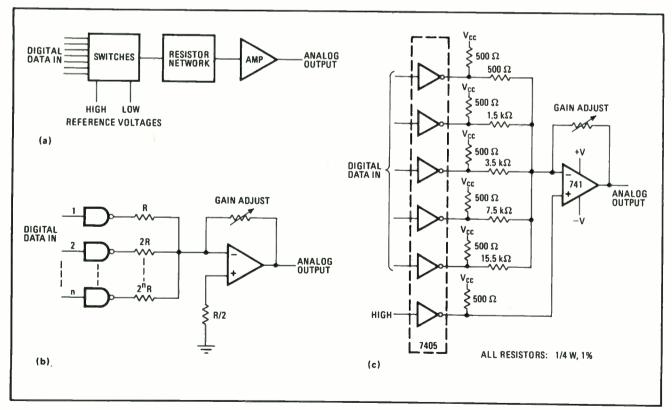

- 108 Logic driving gates double as d-a converter switches

- 109 No-ladder d-a converter works from one 5-V supply

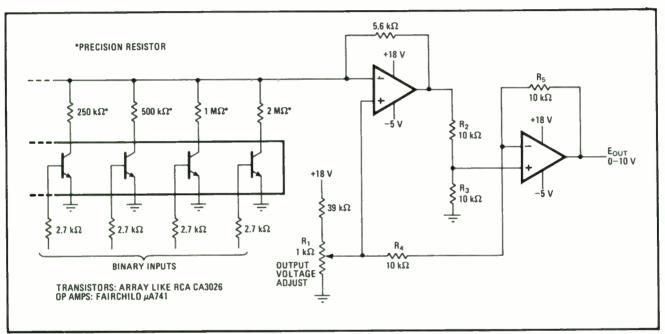

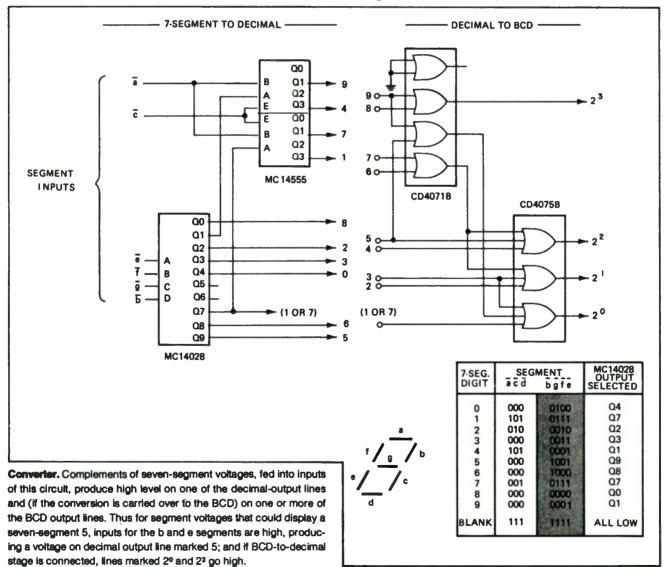

- 110 Digital-to-analog converter is built from low-cost parts

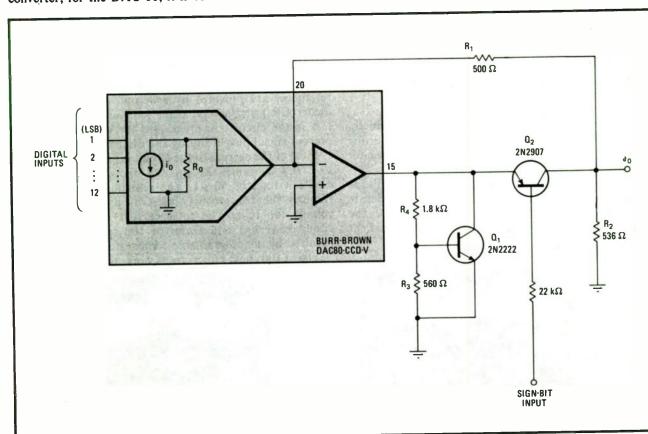

- 110 Amplifier adds sign bit to a-d converter output

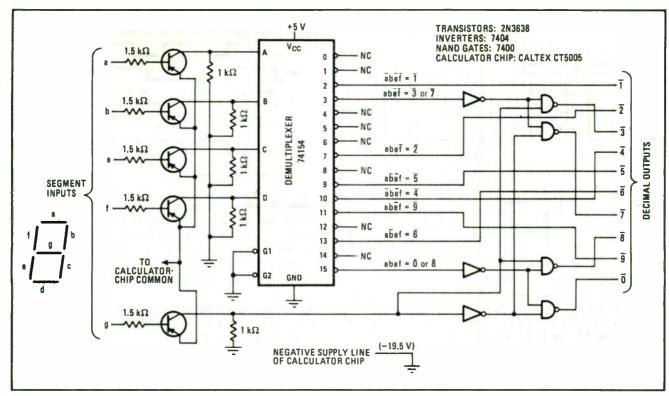

#### 15. Discriminators

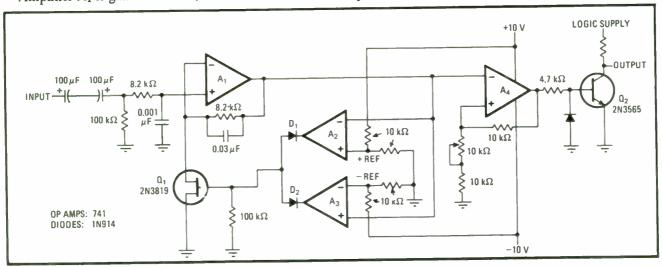

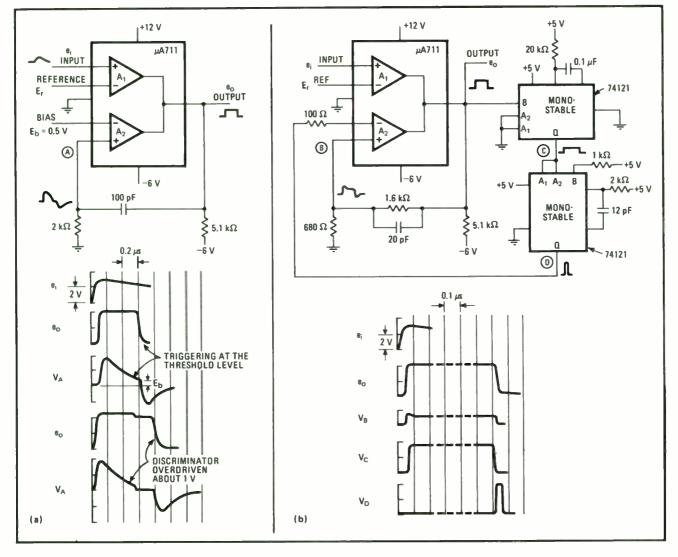

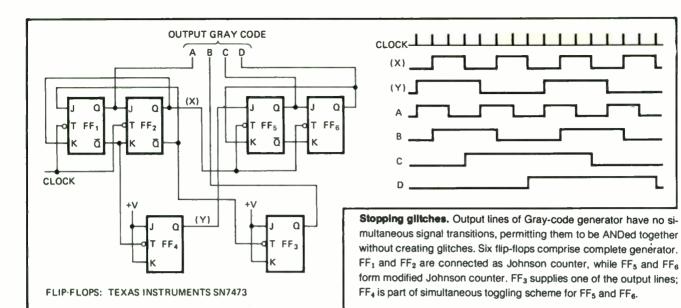

- 112 Adjustable discriminator cleans up signal noise

- 113 Two-IC pulse discriminator handles wide range of inputs

- 114 Voltage discriminator has 0.1-mV resolution

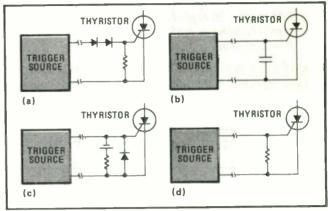

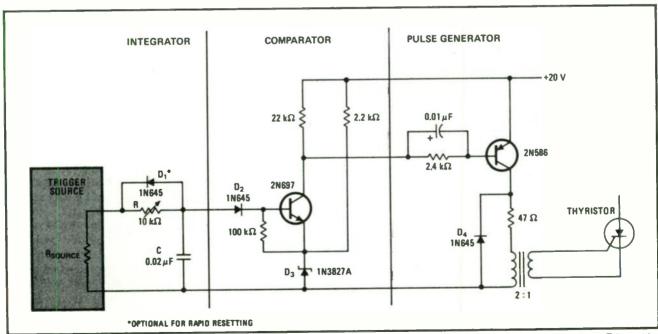

- 115 Buffer keeps noise from triggering thyristor

#### 16. Display circuits

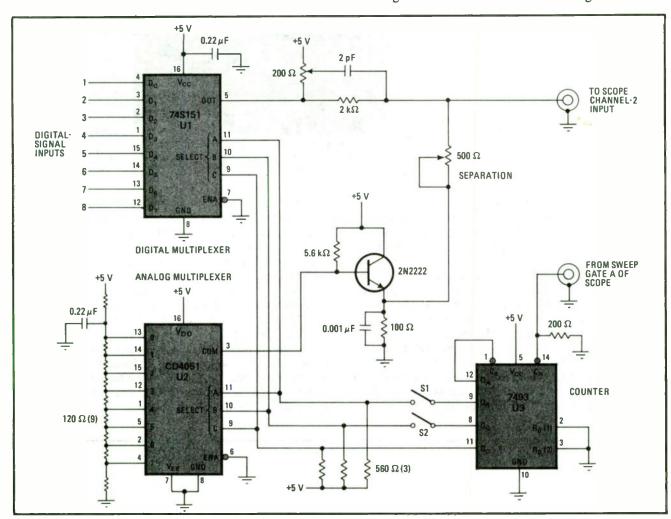

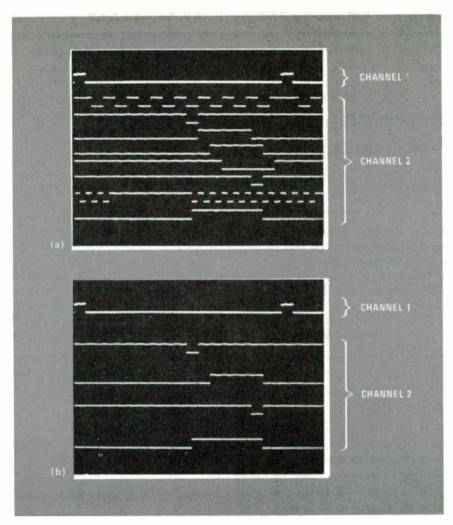

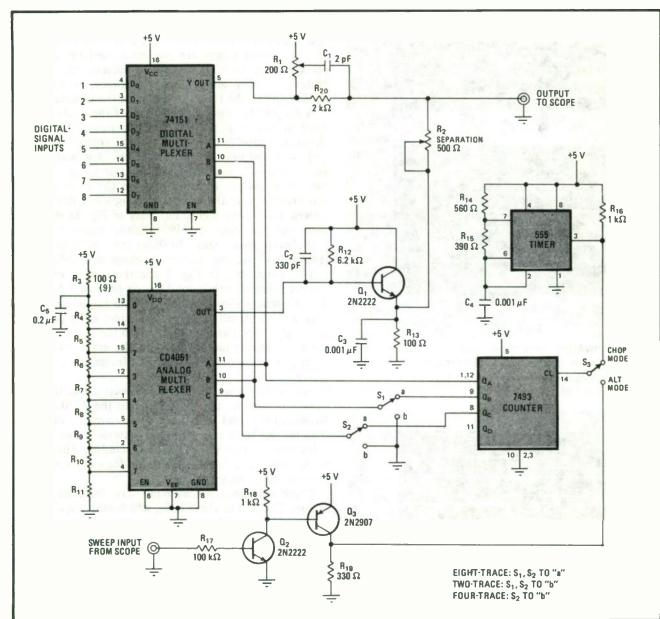

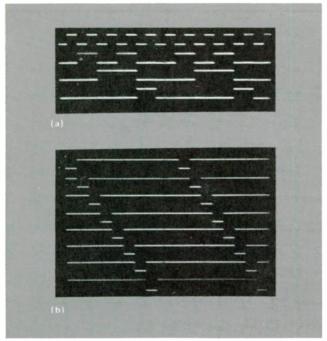

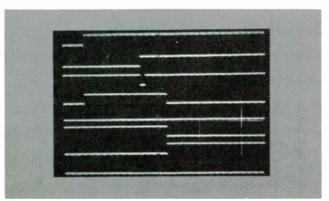

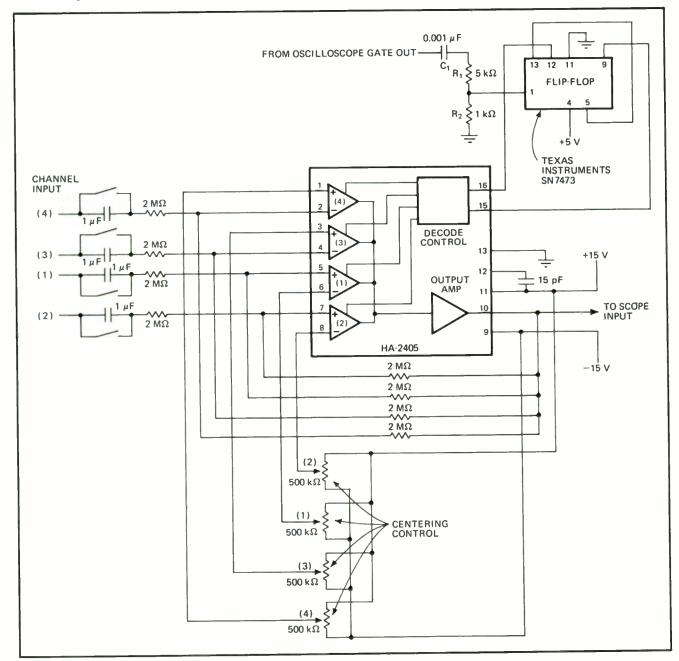

- 117 Scope display of eight signals helps debug sequential logic

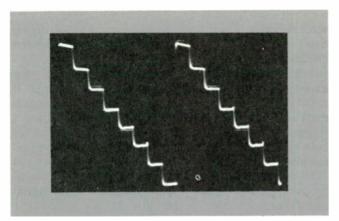

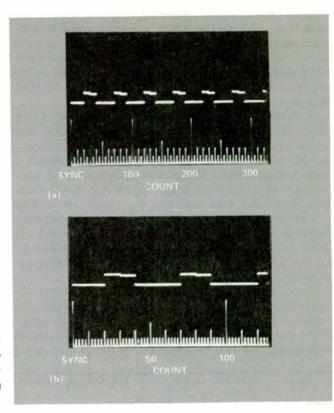

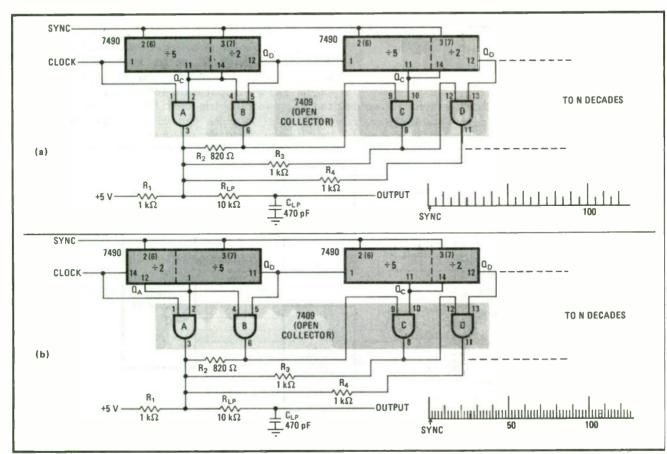

- 119 Chopping mode improves multiple-trace display

- 121 Graduated-scale generator calibrates data display

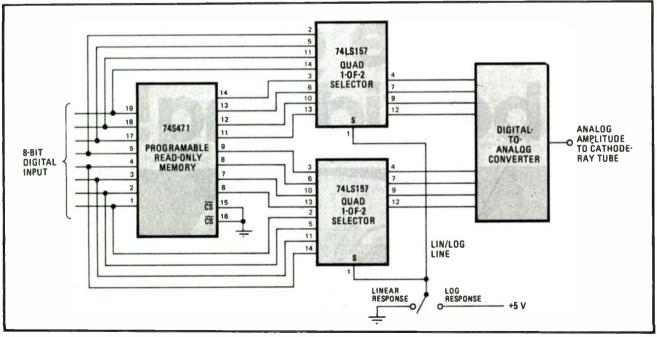

- 122 PROM provides linear or logarithmic display

- 123 Converter for oscilloscope provides four-channel displays

#### 17. Encoders and decoders

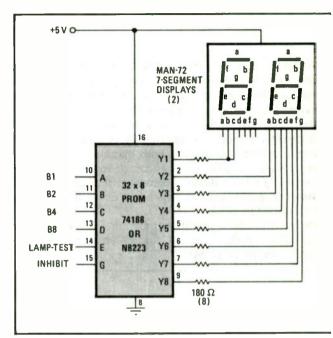

- 125 PROM converts binary code to drive 11/2-digit display

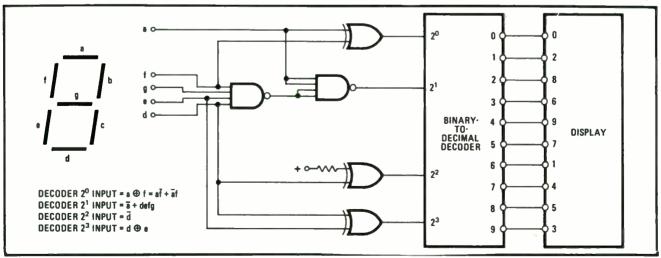

- 126 Converter changes 7-segment output to decimal or BCD

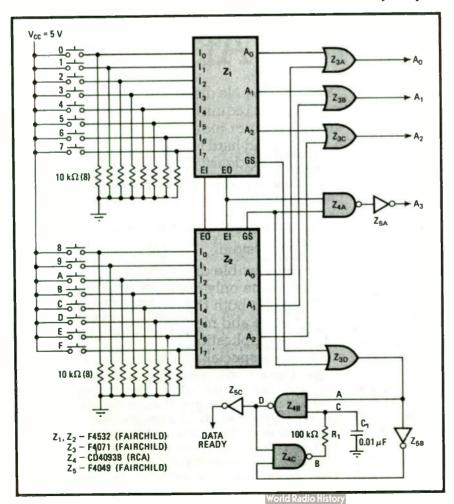

- 127 Hexadecimal encoder debounces keyboard

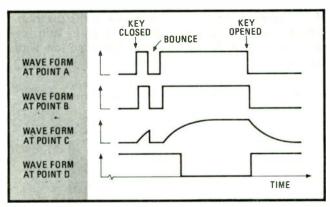

- 128 Providing a decimal output for a calculator chip

- 129 Gray-code generator avoids output glitches

- 130 IC trio converts 7-segment code to decimal

#### 18. Filters

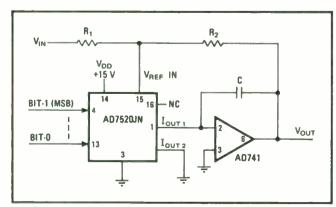

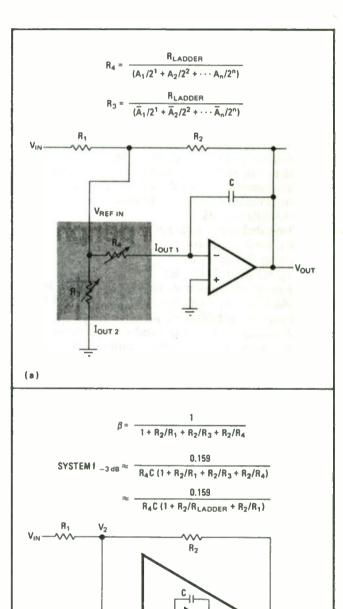

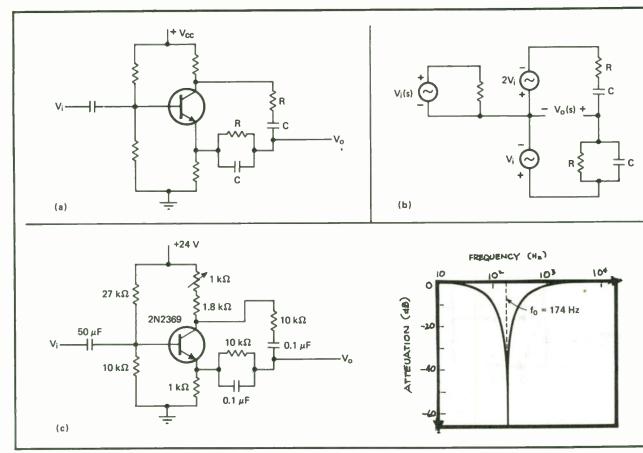

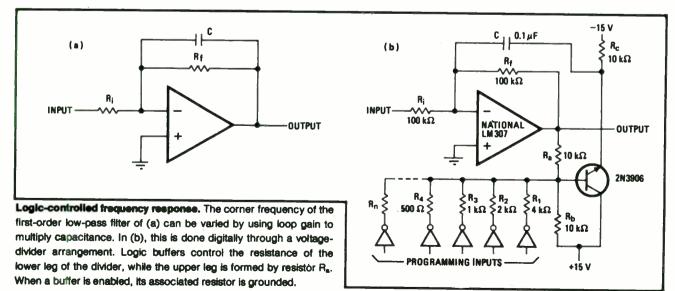

- 131 Digital-to-analog converter controls active filter

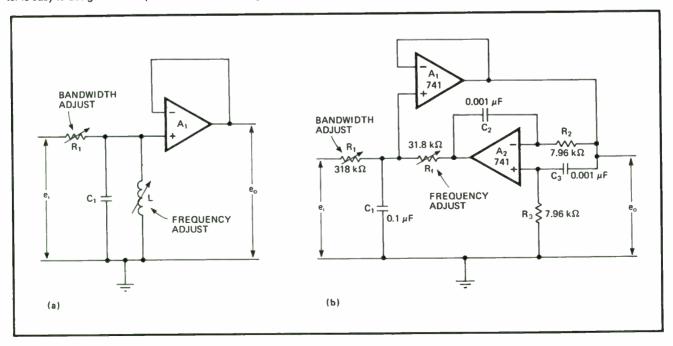

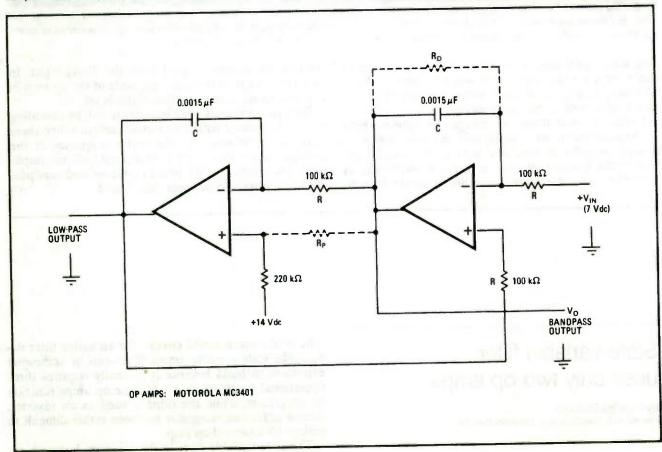

- 132 Active filter has separate band and frequency controls

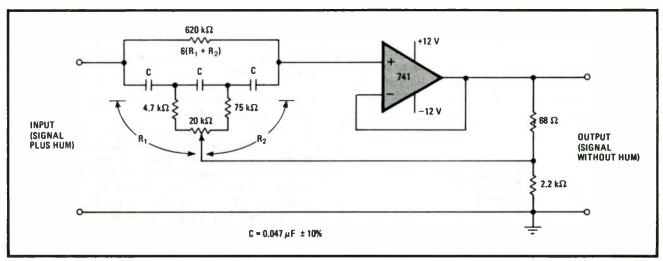

- 133 Wien bridge in notch filter gives 50 dB rejection

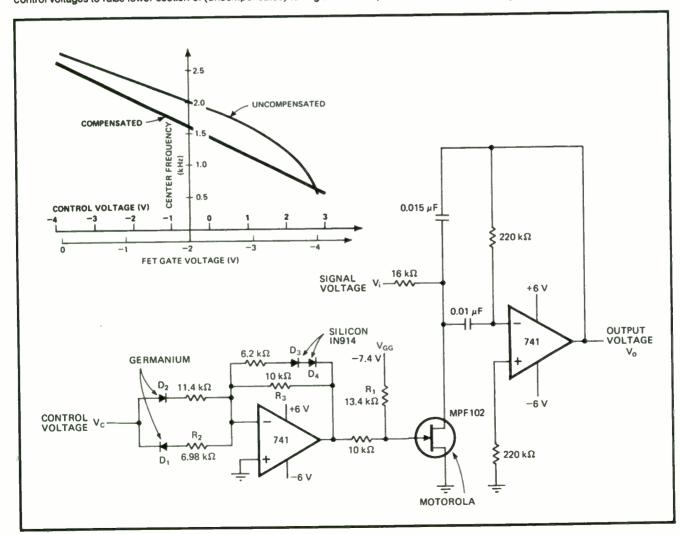

- 134 Voltage-tuned filter varies center frequency linearly

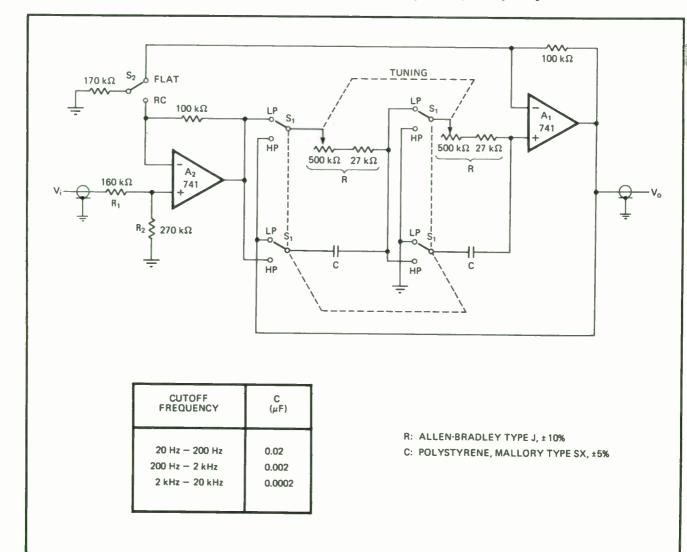

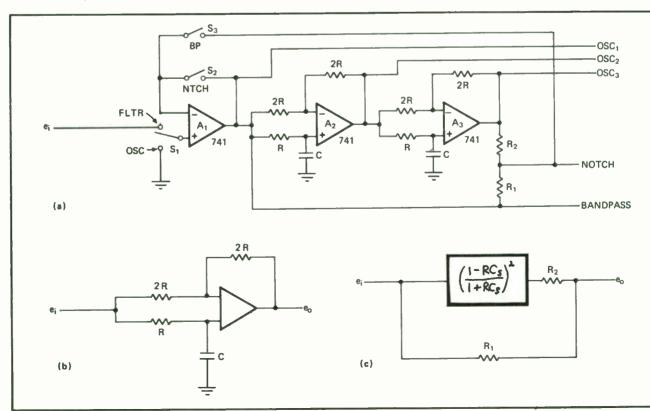

- 135 Tunable active filter has switchable response

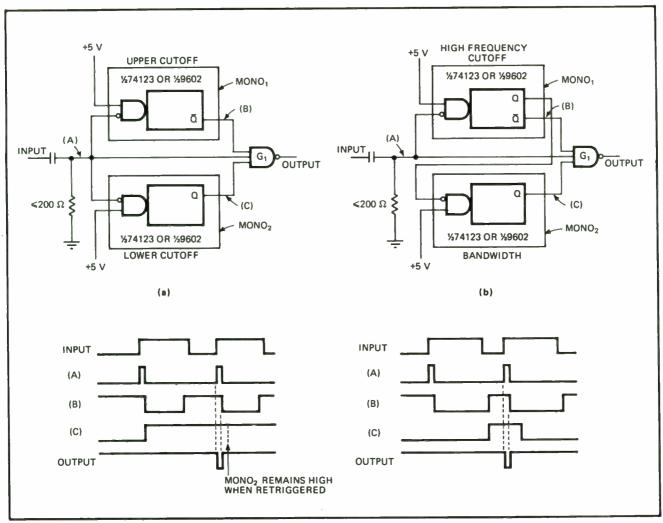

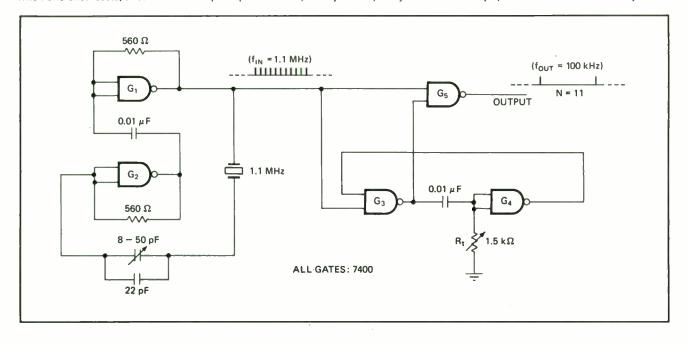

- 136 Two-IC digital filter varies passband easily

- 137 Analog filter can be programed digitally

- 138 Narrowband digital filter achieves high Qs

- 139 Tunable notch filter suppresses hum

- 140 Nonlinear low-pass filter rejects impulse signals

- 141 State-variable filter uses only two op amps

- 143 Three-mode network is filter or oscillator

#### 19. Frequency dividers

- 145 TTL decade counter divides pulse train by any integer

- 146 Control one-shot divides frequency by up to 30

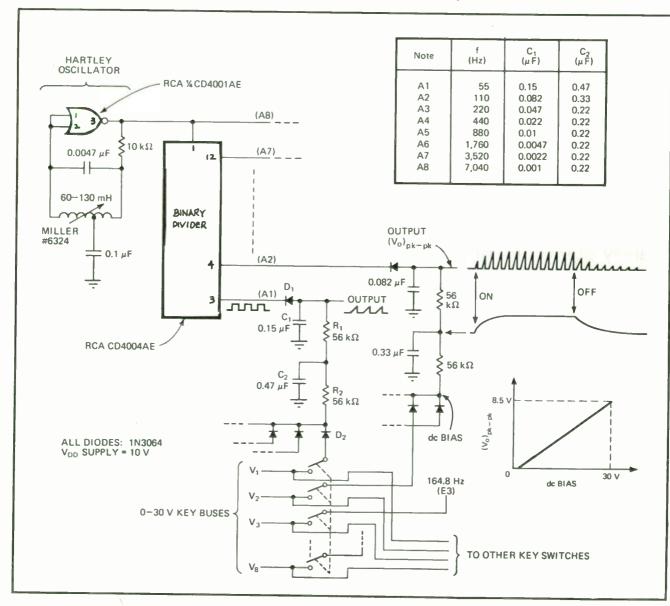

- 146 Binary division produces harmonic frequencies

#### 20. Frequency doublers

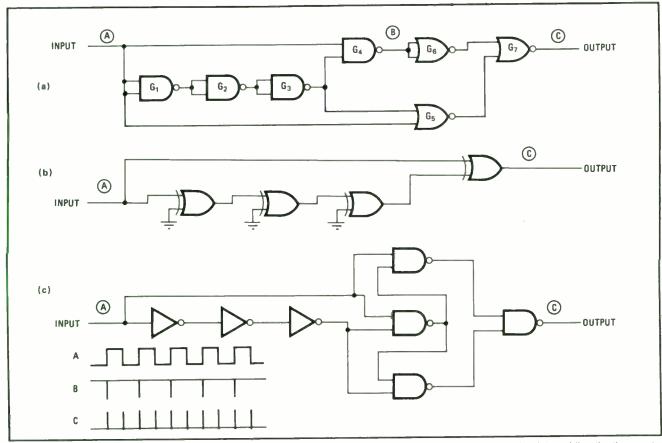

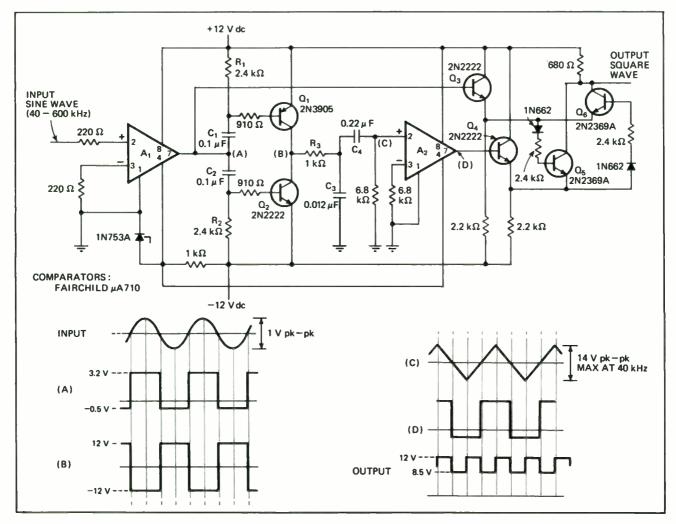

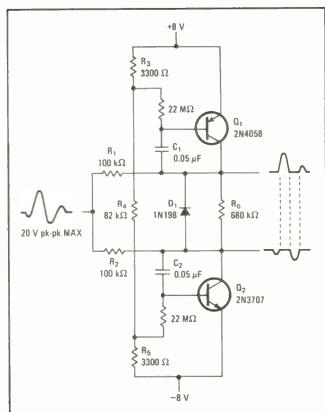

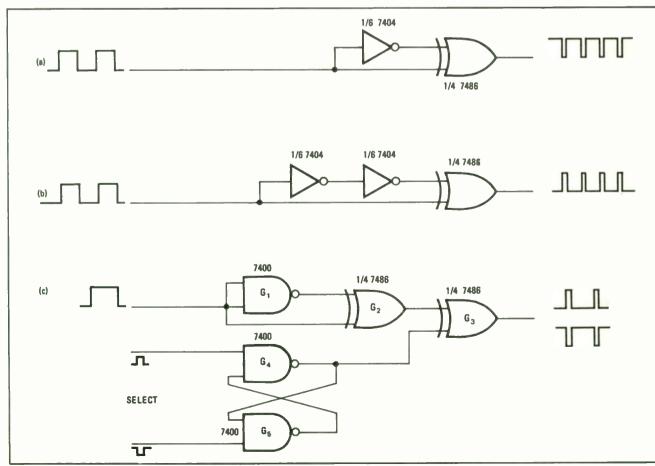

- 148 Frequency doubler accepts any waveshape

- 149 Pulse-frequency doubler requires no adjustment

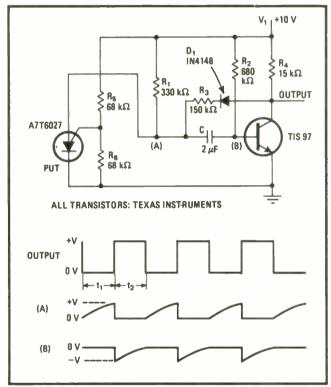

- 150 Switched frequency doubler provides multiple outputs

- 151 Frequency-doubler produces square-wave output

#### 21. Frequency synthesizers

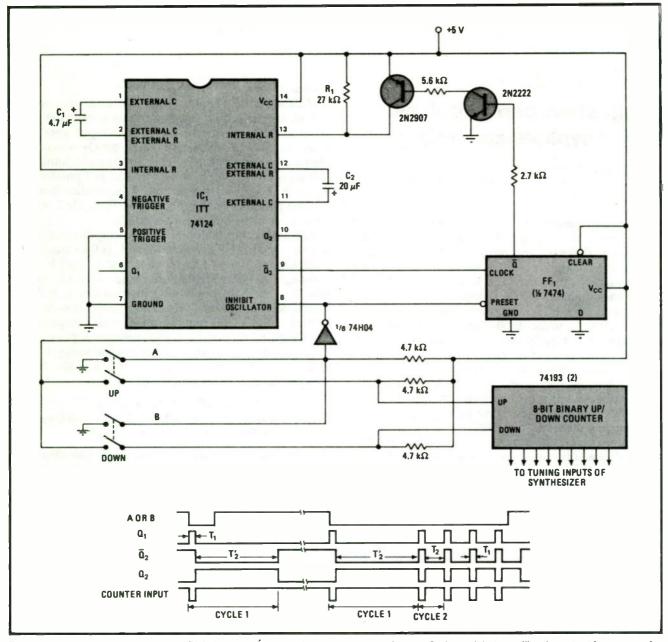

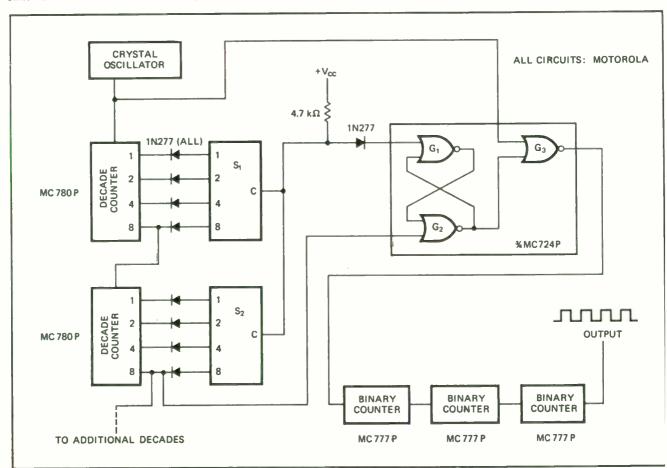

- 153 Long/short-period pulses speed synthesizer setting

- 155 Thumbwheel switches set synthesizer output frequency

#### 22. Function generators

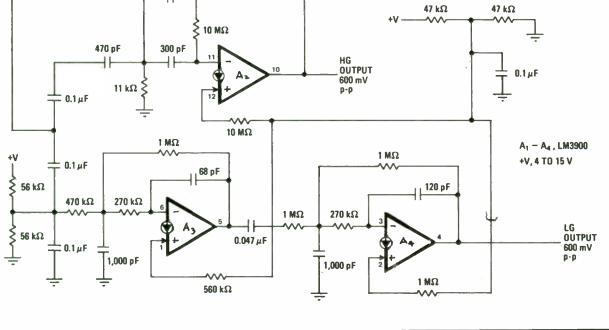

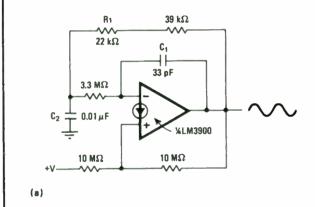

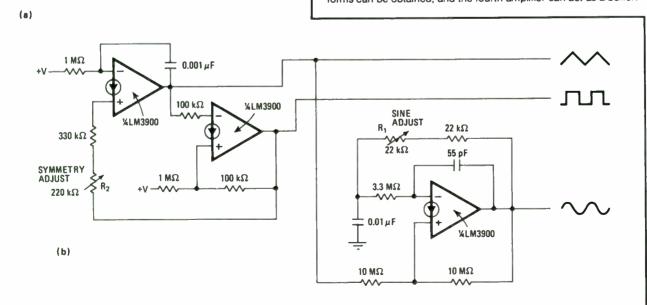

- 156 Norton quad amplifier can be a low-cost function generator

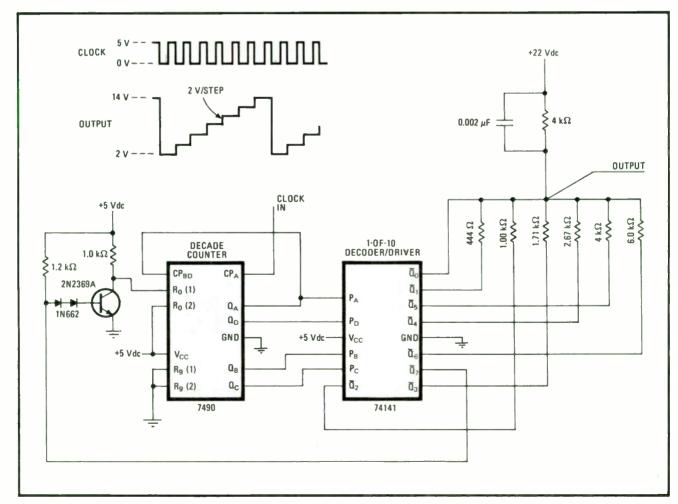

- 157 Counter and decoder/driver produces staircase voltage

- 158 Synchronous ramp generator maintains output linearity

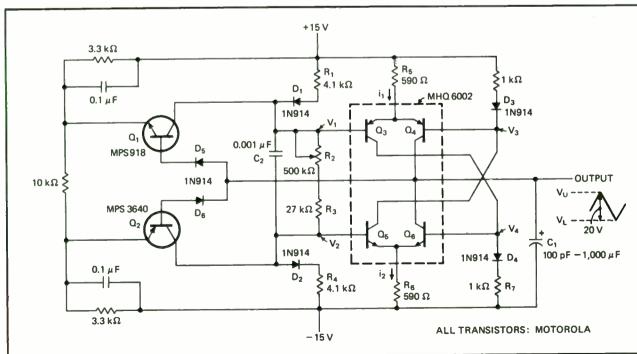

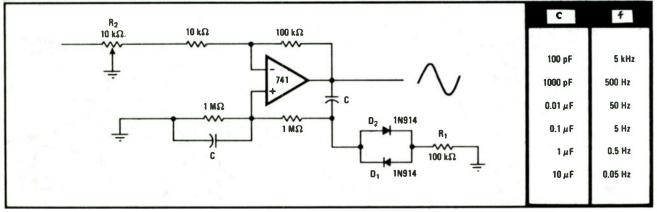

- 159 Triangular-wave generator spans eight decades

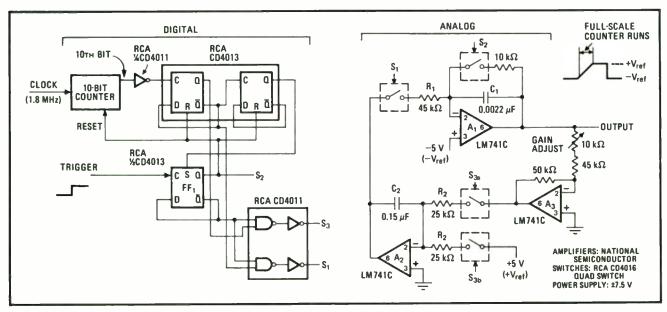

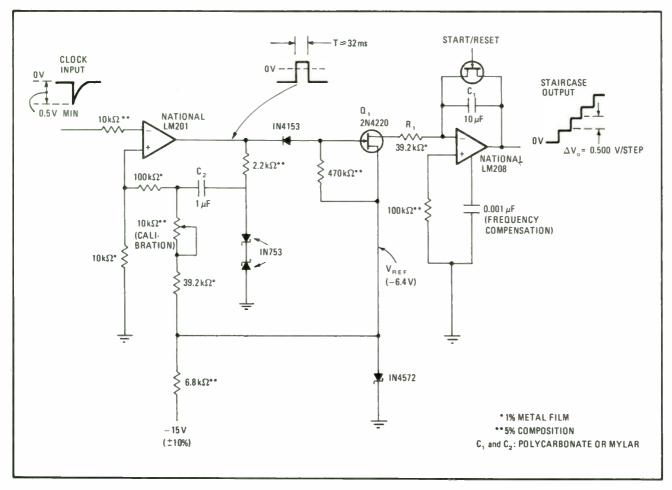

- 160 Staircase generator resists output drift

- 161 Generating tone bursts with only two IC timers

- 162 Waveform is synthesized from linear segments

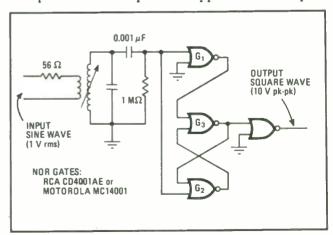

- 163 Link-coupled tank circuit steps up C-MOS drive voltage

- 164 Square-wave generator stresses frequency stability

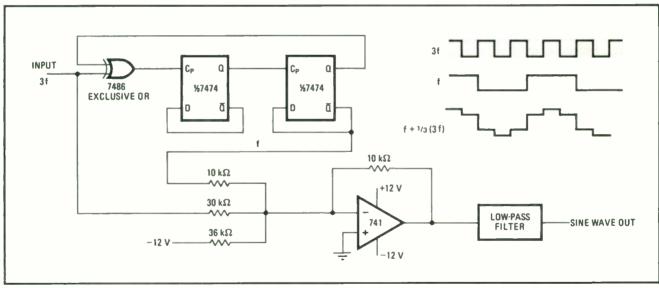

- 165 Digital pulses synthesize audio sine waves

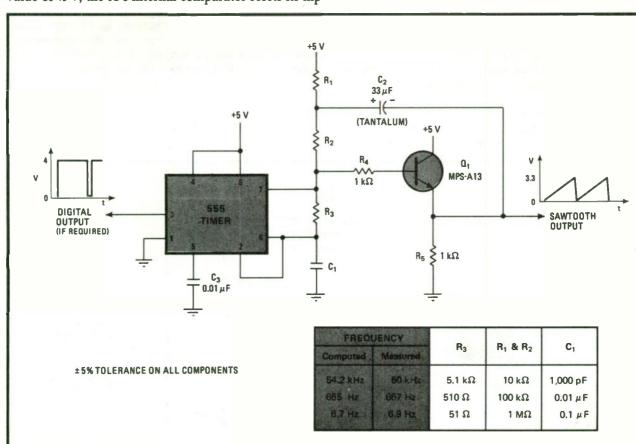

- 166 Timer IC stabilizes sawtooth generator

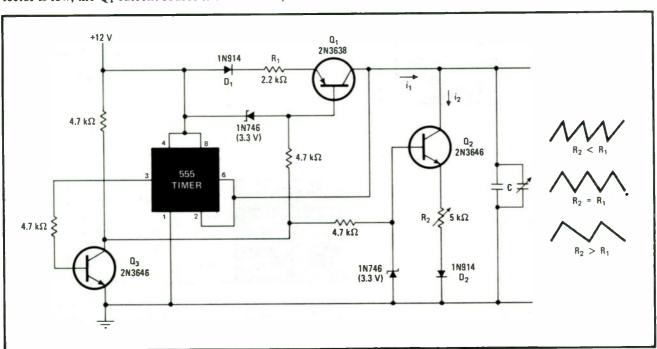

- 167 Triangular waves from 555 have adjustable symmetry

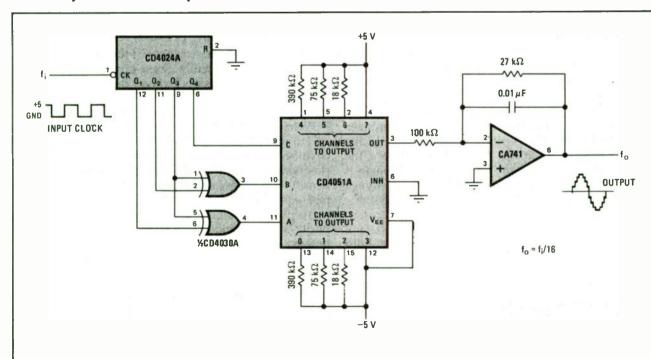

- 169 Frequency divider plus op amp approximates sine wave

#### 23. Instrument circuits

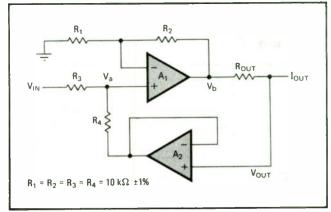

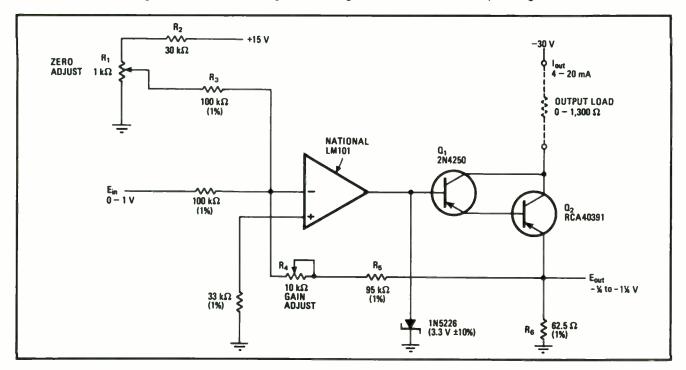

- 170 Voltage-to-current converter for process-control systems

- 171 Data averager for panel meter operates from meter's cloc

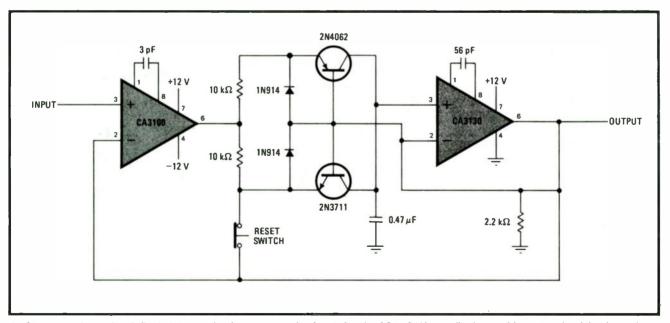

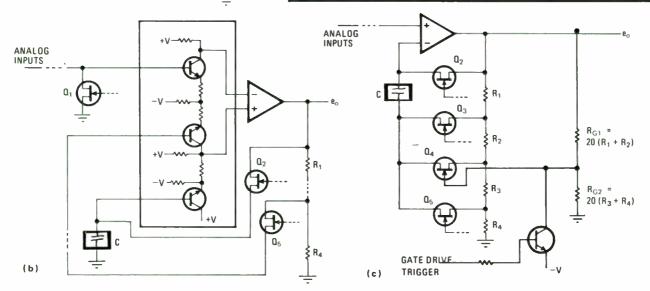

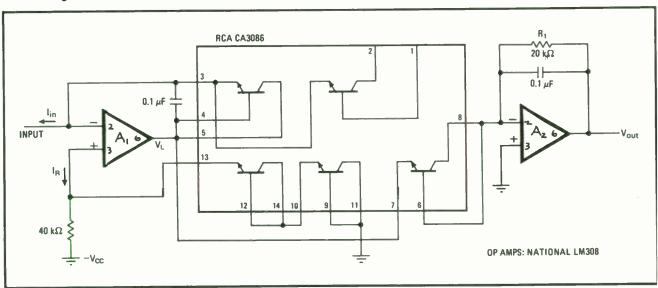

- 172 Capacitor corrects drift for analog data amplifier

- 173 Low-drift ICs form instrument amplifier

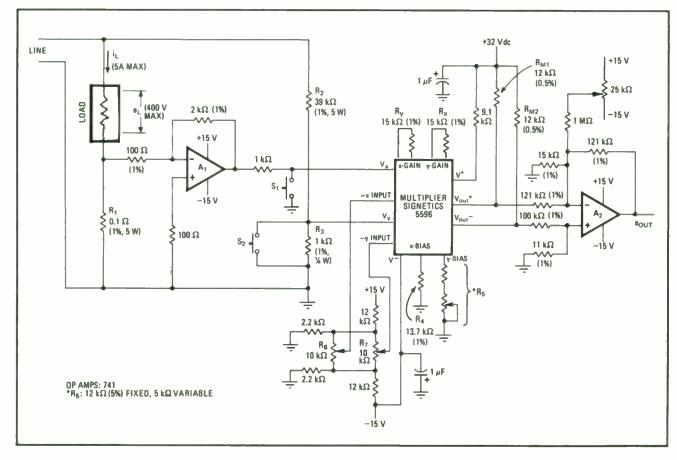

- 175 Integrated multiplier simplifies wattmeter design

#### 24. Integrators

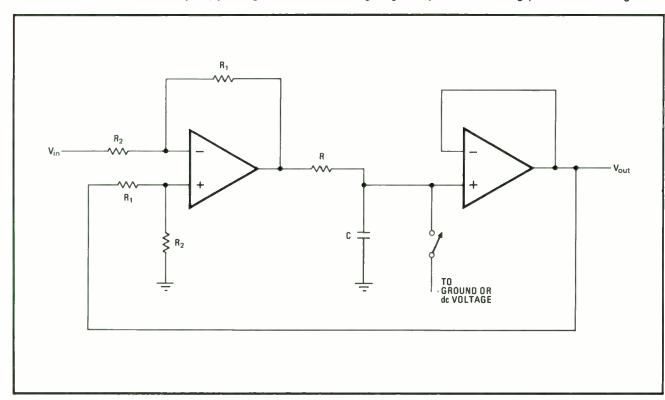

- 177 Two-amplifier integrator extends timing performance

- 178 Inverting transistor boosts integrator's time constant

- 179 Miller-effect integrators act as signal separator

- 179 Precision integrator resets as it samples

#### 25. Inverters

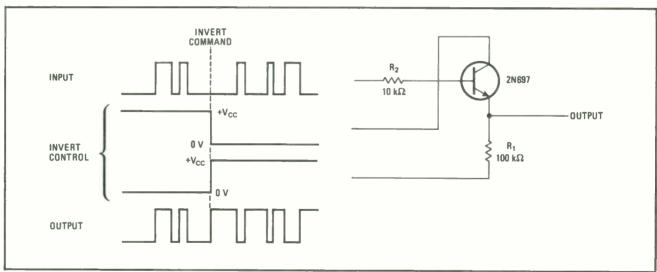

- 181 Single bipolar transistor inverts pulses on command

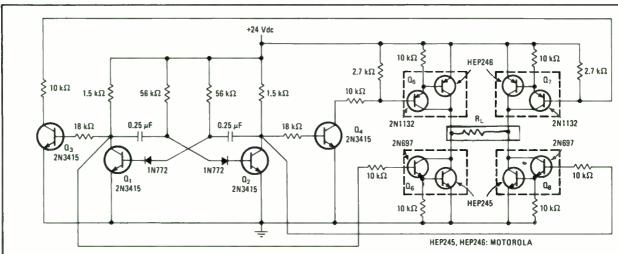

- 182 Digital command inverts signal

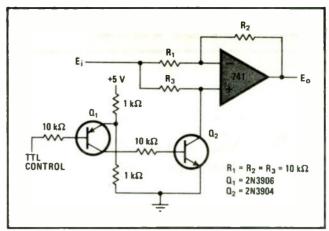

- 183 Transistor array cuts cost of algebraic inversion

#### 26. Limiters

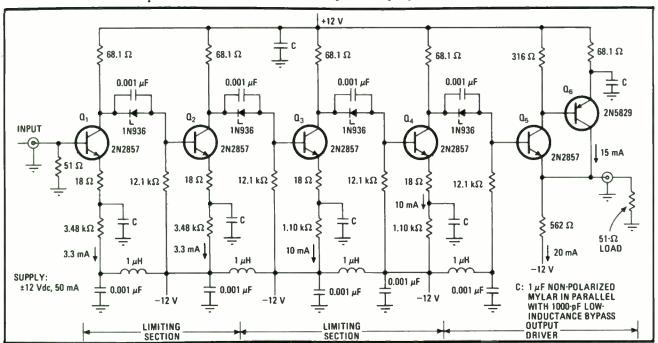

- 184 Broadband cutoff limiter is phase-transparent

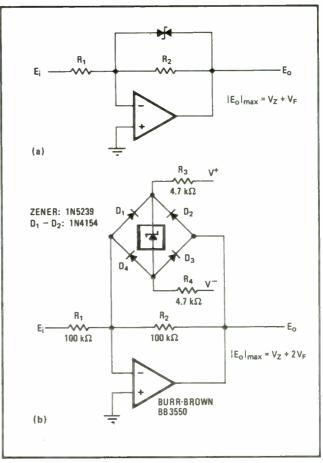

- 185 Linear signal limiting with feedback multiplier

#### 27. Logic circuits

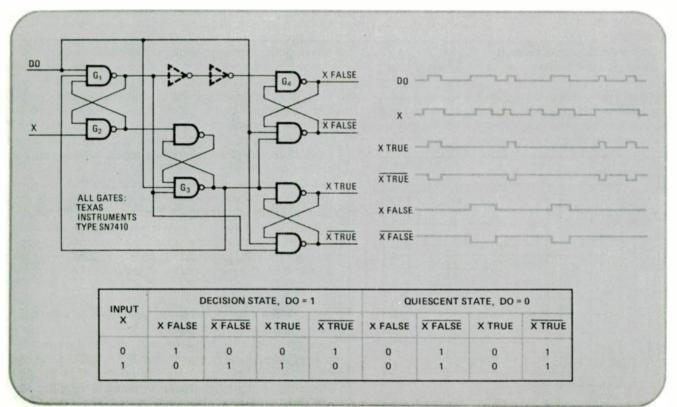

- 186 Unclocked logic element makes quick decisions

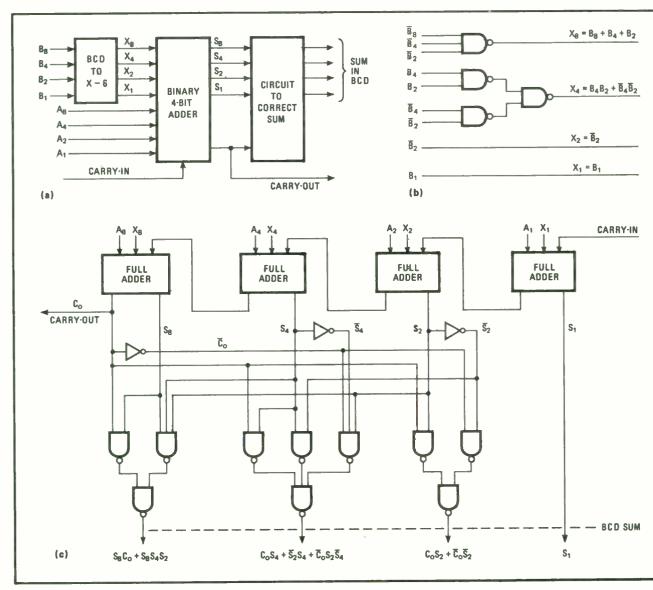

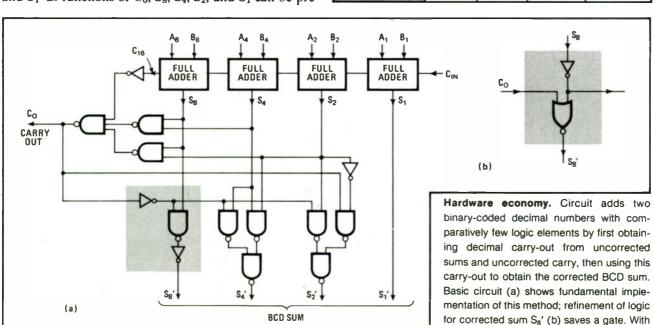

- 187 Simplifying sum-correction logic for adding two BCD numbers

- 188 Circuit adds BCD numbers faster with less hardware

- 189 Common-gate, common-base circuits shift voltage levels

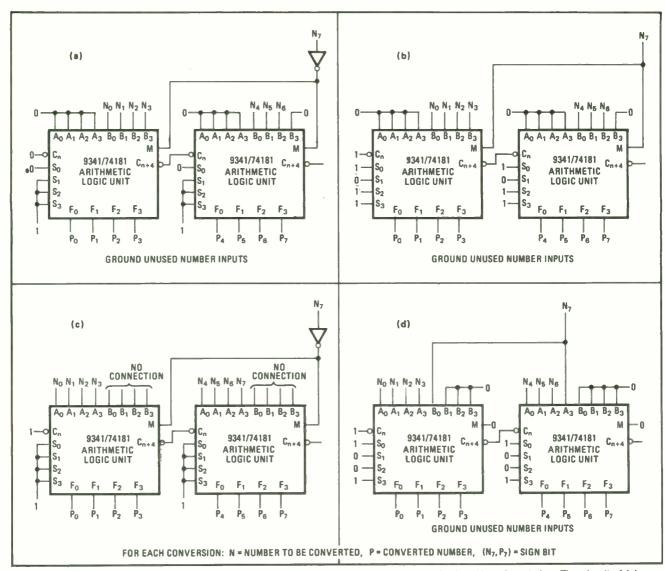

- 190 IC logic units simplify binary number conversion

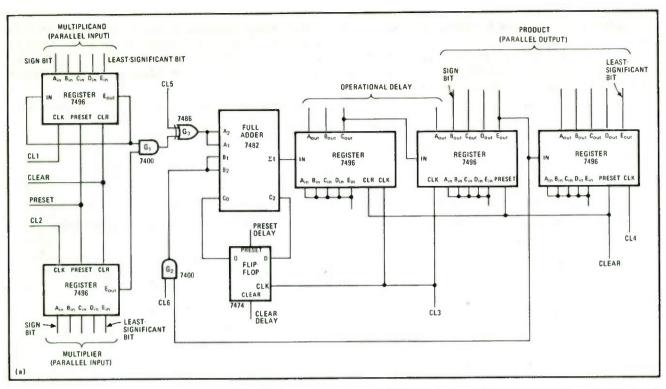

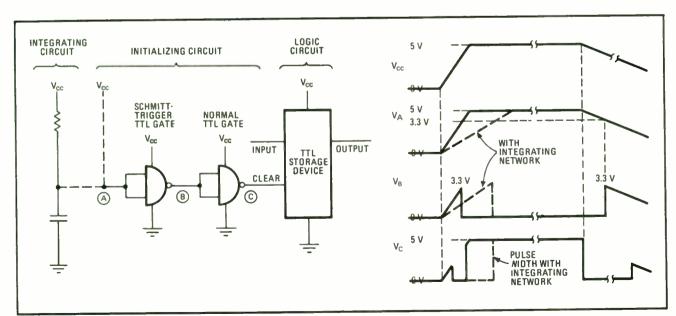

- 191 Serial digital multiplier handles two five-bit numbers

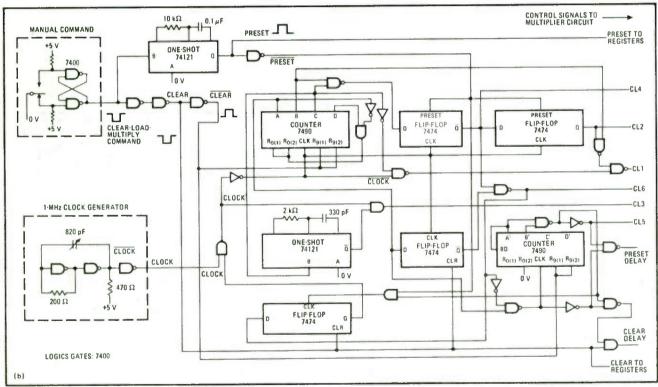

- 193 Gate threshold difference produces initializing pulse

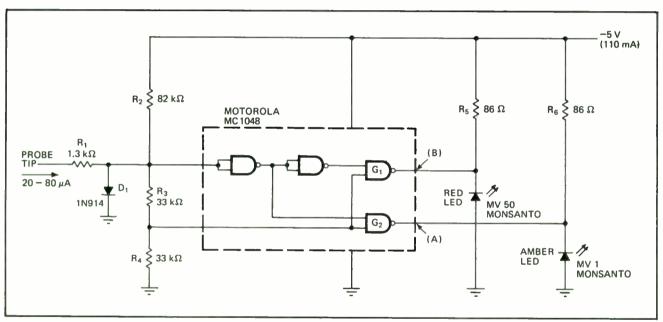

- 194 Logic probe with LED display checks ECL circuits

- 194 Simple gating circuit monitors real-time inputs

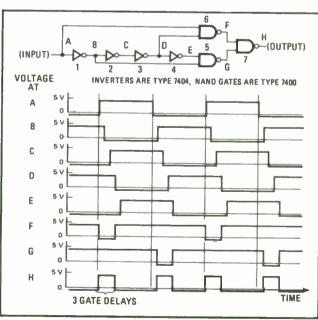

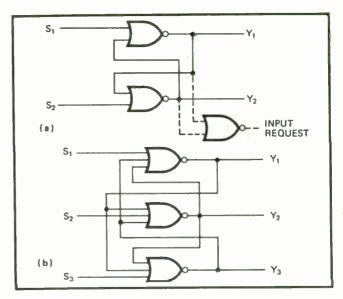

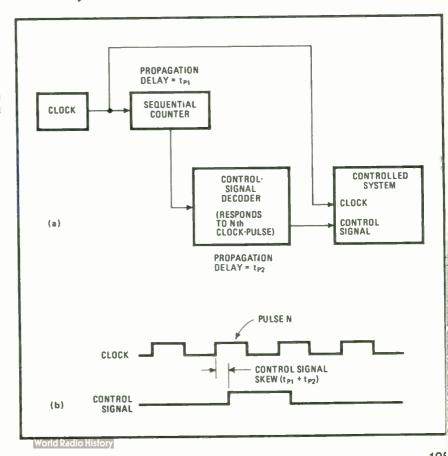

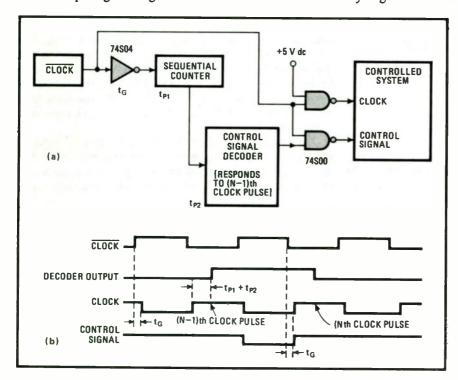

- 195 NAND gates and inverter synchronize control signal

#### 28. Memory circuits

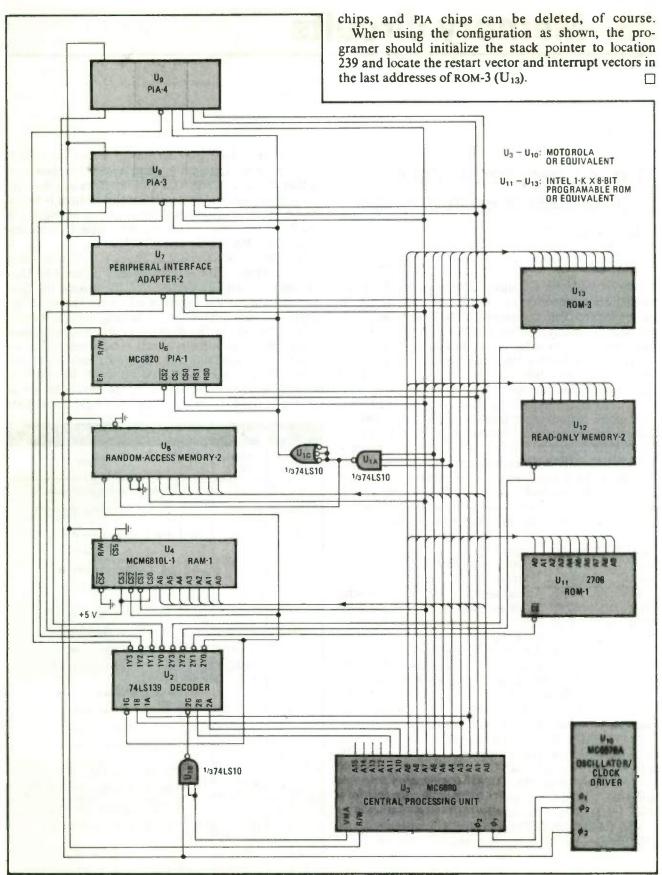

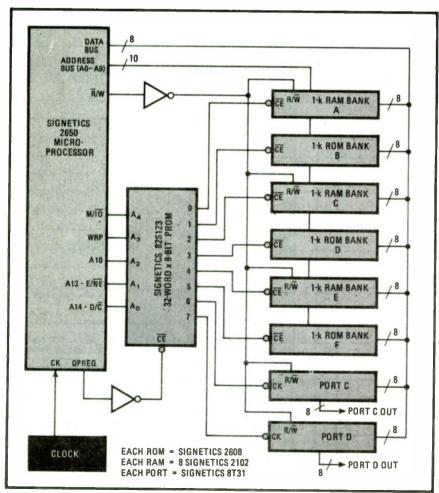

197 Memory, peripherals share microprocessor address range

iv

- 199 Feedback latch reduces memory recovery time

- 200 Register-addressing system accesses within nanoseconds

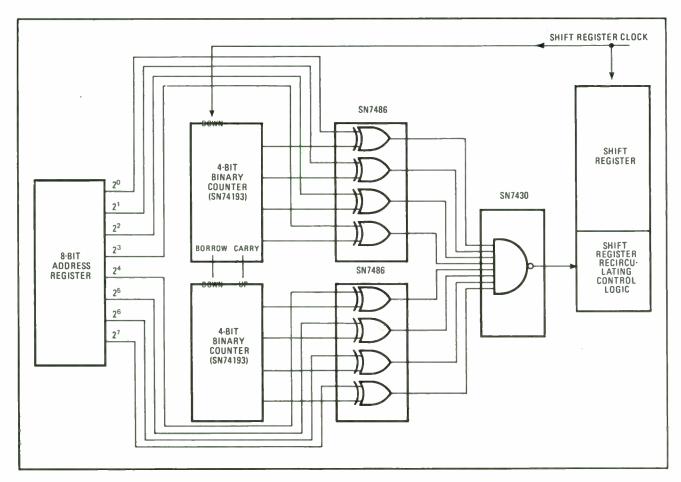

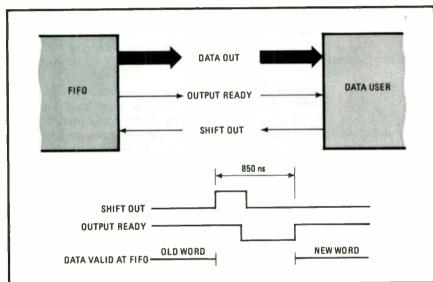

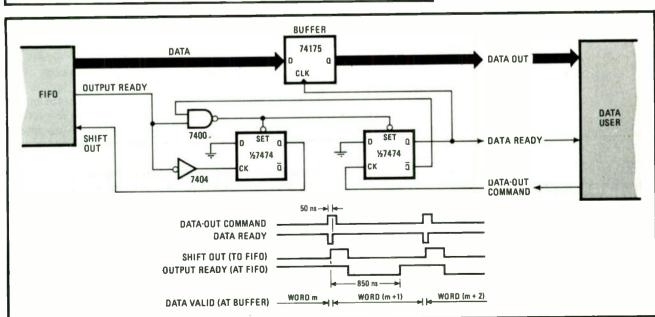

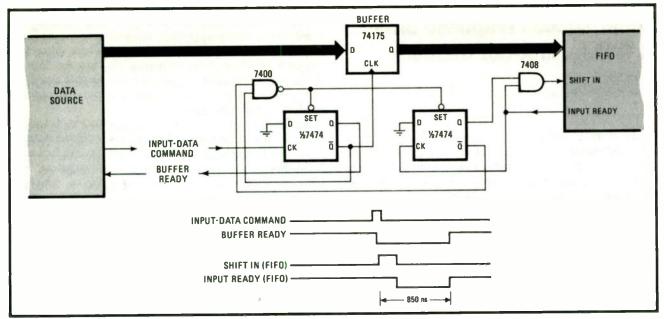

- 201 Buffer speeds response time of first-in, first-out memory

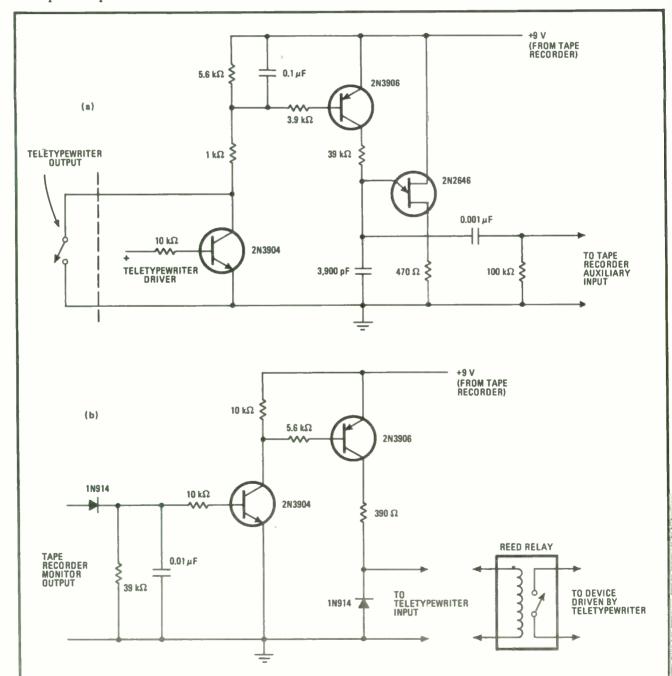

- 202 Storing computer data with a cassette recorder

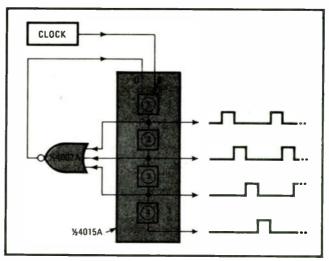

- 204 One NOR gate starts shift-register loop

#### 29. Microprocessors

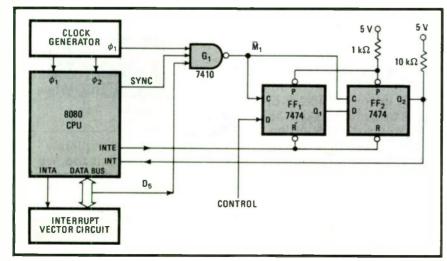

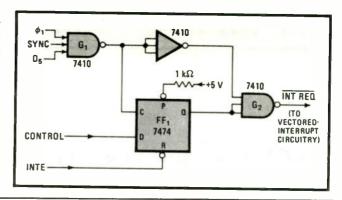

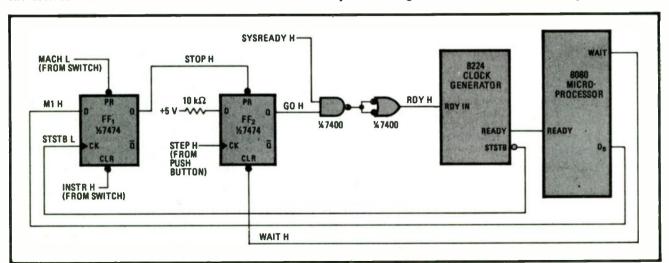

- 205 Hardware helps in tracing microprocessor program

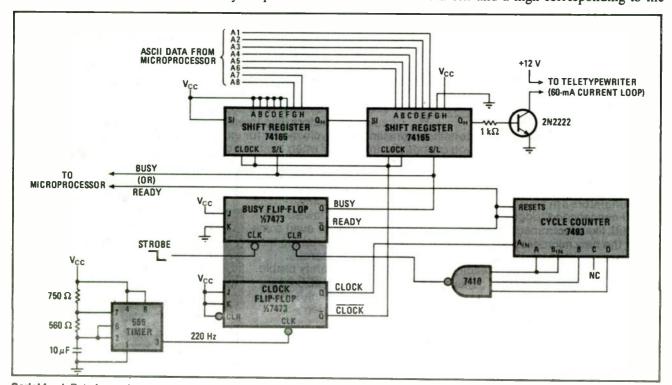

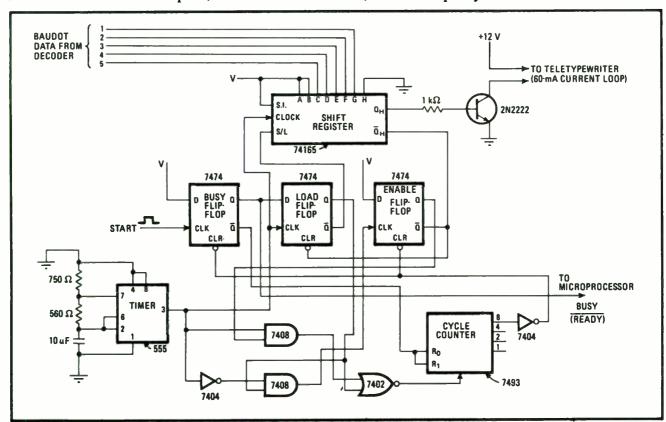

- 206 Converter lets processor drive teletypewriter

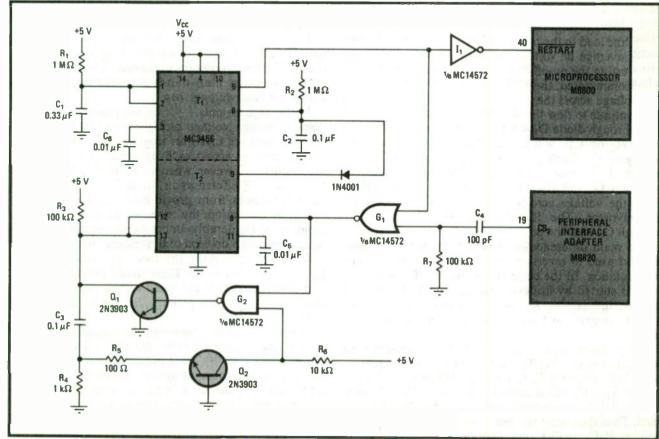

- 207 Dual-555-timer circuit restarts microprocessor

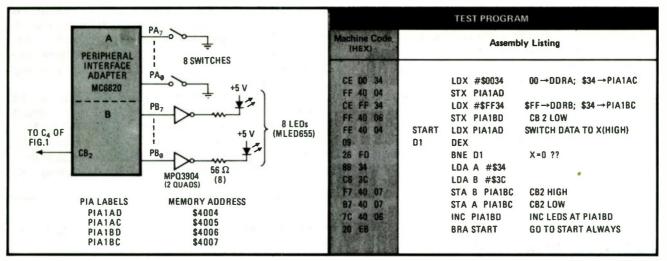

- 209 Interfacing a teletypewriter with an IC microprocessor

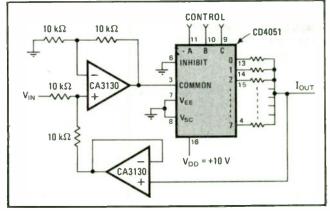

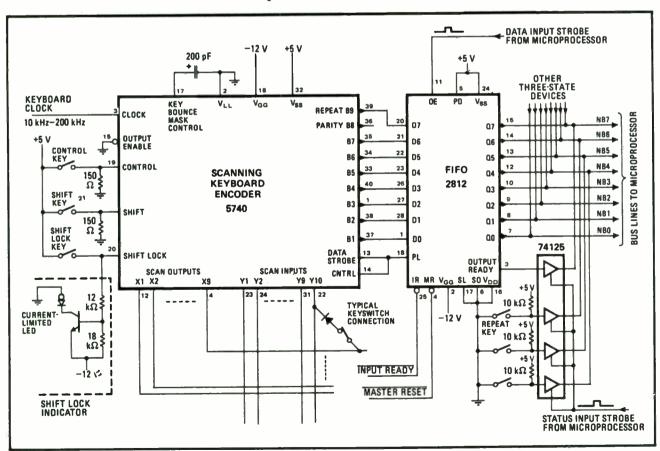

- 210 ICs interface keyboard to microprocessor

- 211 PROM decoder replaces chip-enabling logic

- 214 Circuit steps program for 8080 debugging

#### 30. Modulators and demodulators

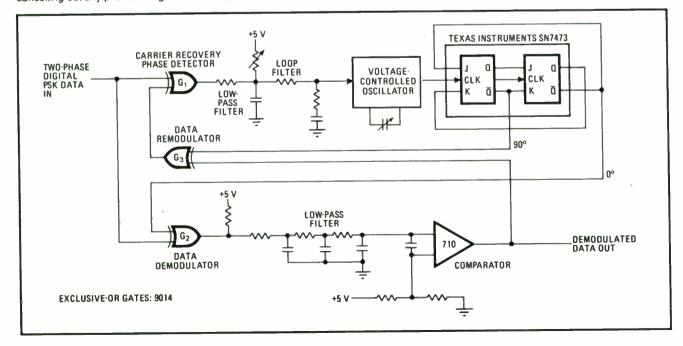

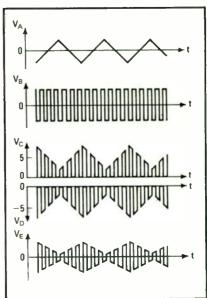

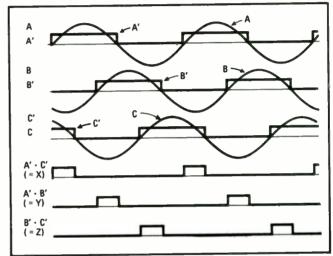

- 216 Digital demodulator for phase-shift-keyed data

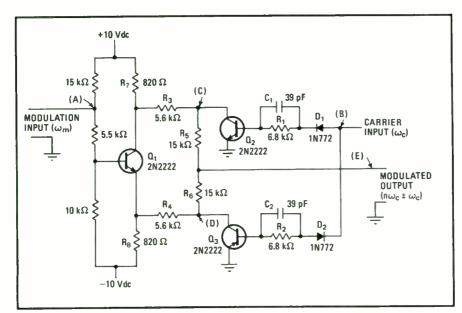

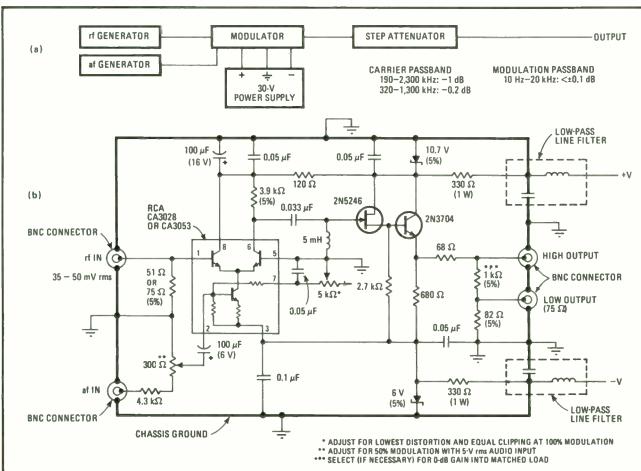

- 217 Amplitude modulator is highly linear

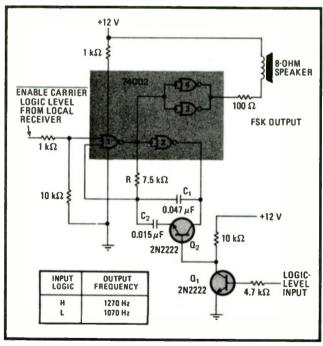

- 218 Mark/space modulator drives acoustic coupler

- 219 Low-distortion modulator tests hi-fi a-m tuners

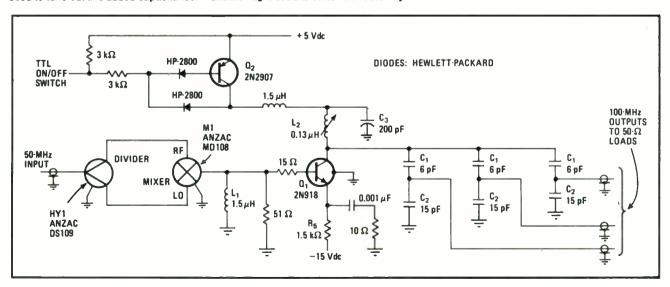

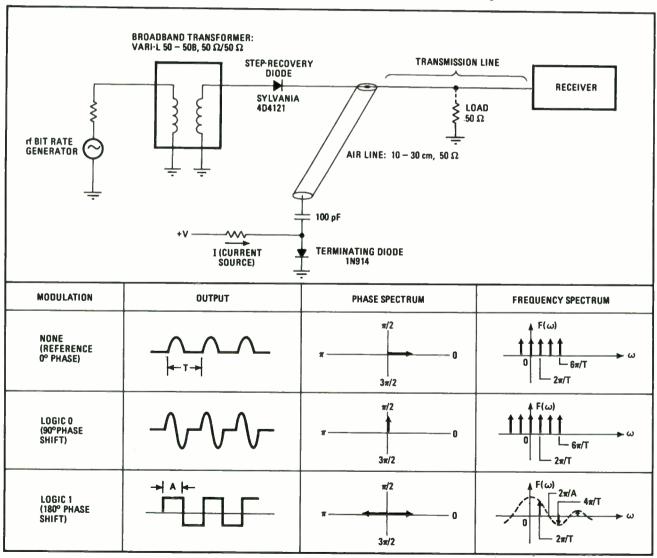

- 220 Coherent phase modulation attains data rates of 100 MHz

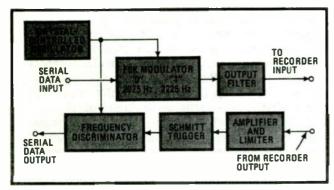

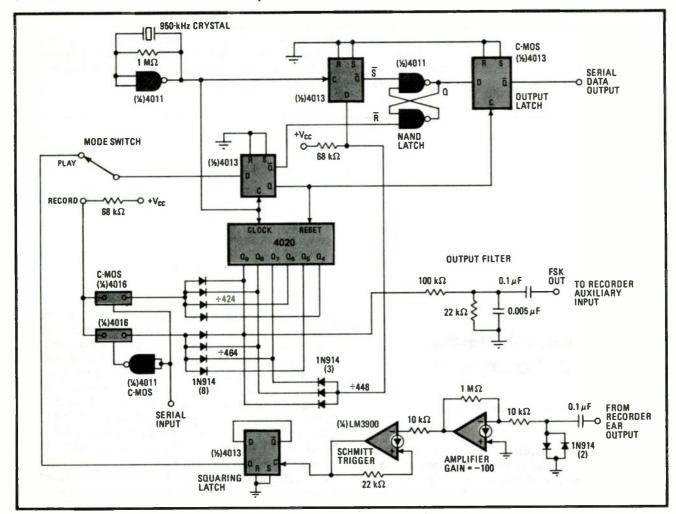

- 221 FSK modem interfaces cassette and computer

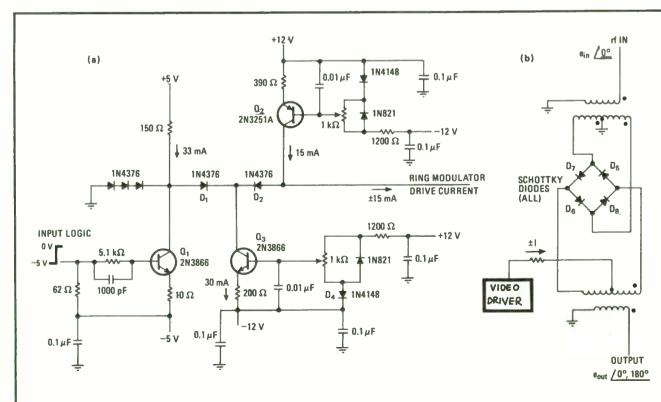

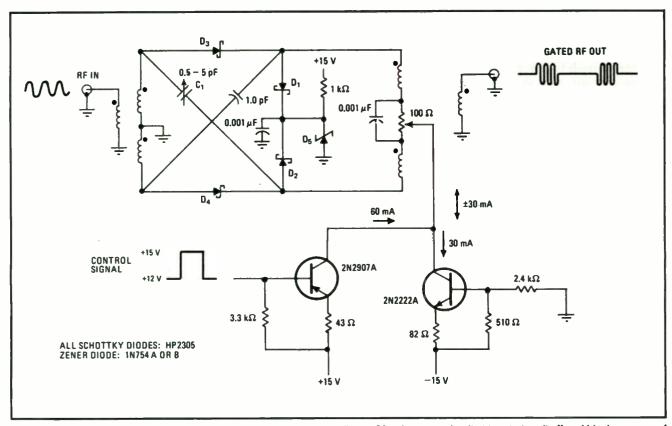

- 223 Binary rf phase modulator switches in 3 nanoseconds

- 224 Mark/space demodulator employs active filters

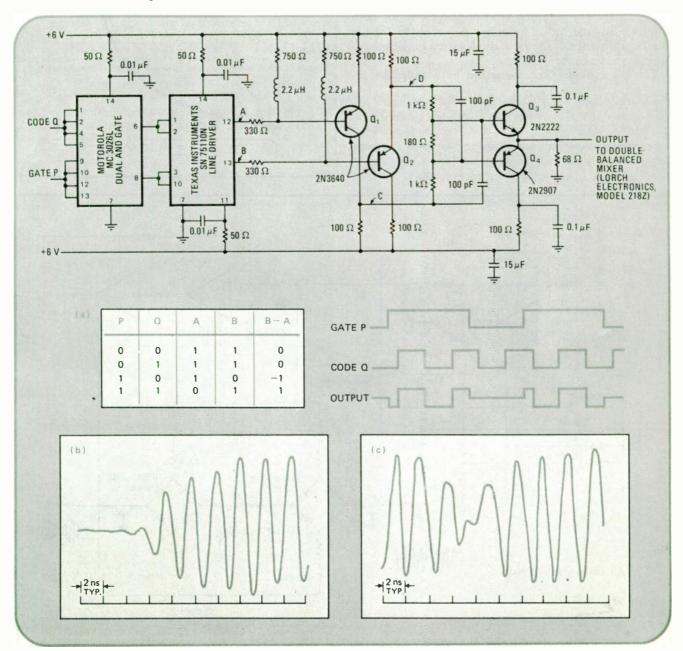

- 224 Fast-switching modulator reverses uhf signal phase

- 226 Variable-gain amplifier yields linear rf modulator

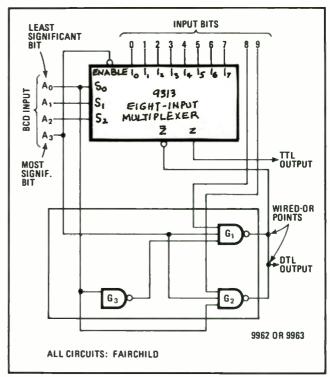

#### 31. Multiplexers

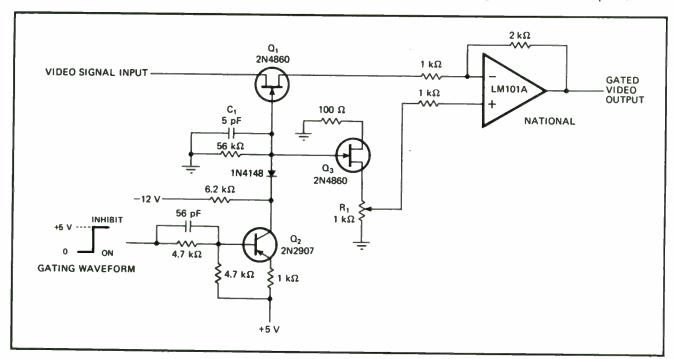

- 227 Gated MOSFET acts as multiplexing switch

- 228 Wired-OR DTL gates increase multiplexer input capacity

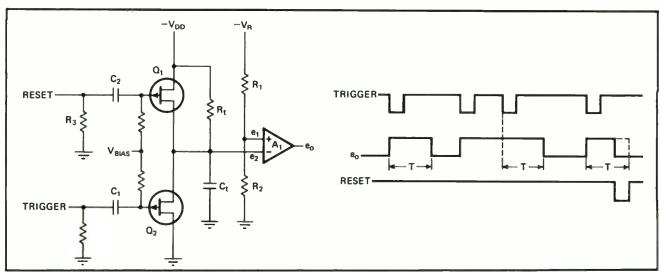

#### 32. Multivibrators

- 229 Output comparator enhances versatility of one-shot

- 230 Multivibrator clock obeys digital commands

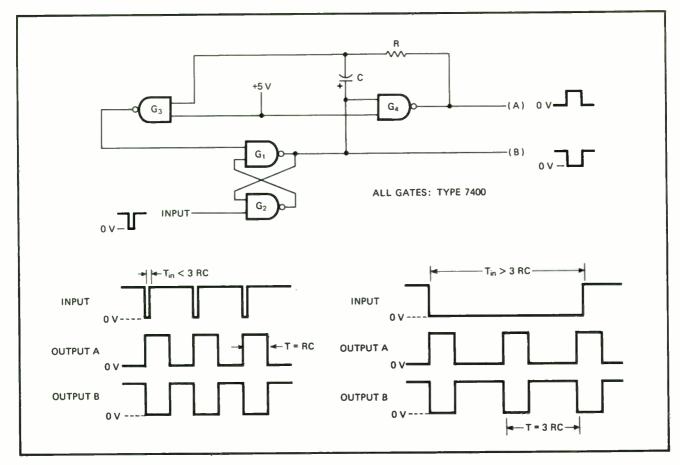

- 231 Exclusive-OR gate makes bidirectional one-shot

- 232 Double-duty multivibrator gives complementary outputs

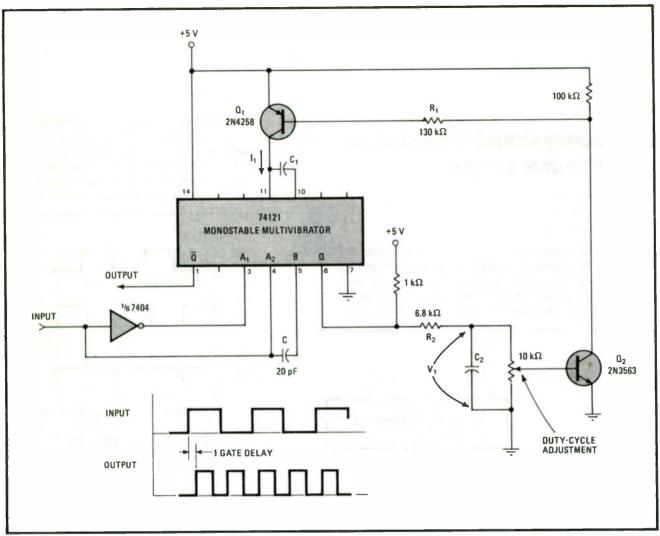

- 233 Programable monostable is immune to supply drift

- 234 Astable multivibrator needs only one capacitor

- 235 IC timer circuit yields 50% duty cycle

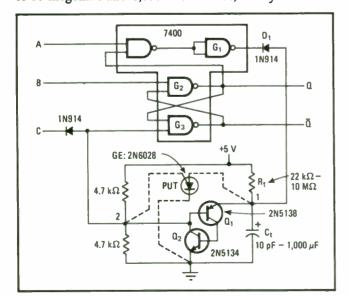

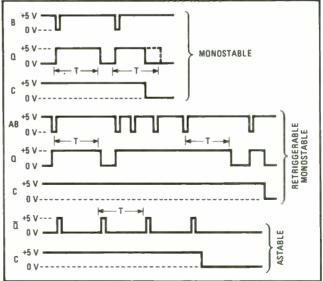

- 236 Programable multivibrator is four-in-one circuit

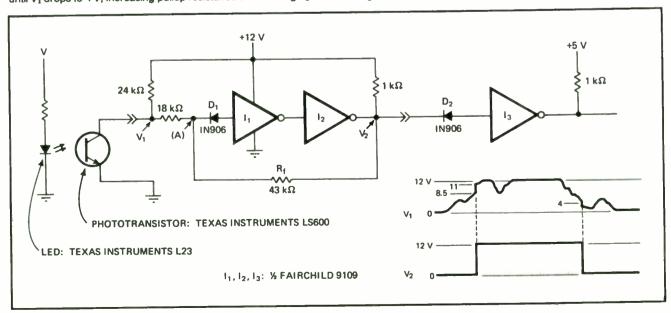

- 237 Monostable's pulse width is programable

#### 33. Operational amplifiers

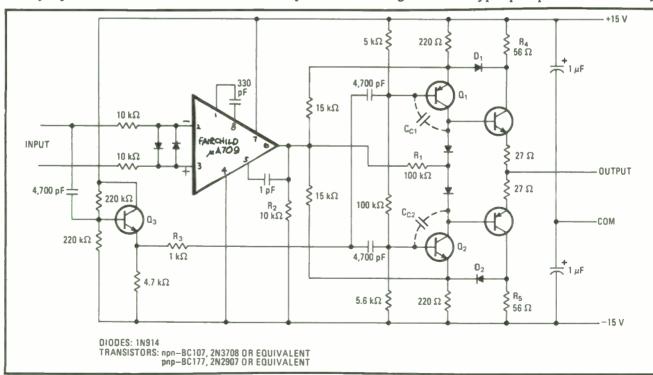

- 239 Helping a 709-type op amp to outperform itself

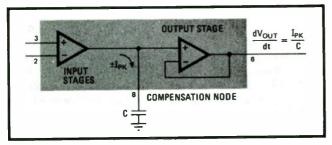

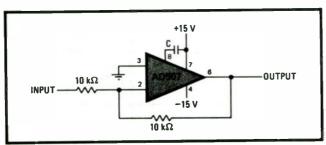

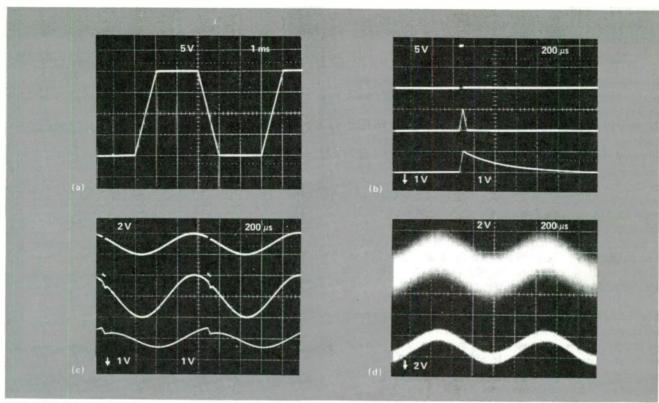

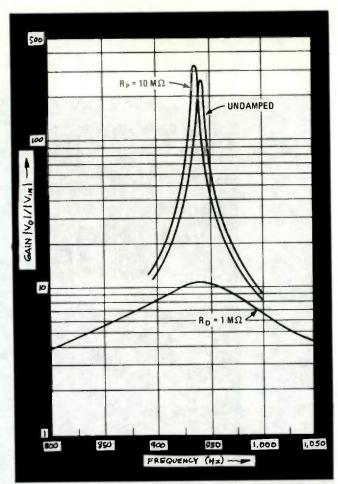

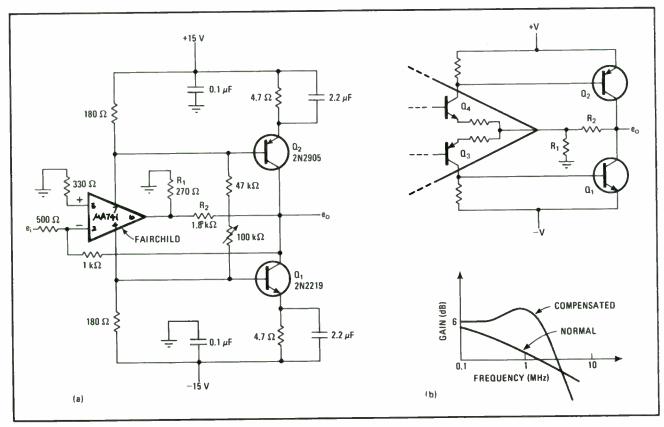

- 240 Complementary output stage improves op-amp response

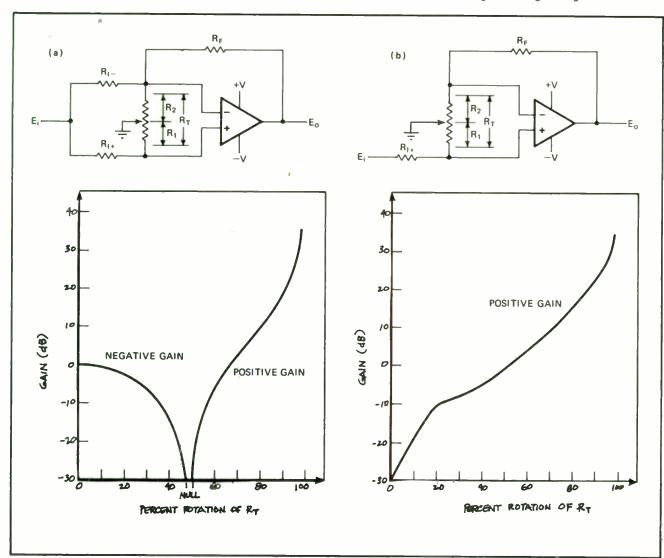

- 241 Controlling op amp gain with one potentiometer

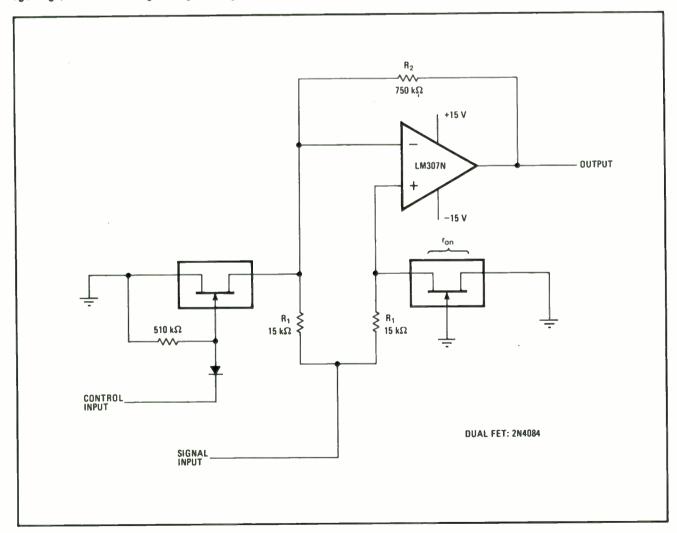

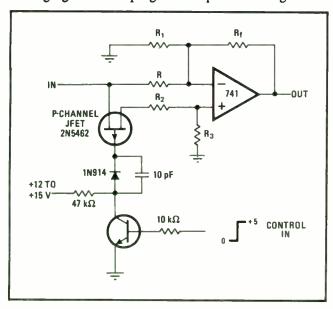

- 242 FET-controlled op amp permits wide dynamic range

- 243 Series-connected op amps null offset voltage

- 244 Continuing biasing improves clamping amplifier

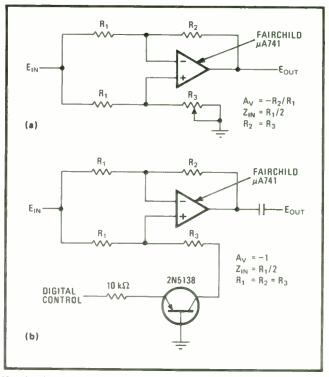

- 245 More applications for the 741-type op amp

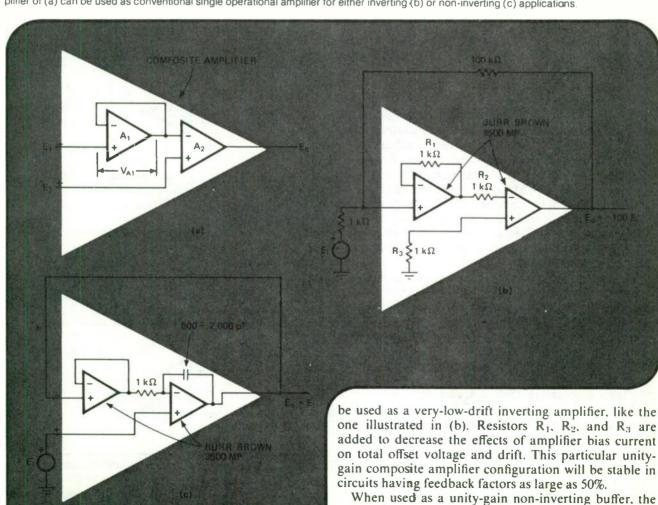

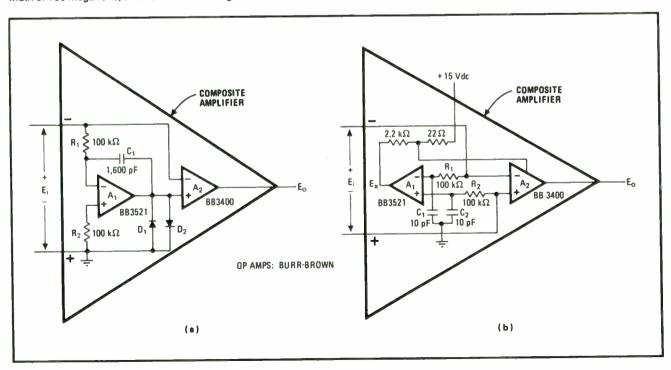

- 246 Combined op amps improve over-all amplifier response

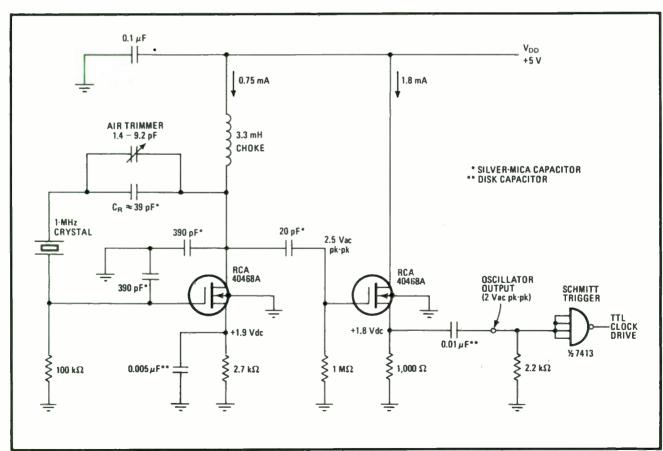

- 247 Op amps multiply RC time constants

- 249 FET programs op amp for invertible gain

#### 34. Optoelectronic circuits

- 250 Negative feedback keeps LED intensity constant

- 251 Analog voltage sensor controls LED threshold

- 252 Matched optical couplers stabilize isolation circuit

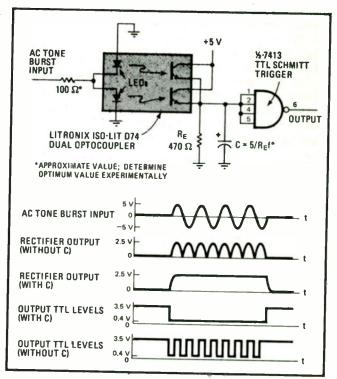

- 253 Optocoupler converts ac tone to digital logic levels

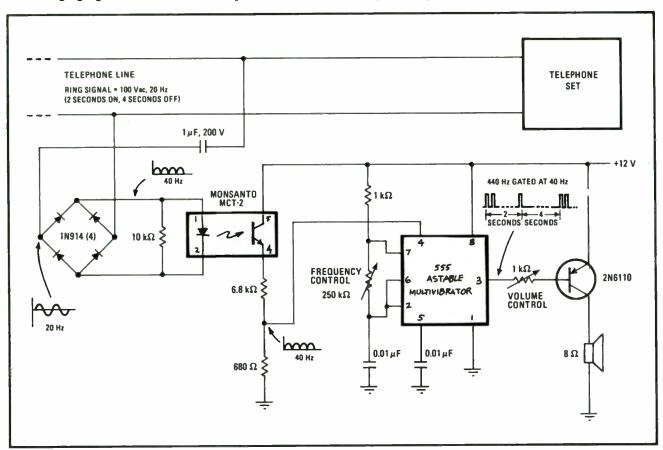

- 254 Optically coupled ringer doesn't load phone line

#### 35. Oscillators

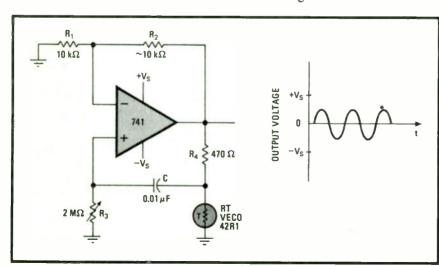

- 256 One-op-amp oscillator keeps sine-wave amplitude constant

- 257 Low-distortion oscillator uses state-variable filter

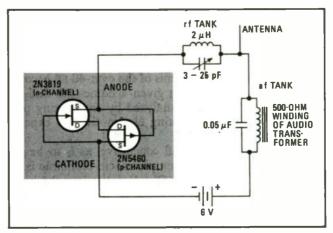

- 258 Complementary JFETS form bimode oscillator

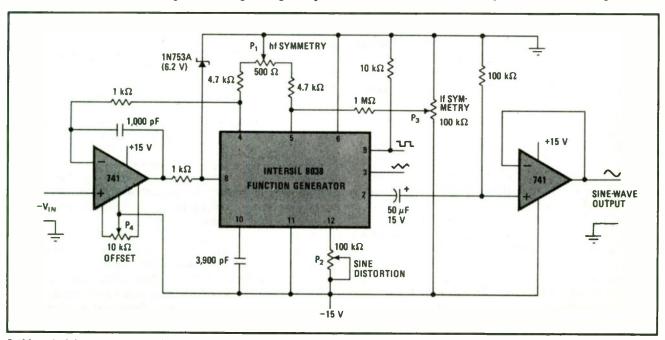

- 259 Modified function generator yields linear VCO

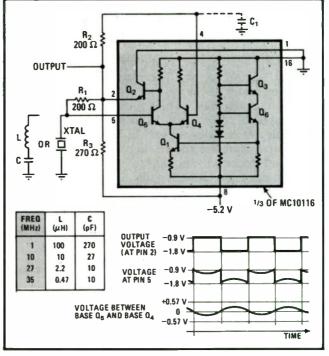

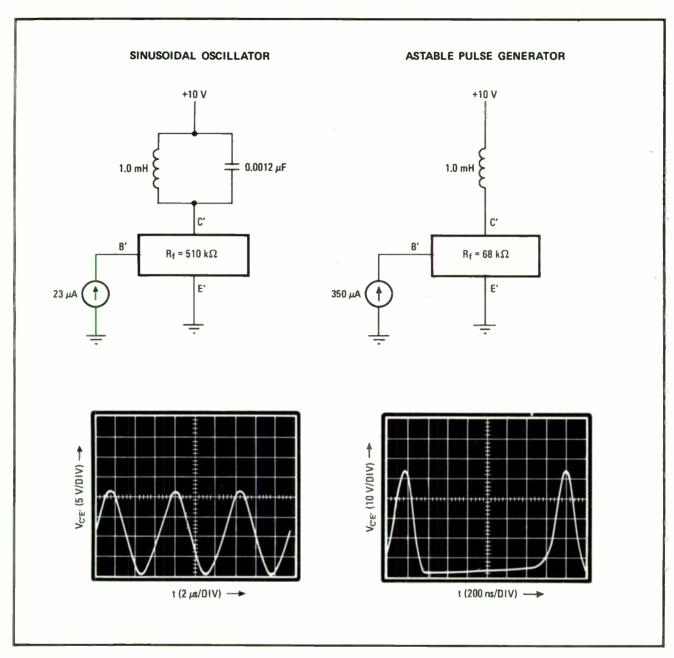

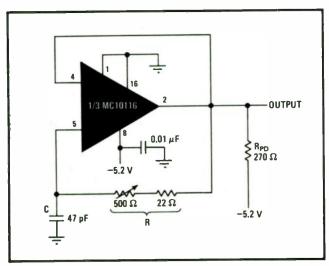

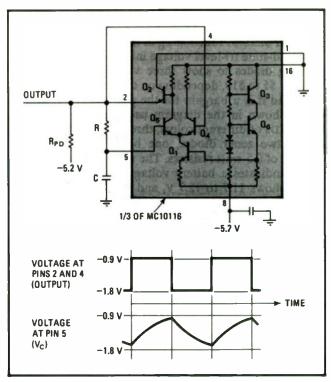

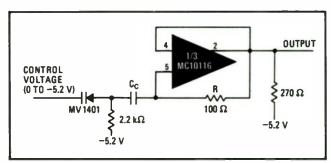

- 260 ECL tuned oscillators are voltage-stable

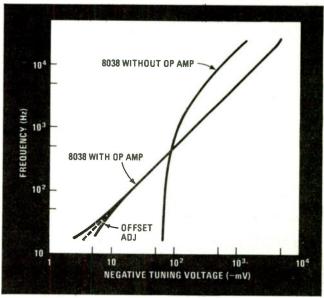

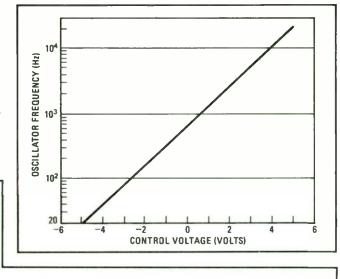

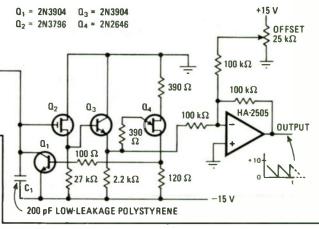

- 261 Antilog function generator keeps VCO output linear

- 262 Common silicon diodes stabilize oscillator

- 263 Stable crystal oscillator works over wide supply range

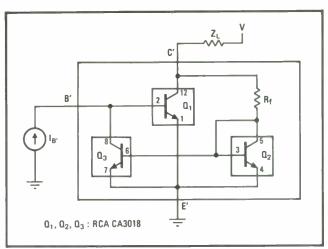

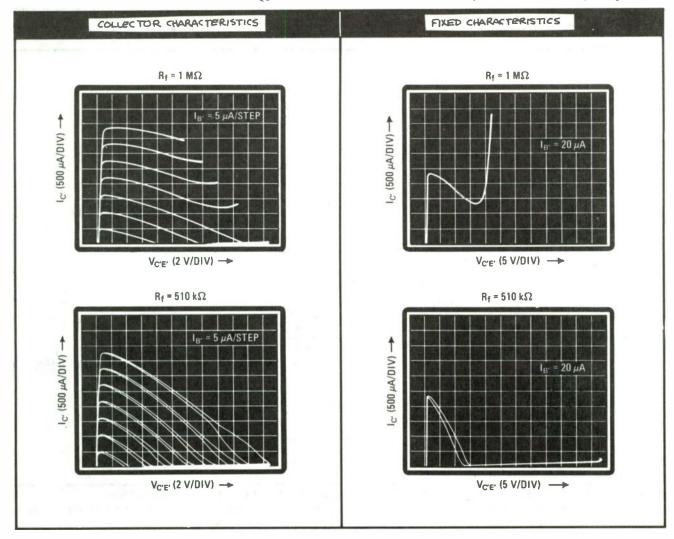

- 264 Negative-resistance generator has controllable response

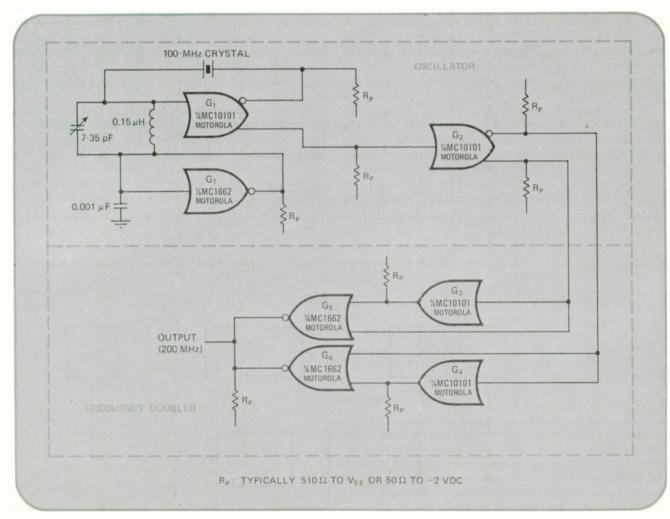

- 266 ECL gates stretch oscillator range

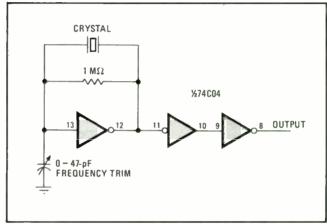

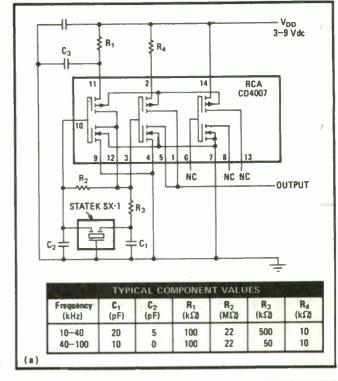

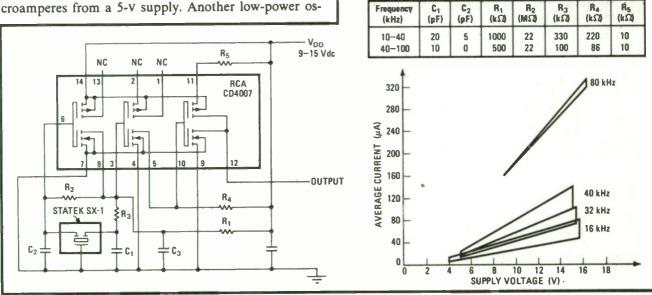

- 267 C-MOS minimizes the size of crystal oscillators

- 269 ECL IC oscillates from 10 to 50 MHz

#### 36. Phase-lock circuits

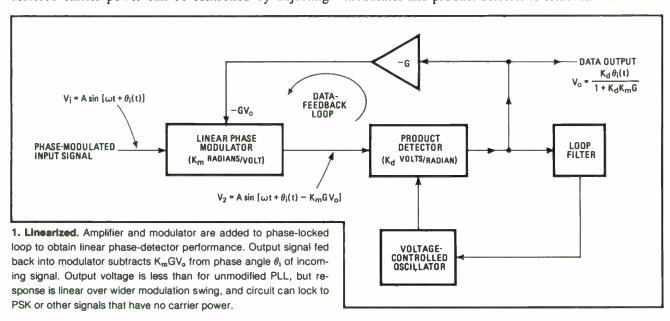

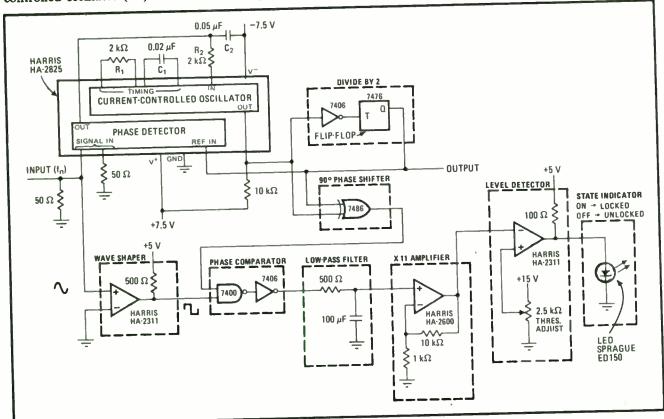

- 270 Feedback in phase-locked loop linearizes phase demodulator

- 271 Phase-locked loop includes lock indicator

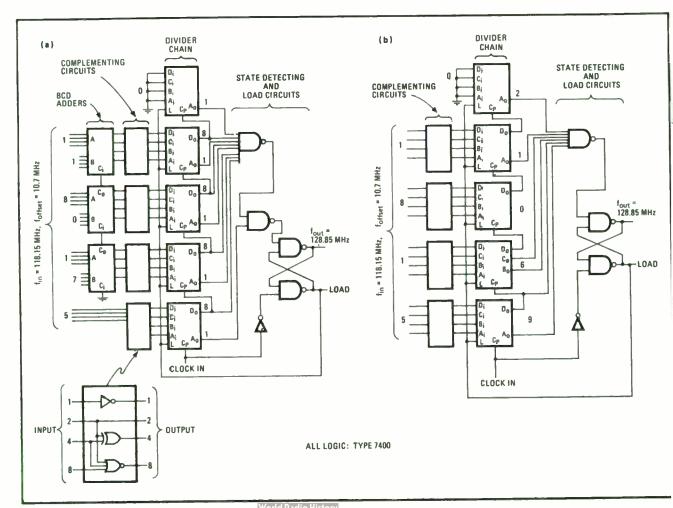

- 273 Circumventing BCD addition in digital phase-locked loops

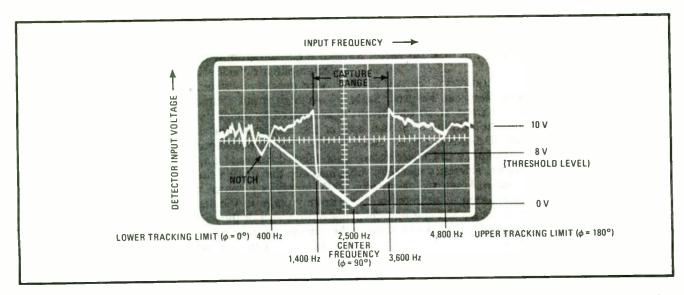

- 274 Phase-locked loop adjusts to varying signal conditions

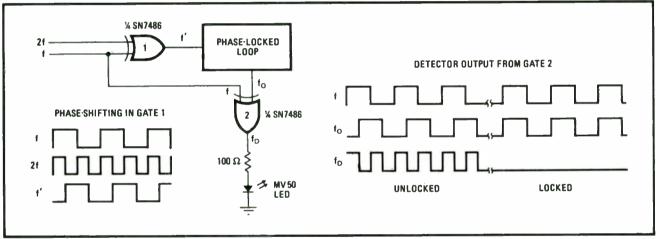

- 276 Logic gates and LED indicate phase lock

- 276 Analog multiplier/divider simplifies frequency locking

#### 37. Phase shifters

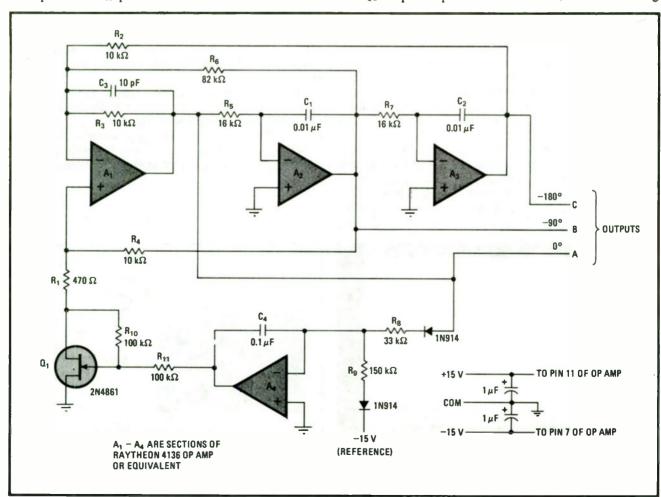

- 278 Outputs of op-amp networks have fixed phase difference

- 279 All-digital phase shifter handles 5-to-1 bandwidth

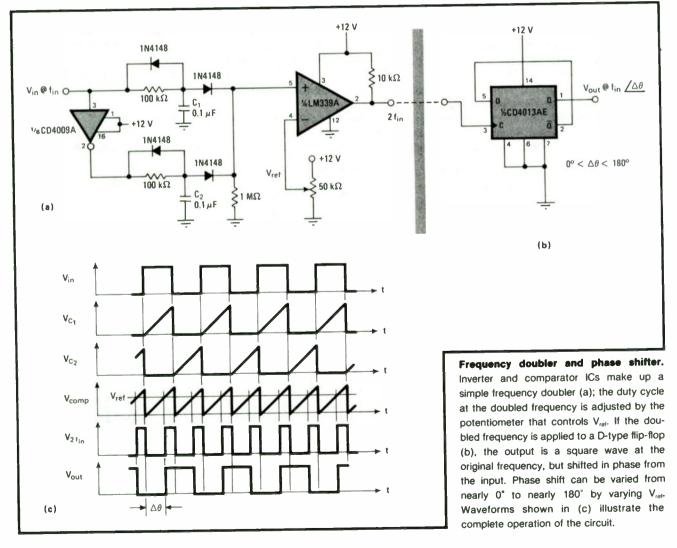

- 280 Frequency doubler and flip-flop make adjustable phase shifter

#### 38. Potentiometer circuits

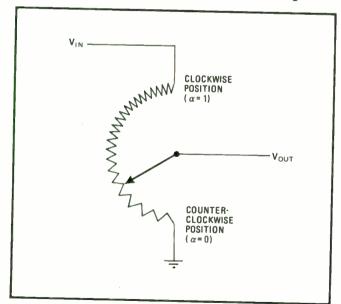

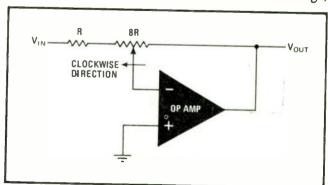

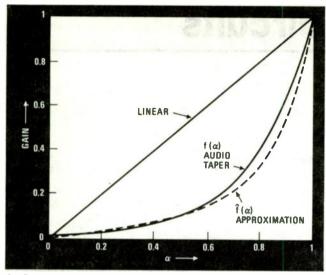

- 281 Linear pot and op amp provide tapered audio volume control

- 283 Series resistance improves potentiometer linearity

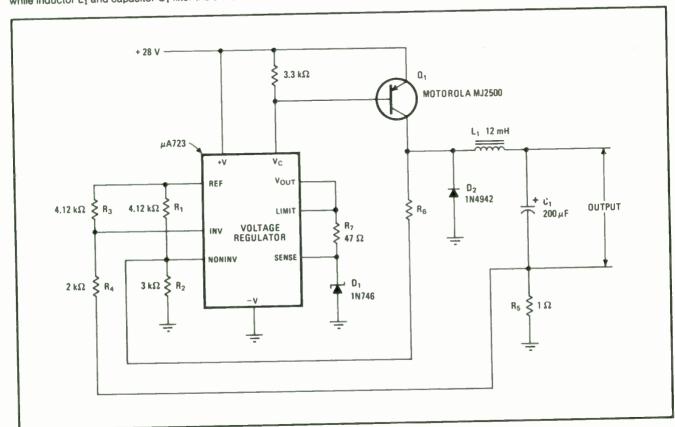

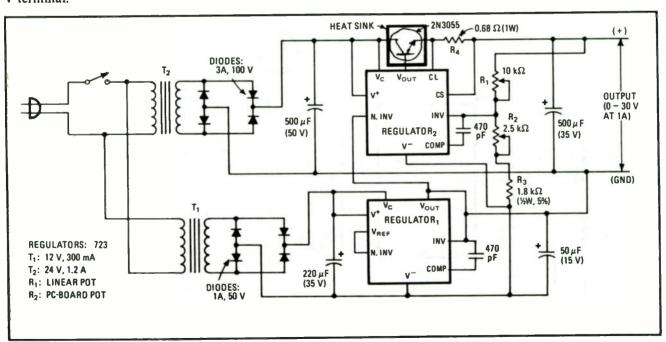

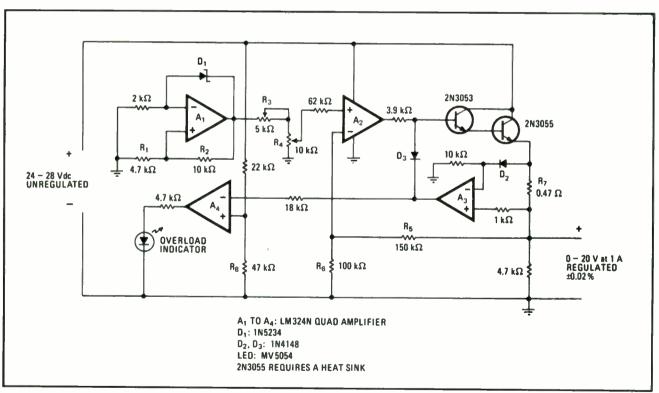

#### 39. Power supplies

- 284 Voltage doublers power microprocessor PROMs

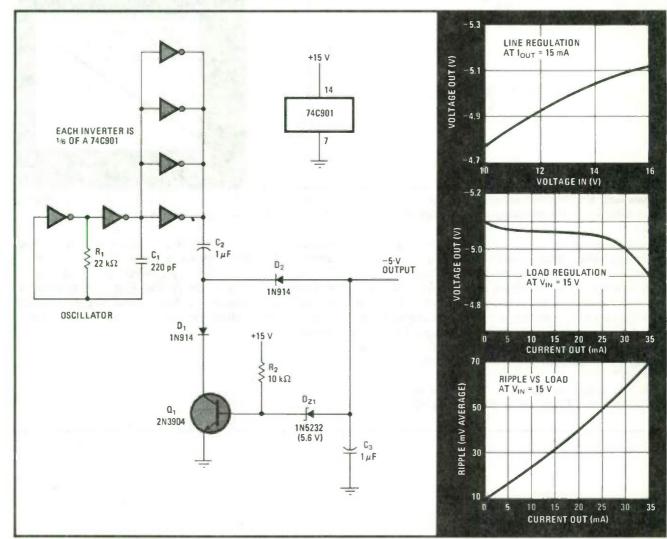

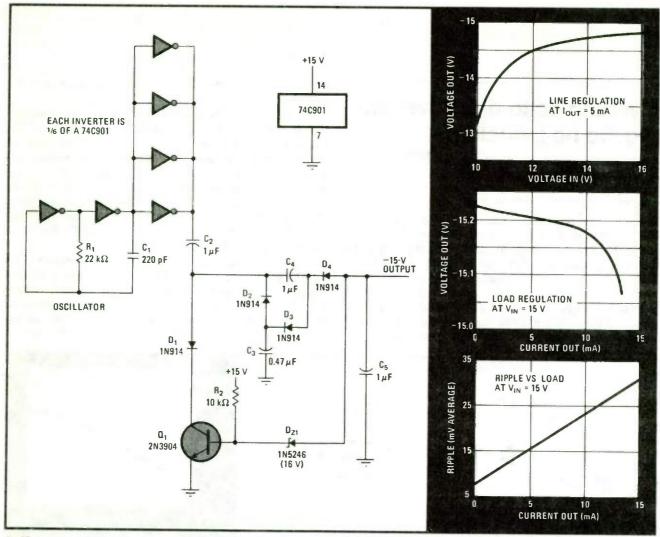

- 285 Inverting dc-to-dc converters require no inductors

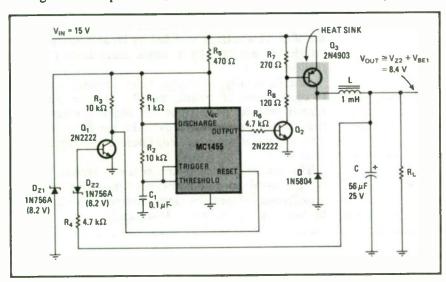

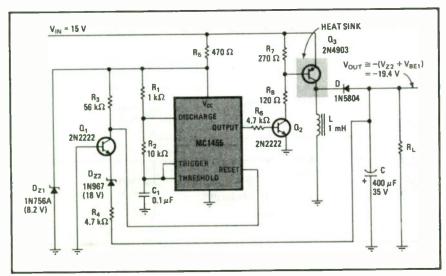

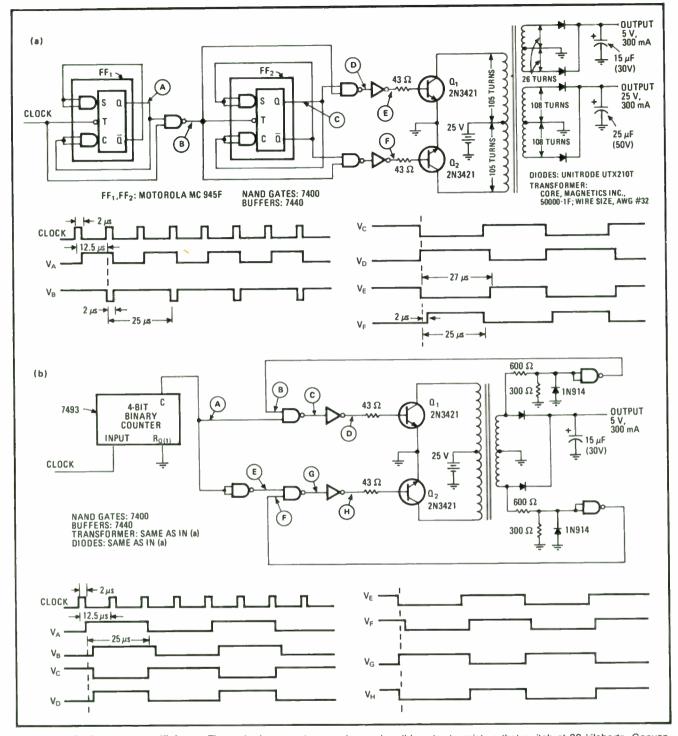

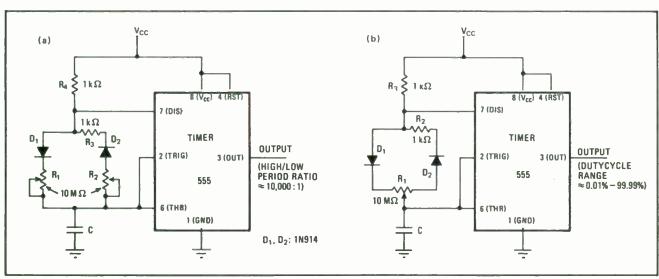

- 287 IC timers control dc-dc converters

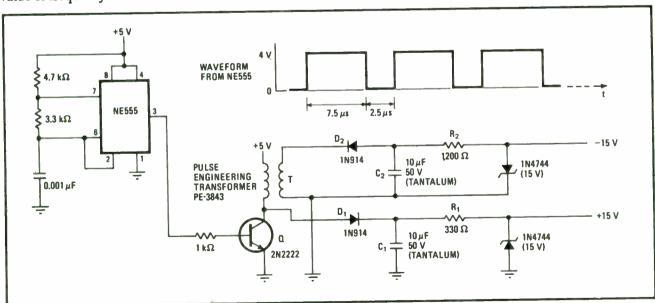

- 288 Compact dc-dc converter yields ± 15 V from +5 V

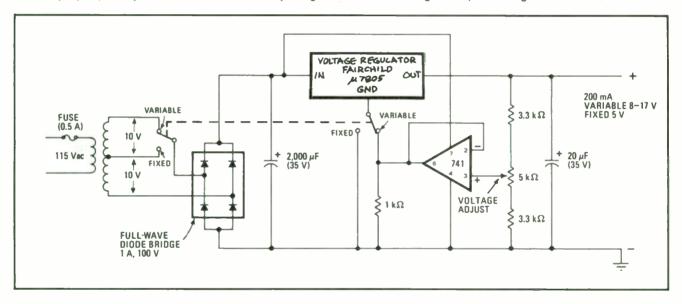

- 289 Power-supply add-on yields variable-ratio output

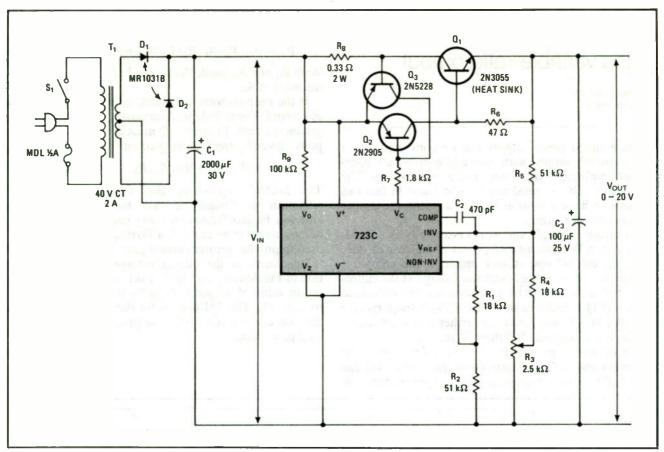

- 289 Regulated power supply is adjustable from 0 to 38 V

- 291 Gate bias circuit for n-MOS runs from 5-V TTL supply

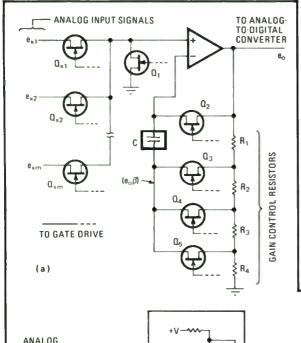

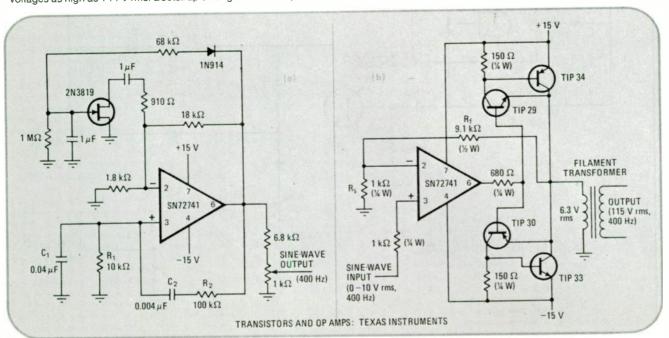

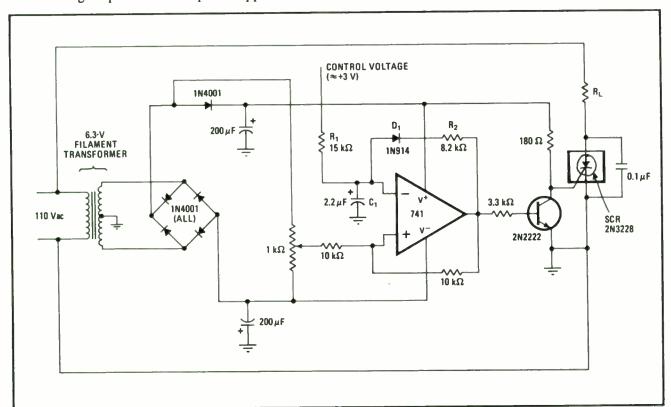

- 292 Filament transformer output drops cost of 400-Hz supply

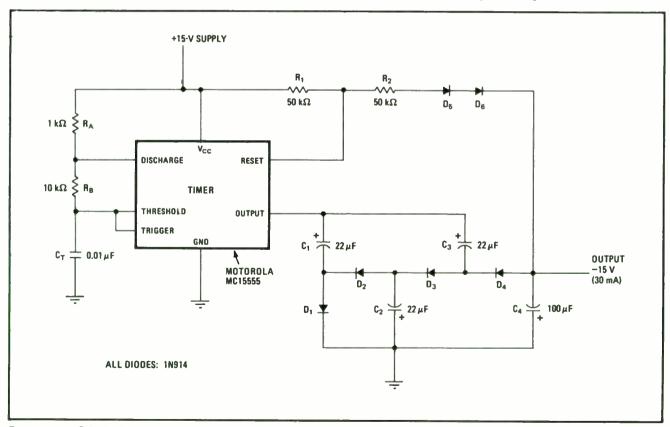

- 293 IC timer and voltage doubler form a dc-dc converter

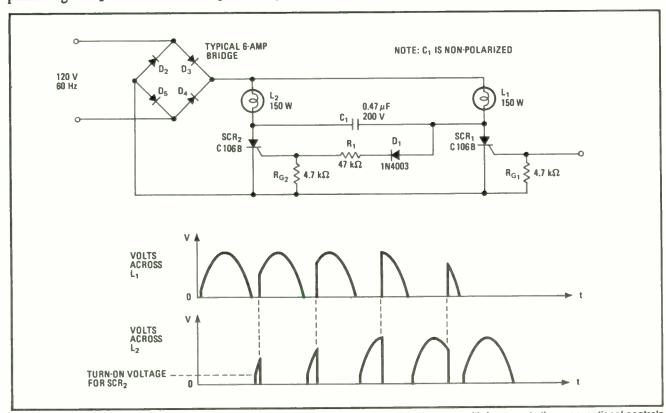

- 294 SCR zero-cross trigger limits maximum load power

- 295 Handy supply provides fixed and variable outputs

- 295 Eliminating current spiking from dc-to-dc converters

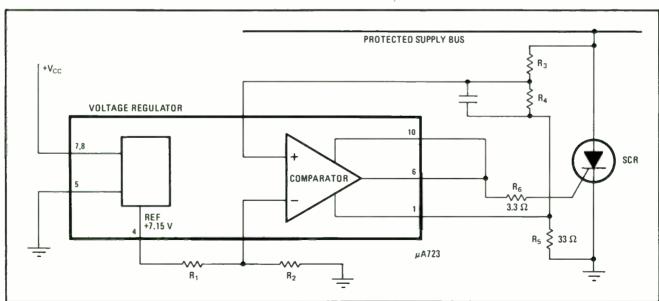

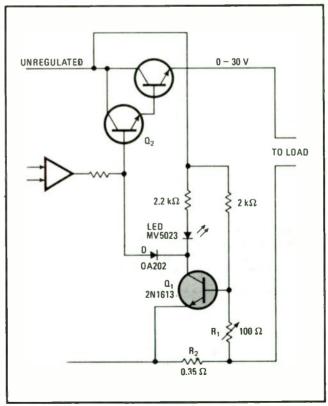

- 297 SCR crowbar circuit fires quickly and surely

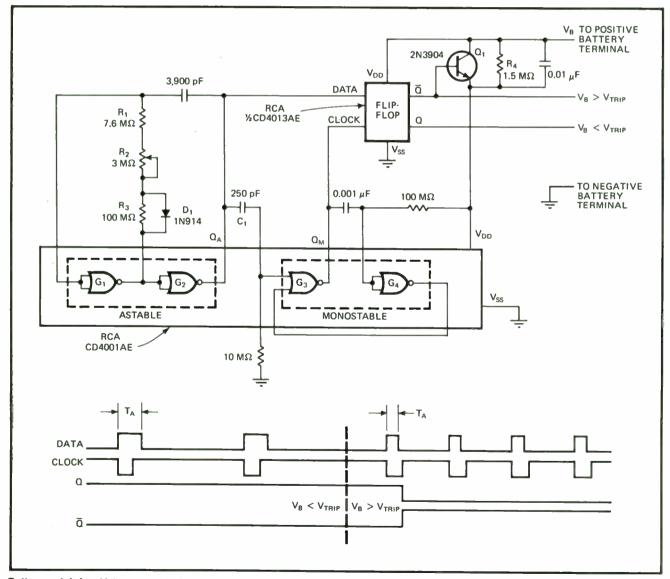

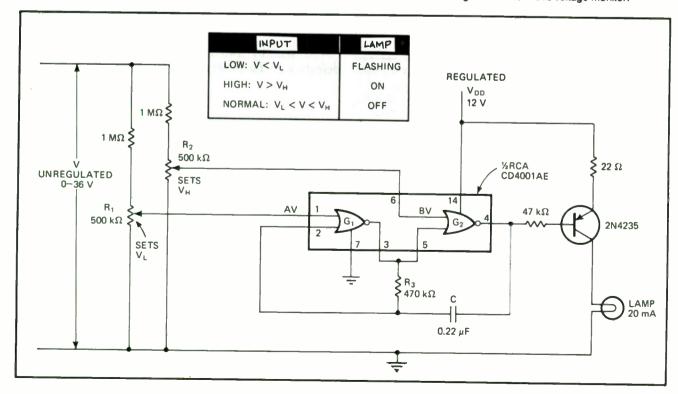

- 298 C-MOS voltage monitor protects Ni-Cd batteries

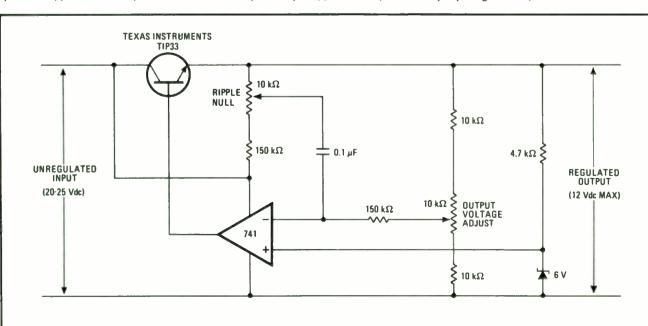

- 299 Inexpensive power supply produces zero-ripple output

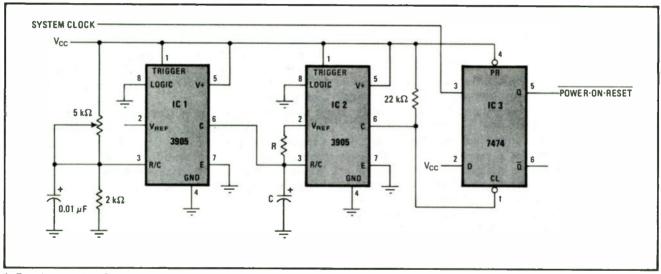

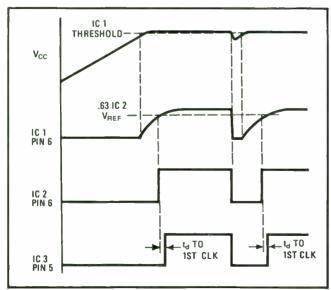

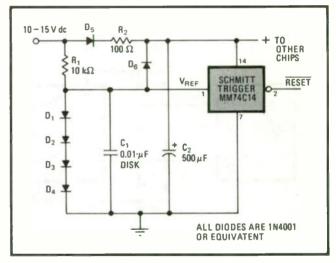

- 300 Timer circuit generates precision power-on reset

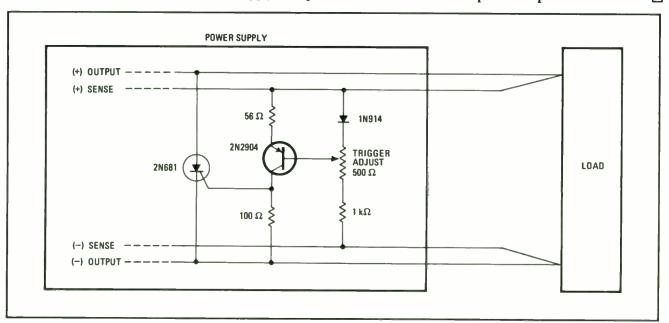

- 301 Crowbar protection circuit senses load voltage directly

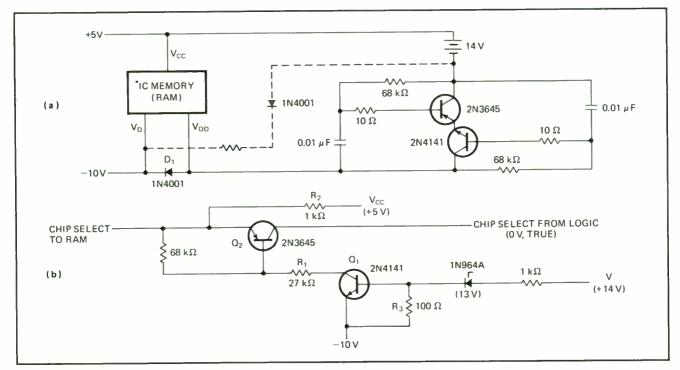

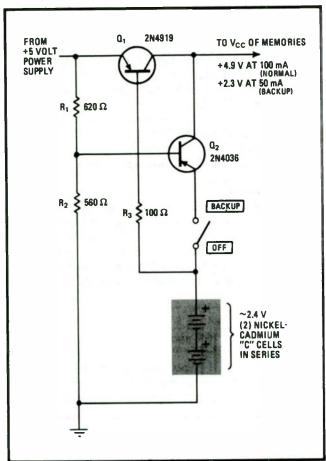

- 301 Pulsed standby battery saves MOS memory data

- 303 One lamp can monitor battery voltage

| 304 | 2 | A-V | hattery | backup | protects | microprocessor | memory |

|-----|---|-----|---------|--------|----------|----------------|--------|

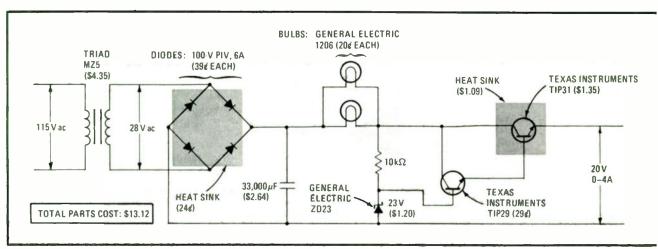

305 Four-ampere power supply costs just \$13 to build

#### 40. Programable gain controls

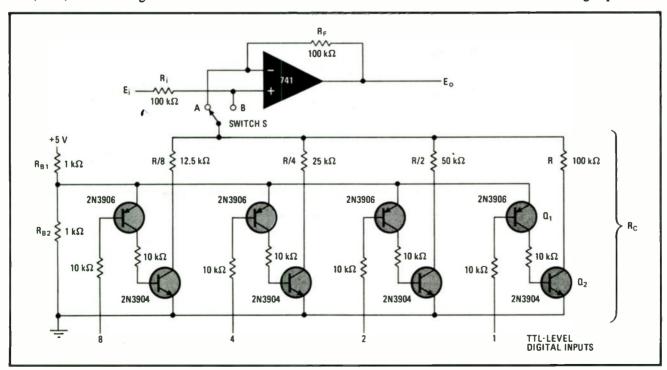

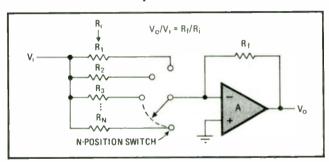

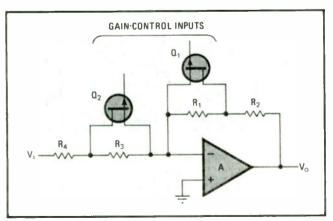

- 306 Digital word sets gain of amplifier

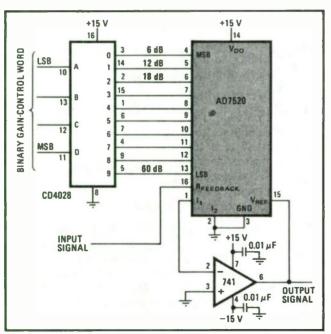

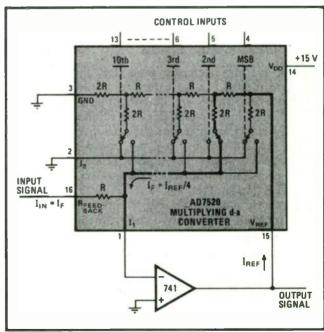

- 307 D-a converter forms programable gain control

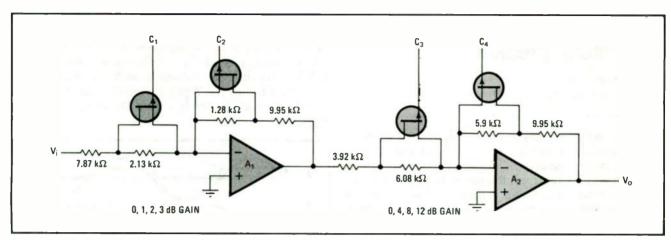

- 308 Combination logic cuts parts in digitally controlled amplifier

#### 41. Protection circuits

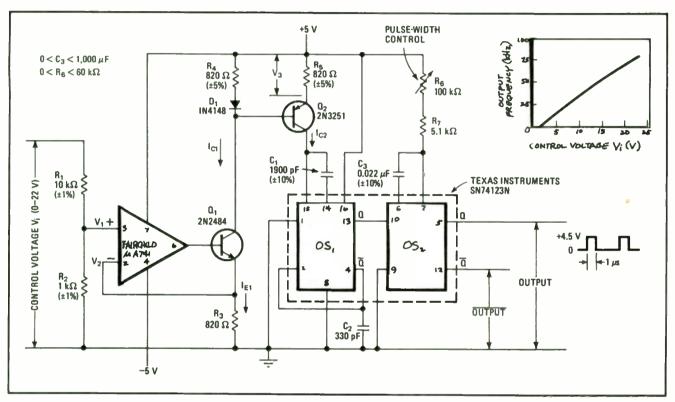

- 310 Phase-sequence detector trips circuit breaker

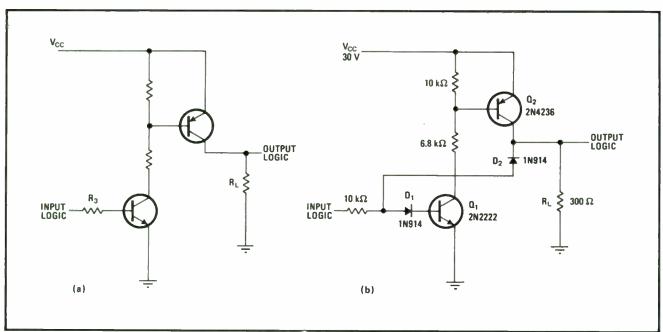

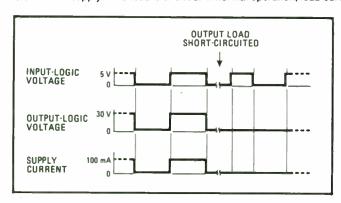

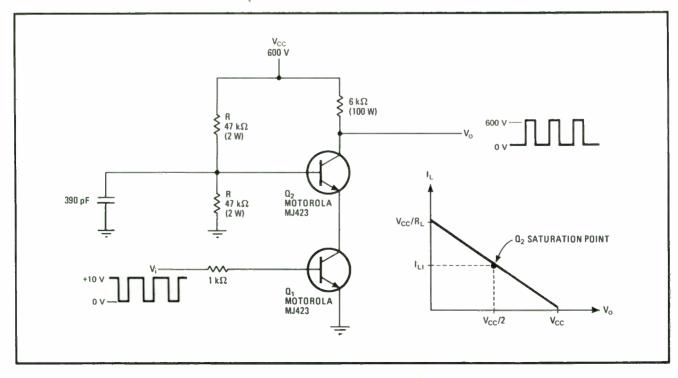

- 311 Current and power limiter protects switching transistor

- 312 Diodes switch high power to protect sonar receiver

- 313 Sensing resistor limits power-supply current

- 314 Two diodes protect logic-level translator

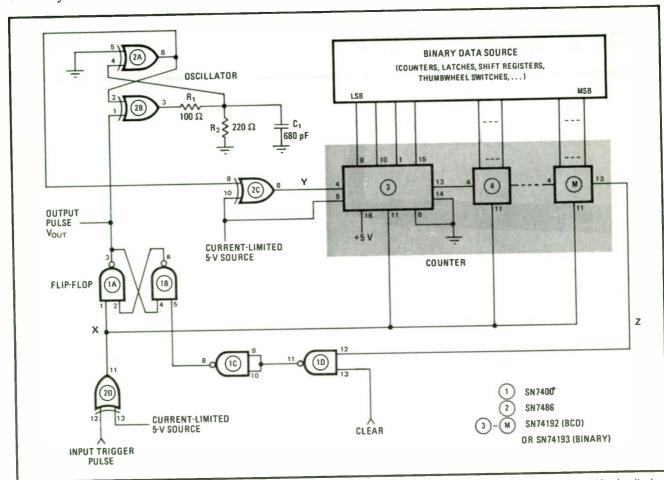

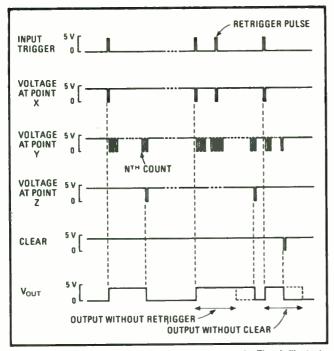

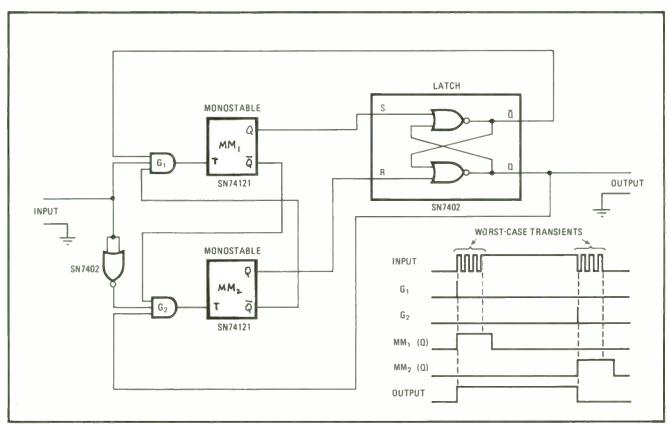

- 315 Digital transient suppressor eliminates logic errors

- 316 Voltage regulator protects logic pull-up transistors

- 317 Power-failure detector is good for short lapses

- 318 How to prevent spurious tripping of protection circuits

- 319 C-MOS reset circuit ignores brief outages

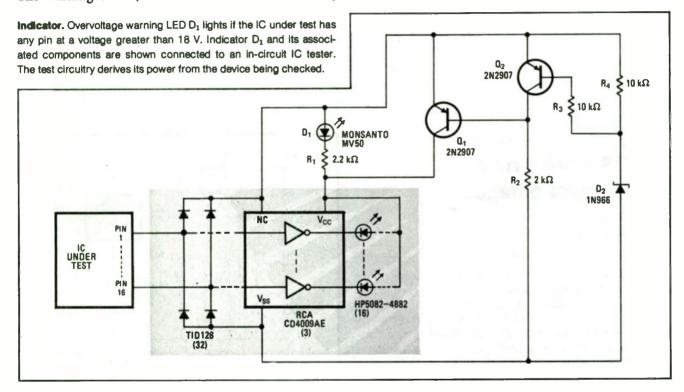

- 320 Overvoltage indicator can be added to C-MOS IC tester

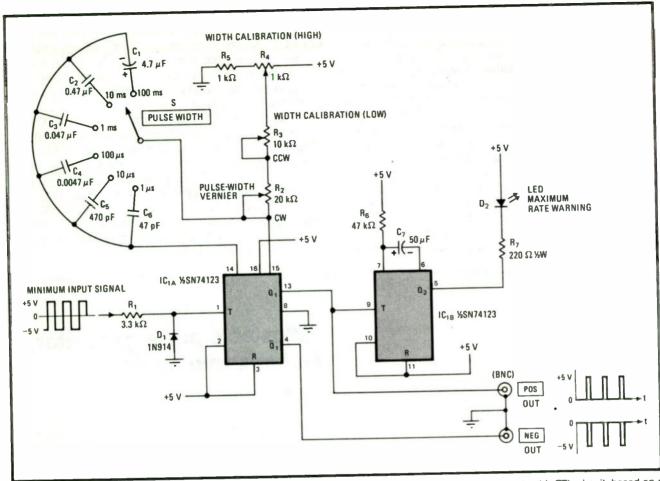

#### 42. Pulse generators

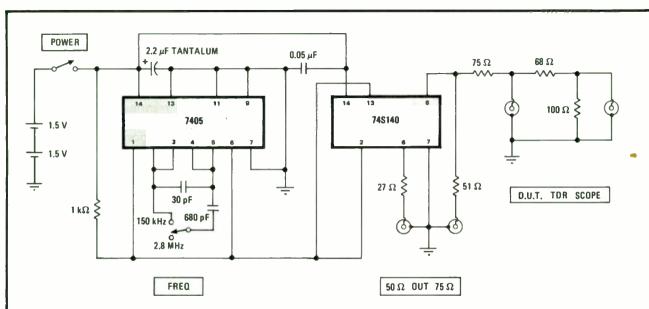

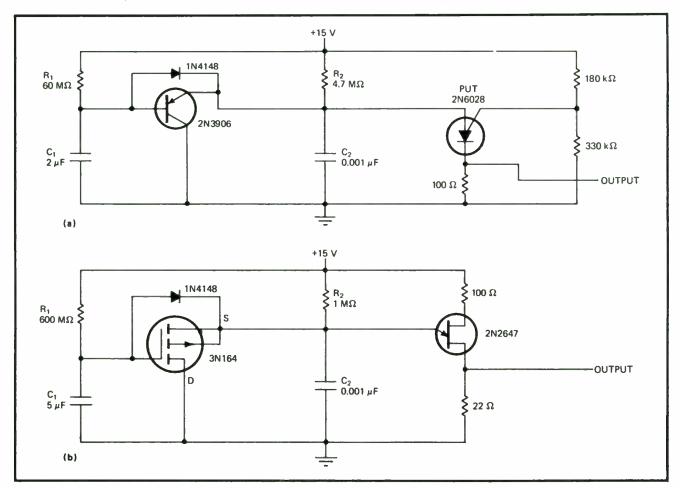

- 321 Nanosecond-pulse generator is powered by two D cells

- 322 Generating pulses with C-MOS flip-flops

- 323 Preset generator produces desired number of pulses 324 Controlling duty cycle and rep rate independently

- 325 Pulse generator accuracy is immune to aging 326 Generator's duty cycle stays constant under load

- 326 Generator independently varies pulse rate and width

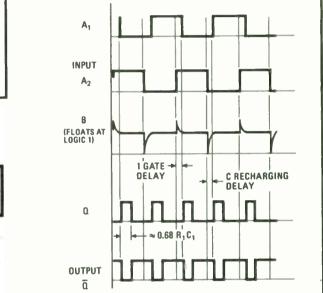

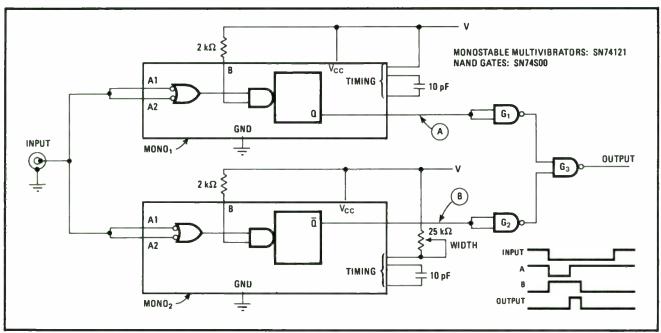

- 327 Generating nanosecond pulses with TTL monostables

- 328 Single switch regulates number of pulses

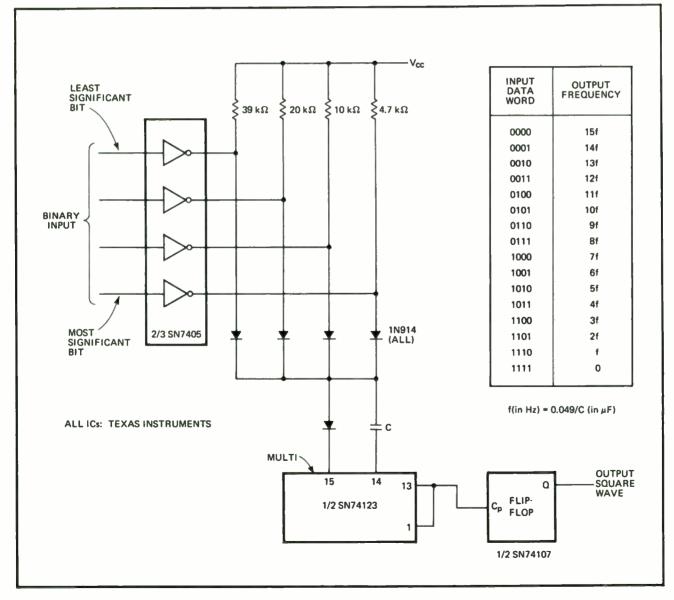

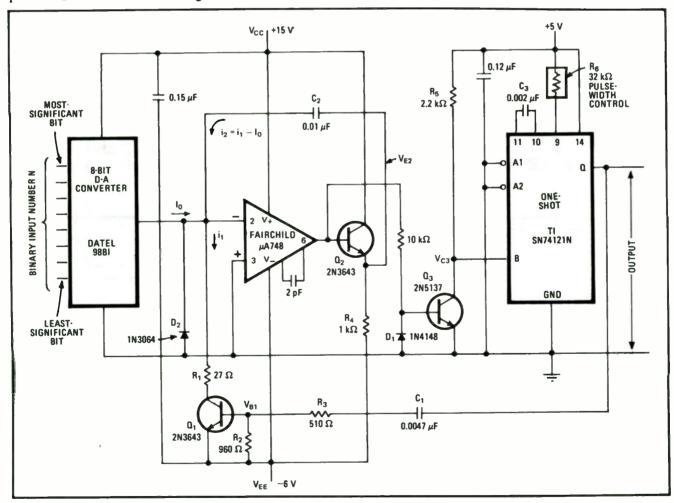

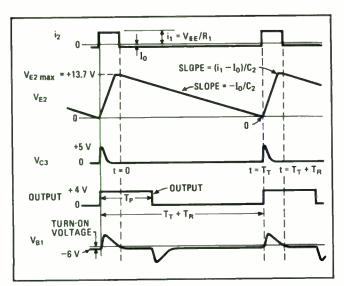

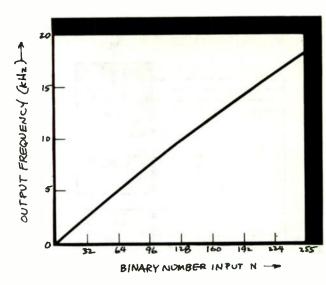

- 330 Binary input determines pulse-generator frequency

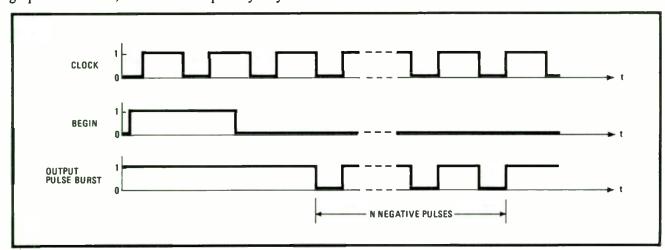

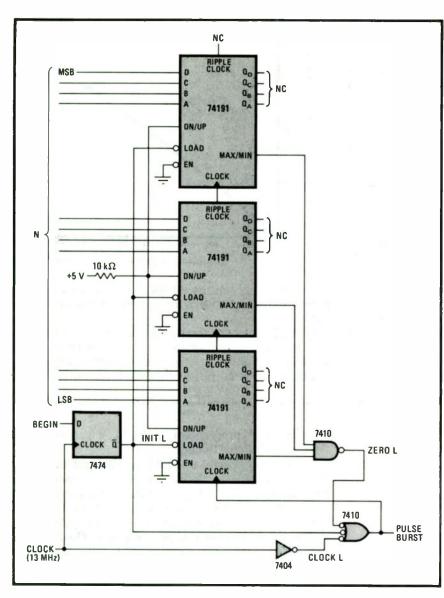

- 331 Pulse generator produces programable burst

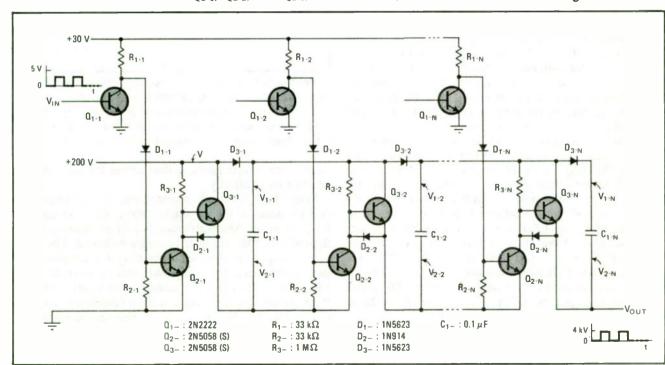

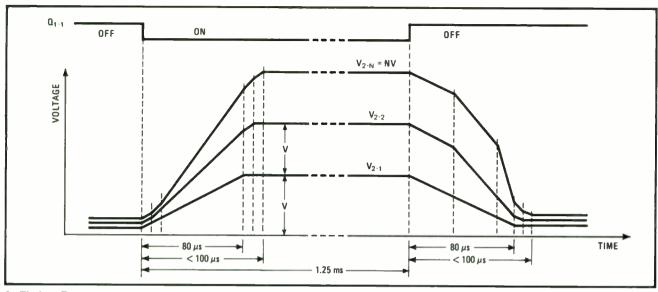

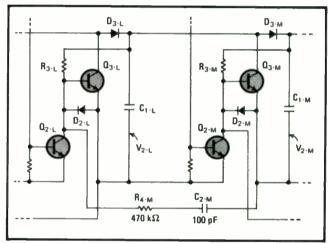

- 333 Bootstrap circuit generates high-voltage pulse train

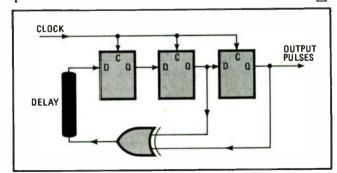

- 335 Delay line in shift register speeds m-sequence generation

- 336 One-shot with feedback loop maintains constant duty cycle

- 337 Adjustable pulse generator features rate alarm

#### 43. Rectifiers

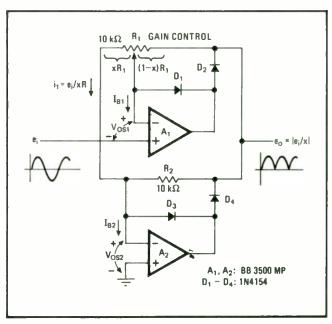

- 339 Rectifying wide-range signals with precision, variable gain

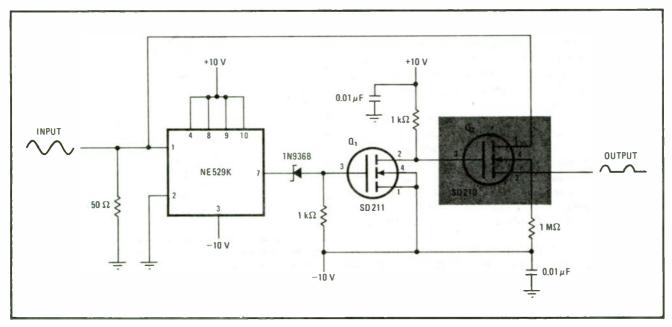

- 340 Comparator and D-MOS switch rectify small signals linearly

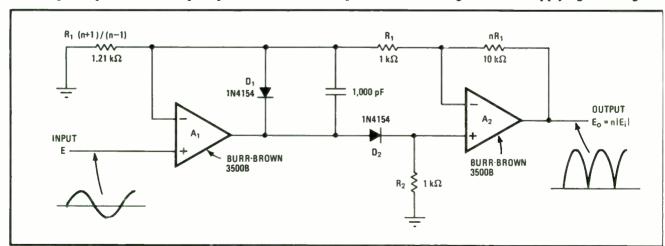

- 341 Full-wave rectifier needs only three matched resistors

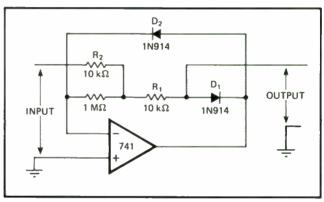

- 342 Op amp with feedback makes full-wave rectifier

#### 44. Security circuits

- 343 Latch circuits interlock remote switches electrically

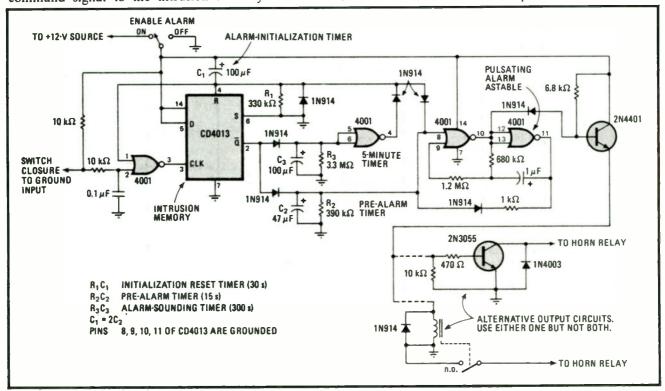

- 344 Auto intrusion alarm uses C-MOS circuits

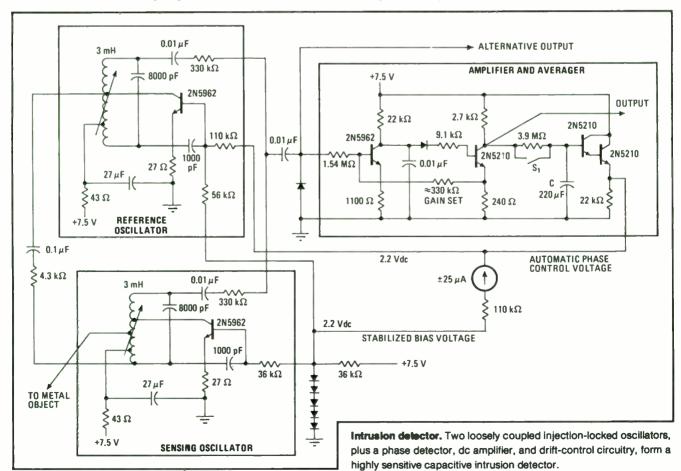

- 345 Twin oscillators form intruder detector

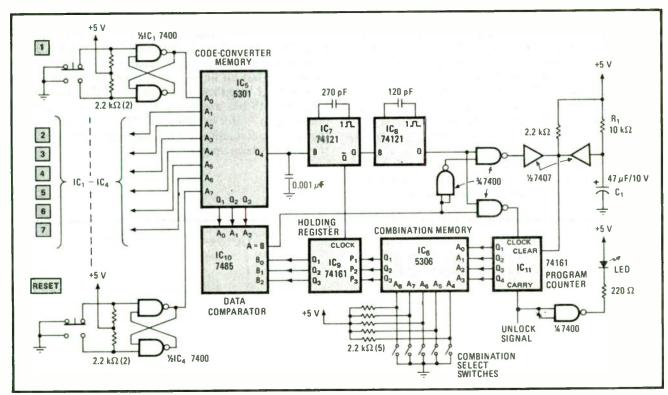

- 346 Electronic combination lock offers double protection

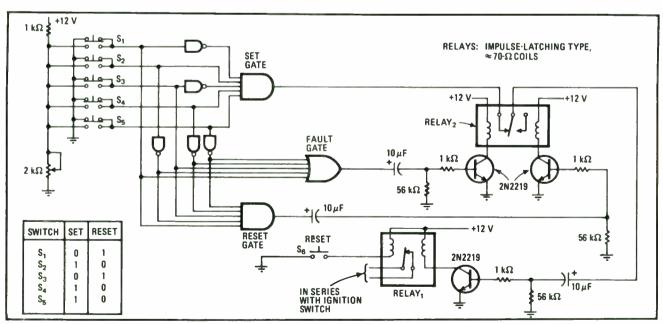

- 347 Digital combination lock is virtually crackproof

#### 45. Sensors

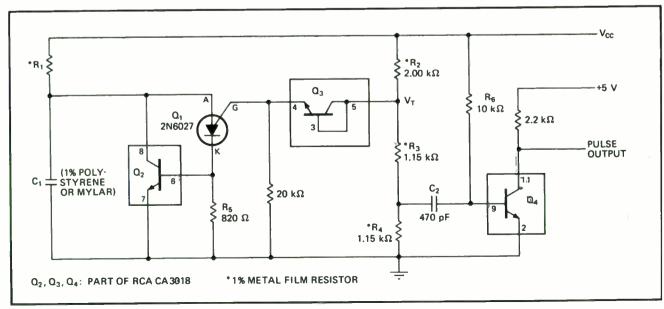

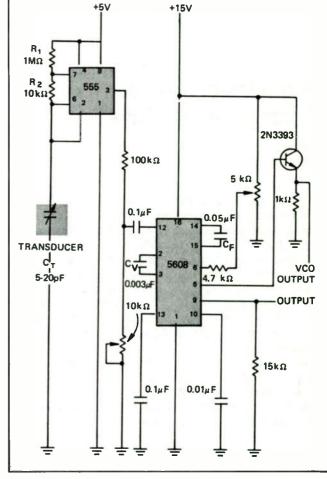

- 349 Capacitive transducer senses tension in muscle fibers

- 350 Photodetector senses motion in noisy surroundings

#### 46. Switching circuits

- 352 Doubling breakdown voltage with cascoded transistors

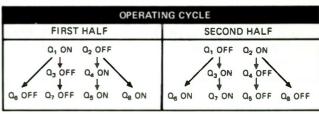

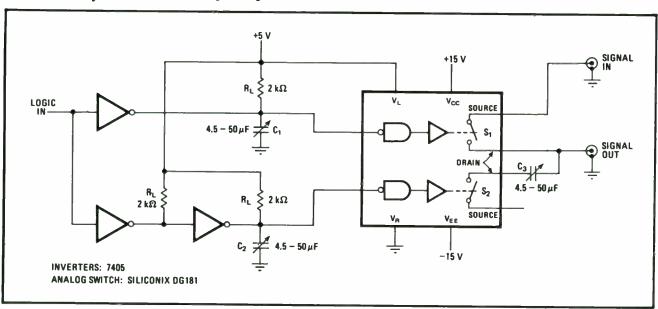

- 353 Solid-state dpdt switch provides current reversal

- 354 Attenuating transients in analog FET switches

- 355 Transistor gating circuit cuts signal delay to 100 ps

- 355 Op amp cancels video switching transients

- 356 Analog gate and zener diode give 70-dB isolation at 80 MHz

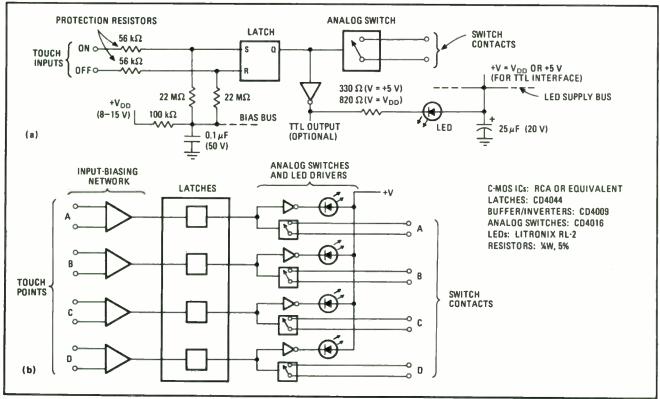

- 357 C-MOS touch-switch array controls analog signals

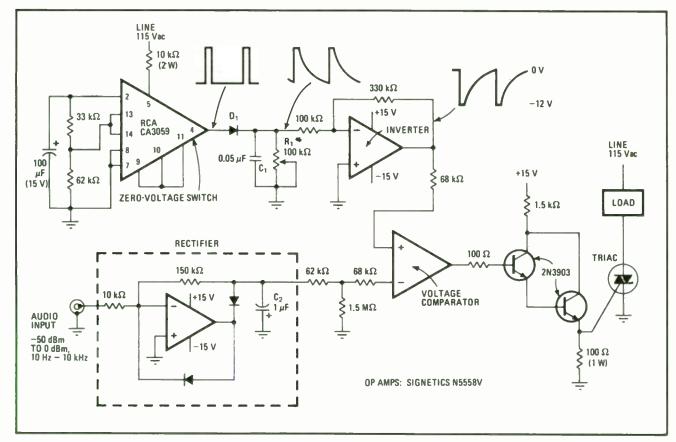

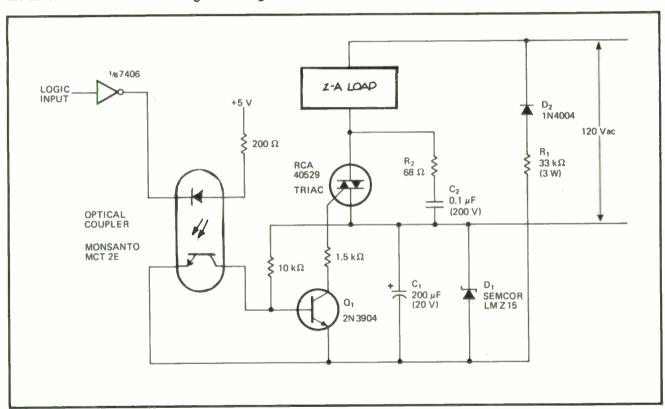

- 359 Switching large ac loads with logic-level signals

#### 47. Temperature controls

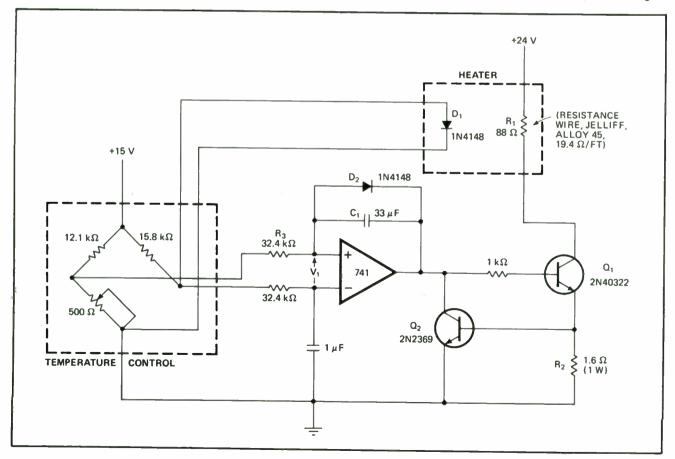

- 360 Diode plus low-cost op amp makes accurate thermostat

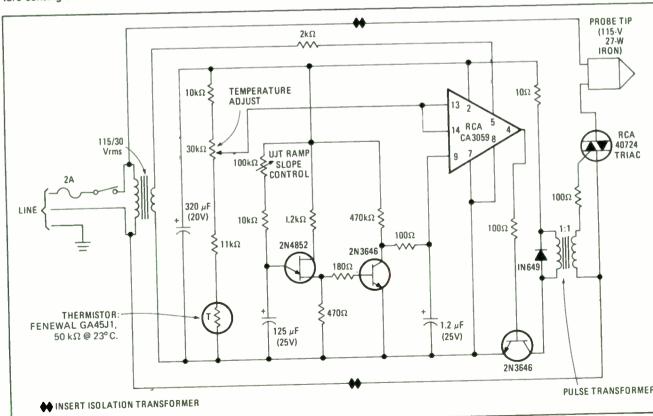

- 361 Soldering iron converts to constant-temperature probe

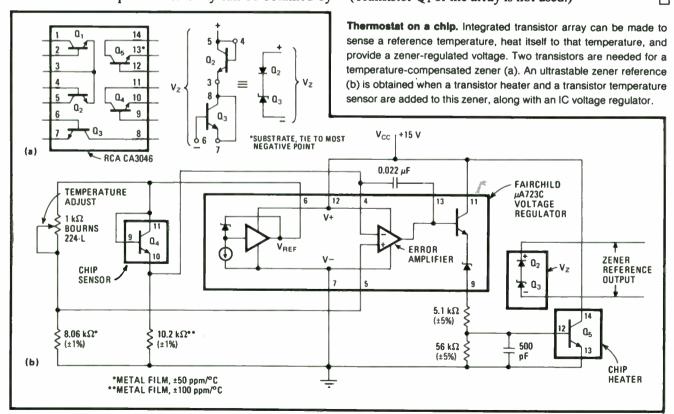

- 362 Using transistor arrays for temperature compensation

- 363 Diode pair senses differential temperature

- 364 Temperature compensation for high-frequency transistors

- 366 Direct-reading converter yields temperature

#### 48. Timing circuits

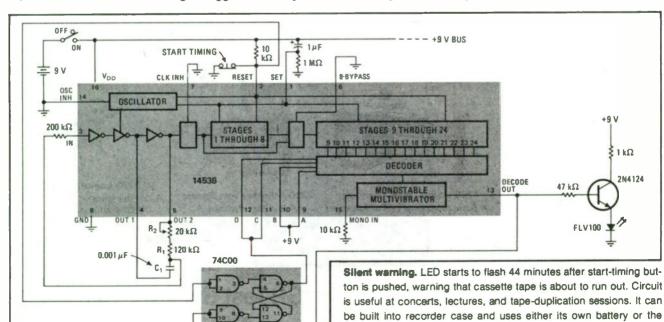

- 367 Silent timer warns of tape run-out

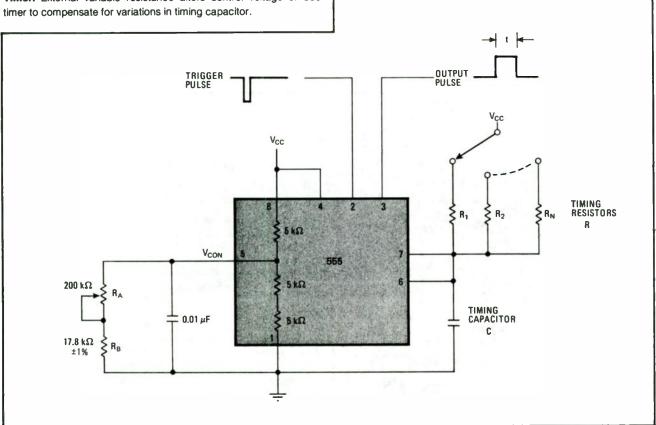

- 368 Compensating the 555 timer for capacitance variations

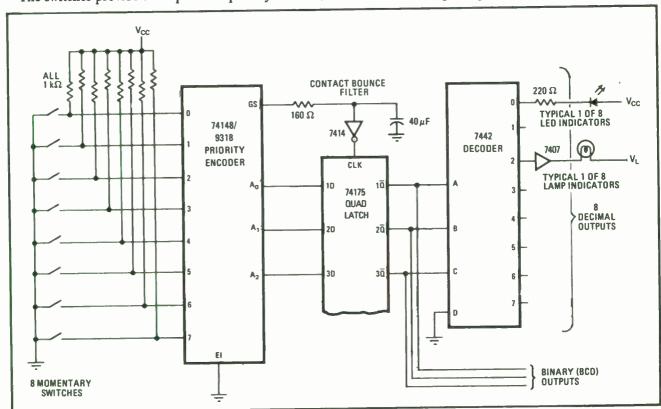

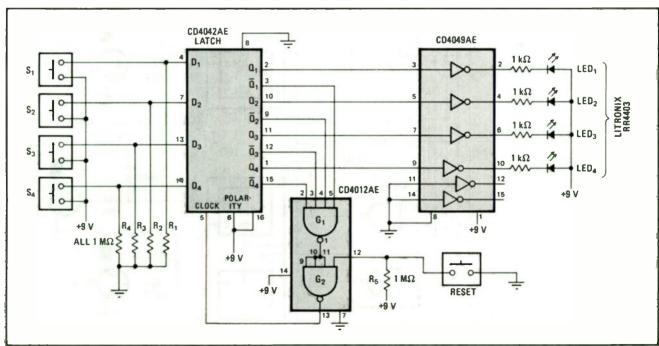

- 369 Discriminator displays first of four responses

- 370 Simple logic arrangement identifies first event

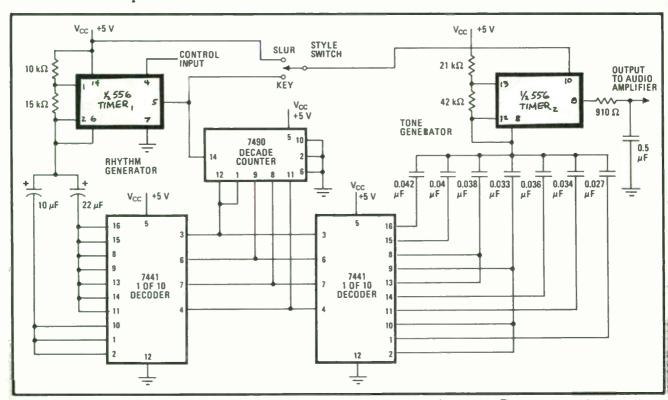

- 371 Making music with IC timers

- 372 Extending time delay with an emitter-follower

- 373 Getting extra control over output periods of IC timer

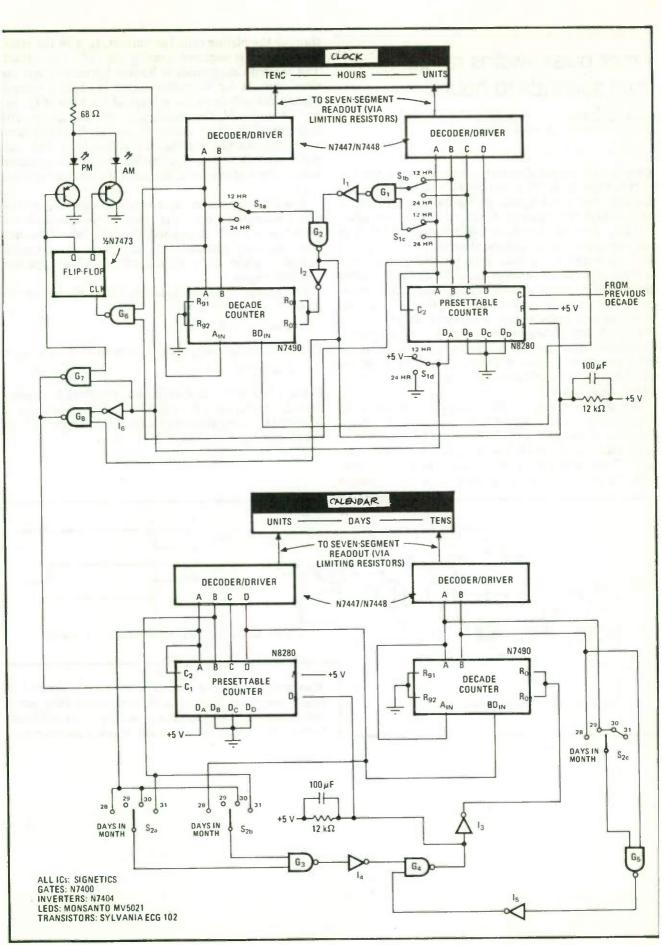

- 374 Digital clock/calendar offers dual-mode display

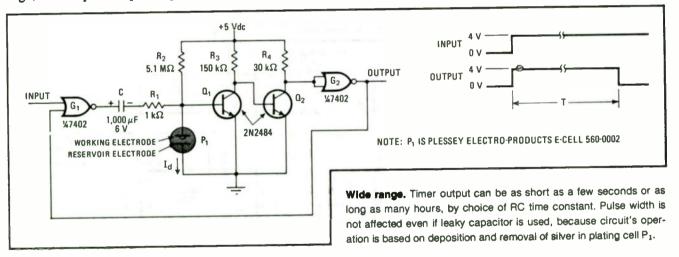

- 376 Timer pulse widths range from seconds to hours

#### 49. Triggers

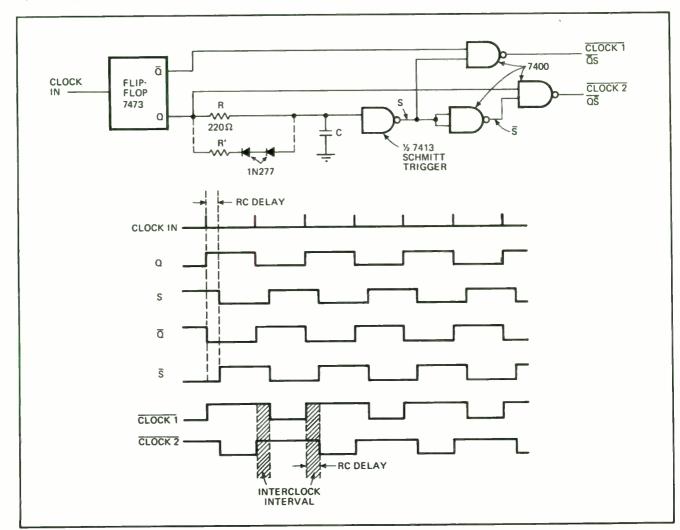

- 377 Schmitt trigger prevents clock train overlap

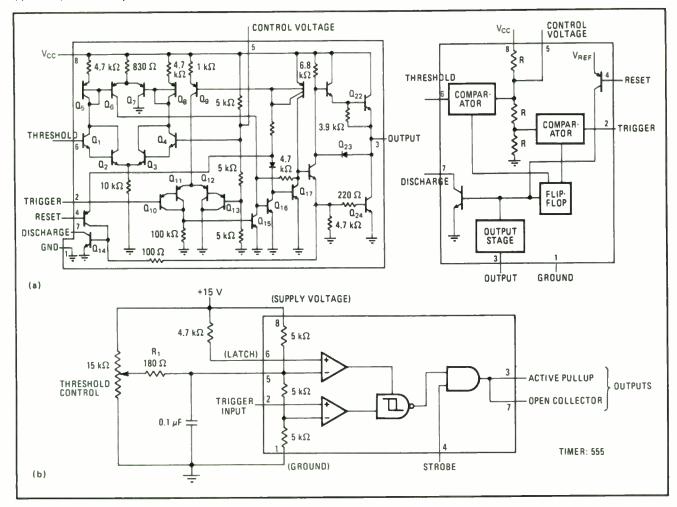

- 378 Integrated timer operates as variable Schmitt trigger

#### 50. Voltage references

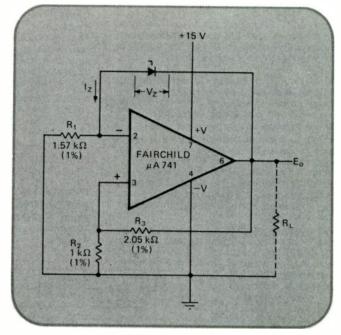

- 380 Stable voltage reference uses single power supply

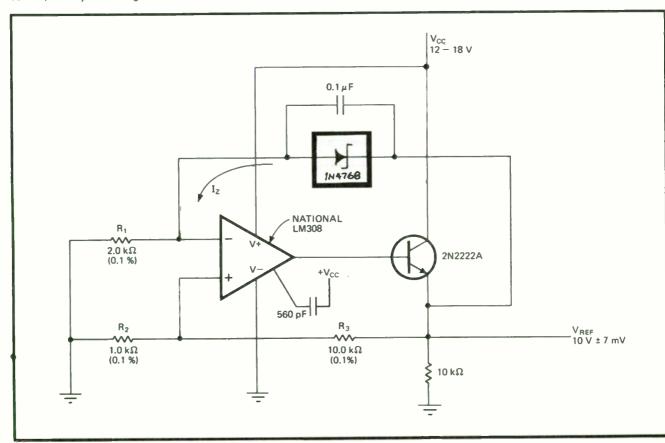

- 381 Single-supply reference source uses self-regulated zener

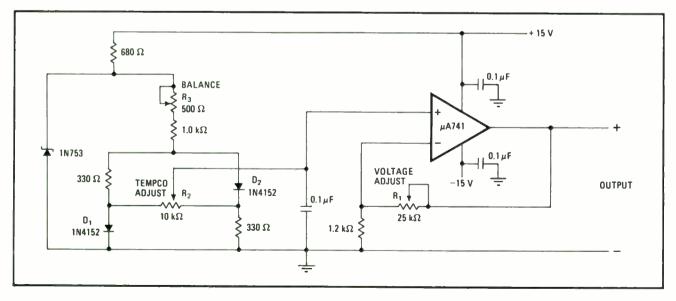

- 382 Variable voltage source has independently adjustable TC

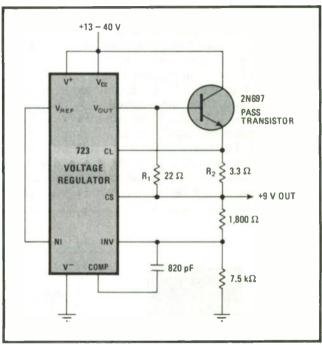

#### 51. Voltage regulators

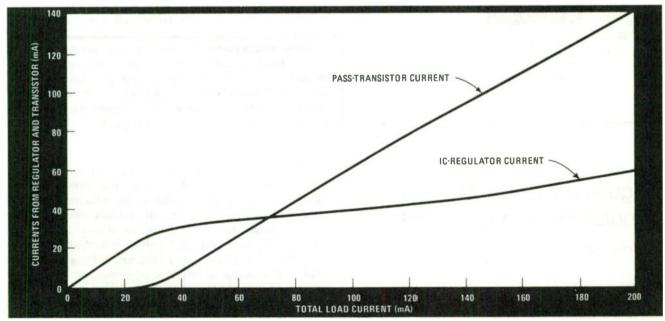

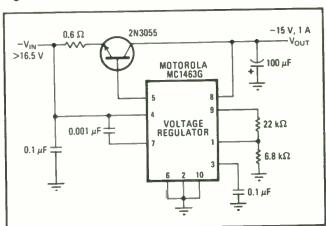

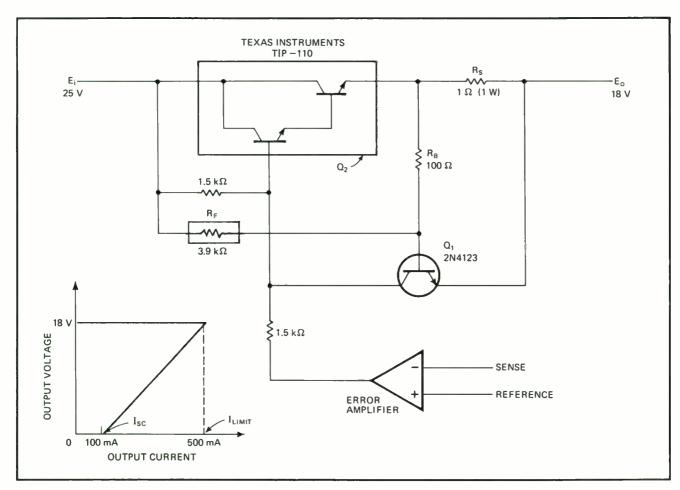

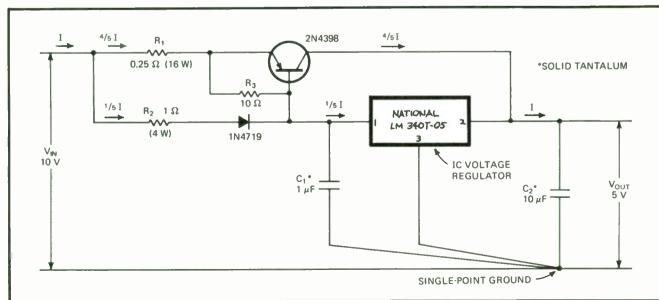

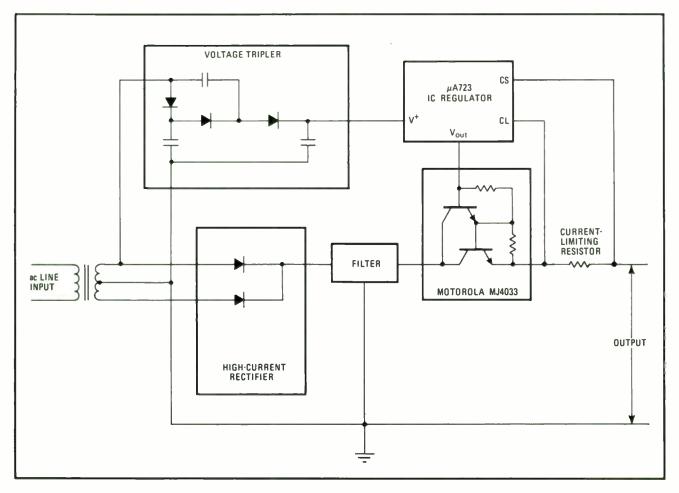

- 383 Extra resistor helps regulator share load with transistor

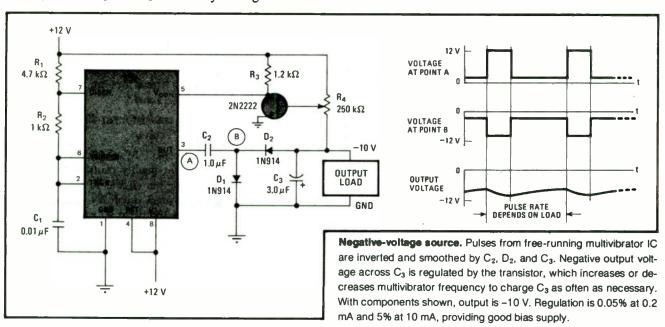

- 384 555 as switching regulator supplies negative voltage

- 384 Regulator for standby supply handles large load currents

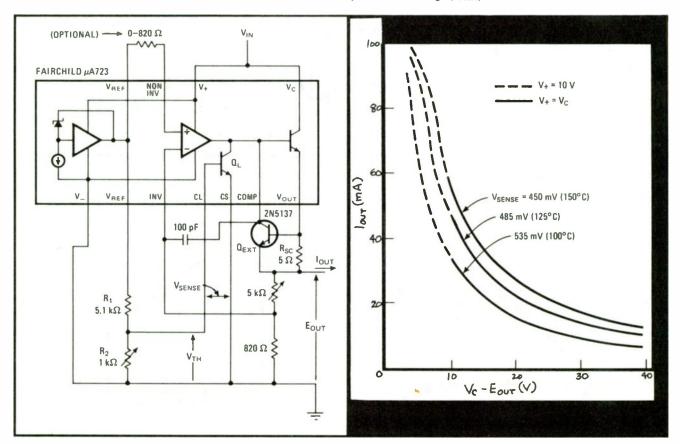

- 386 Temperature limiting boosts regulator output current

- 387 Boosting IC regulator current with almost no power loss

- 388 Adding foldback resistor provides overload safety

- 389 Current-sharing design boosts regulator output

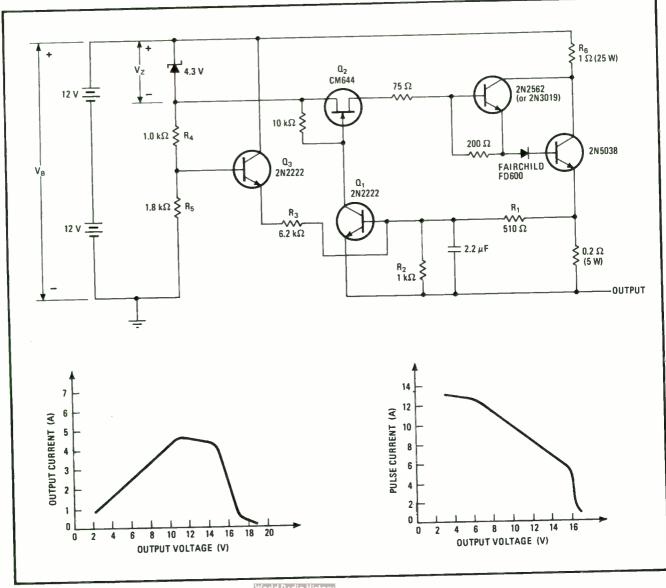

- 390 Economical series regulator supplies up to 10 amperes

- 391 Switching regulator produces constant-current output

- 392 Regulating supply voltage all the way down to zero 393 Regulator for op amps practically powers itself

- 394 Regulating voltage with just one quad IC and one supply

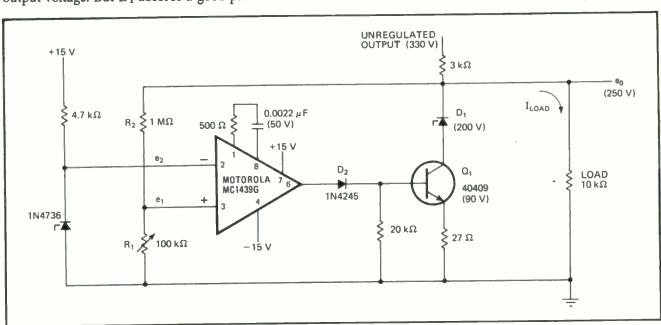

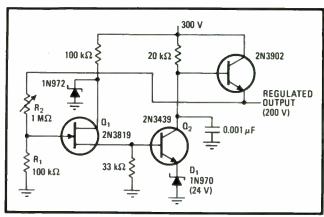

- 395 Regulating high voltage with low-voltage transistors 396 Regulating high voltages with low-voltage zeners

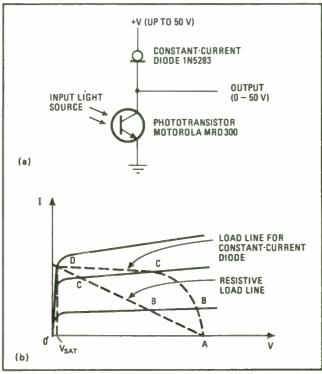

- 351 Two-component light sensor has high voltage output

# **Preface**

Since 1964, the Designer's Casebook section of *Electronics* magazine has been consistently one of the best read sections of the magazine. The reasons for this are not hard to find. First, engineers are always looking for ways to relieve the drudgery that is part of design. If they can save time and effort by incorporating or adapting ideas from others, they will do so with alacrity. Second, the standards of *Electronics* have always been high. Published Casebook ideas are selected for innovation, usefulness, and accuracy.

This volume is a compilation of 346 useful circuits that have appeared in Designer's Casebook over the last four years. They were designed by engineering readers of *Electronics* from all over the world and represent approaches to achieving oft-required electronic functions in a variety of ways. There are 51 such functions arranged alphabetically, and the circuits have been conveniently grouped within them for fast access.

This is not intended as a hobbyist book. While some are relatively simple, most of the circuits in this volume have been designed by engineers for the achievement of engineering objectives. They are presented on the same principle that has made Designer's Casebook so popular for so many years: namely, that re-inventing the wheel is wasteful of engineering time.

To the hundreds of inventive engineers who have contributed their innovative ideas to Designer's Casebook, and to the thousands of loyal *Electronics* readers who have responded enthusiastically to them, this book is gratefully dedicated.

### 1. Amplifiers

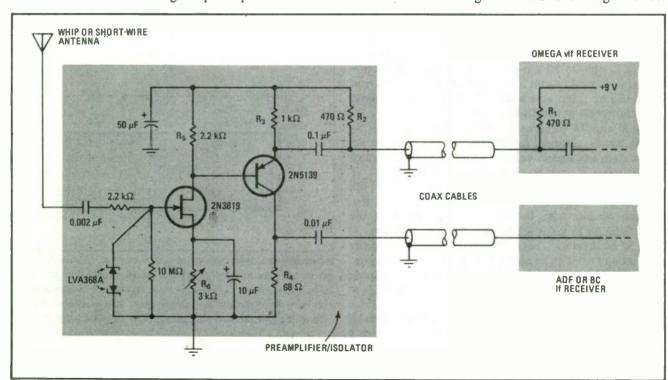

### Single preamplifier/isolator drives If and vlf receivers

by R.W. Burhans Ohio University, Athens, Ohio

Some rf front-end circuitry proposed for Omega receivers [Electronics, Sept. 5, 1974, p. 98] has now been used in several flight tests of simplified vlf navigation for general aviation. The results showed that the first-stage MOSFET occasionally burned out in the presence of very close lightning discharges, and that a common antenna, such as the automatic direction finder sense whip, should be used for both the Omega navigation receiver and the ADF receiver.

Corrections for both problems are made in the circuit of Fig. 1. The MOSFET has been replaced by a low-cost junction FET that provides a gain of 2 or 3 and adequate low-noise performance over the frequency range from 5 to 1,500 kHz. An expensive wideband line-isolating transformer used in the original preamplifier has been

eliminated by using a simple resistor divider string (R<sub>1</sub>, R<sub>2</sub>) to carry power to the preamplifier and signal output to the Omega receiver over a single cable. A small resistor in the collector lead of the 2N5139 output emitterfollower provides a unity-gain buffer output for driving an ADF or broadcast-band receiver from the preamplifier at a low impedance level through a separate cable. Isolation between the vlf receiver (10-100 kHz and the ADF/broadcast-band receiver (200-1,500 kHz) is completely satisfactory.

The 2N3819 JFET is much less likely than a MOSFET to burn out with static charges, and the back-to-back zener diodes give gross protection from high-level short-duration burst interference. The atmospheric 5-1,500-kHz noise level is usually a limiting factor in high-out-put-impedance preamplifiers of this sort, so an ultra-low-noise MOSFET is not required.

Adjustment of source-bias resistor  $R_6$  centers the operating point for equal positive and negative peak clipping on large signals. The circuit can handle input signal levels up to 0.1 volt rms before round-off distortion of the output waveform begins. For unity gain at the lf terminal, the ratio of  $R_4/R_3$  is approximately  $B \times A$ , where B is the current gain of the 2N5139 stage and A is

**Dual-purpose front end.** Preamplifier/isolator circuit, fed by a single antenna, drives a vlf navigation receiver and an lf broadcast-band or automatic-direction-finder receiver. The two receivers are connected to the preamp by separate coaxial cables that can be as long as 100 feet. Circuit is designed for small general-aviation aircraft, so size, weight, and cost are minimized and ruggedness is emphasized.

the gain of the 2N3819 stage. A gain of 2 or 3 at the vlf output is desirable to drive the additional filters and limiting amplifiers in the Omega receiver.

This isolating preamplifier can also be used in ground-station monitors with a single wire antenna driving two receivers, such as a WWVB 60-kHz time ref-

erence plus 100-kHz Loran C, or an Omega plus Loran C, and so forth. One of the receivers must supply power to the preamplifier, as shown in the figure. The upper frequency is limited to 1,500 kHz by the low-cost JFETs; somewhat higher-frequency performance might be achieved with JFETs such as the 2N4416.

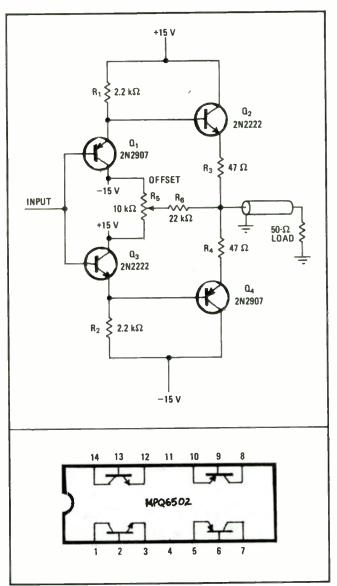

### Unity-gain stage is 50-ohm driver

by William A. Palm Control Data Corp., Minneapolis, Minn.

A recurring problem for the circuit designer is the connection of his op amp, his oscillator, or his test instrument to the low-impedance outside world. The simple buffer-driver shown here provides unity-gain class A operation, high input impedance, and 50-ohm output impedance over a wide frequency range. It also provides blast-out (short-circuit) protection and can be built with a single IC.

Because the base-to-emitter voltages of transistors Q<sub>1</sub> and Q<sub>2</sub> cancel each other, the dc voltage between input and output is near zero. With 2N2222 and 2N2907 transistors, actual offset voltage will run from 0 to 50 millivolts. This offset can be balanced out by adjustment of resistor R<sub>5</sub>.

With ±15-V supplies and the resistor values shown, this driver will deliver 10 V peak to peak, undistorted, into a 50-ohm load. Without the external load, the output will double to 20 V p-p. For total circuit protection against a shorted output and dc inputs, resistors R<sub>3</sub> and R<sub>4</sub> should be rated at 4 watts. The circuit draws about 17 milliamperes in the quiescent state.

Actual supply voltages are not critical. Resistors  $R_1$  and  $R_2$  can be changed for the appropriate drive to accommodate any supply voltages from  $\pm 5$  V to  $\pm 20$  V. For  $\pm 5$ -V supplies,  $R_1$  and  $R_2$  should be 680 ohms.

The input impedance of the circuit is a function of the gains of the transistors used. For transistors with hfe between 50 and 100, the input impedance is in the range from 50 to 100 kilohms at 1 kHz and decreases to 25 to 50 kilohms at 1 MHz. This impedance is normally high enough to offer imperceptible loading on op amps. Even a 2-kilohm potentiometer, used as an amplitude adjuster, sees only a 4% loading from low frequencies to 1 MHz.

For the circuit shown, the driver has a bandwidth of about 10 MHz when the source has an impedance of 1 kilohm. With a source impedance of 50 ohms, the frequency response is greater than 10 MHz.

A convenient means of packaging this circuit is the MPQ6502 complementary quad shown in the inset. The MPQ6502 has two 2N2222 (npn) and two 2N2907 (pnp) transistors in the handy 14-pin dual-in-line package.

**Driver delivers.** Unity-gain driver has zero offset, delivers 20 V p-p into an open circuit, or 10 V p-p into a 50-ohm load. Useful as output for op amps and test instruments, it has high input impedance, good frequency response, and low current drain. Supply voltages are not critical. The four transistors are packaged in an MPQ6502 IC.

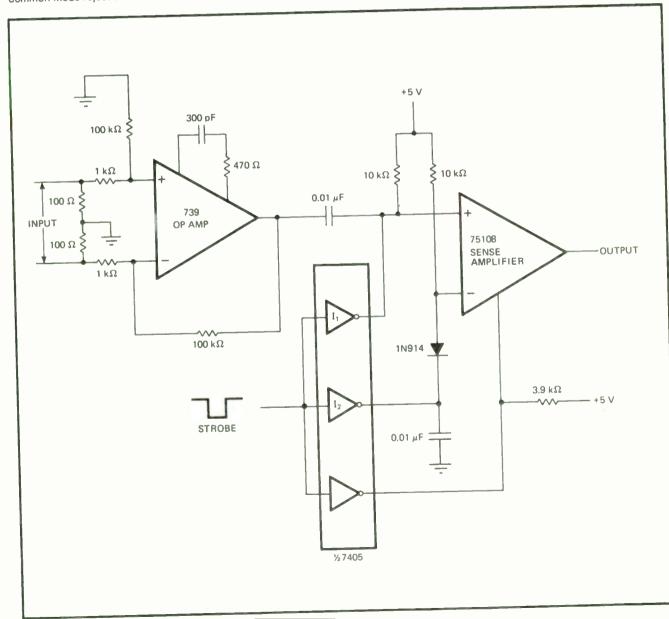

# Eliminating offset error in sense amplifiers

by Dan Chin Cambridge Memories, Newton, Mass.

A sense amplifier for a memory must detect a pulse signal during a gated time interval. But a significant error occurs at the amplifier's output when its input offset voltage is large in comparison with the voltage amplitude of the pulse signal.

If the offset voltage is removed by ac coupling, however, the pulse's baseline could shift when the readout data pattern changes. But if, in addition to being accoupled, the pulse is held to ground except during the time interval of interest, a reference voltage can be developed and the pulse compared to it.

The dc-restored sense amplifier in the figure makes use of this technique. The input operational amplifier performs as a basic linear amplifier, providing a signal gain of 100. The amplifier's output is ac-coupled to the

sense amplifier for detection.

Dc restoration is accomplished by the open-collector inverters connected to the inputs of the sense amplifier. Two of the inverters,  $I_1$  and  $I_2$ , assure that any offset voltage is applied equally to both inputs of the detector, permitting offset error to be eliminated by the detector's common-mode rejection. The diode in series with the detector's negative input sets the threshold level halfway between the pulse baseline and the minimum expected peak voltage.

**Sensing pulses, barring offset errors.** Data is ac-coupled from the operational amplifier to the sense amplifier to get rid of offset-voltage error. The dc signal level is then restored by open-collector inverter gates. Any additional offset error is eliminated by the sense amplifier's common-mode rejection because inverters I<sub>1</sub> and I<sub>2</sub>, at each of the sense amplifier's inputs, introduce equal offsets.

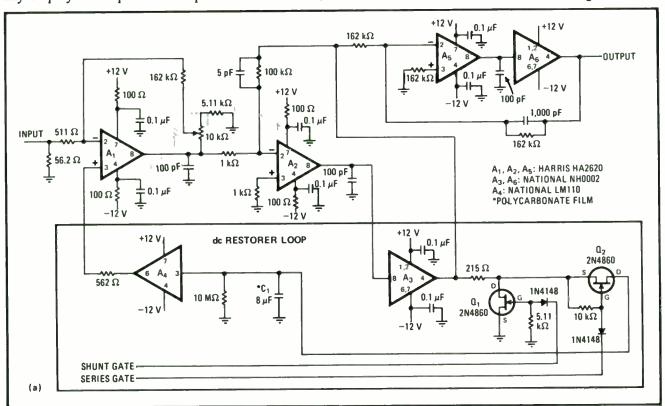

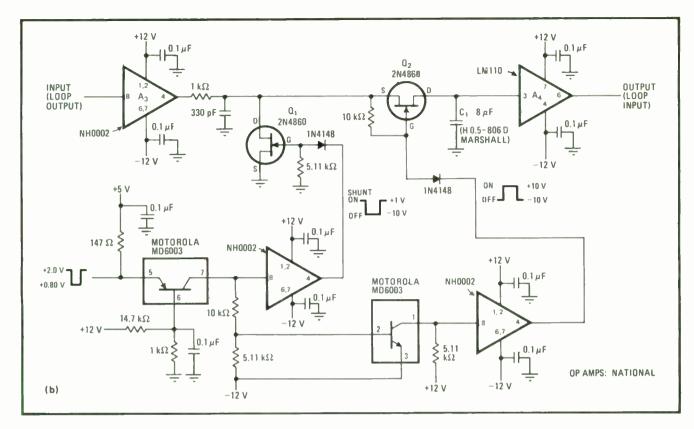

### Dc restorer for video use offers ultra-stability

by Roland J. Turner

AEL Communications Corp., Lansdale, Pa.

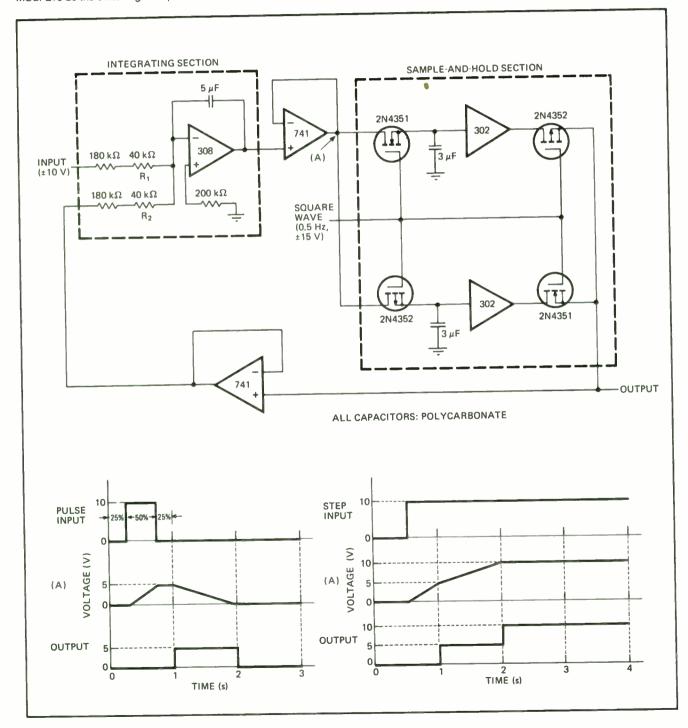

A sample-and-hold technique, along with strong degenerative feedback, permits an active dc restorer to operate with very high stability over a wide temperature range. Restoration stability can be maintained to within 30 microvolts, even in the presence of a dc offset voltage as large as 100 millivolts.

The circuit is useful in radar applications, where it is often essential to peak-detect or integrate video signals relative to a stable dc reference. This is especially true if the video sensor contains diodes that have a tempera-

ture-dependent offset voltage.

The dc restoration must be performed without any temperature-induced offset voltage, since dc coupling must be preserved in the video processing (peak detection or integration) following dc restoration. Accurate signal detection, then, heavily depends on providing a stabilized dc restoration level. The video output signals must be independent of any thermal variations that may occur in the video detector and dc restorer.

Conventionally, a dc restorer operates at relatively high signal levels and requires considerable video gain prior to dc restoration. Moreover, a dc restorer generally employs a temperature-compensated zener diode, and two matched diodes to keep the dc restored level relatively constant over a wide temperature range. But even with the best matched diodes and the most stable temperature-compensated zener, the dc restored level cannot be made more stable than  $\pm 10$  mV over a  $100^{\circ}$ C temperature range. With the dc restorer shown here, however, stabilities of  $30~\mu V$  can be established at extremely low video levels.

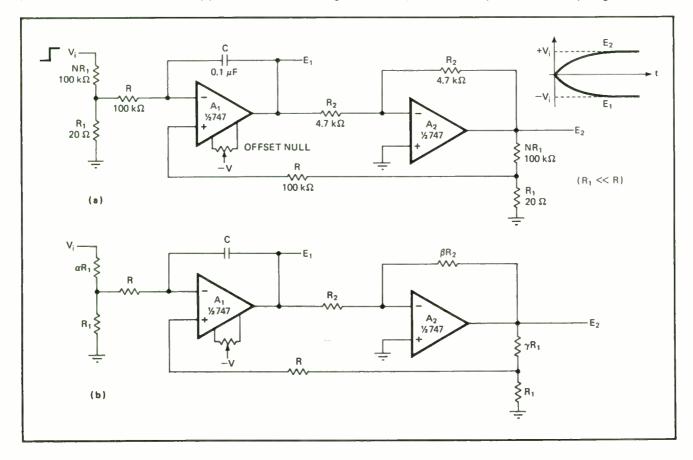

A complete video amplifier employing this improved de restoration technique is drawn in (a). In this circuit's sample-and-hold scheme, the de output of a de-coupled amplifier is sampled over a 50-microsecond gating interval. It should be noted that de coupling must be maintained from the input (sensor) through to the output integrator or peak detector. As a result, de signal changes longer than the sensor's thermal time constant, which is typically less than 10 milliseconds, can be recognized as a valid signal/target by the peak detector or integrator.

The full schematic of the dc-restorer section of the video amplifier is given in (b). During the dc-restoration interval, the FET shunt gate,  $Q_1$ , is open, while the FET series gate,  $Q_2$ , is closed. During the gating interval, sampling capacitor  $C_1$ , which is a highly temperature-stable polycarbonate-film capacitor, charges to the average noise level present at the output of amplifier A.

When the sampling gate is closed, the circuit's sampling process activates a degenerative-feedback loop that forces the average signal value at  $A_3$ 's output to approach the signal-noise level. In effect, the dc level at the noninverting terminal of input amplifier  $A_1$  is forced to match the dc level at  $A_1$ 's inverting terminal to

**Emphasizing stability.** Dc restoration loop of video amplifier (a) allows the amplifier to match dc input levels to within 30 microvolts, in spite of widely varying temperatures. The sample-and-hold circuitry of the dc restorer loop is shown in (b). During the gating interval, which is 50 microseconds long, FET shunt gate  $Q_1$  is off, FET series gate  $Q_2$  is on, and capacitor  $C_1$  (a temperature-stable unit) charges.

within 30  $\mu$ V. During the signal processing interval, when shunt FET gate  $Q_1$  is on and series FET gate  $Q_2$  is off, the voltage across capacitor  $C_1$  establishes an ultrastable dc-restored level at the positive input to amplifier  $A_1$  as a reference for detecting whatever video signals may be present at the negative input of  $A_1$ .

To realize a high degree of dc-restoration stability within the gating aperture, it is essential to select op amps for amplifiers A<sub>1</sub> and A<sub>2</sub> that have fast slew rates. This is why Harris' type HA2620 op amp, which has a gain-bandwidth product of greater than 30 megahertz, is used for both A<sub>1</sub> and A<sub>2</sub>. Amplifier A<sub>4</sub> is a high-stability buffer that serves as a high-input-impedance load for the sampling capacitor, C<sub>1</sub>.

This active dc restorer can reduce a 100-mV dc offset at the sensor to an equivalent dc offset of less than 30  $\mu$ V. And because of the low leakage of the sampling

gate, the stored charge on capacitor  $C_1$  is not disturbed during the hold interval, even if a 10-v signal is present at the gate input.

The forward gains (80 decibels) of amplifiers A<sub>1</sub>, A<sub>2</sub>, and A<sub>3</sub> contribute to the degenerative-feedback loop during the dc restoration interval, forcing A<sub>1</sub>'s positive input to follow the dc offset present at A<sub>1</sub>'s negative (sensor) input. The circuit's integrating stage containing amplifiers A<sub>5</sub> and A<sub>6</sub> must be placed outside the dc-restoration loop, since the fast slew rate of the forward-control loop must be preserved during the dc restoration interval.

For the circuit to operate properly, the input-signal condition must be known during the dc-restoration interval. In radar systems, this time occurs between pulse transmission and signal reception; for television signals, this time occurs during the sync tip transmission.

### CATV transistors function as low-distortion vhf preamplifiers

by Paolo Antoniazzi Societá Generale Semiconduttori, Milan, Italy

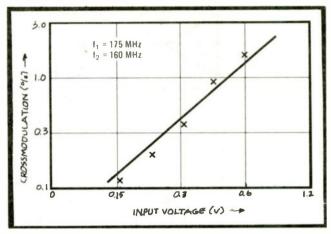

A standard cable-TV transistor makes an excellent vhf preamplifier, minimizing signal distortion over a wide dynamic range. Generally, FETs or MOSFETs are used rather than bipolar transistors because of the crossmodulation distortion created by the nonlinear behavior of the bipolar's base-emitter junction. CATV transistors, however, operate at currents of 20 to 80 milliamperes, so that their intrinsic emitter resistance is kept small and the effects of input-junction nonlinearities are eliminated.

The single-stage antenna preamplifier shown is intended for mobile fm communications applications and is particularly suitable for use with double-balanced Schottky-diode mixers. It obtains 13 decibels of gain at 175 megahertz from a medium-power CATV transistor.

The circuit can handle 0.5-volt inputs with less than 1% cross-modulation, as indicated by the performance plot. Noise figure depends on how large the operating current is. But even for a transistor collector current of

50 mA, the noise figure is typically 5 dB or less.

The transistor used here is designed principally for line-amplifier applications. Its crossover frequency is

(75 C) OUT fo = 175 MHz BANDWIDTH = 40 MHz 3 TURNS 10 BFR36 (75.52) 330 pF 1,000 pF 1.5 kΩ 56 Ω 1.000 nE ≨ 330 Ω 18 V (55 mA)

1.5 gigahertz, its operating current can range from 20 to 150 mA, and its feedback capacitance is typically 1.7 picofarads at a bias voltage of 15 v.

Linear performer. Bipolar CATV transistor is heart of vhf antenna preamplifier that can process 0.5-volt inputs with under 1% cross-modulation. The nonlinearities that are normally associated with a bipolar transistor's base-emitter junction and that cause signal distortion are practically eliminated in the CATV transistor because of its high operating current. Circuit gain is 13 dB at 175 MHz.

# High-speed voltage-follower has only 1-nanosecond delay

by O.A. Horna

COMSAT Laboratories, Clarksburg, Md.

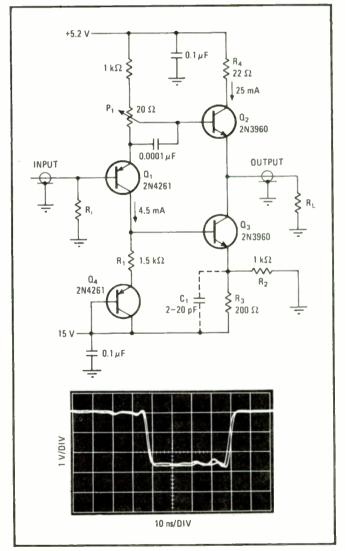

When a voltage-follower is needed for isolation and/or impedance transformation in fast analog circuits, a simple emitter-follower can be made to give better performance than an integrated operational amplifier. A dual complementary emitter-follower overcomes the disadvantages of the conventional emitter-follower—its input-to-output offset voltage and its relatively low voltage gain. Propagation delay for this complementary circuit is less than 1 nanosecond.

The first emitter-follower, pnp transistor  $Q_1$ , drives a second emitter-follower, npn transistor  $Q_2$ , so that the offset (emitter-base) voltages of these transistors are opposite in polarity. The dc voltage difference between input and output terminals is therefore very small and can be adjusted to almost zero with potentiometer  $P_1$ . Transistors  $Q_1$  and  $Q_2$  should make good thermal contact with each other to compensate for the temperature dependence of their emitter-base voltages.

Output transistor  $Q_2$  is loaded by a variable current source, npn transistor  $Q_3$ , the base of which is connected to the collector of transistor  $Q_1$ . For a given bias current

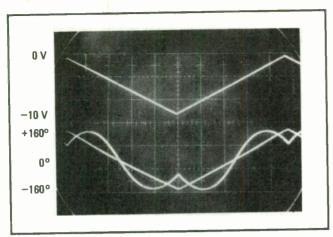

Fast emitter-follower. Back-to-back emitter-followers, transistors  $Q_1$  and  $Q_2$ , are complements, causing their opposite-polarity offset voltages practically to cancel. (Potentiometer  $P_1$  permits fine offset zero adjustment.) Transistor  $Q_3$  is a variable-load current source, while transistor  $Q_4$  is wired as a diode for  $Q_3$ 's temperature compensating. Scope display shows superimposed input and output signals.

(25 milliamperes here), transistor  $Q_2$  can then deliver nearly twice as much current to the load as would be possible with a constant-current source. The last transistor,  $Q_4$ , is connected as a diode to temperature-compensate transistor  $Q_3$ 's emitter-base voltage.

When the input voltage goes positive, the emitters of transistors  $Q_1$  and  $Q_2$  also become positive. The current through transistor  $Q_1$  decreases, dropping the voltage across resistor  $R_1$  as well as the current through transistor  $Q_3$ . The opposite action occurs for a negative input.

The voltage gain of transistors  $Q_1$  and  $Q_3$  can be made greater than unity (between 1.1 and 1.2) by adjusting the resistance ratio of resistor  $R_2$  to resistor  $R_3$ . This compensates for the voltage gain of transistors  $Q_1$  and  $Q_2$ , which is less than unity (between 0.9 and 0.95). With an unloaded output, the circuit's total stable voltage gain ranges from 0.985 to 0.995, and the output resistance is less than 1 ohm. (The output is protected against short circuits by resistor  $R_4$ .)

The scope trace shows the circuit's input and output voltages superimposed on each other. With a load resistor of 50 ohms and an output voltage of ±2.5 volts,

the circuit's propagation delay is less than 1 nanosecond, and the rise and fall times are smaller than 2 ns without overshoot. The maximum voltage swing is ±4 V, the bandwidth is approximately 200 megahertz, and the slew rate is over 2 kilovolts per microsecond.

When the load resistance is less than 200 ohms, the circuit's transient response and the bandwidth can be substantially improved by adding a speed-up capacitor, C<sub>1</sub>. However, under a no-load condition, when the load resistance is 500 ohms or more, this capacitor can cause the circuit to oscillate.

All four discrete transistors can be replaced by a single quad package, Motorola's MHQ6001, which contains two pairs of pnp and npn transistors. Since these transistors have a gain-bandwidth product of only 400 MHz, as opposed to 1 gigahertz for the discretes, the circuit's propagation delay and rise and fall times will be three to four times longer.

For the bias currents given in the figure, the dc source resistance, R<sub>i</sub>, must be less than 2 kilohms. The circuit's input resistance is greater than 50 kilohms for load resistances of 50 ohms or more.

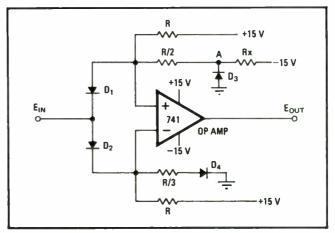

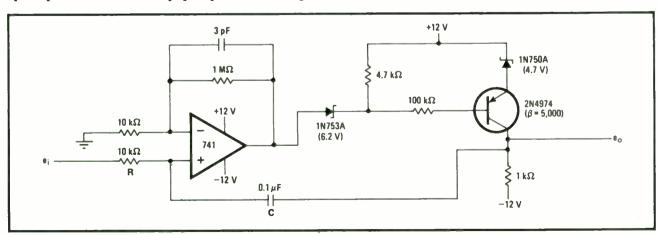

# Getting power and gain out of the 741-type op amp

by Pedro P. Garza, Jr. General Electric Co., Apollo and Ground Systems, Houston, Texas

The popular 741-type operational amplifier can be used as the basis for a high-voltage power amplifier that is capable of delivering 22 watts of peak power at an output voltage swing of 60 volts. Voltage gain for the amplifier is 10, and its frequency response is flat from dc to 30 kilohertz.

Most integrated-circuit op amps are not designed to accept more than 36 v across their power pins. Here, therefore, transistors  $Q_1$  and  $Q_2$  protect the 741-type op amp by maintaining a 30-v differential across the device's power pins. The base of transistor  $Q_1$  is biased at 15 v by the voltage divider network formed by the 3-kilohm resistors, while  $Q_1$ 's emitter is at 15 v minus its base-emitter voltage drop. The biasing arrangement for transistor  $Q_2$  is similar.

Since a 39-ohm resistance (resistor R<sub>1</sub>) is connected to the op amp's push-pull output, substantial currents will be drawn by the device. Currents i<sub>1</sub> and i<sub>2</sub>, which appear at the collectors of Q<sub>1</sub> and Q<sub>2</sub>, are used to generate the base drive voltage for the power-output stage, made up of transistors Q<sub>3</sub> and Q<sub>4</sub>. The power-output stage has a wider frequency response than the 741-type op amp. The negative feedback path through capacitor C<sub>1</sub> provides a frequency roll-off characteristic similar to that of the op amp, thus assuring unconditional stability.

The resistance ratio of resistor  $R_3$  to resistor  $R_2$  determines the amplifier's voltage gain. If the op amp's input-offset voltage is nulled out and resistors having tolerances of  $\pm 0.25\%$  are used for  $R_2$  and  $R_3$ , the power amplifier's linearity error will be within 0.4% over the output voltage range of  $\pm 29.8$  v to  $\pm 29.8$  v.

+30 V 160 Ω 3 kΩ 2N5876 2N3642  $3\,k\Omega$ 10 pF  $R_3$  $R_2$  $56~k\Omega$  $5.6~k\Omega$ 5600 pF FAIRCHILD μA741 ≥ R<sub>L</sub> ≥ 40 Ω ≥ 39 Ω  $5.6 k\Omega$ 2N2905 2N5878 **≶3**kΩ ≷ 160 Ω -30 V

**Power amplifier.** Widely used 741-type op amp is heart of 22-watt power amplifier that supplies 60-volt output swing. Transistors  $Q_1$  and  $Q_2$  keep peak-to-peak voltage across op amp's power pins at 30 V so that device's 38-V rating is not exceeded. Using low-value load resistor  $(R_1)$  at op-amp output produces currents  $(i_1$  and  $i_2)$  large enough to drive output power stage of transistors  $Q_3$  and  $Q_4$ .

Output voltage swings of more than 60 v are possible if transistors with higher collector-base breakdown-voltage ratings are used along with higher power supply voltages.

World Radio History

### High-gain triple Darlington has low saturation voltage

by Eric Burwen

G&S Systems Inc., Burlington, Mass.

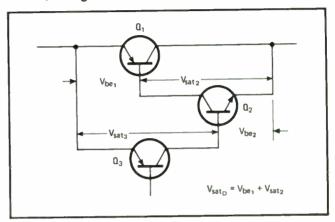

A triple Darlington amplifier can be useful in situations that require a minimum of base drive, such as high-efficiency switching regulators or buffer amplifiers with high input impedance. Combining very high current gain and a saturation voltage equal to that of the two-transistor Darlington, this circuit was originally conceived for use in high radiation environments, where the  $\beta$  parameter of a transistor can readily degrade to 5 or even less.

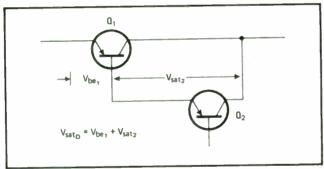

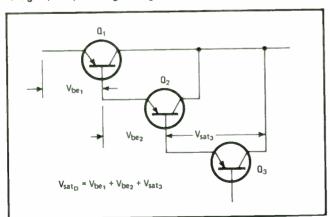

In the conventional Darlington amplifier (Fig. 1), the total saturation voltage is the sum of the base-to-emitter voltage of Q<sub>1</sub> and the saturation voltage of Q<sub>2</sub> alone. Although no transistor or circuit attains the ideal 0-volt saturation voltage, that of the Darlington amplifier is suitably low. But if three transistors of like polarity were cascaded (Fig. 2), the V<sub>sat</sub> of the resulting amplifier would be nearly double that of the conventional two-transistor circuit.

On the other hand, a triple Darlington made of complementary transistors (Fig. 3) has the same saturation voltage as that of the double Darlington. This is true whenever the saturation voltage of  $Q_3$  taken alone is

1. Conventional. Two-transistor Darlington amplifier has high current gain, compensating for degraded  $\beta$ , and low saturation voltage.

2. Unsatisfactory. Simply cascading three similar transistors gives a saturation voltage that is much too high.

less than or equal to the combination of:

$V_{\rm be1} + V_{\rm sat2} - V_{\rm be2}$

Because the current gain of the triple Darlington is large, the currents in  $Q_1$  and  $Q_2$  are large, so that these three voltages do in fact add up to a level larger than  $V_{\text{sat3}}$  alone. (When  $Q_3$  is in the circuit, of course, its saturation voltage is exactly equal to the combination, by Kirchhoff's law.)

In an experimental version of the triple Darlington (Fig. 4), a current of 8 microamperes controls a load of 2 amperes—a gain of 250,000. The saturation voltage at 2 A is 1.2 volts, the sum of  $V_{be1} = 0.9 \text{ v}$  and  $V_{sat2} = 0.3 \text{ v}$ . Transition times are  $t_{on} = 200$  nanoseconds and  $t_{off} = 500$  ns; storage time is 1 microsecond.

3. Triple Darlington. Making the circuit out of two pnp and one npn transistors gives high gain without boosting saturation voltage.

**4. Switching-time test circuit.** Gain is 250,000 in this circuit. The 10-ohm resistor (color) is required to limit the current in  $Q_3$ ; otherwise, when that transistor saturates, its large current will pass through the base of  $Q_2$  and reduce the  $\beta$ .

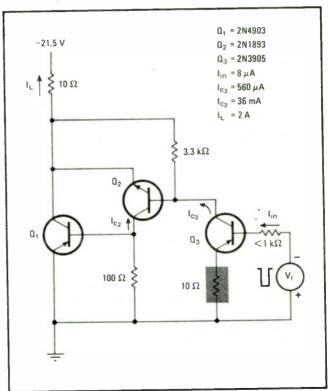

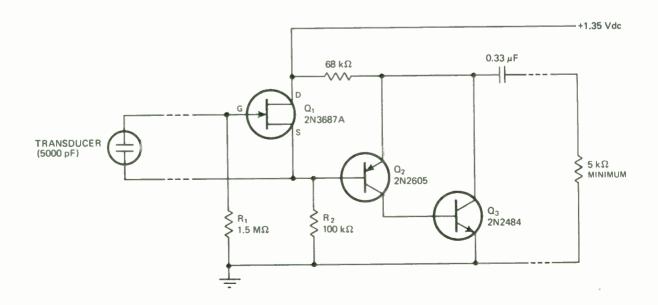

### Transducer preamplifier conserves quiescent power

by Robert F. Downs

Ocean & Atmospheric Science Inc., Santa Ana, Calif.

A low-voltage micropower preamplifier holds power dissipation to approximately 13 microwatts because of the low bias current of its two-transistor impedance converter output stage. The preamplifier, which is intended for use with a capacitive transducer, operates at a quiescent current of 10 microamperes with a supply voltage of only 1.35 volts.

The gate of field-effect transistor  $Q_1$  is essentially biased at 0 v through resistor  $R_1$ . Negative feedback, provided by resistor  $R_2$ , maintains  $Q_1$ 's gate-to-source voltage at approximately -0.4 v, forcing its drain current to less than  $4\mu$ A. Resistor  $R_2$ , therefore, contributes significantly to  $Q_1$ 's bias stability.

Preamplifier input impedance depends on both  $R_1$  and the voltage gain of the field-effect transistor stage. Actual FET intrinsic input impedance can be ignored since it is orders of magnitude larger than  $R_1$ .

If  $e_i$  denotes input signal voltage, the voltage across  $R_1$  can be expressed as  $e_i(1+K_v)$ , where  $K_v$  is the stage's voltage gain. Since current through  $R_1$  is in-

creased by a factor of  $1 + K_v$ , the apparent input impedance is  $R_1/(1+K_v)$ .

On a small-signal basis, then, the preamplifier's input stage is equivalent to a common-source configuration, while the bias arrangement is that of a source-follower. For the over-all circuit, the dc input impedance is around 1.5 megohms, while the ac input impedance is about 300 kilohms.

The FET selected for this circuit should have a low pinch-off voltage ( $V_P$ ) and a low drain current ( $I_{DDS}$ ) when the gate-source junction is shorted. For the device used,  $V_P$  is about 0.1 V and  $I_{DSS}$  approximately 100  $\mu$ A. Because a FET's transconductance ( $g_m$ ) depends on drain current,  $Q_1$ 's  $g_m$  is only around 50 micromhos.

Since the FET's output conductance is negligible, its output impedance, like that of a common-source stage, essentially equals  $R_2$ . Because this is a high resistance value, two bipolar transistors,  $Q_2$  and  $Q_3$ , are used as an impedance converter.

This converter stage operates like a pnp emitter-follower, providing very high values of current gain and input impedance. Moreover, it realizes greater bias voltage compatibility between the FET and bipolar stages than a conventional Darlington pair could. Converter bias current is about 6  $\mu$ A, input impedance exceeds 2 megohms, and output impedance is about 4 kilohms.

For the preamplifier, equivalent input broadband noise is relatively low, about 33  $\mu$ V from 140 hertz to 20 kilohertz. And voltage gain is nominally 5 (14 decibels).

**Power pincher.** Preamplifier for capacitive transducer input dissipates only 13 microwatts and operates from 1.35-volt supply. Bias current of impedance converter, composed of bipolar transistors  $Q_2$  and  $Q_3$ , is only 6 microamperes, keeping total circuit current drain to only 10  $\mu$ A. FET input stage has source-follower bias arrangement but provides voltage gain of common-source configuration.

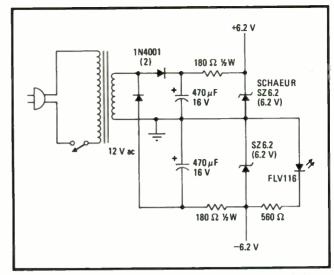

### Two ICs make low-cost video-distribution amp

by M. J. Salvati Sony Corp. of America, Long Island City, N.Y.

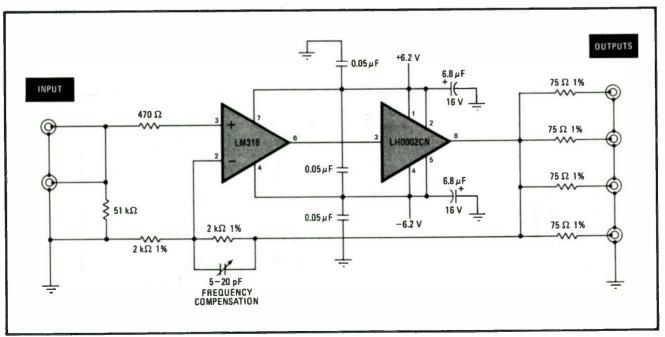

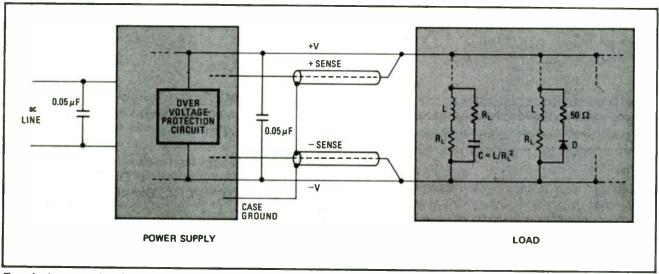

For less than \$25 in parts, a video distribution amplifier can be constructed with all the features of commercial models selling for over \$300. The circuit shown in Fig. 1 takes the 1-volt peak-to-peak output of a standard video signal generator or TV camera and provides four or more independent outputs that each deliver 1-v pk-pk video into 75-ohm loads. Two input connectors are mounted in parallel because the 50-kilohm impedance is high enough to permit "loop-through" connection, in which a second distribution amplifier is paralleled with the first by means of the second connector. If not used for loop-through, the second connector should be terminated with 75 ohms. The frequency response of the unit is flat from dc to 4 megahertz.

The video distribution amplifier circuit in Fig. 1 uses a National LM318 high-speed operational amplifier and a National LH0002CN current driver in a feedback loop. The resulting output impedance is so low that the output approximates a zero-impedance voltage source, so loads connected to the output resistors have no effect on each other. The 75-ohm output resistors provide the proper drive-source impedance for coaxial cable, short-circuit protection for the LH0002CN, and increased isolation between loads.

The only adjustment required is the frequency-response compensation capacitor. This trimmer is set to

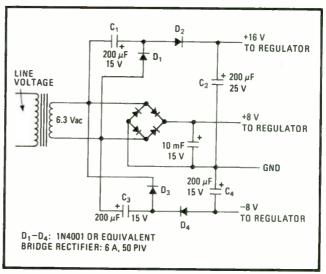

2. Power supply. Compact supply uses zener-diode regulation to provide  $\pm 6.2$  volts required for video distribution amplifier. This power supply and the amplifier shown in Fig. 1 are capable of driving more outputs than the four shown.

provide the same output amplitude with a 1-MHz sinewave input as is obtained with a 10-kilohertz sine wave input.

The 6.8-microfarad bypass capacitors should be tantalum electrolytics and should be installed close to the LH0002CN pins. The 0.05- $\mu$ F bypass capacitors should be disk ceramics installed as close to the LM318 pins as possible. The 75-ohm and 2-kilohm precision resistors must be noninductive types, such as metal film or carbon film.

The outstanding feature of this design is the low cost of the ICs implementing it. Although the slewing ability

1. Video distribution amplifier. Signal from TV camera or video signal generator is amplified to provide 1 v peak-to-peak at each of four outputs matched to 75-ohm loads. Second input connector can be used for "loop-through" connection of a second distribution amplifier or for a terminating resistor. Frequency-compensation adjustment balances stray capacitances, providing flat response from dc to 4 MHz.

of the LM318 is insufficient to handle reliably a 2-v pk-pk output swing at 4 MHz, the amplitude of the highest-frequency component (color burst) in a standard composite video signal is only a small percentage of the overall amplitude, so the LM318 can easily handle a standard video signal.

The power supply recommended for use with this amplifier is shown in Fig. 2. Fig. 3 shows the complete video distribution amplifier and power supply unit

packaged in a metal box.

3. All packed up and ready to go. Amplifier-and-power-supply unit for 4-way distribution of video signals is packaged in metal box. Parts cost for complete assembly is less than \$25.

### 2. Analog-digital converters

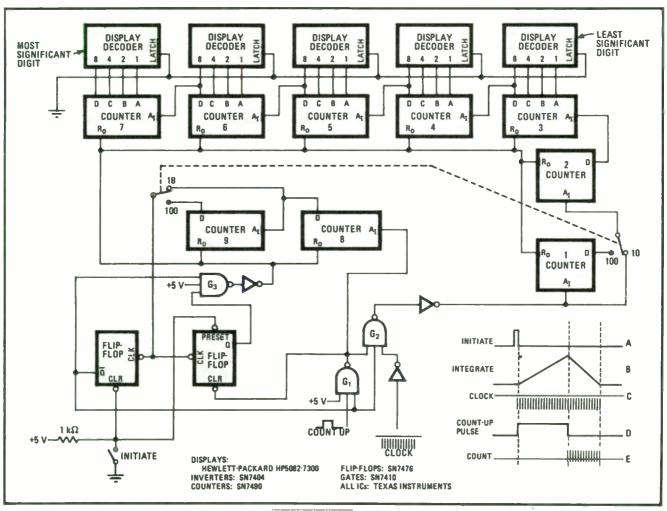

### Adding automatic zeroing to analog-to-digital converter

by Tom Birchell

Advanced Electronic Controls, Fremont, Calif.

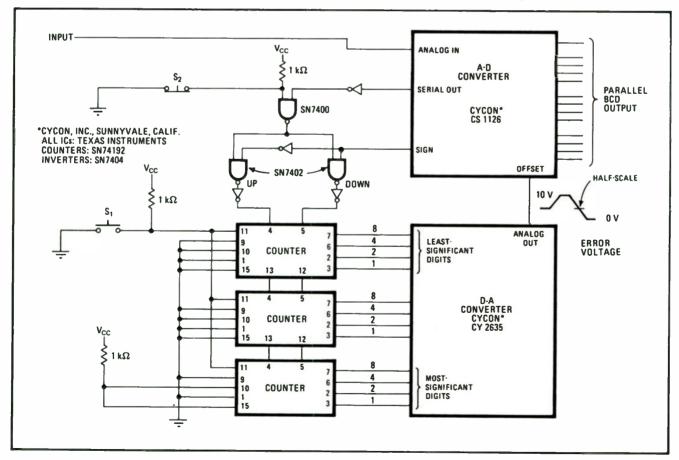

Automatic zeroing can easily be added to a countingtype analog-to-digital converter by using up/down decade counters and a digital-to-analog converter to generate an error-correction signal. The automatic zero function can be especially useful in a-d applications involving strain gages or other sensors where mechanical considerations can cause minute-to-minute changes in the effective zero point.

Normally, a zero-setting potentiometer must be adjusted constantly, but with the closed logic servo loop shown, it is only necessary to depress a pushbutton switch to produce the activating logic signal. Essentially, the circuit employs the pulse train occurring at the serial output of the counting-type a-d converter to generate

an error voltage. This error voltage is then fed back to the offset-adjustment input of the a-d converter to correct this device's zero setting.

Switch S<sub>1</sub> (which is optional) loads the four-bit synchronous decade counters with a starting number for calibration purposes. Here, the half-scale point of the d-a converter's output is chosen as the calibration number to obtain a symmetrical correction range. If the expected offset variations will occur predominately in one direction, the calibration number should be selected to optimize the correction range.

Once the decade counters are preloaded, switch S<sub>2</sub> initiates the correction cycle. When switch S<sub>2</sub> is depressed, the pulses from the serial output of the a-d converter drive the decade counters either up or down, depending on the error polarity, which is determined by the sign bit. The output voltage of the d-a converter changes accordingly, adjusting the offset input of the a-d converter until no more pulses are produced at this device's serial output. The circuit is now adjusted to the true digital zero point.

For this circuit, the nominal adjustment range is  $\pm 7\%$  of the full range of the a-d converter.

**Eliminating offset error.** Closed servo loop containing decade counters and digital-to-analog converter automatically zeroes the offset voltage of analog-to-digital converter. Pulse train from the a-d converter's serial output is used to generate the error voltage. Depending on the sign bit, the counters are driven up or down, adjusting the d-a converter's output and, therefore, the offset input of the a-d converter.

### Logic system checks out analog-to-digital converter

by Charles J. Huber Westinghouse Electric Corp., Systems Development Div., Baltimore, Md.

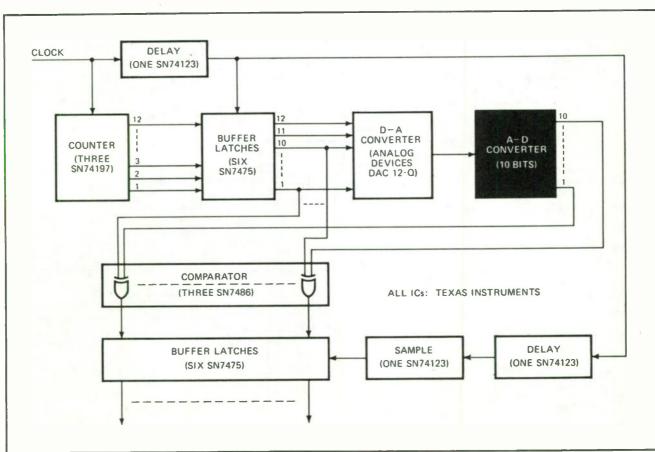

Testing the conversion accuracy of an analog-to-digital converter need not be a laborious and time-consuming task. The test configuration shown can reduce the job to a go/no-go operation without undue expense (approximately \$36 for integrated circuits plus the cost of a digital-to-analog converter).

This test system produces a 12-bit digital ramp that is converted (by the d-a converter) to a 4,096-step analog ramp. The analog ramp is applied to the a-d converter under test, and the resulting output from the 10-bit a-d converter is compared to the 10 most significant bits of the 12-bit digital ramp.

An input clock is applied simultaneously to a oneshot delay network and to a ripple-through counter consisting of three four-bit binary counters. The delayed clock becomes the input for six four-bit buffer latches. These accept and delay all 12 of the bit outputs from the counter to remove glitches from the digital ramp. The delayed clock now acts as the basic time reference. The 10 most significant bits from the latches drive both a d-a converter and a comparator formed by three quad exclusive-OR gates. These gates compare the bits of the digital ramp to the output bits of the a-d converter, on an individual basis. The analog output of the d-a converter corresponds to the input digital code within ±% the least significant bit.

The delayed clock pulse also passes through another one-shot delay network before reaching a sample circuit, which strobes a second set of buffer latches. For zero error at the buffer outputs, the minimum strobe delay equals the a-d conversion time. An interpolating voltage applied to the d-a permits continuous voltage control of the a-d output over the 1/8-bit range.

The test system can accurately determine conversion times of 2 microseconds for successive-approximation and variable-reference a-d converters. Additionally, the nature and position of other conversion errors can be determined by relating displayed error pulses to the digital ramp. For example, small areas of the ramp can be investigated by making constants of the 10 most significant bits of the digital input and using the eleventh and twelfth bits as variable controls.

More system flexibility can be obtained by using an up/down counter to eliminate the d-a converter's slew time when the count changes from 111 . . . 1 to 000 . . . 0. Replacing the counter with a pseudo-random generator allows testing for all input changes.

**Verifying converter accuracy.** A-d converter test system generates 12-bit digital ramp with ripple-through binary counter. Buffer latches smooth out any ramp glitches. D-a converter then develops analog input for a-d converter using only 10 most significant ramp bits. Exclusive-OR gates compare a-d output with ramp. Errors pass to another buffer for comparison with appropriately delayed clock.

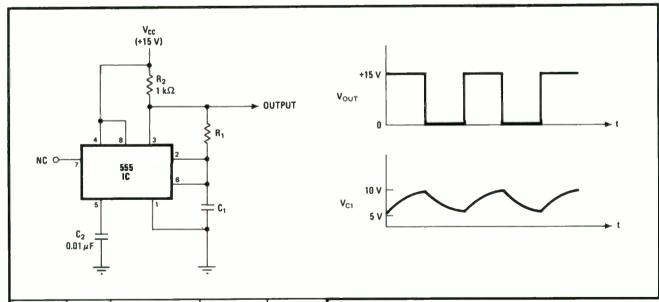

### Height-to-width converter digitizes analog samples

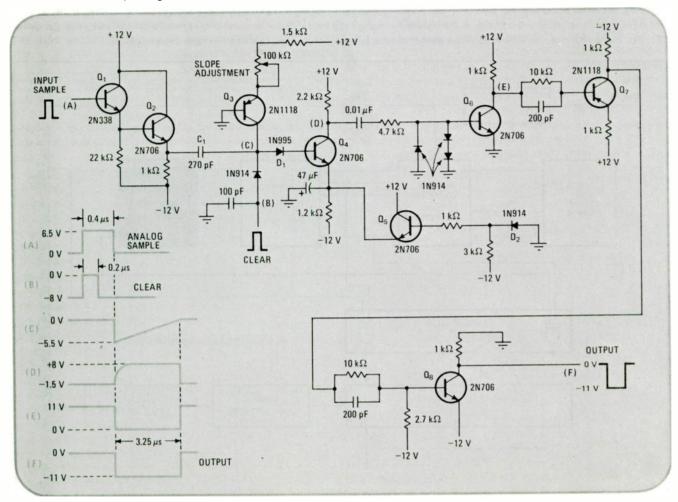

by Roland J. Turner RCA Corp., Missile and Surface Radar division, Moorestown, N.J.

By controlling the charge on a storage capacitor, a temperature-stabilized height-to-width converter can produce a gray code output from an analog input sample. The converter uses a differential diode-transistor arrangement to operate over a temperature range of -55°C to +65°C, and its conversion error is less than 0.15 microsecond for a full-scale output pulse width of 3.25 us.

During the first half of the input sample, a clear pulse removes all charge from storage capacitor  $C_1$ . During the second half, a charge proportional to the sampled analog signal is placed on this same capacitor through transistors  $Q_1$  and  $Q_2$ .

Current source  $Q_3$  keeps diode  $D_1$  forward-biased and transistor  $Q_4$  fully on during the sample time. On the trailing edge of the analog sample,  $D_1$  becomes re-

verse-biased by a voltage level equal to the amplitude of the analog sample before its termination. Transistor  $Q_4$  is then cut off, and for a period of time that is proportional to the stored analog sample amplitude, a current source formed by  $Q_3$  and the slope-control potentiomteter linearly discharges capacitor  $C_1$ .

During the time that  $Q_4$  is off, the converter generates a pulse that has a width proportional to the amplitude of the analog sample. When the stored charge goes to zero, diode  $D_1$  and transistor  $Q_4$  are again turned on by the current source. After  $Q_4$  conducts, a new sample may be processed. Transistors  $Q_6$ ,  $Q_7$ , and  $Q_8$  act as pulse shapers to yield the desired output.

Diodes  $D_1$  and  $D_2$  and transistors  $Q_4$  and  $Q_5$  are connected in a differential configuration to keep  $Q_4$ 's conduction interval independent of temperature variations. The voltage drops of  $D_1$  and  $D_2$  and the base-emitter voltage drops of  $Q_4$  and  $Q_5$  track each other as temperature varies.

The converter in the diagram is designed to operate with a peak-to-peak video input level of 6.5 volts. Maximum output pulse width is determined by the slope adjustment, which is set to provide a pulse width of 3.25  $\mu$ s for a an input video level of 6.5 v. The waveforms shown represent the maximum level of the gray code.  $\square$

Compensating for temperature. Differential hook-up of transistors  $Q_4$  and  $Q_5$  and diodes  $D_1$  and  $D_2$  maintains temperature stability of height-to-width converter. Amplitude of analog input sample is converted to gray code output. Second half of input sample charges capacitor  $C_1$ , then linear current ramp through transistor  $Q_3$  discharges  $C_1$ . During discharge time,  $D_1$  and  $D_2$  are off, and output pulse is produced.

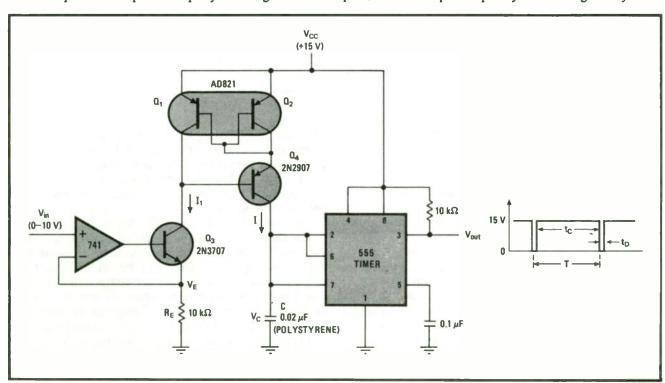

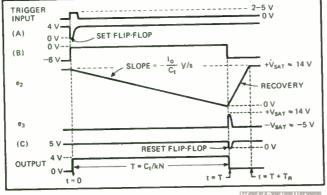

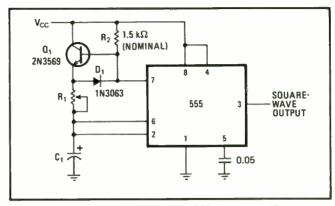

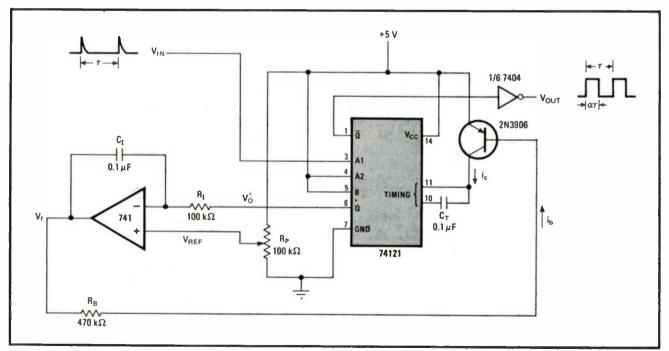

### Current source and 555 timer make linear v-to-f converter

by Andrew McClellan

Case Western Reserve University, Cleveland, Ohio

In many situations it is desirable to linearly control the output frequency of a 555 timer circuit by adjusting a potentiometer or an input voltage. In the conventional astable configuration of the 555, the timing capacitor discharges and charges through one or two timing resistors. Thus the frequency is inversely related to changes in the timing components, and is also inversely related to changes in the control voltage.

However, inexpensive and accurate linear voltage-to-frequency conversion can be obtained from the 555 astable multivibrator circuit in Fig. 1. A voltage-dependent current I linearly charges the timing capacitor C so that output frequency increases linearly with the input control voltage  $V_{\rm in}$ . During the charging phase of the cycle the capacitor voltage is given by:

$$V_{\rm C} = V_{\rm CC}/3 + It/C$$

Charging continues until  $V_C$  reaches  $2V_{CC}/3$ , making charging time  $t_c$  equal to  $V_{CC}C/3I$ .

At this point the capacitor rapidly discharges back to

$V_{\rm CC}/3$  through the ON resistance  $R_{\rm CE}$  of the discharge transistor in the timer (pin 7). The discharge time,  $t_{\rm d}$ , is approximately equal to  $0.69R_{\rm CE}C$ .

The circuit is designed to make t<sub>c</sub> much greater than t<sub>d</sub>, so the period T of the multivibrator is very nearly equal to t<sub>c</sub> and the frequency f becomes:

$$f = 3I/V_{\rm CC}C$$

The 741 operational amplifier and transistor Q<sub>3</sub> form a voltage-dependent current source such that:

$$I_1 = (V_E/R_E)[\beta_3/(\beta_3 + I)] = V_{in}/R_E (approx.)$$

where  $\beta_3$  is the forward current transfer ratio of  $Q_3$ . The op amp greatly reduces any drift due to change of  $V_{BE}$  in  $Q_3$ .

To allow the input voltage  $V_{\rm in}$  to be referenced to ground, the capacitor is actually charged by current I from the current mirror formed by  $Q_1$ ,  $Q_2$ , and  $Q_4$  that makes I equal to  $I_1$ . The transistor  $Q_4$  functions in a modified cascode configuration to increase the output impedance of the current source and increase the tracking of  $I_1$  and I. Substituting  $V_{\rm in}/R_{\rm E}$  for I in the frequency equation gives:

$$f = 3V_{\rm in}/R_{\rm E}CV_{\rm CC}$$

For a maximum input control voltage of 10 volts and the parameters used, the charging current can be easily varied over a range from 10 microamperes to 1 milliampere, and the output frequency in hertz is given by:

1. Linear voltage tuning. Inexpensive linear voltage-to-frequency converter uses an op-amp-driven transistor current source and a current mirror to charge the timing capacitor in a 555 astable multivabrator circuit from control voltage V<sub>in</sub>.

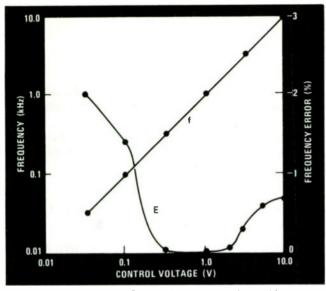

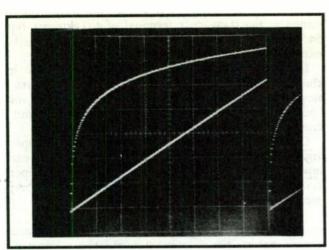

2. Straight and accurate. Graphs show the experimental frequencyversus-voltage relationship, and the percentage departure from linearity, obtained with the circuit in Fig. 1.

$$f = 10^3 V_{\rm in}$$

The experimentally obtained frequency and accuracy are shown in Fig. 2. At high frequencies (10 kilohertz) the non-zero discharge time (t<sub>d</sub>) becomes significant and tends to make the frequency less than the predicted value. At low frequencies (100 hertz) the decreased transistor betas and the bias currents of the comparators (pins 2 and 6) decrease the voltage-to-current conversion factor and tend to also make the frequency less than the predicted value. This latter error may be compensated for to some degree by adjusting the offset of the 741 so that  $V_E = V_{in} + 1.5$  mV. This has the effect of increasing the conversion factor at low input voltages without seriously affecting the accuracy at larger input voltages. Here this technique reduces the error in the 100-Hz region to less than  $\pm 0.4\%$ .

For higher-frequency operation (1-100 kHz), it's better to reduce capacitor C to 0.002 microfarad, rather than decrease R<sub>E</sub>; otherwise the ratio of t<sub>d</sub> to t<sub>c</sub> would become too large, and errors would result at the high end of the frequency range.

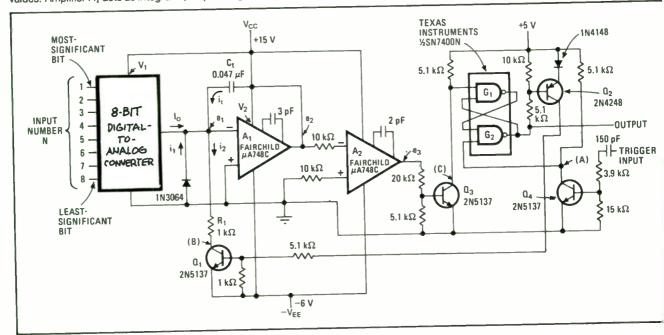

#### Analog-to-digital converter produces logarithmic output

by Ronald Ferrie Communications & Controls Co., Pittsburgh, Pa

When the logarithm of a signal voltage must be converted to a digital number, a log converter is normally used in conjunction with an analog-to-digital converter. But the circuitry involved becomes much simpler if the a-d converter is made to perform the log conversion itself. The resulting digital log converter has a two-decade dynamic range that can be set over a wide range of voltage levels.

In the circuit, a START pulse sets flip-flop FF<sub>1</sub> and resets the counter to zero. This action closes switch  $S_1$  and opens switch S2. (Field-effect transistors are used for these switches.) The unknown input voltage is now applied to the integrator, charging capacitor C through R<sub>1</sub>.

The reference voltage for the comparator is initially set at zero. As the output voltage from the integrator passes through zero, gate G<sub>1</sub> is enabled so that pulses from the oscillator enter the counter at frequency fo.

When the counter is filled (N pulses accumulated), the next pulse causes the counter to return to zero and to generate a carry-out pulse that resets flip-flop FF<sub>1</sub>. This opens switch S<sub>1</sub>, disconnecting the input voltage from the integrator, and closes switch S2, causing capacitor C to discharge through resistor R<sub>2</sub>. Also, the comparator reference voltage becomes E<sub>R</sub>.

The integrator's output voltage decays until it reaches

the comparator reference of E<sub>R</sub>. This decay period is:

$t_x = R_2 C \ln(E_{o(pk)}/E_R) = R_2 C \ln(E_i N/R_1 C f_o E_R)$ At time tx, the comparator output goes to zero, inhibiting gate G<sub>1</sub> and terminating the count. During the decay period, pulses still enter the counter at frequency for and accumulate for a count of:

$N_x = f_o t_x = f_o R_2 C \ln(E_i N / R_1 C f_o E_R)$

Since time t<sub>x</sub> began with the counter set to zero, this equation represents the total count stored at the end of the decay period. The expression can be rewritten as:

$N_x = K_0 \ln(E_i/K_1) - \alpha$

where:

$K_0 = f_0 R_2 C$

$K_1 = R_1 C f_0 E_R / N$

$\alpha = K_0 \ln(K_1)$

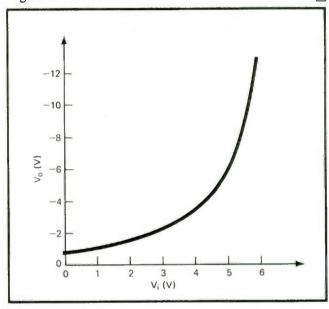

The second equation for  $N_x$  shows that the number stored in the counter at the end of the cycle is proportional to the logarithm of the input voltage minus a constant term, a. The plot of output count versus input voltage shows two typical performance curves for different values of  $K_0$  and  $\alpha$ .

The log converter nominally has a two-decade dynamic range, which can be extended to about three decades easily and to about 3.5 decades with some difficulty. This dynamic range can be set at almost any voltage level, depending on the components selected. The low-voltage limit is primarily determined by the drift and offset voltage of the integrator op amp. And resistor voltage ratings limit the high-voltage level.

Typically, a two-decade log converter built this way, and having an  $\alpha$  value of zero, will accept inputs of 1 to 100 volts, producing an output pulse count of 0 to 460. For such a converter, N = 1,000,  $f_0 = 50$  kilohertz,  $R_1 = 100$  kilohms, and C = 2 microfarads.

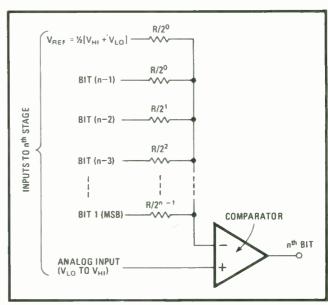

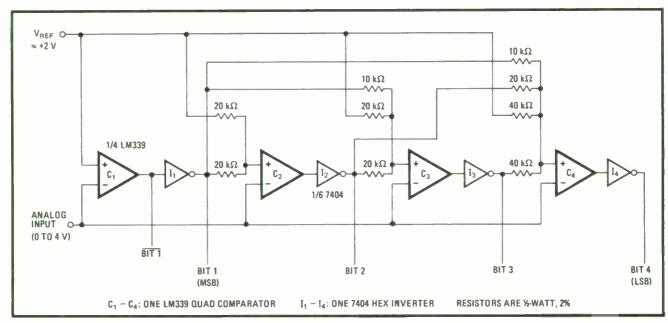

### Comparators and resistors form clockless a-d converter

by Adrian H. Kitai Hamilton, Ont., Canada

A successive-approximation analog-to-digital converter can be built out of comparators and resistors only. Conversion speed is determined by the settling time of the comparators, and no clock is needed.

The concept is illustrated in Fig. 1, which shows the  $n^{th}$  stage of a converter. The analog input voltage is compared with a voltage, the value of which is determined by the outputs of all previous stages, as well as by  $V_{ref}$ . A resistor is connected to weight each of the previous comparator outputs, and an additional resistor is connected to  $V_{ref}$ , which must be midway between the HI and LO levels of the comparator's output voltage. The  $n^{th}$  comparator needs n resistors, except for the first stage which needs none.

Since, however, the open-collector outputs of the comparators do not deliver voltages of sufficient precision, they are in practice followed by inverters that clamp the voltages. To compensate for this inversion of the comparator output, the input connections to the comparators are the reverse of those shown in Fig. 1; i.e., the analog input signal is connected to the inverting inputs instead of to the noninverting inputs.

Figure 2 shows a practical 4-bit circuit that uses only two inexpensive integrated circuits. This circuit is useful for applications such as driving a display of 16 light-emitting diodes. Comparator  $C_1$  has its positive input tied to  $V_{ref}$ . When an analog input lying between ground and  $2V_{ref}$  (near +4 volts) is applied to the negative

input, the output of inverter  $I_1$  is the first bit. This output is used to establish the switching level for  $C_2$ , which is either  $\frac{1}{2}$   $V_{ref}$  or  $\frac{3}{2}$   $V_{ref}$  depending on whether  $I_1$ 's output is LO or HI. In the same way, the remaining comparators provide bits 3 and 4.

To understand the circuit's operation, assume, for simplicity, that the LO and HI output levels of the transistor-transistor-logic inverters are 0 v and +4 v respectively. Then each of the 16 quantized intervals is 0.25 v wide. Also V<sub>ref</sub> is set at +2 v. If, for example, 3.4 v (a value within interval 13) is applied to the analog

**1.** N° stage. In n° stage of successive-approximation a-d converter, an analog input voltage that lies between  $V_{LO}$  and  $V_{HI}$  is compared with a voltage determined by an average of the reference voltage and weighted values of the more significant bits. Reference voltage  $V_{HI}$  is fixed at the midpoint of the analog input range.

2. No clock. Comparator  $C_1$  compares the analog input voltage with  $V_{rel}$ . This defines bit 1 and is averaged with  $V_{rel}$  to set the switching level for  $C_2$ . Bit 2 is averaged with both  $V_{rel}$  and a weighted value of bit 1, to set the switching level for  $C_3$ . Bit 4 is obtained similarly. Each output can drive one TTL load. LM339 comparators can sense input voltages down to ground potential, so only a + 5-volt supply is needed.

input, bit 1 goes HI (+4 v), and the input to the noninverting terminal of  $C_2$  is therefore the average of 4 v and 2 v, or 3 v. This sets bit 2 HI. When the weighted levels at bit 1, bit 2, and  $V_{ref}$  are now combined, the positive  $C_3$  input voltage is 3.5 v. Bit 3 is therefore set LO and is summed along with  $V_{ref}$  and bits 1 and 2 to set the plus input of  $C_4$  at 3.25 v; thus bit 4 is set HI. The output

of the circuit is therefore 1101, or decimal 13.

The quad LM3339 comparator operates from a single +5-v supply and has a settling time of 1.3 microseconds per bit. The totem-pole outputs of the TTL inverters supply the resistor networks with well-clamped voltage levels. In addition, the complement of every bit is available from the LM339 open-collector outputs.

### Comparator IC forms 10-bit a-d converter

by James M. Williams

Massachusetts Institute of Technology, Cambridge, Mass.

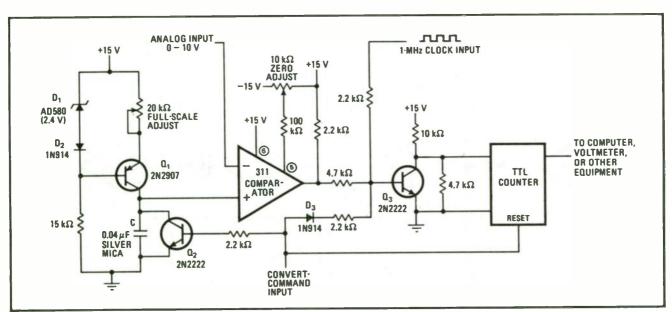

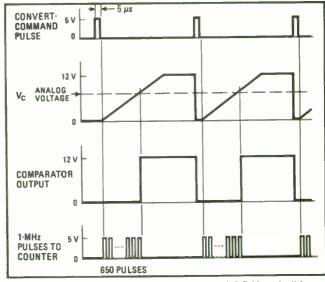

This analog-to-digital converter uses an integrated-circuit comparator to provide an accurate 10-bit representation of an analog signal in 1 millisecond or in 100 microseconds, depending on the clock rate. The circuit, which costs only \$13 to build, is accurate over the temperature range from 15°C to 35°C.

In addition to low cost, advantages include low parts count, low power drain, immunity from power-supply fluctuations, and capability to transmit data over two wires. Disadvantages include the necessity for a stable clock (although one clock can serve many converters), and dependence upon a capacitor for stability. The circuit may be sensitive to noise, but a small RC filter can be used for noise suppression.

Operation over extended temperature ranges is not recommended. If such use is necessary, however, capacitor C (Fig. 1) should consist of a 0.03 silver-mica capacitor in parallel with a 0.01 polystyrene capacitor.

The digital output from this converter is the number

of clock pulses counted during the time required for the capacitor to charge up to the level of the analog voltage. As the circuit diagram in Fig. 1 shows, the analog input can be any voltage from 0 to 10 v. This voltage and the voltage across the capacitor are compared in the IC. As long as the analog voltage is greater than capacitor voltage  $V_{\rm C}$ , the comparator allows a counter to count clock pulses. But when  $V_{\rm C}$  reaches the level of the analog voltage, the counting is stopped. The total number of pulses counted is a measure of the analog input. The charging rate of the capacitor is set so the pulse count is proportional to the voltage; e.g., 1,000 pulses corresponds to 10 v.

The detailed operation of the a-d converter in Fig. 1 is straightforward. Transistor  $Q_1$ , diodes  $D_1$  and  $D_2$ , and the resistors constitute a constant-current source for charging capacitor C. The 2.4-v zener  $D_1$  stabilizes the source against power-supply variations, and the voltage drop across  $D_2$  matches the emitter-to-base voltage in  $Q_1$ , despite any temperature changes.

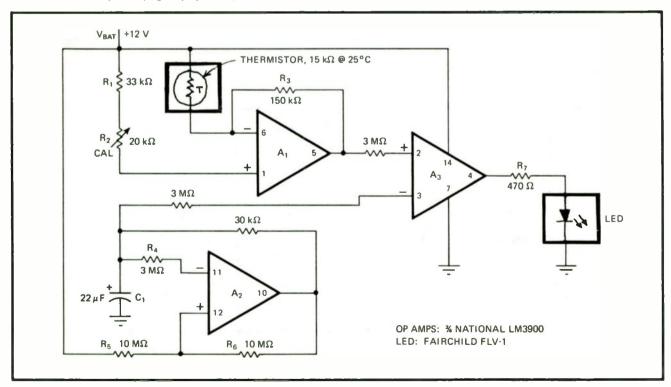

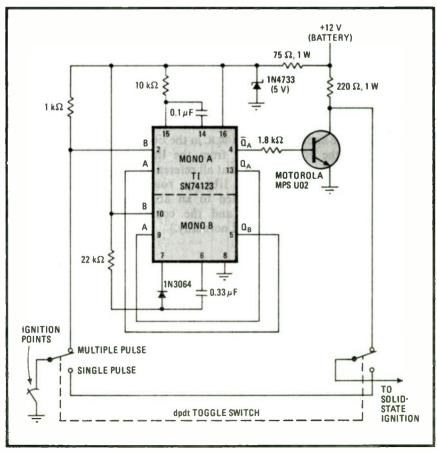

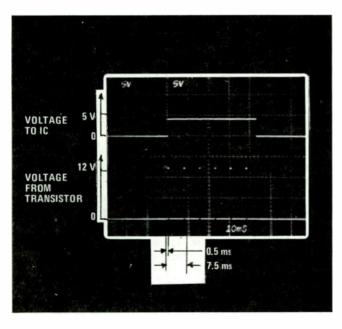

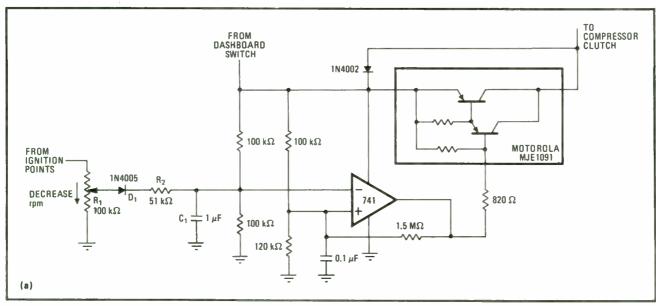

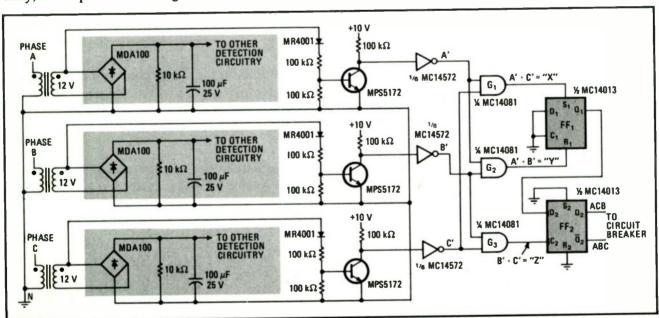

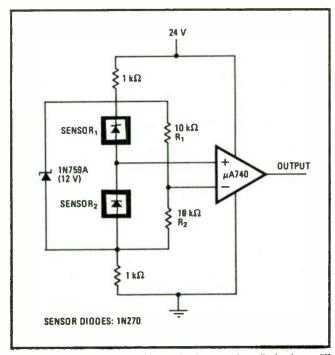

The type 311 IC compares the input voltage to the capacitor voltage  $V_C$  and controls transistor  $Q_3$ . The input voltage is applied to the inverting (-) input of the comparator, and  $V_C$  is applied to the noninverting (+) terminal. At quiescence,  $V_C$  is about 12 V, so the 311 output is high. This high signal keeps  $Q_3$  on, so that the data line into the counter is grounded and no clock pulses are counted.