ROBERT MATKINS

VOLUME 1 🗌 NUMBER 6 JUNE 1964

THE INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS , INC.

ALFRED N. GOLDSMITH Editor Emeritus

| JOHN D. RYDER         | Editor           |

|-----------------------|------------------|

| ELWOOD K. GANNETT     | Managing Editor  |

| RONALD K. JURGEN      | Executive Editor |

| ROBERT E. WHITLOCK    | Senior Editor    |

| SAMUEL WALTERS        | Technical Editor |

| GORDON D. FRIEDLANDER | Technical Editor |

| ELEANOR F. PECK       | Copy Editor      |

**IEEE News Editor**

Editorial Assistant

**GLADYS CHARITZ**

STELLA GRAZDA

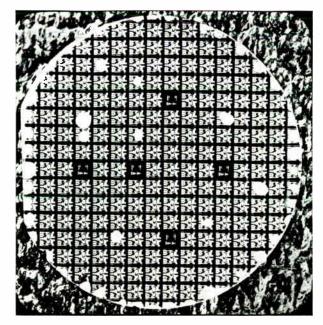

the cover

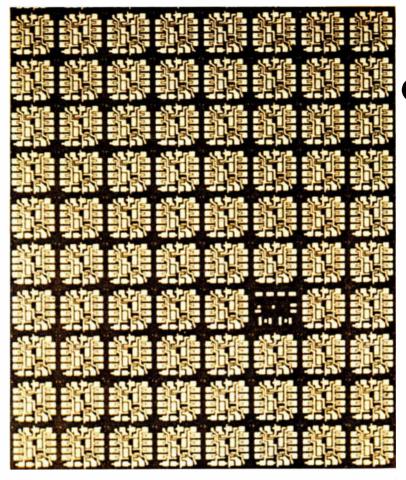

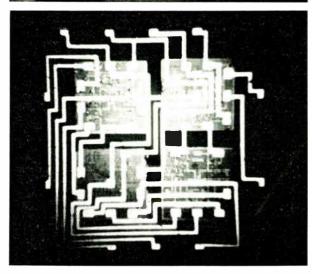

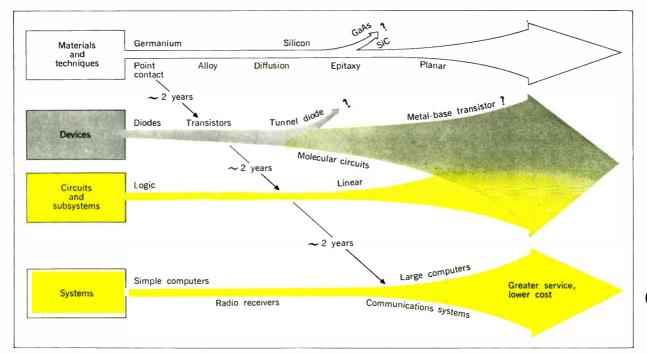

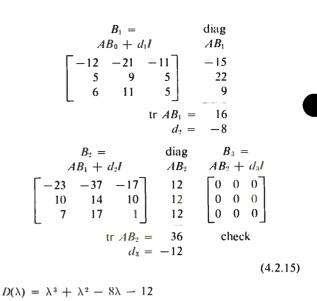

The illustration on the front cover shows a section of an experimental wafer on which several hundred TTL gates are interconnected to perform the function of a multibit shift register. This wafer is representative of the current developmental work in the field of integrated circuits. It evolved as part of a Westinghouse research project calling for experiments with large arrays to determine how complex a logic function may be fabricated on a single slice of silicon. A comprehensive report on integrated circuits begins on page 62 of this issue. It is an edited version of the Modular Magic Symposium held during the 1964 IEEE International Convention. The two leading types of circuits that show promise for integrated-circuit use-monolithic silicon circuits and thin-film circuitsare treated in detail in separate articles in this issue beginning on page 83 and on page 102, respectively.

#### THE INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS, INC.

| HERBERT TAYLOR  | Art Director                 |                                                                                                 |                                                        |                                                              |                                                                                                  |

|-----------------|------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| RUTH M. EDMISTO | IN Production Editor         |                                                                                                 | BOARD OF D                                             | IRECTORS, 1964                                               |                                                                                                  |

| KUTA M. EUMISTU | r Froduction Eauor           | C. H. Linder, <i>Presider</i><br>B. M. Oliver, <i>Vice Pre</i><br>W. E. Peterson, <i>Vice F</i> | sident                                                 | 1                                                            | W. R. Clark, <i>Treasurer</i><br>Haraden Pratt, <i>Secretary</i><br>John D. Ryder, <i>Editor</i> |

| EDITORIAL (     | <b>DPERATIONS</b>            | B. S. Angwin<br>Hendley Blackmon<br>W. H. Chase                                                 | J. T. Henderson<br>S. W. Herwald<br>L. C. Holmes       | J. C. R. Punchard<br>Herre Rinia<br>W. G. Shepherd           | B. R. Teare, Jr.<br>Ernst Weber<br>Joseph Weil                                                   |

| HELENE FRISCHAU | IER<br>Administrative Editor | L. J. Giacoletto<br>P. E. Haggerty<br>Ferdinand Hamburge                                        | T. F. Jones, Jr.<br>W. K. MacAdam<br>r, Jr. A. N. Gold | George Sinclair<br>E. C. Starr<br>smith, <i>Director Eme</i> | F. K. Willenbrock<br>C. R, Wischmeyer                                                            |

| W. R. CRONE     | Assistant Editor             |                                                                                                 |                                                        | rtson, Director Eme                                          |                                                                                                  |

| ADVERTISING                                       | Donald<br>George W. Bailey, <i>Executive Consul</i>                                                     |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| WILLIAM C. COPP Advertising Manager               | John L. Callahan,<br>Technical Operations Committee                                                     |

| LILLIAN PETRANEK<br>Assistant Advertising Manager | Laurence G. Cumming, Field Opera<br>Richard M. Emberson,<br>Professional Technical Groups               |

| CARL MAIER                                        |                                                                                                         |

| Advertising Production Manager                    | IEEE SPECTRUM is published mo<br>Engineers, Inc. Headquarters addres<br>Cable address: ITRIPLEE. Teleph |

| EDITORIAL BOARD                                   | ampton Sts., Easton, Pa. Change<br>Headquarters. Annual subscriptic                                     |

JOHN O. RYOER Chairman THOMAS F. JONES, JR. Vice Chairman E. K. GANNETT C. T. HATCHER W. K. MAC ADAM S. W. HERWALD A. H. WAYNICK T. A. HUNTER F. K. WILLENBROCK

#### **HEADQUARTERS STAFF**

G. Fink, General Manager Nelson S. Hibshman, Executive Consultant ltant WIL Elwood K. Gannett, Editorial Operations ations Joan Kearney, Administrative Assistant LILL William J. Keyes, **Executive Assistant for Administration** CAR onthly by The Institute of Electrical and Electronics ss: Box A, Lenox Hill Station, New York, N.Y. 10021. one: 212-PL 2-6800. Published at 20th and Northe of address requires thirty days notice to IEEE ED. on: IEEE members, first subscription included in dues, one additional subscription \$13.50. College and public libraries, \$13.50 in U.S.A. and Canada, \$14.50 elsewhere. Others, \$18.00 in U.S.A. and Canada, \$19.00 elsewhere. Single copies: members, one additional copy \$1.00, college and public libraries, \$1.50 in U.S.A. and Canada, \$1.75 elsewhere. Others, \$2.00 in U.S.A. and Canada, \$2.25 elsewhere. Editorial correspondence should be addressed to IEEE SPECTRUM at IEEE Headquarters. Advertising correspondence should be addressed to IEEE Advertising Department, 72 W. 45 St., New York, N.Y. 10036. Telephone: 212-MU 2-6606. Responsibility for the contents of papers published rests upon the authors, and not the IEEE or its members. All republication rights, including translations, are reserved by the IEEE. Abstracting is permitted with mention of source. Second-class postage paid at Easton, Pa. Printed in U.S.A. Copyright © 1964 by The Institute of Electrical and Electronics Engineers, Inc.

> IEEE Spectrum is a trademark owned by The Institute of Electrical and Electronics Engineers, Inc.

The Alaskan earthquake has focused the attention of the world on seismic phenomena. The electronics engineer naturally asks, "Can we use the techniques of radar and seismic sounding to investigate the earth's interior?" Burt Rudman, consultant in AIL's Research and Systems Engineering Division, has been thinking about this problem for some time and we present his thoughts in this advertisement.

## Seismic Sounding of the Earth's Interior

Man's knowledge of the interior structure of the earth comes from astronomical observations and studies of the effects of this interior structure on the paths of seismic energy. In most instances the seismic wave has been generated by an earthquake. Because he has no control over the location, timing, or magnitude of this energy source, the seismologist must accept amplitude measurements at distances where seismographic stations happen to be located taking into account differences in energy, depth, and radiation patterns and paths.

Although seismological studies using large-scale explosions (about 20 kilotons) have overcome some of these problems, they do not present an ideal solution. This article explores the possibility of using injected coherent energy for seismic sounding of the earth's interior. Because this input signal is known and coherent, it would permit long-term data processing of the detected output signal (a method not feasible in examining data from earthquakes or explosions). This energy could be detected at almost any point on the earth's surface, including a location diametrically opposite the transmitting source. The received signal-to-noise ratio could be increased by optimizing the location of the detectors or by data processing.

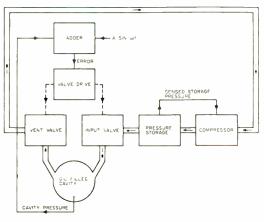

To generate a seismic signal by controlled and coherent applications of pressure, consider a spherical cavity excavated at an overburden depth great enough to withstand the required overpressures. The depth will set the upper limit of allowable pressure, and the cavity size will influence the lower limit of required pressure. If this cavity is filled with hydraulic oil, which is subjected to sine-variant pressure, the pressure function will be transferred to the cavity walls and hence to a propagating seismic wave.

A pressure source maintained by a compressor is connected to the cavity through a continuous-control valve-vent system. A pressure sensor in the cavity provides loop control for the valve-vent drive. A sine-wave signal injected into the loop acts as an input source. The pressure in such a system should probably be limited to 200 atmospheres (paralleling current hydraulic-control limitations). At this pressure, overburden requirements dictate a depth of 940 meters or more.

The frequency at which a cavity is resonant is equal to the ratio of the velocity of the compressional wave in the surrounding medium to the radius of the cavity. A 1-cps wave (the frequency best propagated by earthquakes over the path of present interest) would require a cavity of 6-km radius for resonance.

A pulse length of 10 seconds at a 1-cps carrier frequency represents a reasonable compromise for the demands of average power, signal-to-noise ratio, and system space resolution.

The bandwidth of the system is 0.075 cps. Since the signal-to-noise criterion of the system was determined from the microseismic noise in a 1-cps band, this bandwidth represents an improvement in the signal-tonoise energy ratio of 40:3: the system's peak-power requirement (869,000 kw for global range) is reduced by the same ratio to 65,000 kw. If the interpulse interval is 1 hour (to avoid intermode ambiguity), the transmitting duty cycle is 1/360. Considerations of bandwidth and duty cycle reduce the requirements to 362 kw of average power at an assumed efficiency of 50 percent.

The system illustrated, with its small duty cycle, does not present any problem for the average power. However, the peak power at this point is 130,000 kw (65,000 kw into the earth), requiring a pressure of 1450 atmospheres for a 1-meter cavity radius. A cavity radius of 7.25 meters would reduce pressure requirements to the hydraulic system limit of 200 atmospheres.

For a receiver at near-surface depths, 50 hours of transmission (10 seconds during each hour) would be required to keep the

Seismic Wave Generator

size of the transmitting cavity at 1 meter and its depth at 1 km. (The actual processing time could. of course, be short—working from tape.) At a receiver depth of about 1900 meters in sandstone. an amplitude signal-to-noise ratio of 7.25 would be achieved, thereby lessening the need for data processing.

We have idealized the problem in omitting the losses due to coupling at the transmitter. For a 7.25-meter cavity, the coupling loss would be on the order of  $10^4$  but since this loss is an inverse function of cavity size to the fourth power, a 72.5-meter cavity would compensate for it.

A decrease in the range requirement and/or an increase in processing time would further reduce the power required. These requirements could be satisfied by many combinations of receiver/transmitter depth, transmitting cavity size, and processing time. Many assumptions have been made and much remains to be proved but the system of injecting coherent seismic energy into the earth seems feasible.

A complete bound set of our eighth series of articles is available on request. Write to Harold Hechtman at AIL for your set.

AIRBORNE INSTRUMENTS LABORATORY Deer Park, Long Island, New York

For more information on advertisements use the reader service card

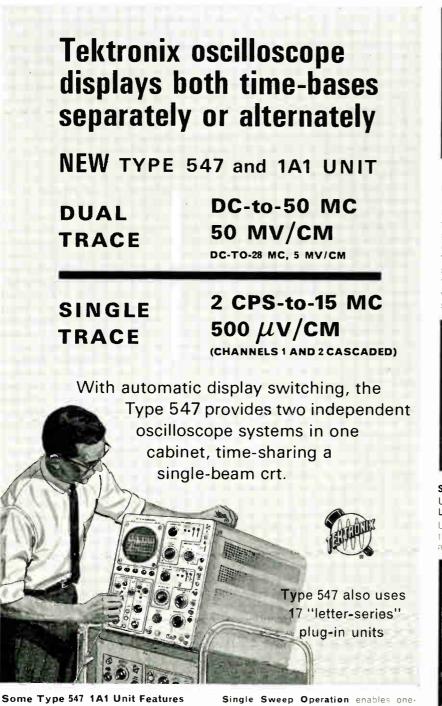

New CRT (with internal grafic de and ontrollable illumination) provides bright "noparallax" displays of small spot size and uniform focus over the full 6- m by 10-cm .ie..ing area

Calibrated Sweep Delay estends continuously from 0.1 millrose. chil to 50 seconds.

2 Independent Sweep Systems provide 24 Jalibrated time-base ratios from 5 se to 0.1 µsec cm. Three mainified positions of 2X, 5X, and 10X, are common to both sweeps-with the JUX maintier in reasing the maximum calibrated sweep rates to 10 nsec, cm.

Tektronix, Inc.

shot displays for photo-iraphy of either normal or delayed sweeps, including alternate presentations.

2 Independent Triggering Systems simplify set-up procedures, provide stable displays over the full passband and to beyond 50 Mc, and include brightline automatic modes for convenience.

- Type 547 On illostope .....\$1875 mit out ; lumm unit)

- Type 1A1 Dual-Trace Unit ..., .. \$ 600

Ral--Mo int Model Type RM647 ... \$1975

U.C. Calls Price 1.0.0. deaverton, rejon

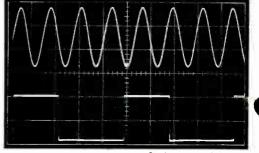

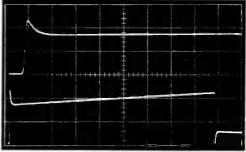

#### 2 signals – different sweeps Upper trace is Channel 1/A sweep, 1 $\mu$ sec/cm. Lower trace is Channel 2/B sweep, 10 $\mu$ sec/cm.

Using same or different sween rates (and sensitivities) to alternately display different signals provides equivalent dual-scope operation, in many instances.

Triggering internally (normal) permits viewing stable displays of waveforms unrelated in frequency. Triggering internally (plug-in, Channel 1) permits viewing frequency or phase differences with respect to Channel 1.

same signal - different sweeps Upper trace is Channel 1/A sweep, 0.1 µsec/cm.

Lower trace is Channel 1/B sweep, 1  $\mu$ sec/cm. Using different sweep rates to alternately display the same signal permits close analysis of waveform aperrations in different time domains.

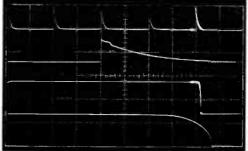

#### Single-exposure 2 signals – portions of each magnified

Trace 1 is Channel 2/B sweep, 10  $\mu$ sec/cm. Trace 2 (brightened portion of Trace 1) is

- Channel 2/A sweep, 0.5 µsec/cm. Trace 3 is Channel 1/B sweep, 10  $\mu$ sec/cm. Trace 4 (brightened portion of Trace 3) is

- Channel 1/A sweep, 0.5 µsec/cm.

Using sweep delay technique-plus automatic alternate switching of the time bases-permits displaying both signals with a selected brightened portion and the brightened partitions expanded to a full 10 centimeters.

B weep triggering internally from Channel 1 (plugin) assures a stable time-related display with ut using external trigger probe.

#### For a demonstration, call your Tektronix Field Engineer

POBOX 500 · BEAVERTON, OREGON 97005 · Phone: (Area Code 503) Mitchell 4-0161 · Telex 036-691 TWX 503-291-6805 · Cable TEKTRONIX · OVERSEAS DISTRIBUTORS IN 25 COUNTRIES TEKTRONIX FIELD OFFICES in principal cities in United States. Consult Telephone Directory

Tektronix Australia Pty., Ltd., Melbourne; Sydney • Tektronix Canada Ltd., Montreal; Toronto Tektronix International A.G., Zug, Switzerland • Tektronix Ltd., Guernsey, C. I. • Tektronix U. K. Ltd., Harpenden, Herts

For more information on advertisements use the reader service card

World Radio History

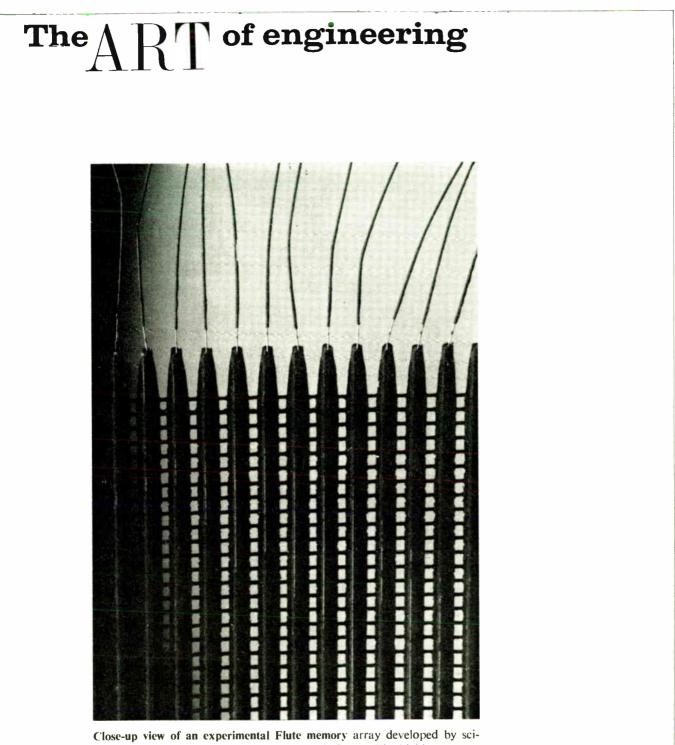

Close-up view of an experimental Flute memory array developed by scientists at IBM's Thomas J. Watson Research Center. The highly compact device is made by molding tiny magnetic ferrite "tubes" over a mesh of fine wires. The name of the array is derived from the flute-like appearance of the individual magnetic tubes. It can store 5000 bits of information. Storage is accomplished by changing the magnetization direction of the ferrite material at the intersection of any two wires. More detailed information appears in the Focal Points department in this issue on page 186.

# Reflections

## 75 years ago

New York City Rapid Transit. "It is particularly noticeable that all who have, so far, considered the question of rapid transit for the city of New York, have assumed that it is so deficient in these facilities that the question was of the most immediate and vital importance. and, while I do not for a moment wish to underestimate the urgency of the demand to meet the rapid growth which has already almost overtaxed the elevated system, we should not lose sight of the fact that New York has even today, all things considered, a better rapid transit system than any other city in the world. In evidence of this it is only necessary to cite the facts that one may enter a well-appointed car at the Battery, and, traveling through the best atmosphere of the city, be carried with remarkable smoothness to Fifty-ninth street in 26 minutes, or at the average speed of 12 miles per hour including stops, and in about this manner, the elevated system contrives to carry onehalf million passengers per diem for a lower rate of fare than is done in any other city for similar accommodations. and with a smaller proportion of accidents than may be found on any steam road in the world making an equal number of stops per one hundred miles run. On a recent holiday, namely, April 30th last, 835,721 passengers were carried on this much abused system without noticeable detention or accident-but New York wants more, and in view of the rapidly growing traffic which has already almost exceeded the ability of the system, it must be admitted that the demand is a pressing one, as this one half million will grow to one million in a short time, and it is exceeding improbable that any steam motor can be devised to permit of this increase, at least on the present structures, without subjecting them to quickly destructive strains. With steam, therefore, the only avenue open for increasing the passenger capacity, namely the use of longer

trains, is obviously out of the question, since it is a notorious fact that the present motors are taxed to their utmost.

"To the mind of the mechanical engineer, having in view the ordinary coefficients of tractive ability, there is no remedy for this, but I think I shall be able to produce at least some little evidence that, owing to certain effects which have not yet been satisfactorily explained, an electric motor may be made capable of solving the problem at least so far as the ultimate strength of the present elevated structure will permit, inasmuch as the effects alluded to certainly do increase the tractive ability beyond that obtained by the use of any coefficients which may be found in the works of that eminent authority, D. K. Clark, or still later in the excellent treatise on the 'Economic Theory of Railroad Location,' by A. M. Wellington. - - -"

"--- it is now possible to run, and compete with steam on the Ninth Avenue railroad; and, of course, any of the others with a certain concrete economy based upon a series of tests made under circumstances to the last degree prejudicial for an economical showing and without taking into account the great gains which would inevitably result from the use of a large central station, with dynamos of the highest efficiency, and with the obvious advantage resulting from the operation of a number of motive units under varying loads from a central station or dwelling upon such abstract economies as freedom from cinder, dropping water, smoke and noise," (Leo Daft, "Some Recent Electrical Work on the Elevated Railroads and Its Bearing on the Rapid Transit Problem," Trans. AIEE, vol. VI, Nov. 1888-Nov. 1889, pp. 359-387.)

## 50 years ago

All At Sea. "I have repeatedly argued before you that steamships are not so well equipped with radio apparatus as they should be, that the apparatus in use is not so powerful, efficient or reliable as it should be from the standpoint of commercial and distress requirements taken in conjunction with the present knowledge and available apparatus.

"I have particularly tried to point out that it is absurd to give a steamship a comparatively strong voice for ordinary conditions and a hoarse stuttering whisper for use under conditions of extreme distress, when a good strong voice for both ordinary and distress conditions is easily obtainable. Vessels are said to sail as long as five days in some parts of the ocean without being able to carry on communication because of the great average distance of ships and small radio range.

"I have endeavored to bring these points to the attention of all concerned, and have continually described the kind of apparatus I believe should be used. For a time I tried to explain verbally what I believed could be reasonably obtained at the present time.

"A little more than a year ago, I put my ideas of what should be used as radio equipment on board vessels into the form of a set of specifications, and in June, 1913, a number of these specifications were struck off. And it is these revised specifications, with some slight modifications and explanations, that I am presenting tonight for your discussion. In making these specifications, I tried to put myself in the position of steamship owners who desired to secure as satisfactory equipment as could be obtained at a reasonable price at the present point in radio development; and to make the specifications such that when sent out to all manufacturers of radio apparatus, apparatus conforming to the present status of radio development would be offered. This practice of sending out specifications has been adopted by the United States Navy to a considerable extent; and it is probably due to this, in a general way, that we have quite high class radio apparatus manufactured in the United States. Should

# KIN TEL

world's largest DC amplifier manufacturer

## Solid state, non inverting amplifier

Model 121A/A. Response from DC to beyond 200 kc. Input impedance >10 megohms; output capability ±15 volts, 100 ma; output impedance <0.2 ohm in series with 50 microhenries. Price: \$995.

## Floating, differential amplifier

Model 114C. High common mode rejection, low effective input capacity. DC to 85 cps. Input impedance >40 megohms; output capability  $\pm 10$  volts, 10 ma; output impedance <0.25 ohm to 500 cps; <1 ohm to 2 kc. Price: \$995.

# has an amplifier to fit your

## requirements

Model 114A. Effective input capacity less than  $1\mu\mu$ fd, high common mode rejection. 100 cycle bandwidth. Input impedance >5 megohms. Output capability ±10 volts, 10 ma; output impedance <2 ohms, DC to 1 kc. Price: \$895.

## Wideband amplifier

Model 112A. Four different plug-in attenuator units. DC to 40 kc. Input impedance 100 K ohms; output capability  $\pm 35$  volts, 40 ma; output impedance <1 ohm in series with 25 microhenries. Prices: \$575 to \$680.

Visit our Booth 1017 at WESCON, Sports Arena, Los Angeles, August 25-28.

All KIN TEL DC data amplifiers: have drift less than  $2\mu v \cdot accuracy$  of 0.01% for any single gain step  $\cdot$  fit six to a standard 19-inch rack  $\cdot$  are available in portable cabinets  $\cdot$  have an integral power supply  $\cdot$  are chopper-stabilized  $\cdot$  have exceptional linearity and low output impedance.

All prices FOB, San Diego, California. (Additional export charge.) Write for detailed information. Representatives in all major cities. 5725 Kearny Villa Road San Diego, California 92112 Phone (714) 277-6700

this practice be followed by the steamship companies, it would probably result in still further development. It certainly would result in the steamship companies obtaining far better apparatus than they have at present." (R. H. Marriott, "Specifications for Steamship Radio Equipment," *Proc. IRE*, June 1914, pp. 165–166.)

The Electric Gyroscope. "Until a few years ago the gyroscope was little known or heard of except as a child's toy, although as far back as 1852 its action was investigated by the French scientist Foucault, who published the results of his experiments in which he laid down very clearly the laws of its action. ---"

"For nearly half a century after Foucault had demonstrated its action, the gyroscope was put to no practical use. The late American author and scientist Hopkins, whose writings were published for many years in the Scientific American, was the first to drive a gyroscope electrically. He was able to enlarge on Foucault's experiments and obtain much more persistent results with his continuously driven wheel.

"The first serious application of the gyroscope in engineering work was by Obrey, an Austrian naval officer, who made use of the gyroscope to steer torpedoes. About 1903 Dr. Schlick, a German engineer, proposed the use of the gyroscope for stabilizing ships against rolling and built a number of experimental plants which were tried out with some little success. At about the same time Lewis Brennan brought general public attention to the gyroscope by his announcement of a railroad car that would maintain its equilibrium on a single rail. A car of this type was exhibited in this country in 1910 and the subject of monorail traction was much discussed in the press at the time in connection with the possibilities for high speeds which were claimed for this invention.

"Practically all of the serious applications of the gyroscope, and by far the most important of its uses at the present time, have developed in marine work. These are the steering of torpedoes, the use as a compass and the use for stabilizing and controlling the motions of ships, ---"

"The very high development of the gyro compass during the past few years has been largely due to the efforts of a pioneer in the electrical art, Mr. Elmer A. Sperry, whose long and interesting experience with gyroscopic phenomena and belief in their engineering possibilities led him to devote practically all of his time to its development. . ."

"A number of workers abroad have also been laboring with great persistence and some degree of success to solve the many physical problems involved in translating the idea of Foucault into concrete terms of steel and bronze which will function under the extremely severe conditions on shipboard.

"The nature of the problem is indicated when one realizes that the gyro compass is so sensitive that it responds instantly and with the highest degree of accuracy to the very slowly impressed angular motion in space about the earth's axis four thousand miles distant, while at the same time it remains indifferent to the angular movements of the ship several hundred times greater in intensity. ---"

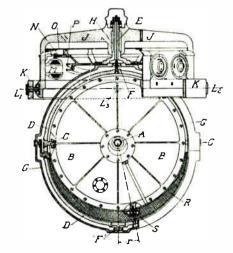

"The general arrangement of parts constituting the Sperry gyro compass is shown in Fig. 9, which for greater clearness in illustrating the various functions has been simplified by the omission of electrical circuits and minor details.

"The gyroscope wheel is mounted to rotate on a horizontal shaft A within the casing B, which is pivoted on the horizontal axis C through its center of gravity and carried by the frame or vertical ring D.

"The ring D is suspended by a torsionless strand E and guided by bearings F and F' to allow a free oscillation of limited amount about its vertical axis within the frame or 'phantom' G, so called because of its characteristic action as a 'shadow' in following up each motion of the ring D. The phantom G has a hollow stem H to which the

Fig. 9 Method of mounting the directive element.

strand E is attached at its upper end, and the stem forms a journal for rotation in azimuth with respect to the supporting base frame J.

"The frame J is mounted to swing in the binnacle by the usual Cardan suspension, consisting of the ring K and suitable bearings L1, L2, L3 and L4, the last not shown.

"The frame J carries a 'follow-up' motor M, driving a master gear N, forming a rigid part of the phantom G, whereby the latter is positively driven in azimuth to respond to any movement of ring D.

"The ring D, which with the casing is termed the 'element,' carries a pair of electrical contacts in the form of trolley wheels, which cooperate with stationary contacts mounted upon the phantom G for the purpose of controlling the follow-up motor M, the electrical connections not being shown in the figure.

"The power-driven phantom G is thus automatically controlled so as to respond instantly to all movements of the sensitive element, and in fact to all relative movement in azimuth between the ship and the gyro.

"This characteristic of the phantom enables it to be used for various important functions, namely to carry the scale or card O and a cam P forming part of the automatic correcting device. The power drive is also utilized in operating the transmitter for the repeater instruments, and in overcoming friction of the slip rings needed to carry current to the gyro.

"Since the phantom G, though at all times rigidly anchored to the binnacle, stands in practically constant relation to the sensitive element as regards motion about the vertical axis, but is nevertheless entirely separate thereform, it serves as an anchorage for producing stresses to restrain and correct the movements of the sensitive element. This is accomplished by means of a yielding connection between the phantom G and the gyro case B, in the form of a pendulum or bail R, supported by and forming a part of the phantom. The point of attachment S to the gyro casing is located in a certain position eccentric to both the vertical and horizontal axes of the gyro. By this means several most important results are obtained, including positive orientation and the prevention of oscillation." (H. C. Ford, "The Electrically Driven Gyroscope in Marine Work," Trans. AIEE, vol. XXXIII, Part I, Jan.-June 1914, pp. 857-872.)

"Varian's new Hydrogen Maser Frequency Standard -with stability of a few parts in 10<sup>13</sup>— is the most stable oscillator in the world. It has been thoroughly tested and is now available for a wide variety of practical applications requiring the most precise measurement of frequency, phase and time. And it's ready for operation just as you see itall it needs is 110-volt primary power. The Model H-10 Hydrogen Maser is the first instrument of its kind ever offered for sale, so if you'd like complete specifications, write Earle Benson, Quantum Electronic Devices, Beverly, Mass."

STABILITY 1 x 10<sup>-13</sup> rms for 10-second averaging interval.<br/> $5 \times 10^{-13}$  rms for 1-month averaging interval.RESEITABILITY 1 x 10<sup>-12</sup>FREQUENCY 1,420,405,751.73 $\pm$ 0.03 cps.

IEEE spectrum JUNE 1964 For mo

For more information on advertisements use the reader service card

10.00

ASSOCIATES

INSTRUMENTGROUP

Beverly, Massachusetts 🗀 Palo Alto, California

In Europe contact: Varian A. G., Zug, Switzerland

World Radio History

## 25 years ago

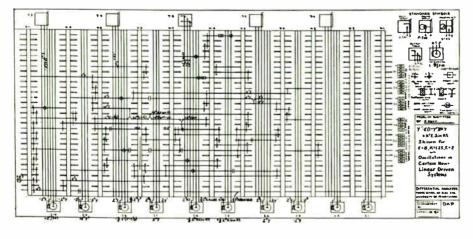

The Machine Age. "As pointed out by van der Pol in 1934, the analytical investigation of systems producing relaxation oscillations under the influence of an impressed periodic force had at that time hardly begun. The intractable nature of the nonlinear differential equations governing such systems affords a ready explanation for the slow progress encountered. Within recent years, however, with the increased development and use of mechanical means for the solution of mathematical problems, the mechanical solution of these equations is made possible. This paper presents differential-analyzer solutions of the equation of oscillation in certain nonlinear driven systems. These solutions, which have been obtained with the Moore School differential analyzer, illustrate the phenomena of automatic synchronization and frequency demultiplication. The nonlinear theory of oscillating systems, as summarized by van der Pol several vears ago, has served as the basis of the work described herein.

"It is observed that in going from the drifting to the synchronized state, synchronization is suddenly effected on the nearest odd subharmonic. Other analyzer solutions, not included in this paper, confirm this. Further, for particular values of K and E, which finally produce synchronization, the resulting steady-state wave form and phase relation with the impressed sinusoid appear to be independent of the initial phase of the sinusoid and of other initial conditions. The only apparent effect of varying the initial phase angle is to hasten or retard by a few cycles the appearance of the steady synchronized state. Inspection of (10a) shows that all such synchronized subharmonics are symmetrical oscillations.

"All of the above phenomena are in agreement with the experimentally observed properties of relaxation oscillations. Especially do they confirm the phenomenon of automatic synchronization over a frequency range as great as an octave (K-2), as mentioned by van der Pol. They also confirm the physical fact that the phenomenon of resonance is practically absent in the case of relaxation oscillations, and that the application of an external electromotive force has as its main effect the variation of time period of the resulting oscillation. This effect is seen to give rise to the phenomenon of subharmonics over a wide range of frequency demultiplication.

"In the course of these studies, employing (10a), only odd-order subharmonics have appeared. The greater the relative frequency of the driving force the higher the order of odd subharmonics it is possible to produce. Increasing the amplitude of the driving force results in successive "driving through" to a lower order of odd subharmonic. It must be stressed that the more general equation (4) is probably the one governing the production of both even- and odd-order subharmonics. Further work in this direction should be undertaken to establish the greater generality of (4) or of a somewhat similar differential equation.

"These results should be of value in the further development of the nonlinear theory of electric oscillations and in application to the design of relaxation oscillators with an impressed sinusoidal electromotive force.

"Fig. B. gives the schematic diagram of the differential-analyzer arrangement used in the course of these studies."

Fig. B-Differential analyzer arrangement used in the studies.

(D. L. Herr, "Oscillations in Certain Nonlinear Driven Systems," *Proc. IRE*, June 1939, pp. 396-402.)

How the West Was Won. The first convention of national scope of the Institute to be held on the Pacific Coast is scheduled for San Francisco during the last four days of June. Headquarters will be at the Mark Hopkins Hotel. In the two previous years, meetings were held in Spokane and Portland and gave unmistakable evidence of a substantial interest in a meeting of national character. The San Francisco World's Fair makes that city particularly attractive.

"To one who knows San Francisco, a renewal of acquaintanceship is all that needs be suggested to start making plans and recalling pleasant memories. To one who has never been there, comes indistinct visions of its many charms. Chinatown, the largest Chinese city outside of the Orient, Fisherman's Wharf where the fishing fleet, back from its morning venture, lies at rest, Market Street with its famed clocktowered ferry building at one end and Twin Peaks at the other, are but a few of its world-famed attractions.

"To these one must add Treasure Island and its 400 man-made acres devoted to recreation and education. Sponsored by eleven western states, fifty million dollars have been invested with one thought—to make the visitor want to return for more. An island that may be reached by automobile by way of the new San Francisco-Oakland Bay Bridge, it harbors the giant clipper ships which bring Asian cities within days rather than weeks of America and recall to mind the earlier clippers which once passed through the Golden Gate.

"Our Convention will be held at the same time as the combined Pacific Coast and Summer Convention of the American Institute of Electrical Engineers. Twenty-seven papers will be presented at six technical sessions. Eight are contributions from Pacific coast authors, sixteen have been prepared by authors from the eastern part of this country, two are from Europe and one from Puerto Rico. Thus, the program which follows is of broad geographical and topical interest.

> Tuesday, June 27 10:00 A.M.-12:00 Noon

Opening address by R. A. Heising, President of the Institute.

"Communications Engineering in Geo-

physical Exploration." by Herbert Hoover, Jr., United Geophysical Corporation, Pasadena, Calif.

- "Federal Communications Commission Engineering Regulations and Standards of Good Engineering Practice for Broadcast Stations," by S. L. Bailey, Jansky and Bailey, Washington, D.C.

- "Columbia's West Coast Operations," by L. H. Bowman, Columbia Broadeasting System, Hollywood, Calif.

#### 2:00 P.M.-4:30 P.M.

- "Recent Developments in Aerial Navigation," by H. H. Willis, Sperry Gyroscope Company, Brooklyn, N.Y.

- "Aircraft Instrument Landing Research at the Massachusetts Institute of Technology," by E. L. Bowles, Massachusetts Institute of Technology, Cambridge, Mass.

- "Study of the Effects of Mountains in Radiogoniometry and of the Combined Use of Radio Beacons and Radio Compasses for Aerial Navigation." by Andre Busignies, Le Materiel Telephonique, Paris, France.

- "Acoustic Models of Radio Antennas," by E. C. Jordan and W. L. Everitt, Ohio State University, Columbus, Ohio.

- "Recent Advances in Receiving Equipment for Transoceanic Telephony," by F. A. Polkinghorn, Bell Telephone Laboratories, New York, N. Y.

Wednesday, June 28 9:00 A.M.—11:00 A.M.

- "Electron Optics in Television," by V. K. Zworykin, RCA Manufacturing Company, Camden, N.J.

- "Current Division in Plane-Electrode Triodes." by Karl Spangenberg, Stanford University, Stanford, Calif.

- "Functions of Electron Bombardment in Television," by I. G. Malofi, RCA Manufacturing Company, Camden, N.J.

- "Surface-Controlled Mercury-Pool Rectifier," by T. M. Libby, Pacific Telephone and Telegraph Company, Seattle, Wash.

#### 2:00 P.M.-4:30 P.M.

- "Direct-Current and Audio-Frequency Amplifier," by L. J. Black and H. J. Scott, University of California, Berkeley, Calif.

- "Golden Gate International Exposition Radio and Sound Distributing Systems," by C. A. Lahar and L. Hewitt, RCA Manufacturing Company, Camden, N.J.

- "Radio-Frequency Spark-Over in Air," by P. A. Ekstrand, Heintz and Kauf-

Portametric 7V

IT'S A FIVE-DIAL POTENTIOMETER... A FOUR-TERMINAL KELVIN BRIDGE... A FIVE-DIAL VOLTAGE DIVIDER... A DIRECT-READING COMPARISON BRIDGE... A PICO AM-METER... A DIRECT-READING RATIOMETER... AN ELEC-TRONIC NULL DETECTOR

Combines the functions of seven instruments (estimated cost if bought separately, \$4000.00). Accuracy  $\pm$  0.02% for essentially all functions. Battery-operated, portable. For detailed information, request Catalog Sheet C-54. Price: **\$750**°°

### \* Potentiometric Voltmeter Bridge

| Function                                   | Ranges                                                       | Ranges Full Scale                                       |                                                    |  |

|--------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------|--|

| Voltmeter                                  | 5                                                            | 0.051110 to<br>511.10 volts                             | 1 microvolt                                        |  |

| Ammeter                                    | 8                                                            | 0.51110 μa to<br>5.1110 amperes                         | 10 picoamperes                                     |  |

| Resistance Bridge<br>(4 terminal, guarded) | 10                                                           | 0.51110 ohms to<br>511.10 megohms                       | 10 microhms                                        |  |

| Comparison Bridge<br>(4 terminal, guarded) | To 5.1110<br>times reference<br>standard                     | 1.0000                                                  | 0.01%                                              |  |

| Ratiometer<br>(Direct reading)             | 3                                                            | 0 to 1.00000<br>0 to 0.051110<br>0 to 0.0051110         | 1 part in 10.5<br>1 part in 10.6<br>1 part in 10.7 |  |

| Null Detector                              | Sensitivity-5 micro<br>ly 1 megohm; AC<br>Guarded, battery o | ovolts; Input impedar<br>C rejection 60 cps<br>perated. | ice—approximate-<br>and up; 80 db,                 |  |

| Accuracy                                   | $\pm 0.02\%$ of readir<br>ranges and function                | ng or 1 switch step<br>ns.                              | on virtually all                                   |  |

| Portable                                   | Rugged portable<br>battery life.                             | case, battery opera                                     | tion, 2000 hour                                    |  |

AT YOUR SERVICE—toll-free telephone network direct to the factory. Check your local directory—call us direct at no cost to you. If we are not listed in your local exchange, call collect 646-4141, Area Code 503.

Electro Scientific Industries, Inc. 13900 N.W. Science Park Drive • Portland, Oregon 97229

World Radio History

# BUDELMAN

## PREFERRED SOURCE FOR COMMUNICATIONS EQUIPMENT

## THE ONLY COMPLETE LINE FOR MICROWAVE • UHF RADIO • MULTIPLEX VF REPEATERS • VHF TRANSMITTERS

Here is a line of communications equipment you can depend upon for outstanding performance and quality from a source that assures fast delivery and low price. A complete line of UHF and microwave radio and multiplex equipment for fixed and transportable applications ... type accepted by the F.C.C. and used in military programs including AN/TRC-18.

## UHF MULTIPLEX RADIO

450-Mc/s and 960-Mc/s band fullduplex and simplex FM radio terminals for thin-route and medium-density (up to 150-Kc/s baseband) communications, telemetry, facsimile, control and data transmission.

## 2 Gc/s MICROWAVE

Medium-density FM microwave equipment for long-haul and short-haul fixed ground-to-space and transportable systems. Compatible with FDM carrier telephone equipment.

## SOLID-STATE MULTIPLEX

Modern plug-in construction designed to conform with C.C.I.T.T. recommendations. Expandable to 240 voice channels. Superior filter design assures top performance. Both onechannel-at-a-time and C.C.I.T.T. group types available.

## WIRE LINE

Carrier telephone equipment and voice frequency hybird repeaters for wire line circuits. Carrier expandable on channel-by-channel basis up to 10 channels.

#### Write today, or call for full data on Budelman UHF Radio, 6000 Mc/s Solid-State Microwave, C.C.I.T.T. Type Multiplex, Low Cost Wire Line Carrier and VF Repeater equipment.

BUDELMAN ELECTRONICS CORPORATION 375 FAIRFIELD AVENUE / STAMFORD, CONNECTICUT 06902 / 203-348-9231 / CABLE ADDRESS: BUDELCO man, South San Francisco, Calif.

- "Solar Cycle and the  $F_2$  Region of the lonosphere," by W. M. Goodall, Bell Telephone Laboratories, Deal, N.J.

- "Atmospheric and Radio Transmissic: Phenomena in Puerto Rico," by G. W. Kenrick and P. T. Sammon, University of Puerto Rico, Rio Piedras, P. R.

- "Transmission on 41 Megacycles," by S. S. MacKeown, B. M. Oliver, and A. C. Tregidga, California Institute of Technology, Pasadena, Calif.

#### Thursday, June 29 9:00 A.M.—11:30 P.M.

(Joint Session with American Institute of Electrical Engineers)

- "The Klystron as a Generator of Very Short Waves," by W. W. Hansen, R. H. Varian, S. F. Varian, D. L. Webster, and J. R. Woodyard, Stanford University, Stanford, Calif.

- "Instruments and Methods of Measuring Radio Noise," by C. V. Aggers, Westinghouse Electric and Manufacturing Company. East Pittsburgh, Penna.; D. E. Foster, RCA License Laboratory, New York, N.Y.; and C. S. Young, Pennsylvania Power and Light Company, Allentown, Penna.

- "Methods of Controlling Radio Interference," by C. V. Aggers, Westinghouse Electric and Manufacturing Company, East Pittsburgh, Penna.

- "Technical Framework of our Television," by E. W. Engstrom, RCA Manufacturing Company, Camden, N.J.

- "A New Standard Volume Indicator and Reference Level," by H. A. Chinn, Columbia Broadcasting System; D. K. Gannett, Bell Telephone Laboratories; and R. M. Morris, National Broadcasting Company; all of New York, N.Y.

#### 2:00 P.M.-4:30 P.M.

- "Electronic-Wave Theory of Velocity-Modulation Tubes," by Simon Ramo, General Electric Company, Schenectady, N.Y.

- "Recent Ultra-High-Frequency Developments," by B. J. Thompon, RCA Manufacturing Company, Harrison, N.J.

- "Simple Television Antennas," by P. S. Carter, RCA Communications, Rocky Point, L.I., N.Y.

- "Continuous-Wave Interference with Television Reception," by C. N. Smyth, Kolster-Brandes, Sidcup, Kent, England,

(Proc. IRE, June 1939, pp. 405-407.)

HEEE spectrum JUNE 1964

World Radio History

6 Gc/s MICROWAVE

Fully solid-state microwave for the

6000-Mc/s band. Most compact . . .

modular construction, less than 24

inches of rack space required. For

high-density long-haul and short-haul

## **Spectral lines**

Problems of the Printed Word. The Editorial Board in its discussions last year rather quickly became convinced that publications were the major means by which our Institute would carry out its responsibility for individual member advancement, and that the same means were necessary to advancement of the field itself. However, in discussion of policy, the Board did not immediately assume that publications need follow present formats.

It studied carefully one proposal, received from several sources, which was based on the premise that we all receive more printed pages than we can assimilate each month. The suggestion then followed that the technical journal of the future should consist only of titles of papers, each with a one-page abstract, and some form of readerservice card by which complete papers might be ordered. The member would then order such complete papers as were of interest to him and would save the space required for filing articles outside his field of interest. Perhaps a certain number of reprints per year could be supplied, at beyond this number a charge would be made.

This plan has merit if it reduces the amount of paper to be filed; it has merit in being expandable to include more papers than are now printed, or to citations and papers from foreign sources. It fails if it does not serve the general technical publication needs of the membership, and the Editorial Board rejected it on this basis. They felt that an abstract of a paper would not carry the prestige of the paper in full, that the plan might not attract the best authors, and that in this way it would retard advancement of the field; it also might fail to provide for the archival needs of the profession.

As to the needs of the average member, the plan provides no means of overcoming human inertia in ordering a needed paper in full; in fact, a member might not know that he should order a certain paper for reading a number of years hence. The plan as proposed suggested that only the abstracts should be carefully edited, the complete papers ordered being published without rewriting or condensing. In this case, libraries attempting to maintain a file in full might be burdened with much excess paper.

The Editorial Board was advised that the economics associated with the present state of the art could not justify such a plan. If quick service on complete papers is to be given, the paper must be on the shelf at the time the abstract is published. This entails the use of a very clear crystal ball in predicting press runs; otherwise the Institute ties up its money in printed paper and shelf space, or is faced with expensive reruns. Not the least of the cost would lie in the salaries of paper pickers charged with assembling the papers for an order.

When we have developed our own technology so that one punches holes in a card to order, the card going direct to a machine that can speedily search its microfilmed files for the requested papers, can cheaply produce a photo copy for the order, and drop that copy in a computer-addressed envelope. Then perhaps we will have an economic rival for our present machines, which set type, print a fixed and paid-in-advance number of copies, and place them in computer-addressed envelopes. We must face these facts: even if the achievement of objectives were comparable by the two methods, the good old magazine method is still the economical one.

Economics was influential in another Editorial Board decision: that concerned with the supply of annual bound volumes of the former AIEE Bimonthlies. The number of orders for these has always been small, and it is difficult and expensive to predict anticipated demand.

Binding is a hand art, and quantity runs produce no saving. The Editorial Board is convinced that those individual members desiring annual volumes would save money by having their monthly copies bound locally instead of buying extra bound volumes from headquarters. To provide for those desiring the service, however, a decision was made to continue bound volumes at a price ensuring recovery of costs, and print them only to fill advance orders at the beginning of the volume year. Special provision was made to meet the needs of the new Group on Electric Power, since that Group will take over the former Bimonthly POWER APPARATUS AND SYSTEMS.

The Editorial Board also noted the present-day pressures for speedy publication of engineering and research results. The verbal presentation requirements for some of our journals have been delaying publication to ten months or more. On the other hand, IEEE PROCEEDINGS, which does not require that a paper be first presented verbally, is able to publish its papers four months after receipt. However, in competitive areas some journals are exceeding the speed of the PROCEEDINGS and it is noted that authors, understandably, consider the factor of speed in choosing the journal in which to publish. To make our various publications attractive to all authors, and because in an organization of 150 000 members, only a small percentage of these can be given the opportunity of reading their papers at meetings, the Editorial Board urged a reconsideration of policies requiring advance verbal presentation before publication. Members of the Board feel that two different audiences and two different purposes are being served in presentation and publication; they are aware of the delays resulting from the presentation requirement, and they see no logic in coupling the needs of one audience to those of another.

These problems may look like fleas on the editorial beast to some; for more about the beast himself, see page 147 of this issue. J. D. Ryder

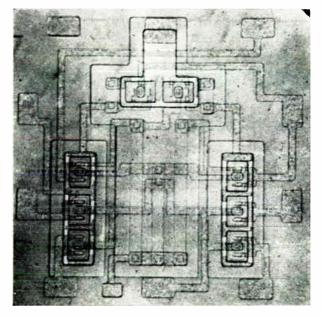

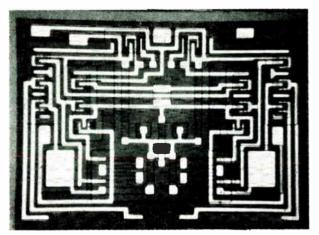

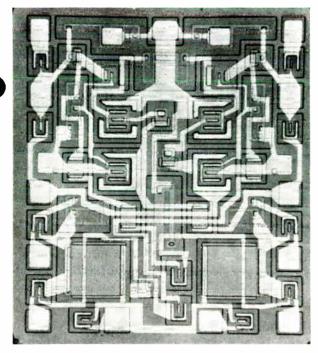

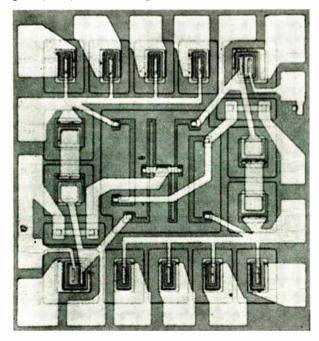

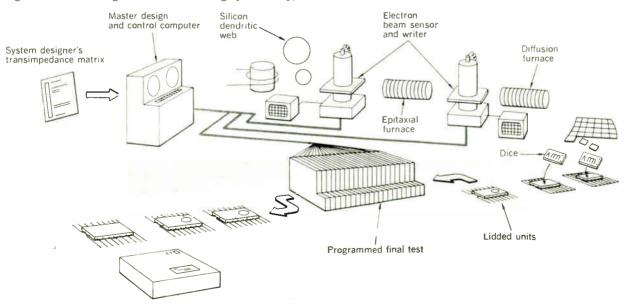

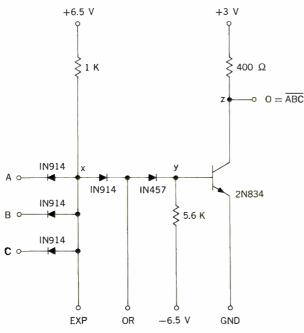

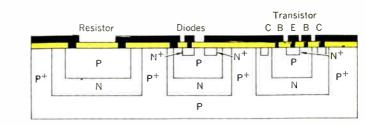

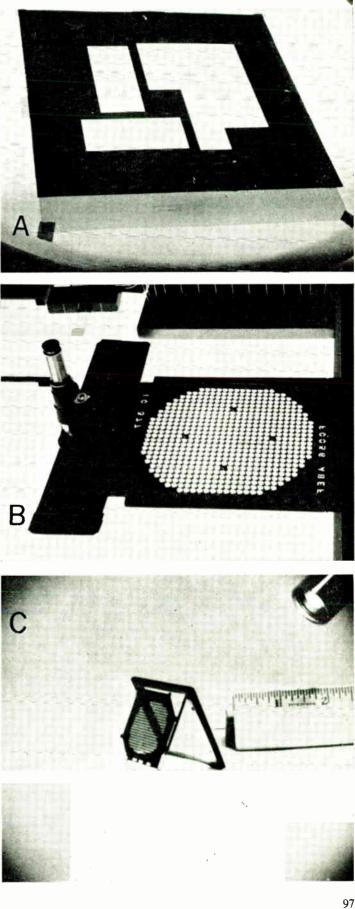

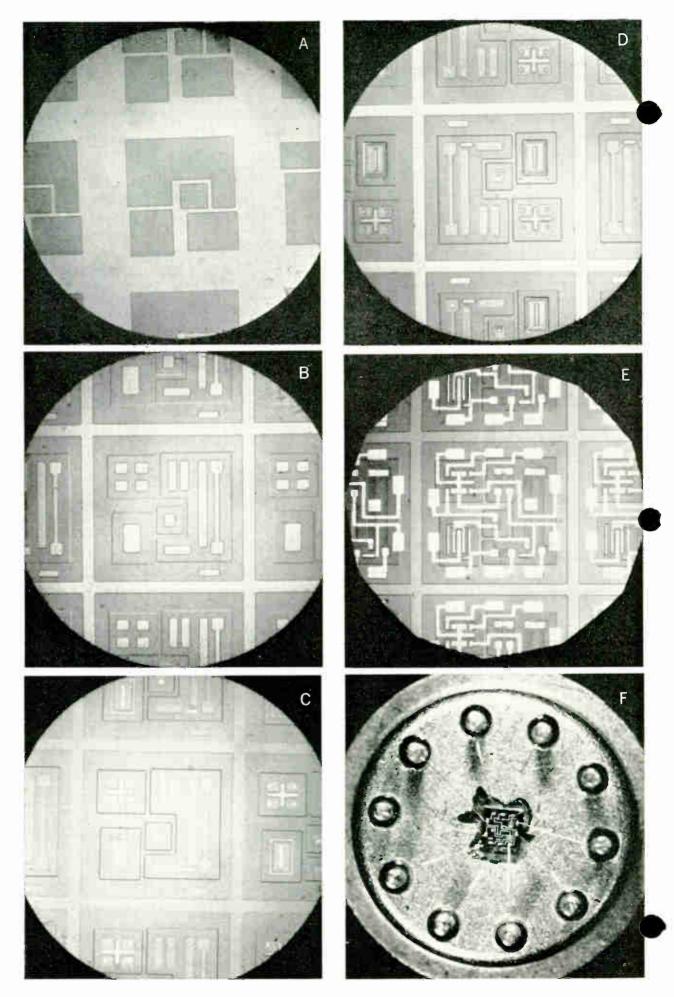

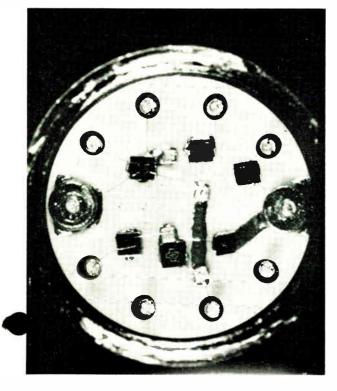

This Westinghouse array of dual DTL gates is fabricated at a density of approximately 1200 gates per square inch. Each gate performs the NAND function and propagates a logic signal at a speed under 17 ns per stage.

## **Integrated circuits**

This edited version of a 1964 IEEE International Convention symposium covers integrated-circuit types; manufacturing principles; the impact of these circuits in government, industrial, and consumer products; and future trends

Patrick E. Haggerty Texas Instruments Inc. C. Lester Hogan Motorola, Inc. Robert N. Noyce Fairchild Camera and Instrument Corporation Leonard C. Maier General Electric Company J. E. Brown Zenith Radio Corporation C. Harry Knowles Westinghouse Electric Corporation

World Radio History

## Introduction

Patrick E. Haggerty, President, Texas Instruments Inc.

Our subject is integrated circuitry. One generally accepted definition describes it as the physical realization of a number of circuit elements inseparably associated on or within a continuous body to perform the function of a circuit.

This discussion will begin with remarks by Dr. Hogan, who will describe the various types of integrated circuits that are available, including thin films, multiple chip, monolithic silicon, hybrid, and magnetic. He will also compare manufacturing processes, performance, and costs. Next. Dr. Noyce will cover the impact of integrated circuitry in government equipment. Dr. Maier will discuss the impact of integrated circuitry in industrial equipment. Mr. Brown's paper will encompass the effects of integrated circuitry applications in consumer equipment. Mr. Knowles will evaluate research and development in the field of integrated circuitry.

At the conclusion, I shall attempt to summarize the economic impact of integrated circuitry on the electronics industry.

## Types of integrated circuits

C. Lester Hogan, Vice President and General Manager, Semiconductor Products Div., Motorola, Inc.

It is difficult to compare the potentials of various technical approaches to a given problem because major breakthroughs often make it possible to achieve particular results cheaper, better, and more reliably by certain methods that may have been discarded as impractical only a few days earlier.

It is impossible to predict breakthroughs in the various present technologies with which we are dealing unless we inject science fiction rather than science.

It is possible, however, to extrapolate efficiencies and productivity within a technology and to set theoretical and practical limits to various technologies that are independent of the breakthroughs. Therefore, I shall make what I feel are proper extrapolations of our current techniques as we become more proficient at the art in which we are engaged. There are many specific approaches to building integrated circuits today. For example, thin-film integrated circuits can be made by sputtering and anodizing tantalum on a suitable substrate without the use of any other element. They can also be made by evaporation of nichrome, aluminum, gold, and copper alloys, or by the IBM cermet approach. All of these methods have definite advantages and disadvantages. Realistic predictions of the potentials of these individual approaches are difficult to make. Many comments can be made, however, about the general approach of thin-film circuits vs. monolithic silicon blocks.

In the IBM cermet method used for thin films, one first needs either a glass or ceramic substrate. A very high-density alumina ceramic may be used with a very fine surface perfection at a size of approximately one-half

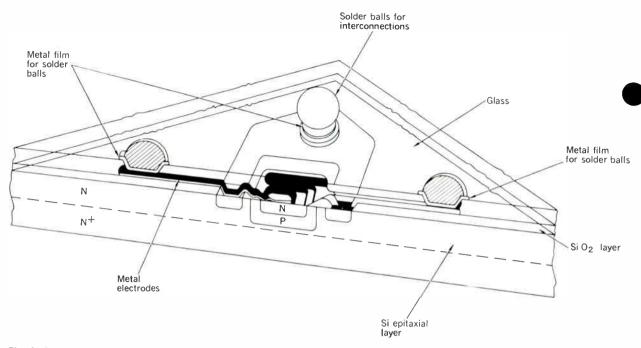

Fig. 1. Cross section of a transistor chip to which three metal balls are attached to make contact with the emitter, base, and collector of the transistor.

inch square, metalized to allow interconnections to be made. The interconnections can be screened on the substrate by using inks that contain noble metals such as silver, gold, or platinum. After firing to fix the interconnections, the resistors are printed by the same technique used for the interconnections but the material used is a combination of palladium-silver and glass particles in an organic vehicle. Resistivities ranging from 50 to 50 000 ohms per square can be obtained. The material is fired at about 800 °C; then copper pins are inserted.

Next, the entire substrate is dipped into solder to cover the pins and interconnection pattern. The solder ensures a good electrical connection between the pins and the interconnection land pattern; it lowers the series resistance of the lands, and it provides the bond required for joining the active elements.

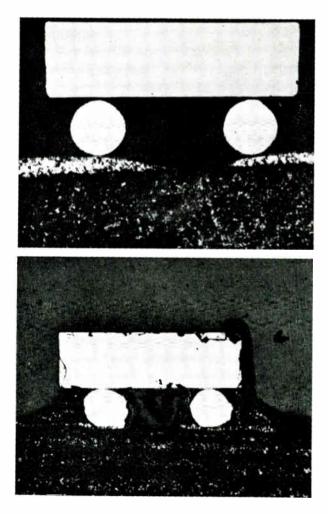

The resistors are then tailored to the desired value by abrasive sand blasting. Finally, the transistors are attached by the flip-chip technique in which three metal balls are attached to the transistor chip to make contact with the emitter, base, and collector, as shown in Fig. 1. When the transistor is flipped over on the alumina cer-

Fig. 2. When the transistor of Fig. 1 is flipped over on the alumina coramic, the three balls contact the three previously tinned land regions on the substrate.

Fig. 3. After heating, the solder flows around the balls and makes both electrical and mechanical connection to the lransistor. Then the unit is potted in plastic.

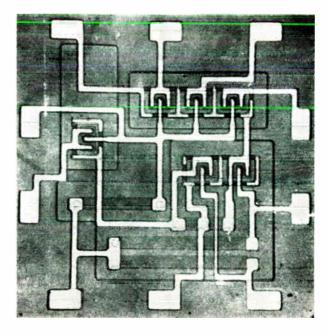

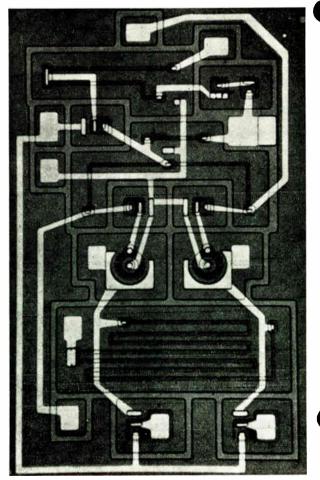

Fig. 4. A typical silicon monolithic integrated circuit. This circuit is a current mode gate that performs both the OR and NOR function in a digital logic system.

Fig. 5. Another silicon monolithic integrated circuit is this flip-flop with set and reset capabilities.

Fig. 6. A third silicon unit is this current mode half-adder.

amic, the three balls contact the three previously tinned land regions on the substrate; see Fig. 2. After heating (Fig. 3), the solder flows around the balls and makes mechanical and electrical connection to the transistor. Finally, the entire substrate is potted in plastic to give a completed thin-film integrated circuit.

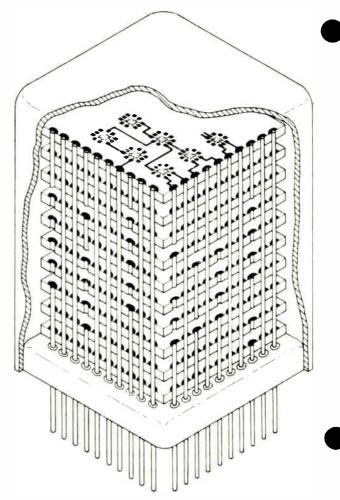

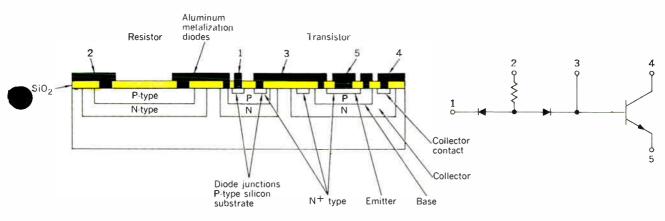

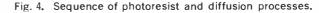

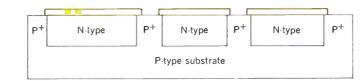

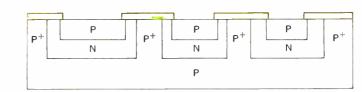

A silicon-substrate monolithic integrated circuit is made by a series of photoresistant and diffusion steps (see "Monolithic integrated circuits," by A. B. Phillips, this issue, pp. 83-101). The main advantage of this process is that more than 400 individual circuits can be processed on one wafer of silicon approximately one inch in diameter. Hence, both the labor and material costs can be kept lower than any other known process provided they are produced in large quantity at reasonable yields. Usually, several hundred wafers can be diffused at one time. Since there can be from 20 to 1000 circuits per wafer, it is possible to process 100 000 circuits at a time.

Typical circuits that are produced by this technique are a current mode gate that performs both the or and NOR function (Fig. 4); a flip-flop with set and reset (Fig. 5); and a current mode half adder (Fig. 6). All of these circuits as shown are on silicon chips of 50 by 50 mils and approximately 400 of them are produced at one time on a single wafer.

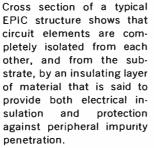

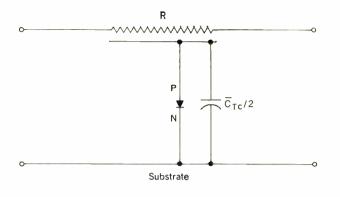

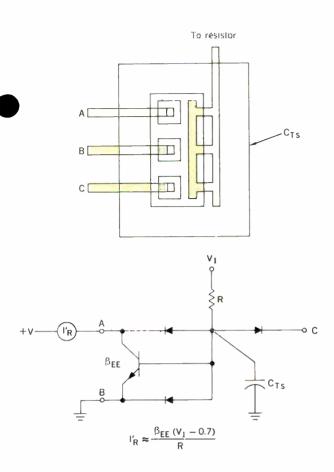

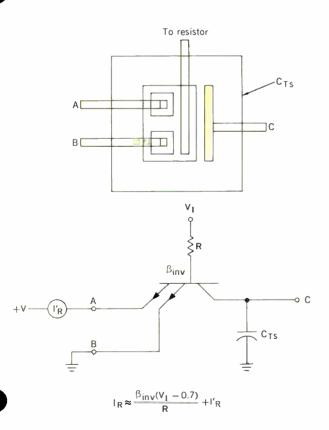

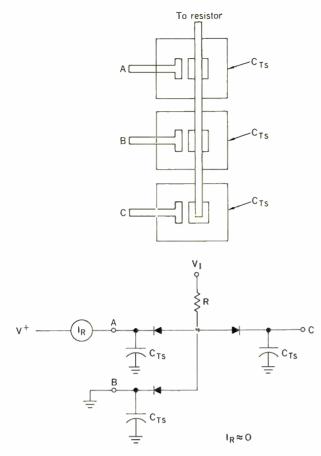

The performance of all silicon-substrate monolithic circuits made to date is limited by the capacitance of the back-biased junctions that occur between the silicon substrate and the isolated n-type islands in which the elements of the circuit are constructed. This parasitic capacitance has been such a limiting factor that there are many exponents of thin-film circuits who have felt that the demand for higher and higher speeds would eventually force the silicon monolithic circuit out of use since thin-film circuits on insulating substrates do not suffer from this effect.

#### 1. Speed comparison data for various NOR gates

|                           | Standard<br>Monolithic,<br>ns | EPIC<br>Monolithic,<br>ns | Hybrid,<br>ns |

|---------------------------|-------------------------------|---------------------------|---------------|

| Delay propagatio          | n                             |                           |               |

| time, t <sub>D</sub>      | 6                             | 5                         | 4.6           |

| Rise time, $t_{\rm R}$    | 8                             | 4.7                       | 4.5           |

| Fall time, t <sub>F</sub> | 9                             | 5.2                       | 5.2           |

| Fanout = 1; fan-          | in = 3; C $_{ m s}$ (test ji  | g) = 13 pF.               |               |

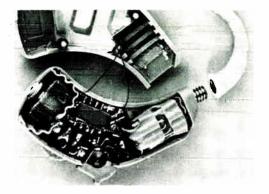

Fig. 7. Hybrid integrated circuits combine one or more integrated circuits with one or more discrete devices.

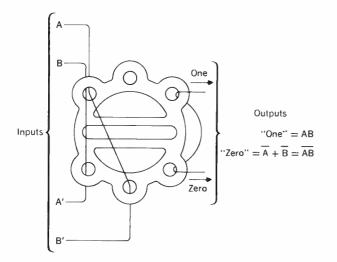

Fig. 8. Multiaperture ferrite cores are used for magnetic elements that can perform most needed logic functions. This particular unit performs as an AND gate.

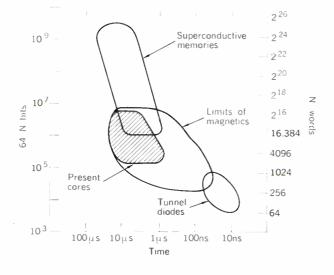

Fig. 9. Limits of speed and storage capacity of magnetic, superconductive, and tunnel-diode memories.

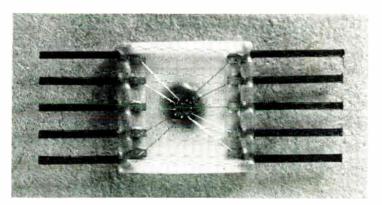

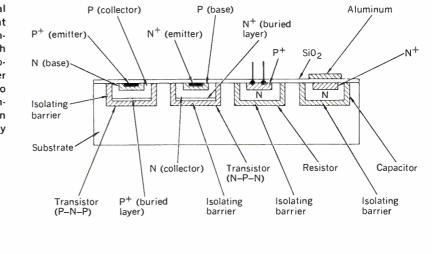

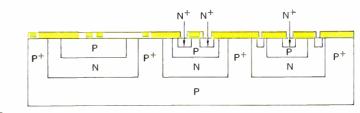

It is, therefore, quite significant that this problem has been solved and the fabrication process for new circuits that do not suffer from this limitation has advanced from the research laboratory to pilot-line production. The new EPIC circuits (see this issue, p. 84) are made by exactly the same processes as before, but now the crossection of the wafer shows that an insulating layer separates each isolation island from the silicon substrate that supports it. The extra processing to obtain this insulating layer will add about 0.5 cent to the cost of the finished integrated circuit when the process is in fullscale production. This insulating layer can be made so thick that the effective capacitance is reduced to zero.

Measurements have been made on hundreds of circuits produced in this new way. They are as fast as their hybrid circuit counterparts which do not suffer from this parasitic problem. Table I shows typical data taken on two monolithic MECL OR-NOR gates. The first set of data was taken on today's standard product; the second was taken on the same gate made by the new EPIC process. Even at this early stage of development, the rise and fall times have been almost cut in half and the propagation delay has been reduced by about 20 per cent.

Hybrid integrated circuits can be made by the combination of one or more integrated circuits in combination with one or more discrete devices as shown in Fig. 7. In spite of its superior performance, the only application for this type of circuitry in the long run is for special purposes where complexity or performance are so demanding that the technology does not permit reduction to monolithic form or when only a few circuits are required and one cannot afford the mask charges associated with the manufacture of monolithic circuits.

There probably will always be circuits than can be realized by the hybrid technique and that cannot be realized by other approaches. But when the quantity of circuits required is great enough -1000 or more of the identical circuit - the hybrid approach cannot achieve the low cost of the monolithic silicon approach.

Magnetic elements have long been used to realize certain circuit functions. Most logic functions can be obtained by the proper winding of wires on multiaperture ferrite cores. Figure 8 shows such a core that can perform the function of an AND gate.

Magnetic circuits can be made at very low cost and probably have a reliability exceeding that of all other integrated circuits. However, the magnetic circuits are extremely large and extremely slow compared to silicon circuits. In addition, transistors are required to drive the magnetic circuits and, if you need a transistor to operate your circuit, you might just as well build the entire function on the silicon substrate. This is true because, in one sense, you can get the other elements free if they do not occupy any more area than the transistors.

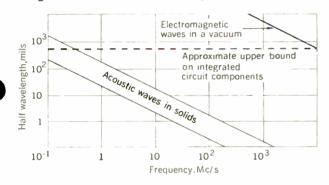

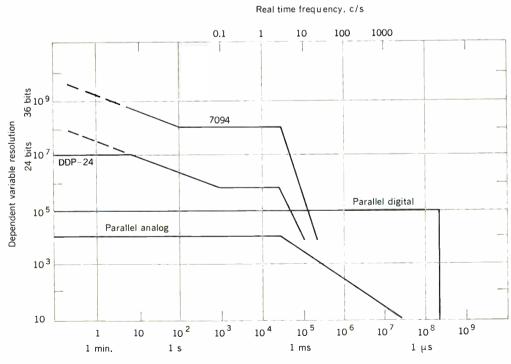

Finally, magnetic thin films and superconducting thin films have received much attention for more than ten years. While they still offer some promise for performing logical functions, their present state of development limits them to use in computer memories. They certainly have very great promise in this area of our technology. Thin magnetic films promise storage capacity as great as ten million bits with cycle times of the order of 100 ns, as shown in Fig. 9 which is taken from a recent paper by J. A. Rajchman of RCA.

Superconducting thin films promise memories with

#### Two-phase J K flip-flop circuit table П.

Tolerance,

Width,

| Year | mils | mils | per square        | Area, mils <sup>2</sup> | Area, mils <sup>2</sup> | per cent | mils           |

|------|------|------|-------------------|-------------------------|-------------------------|----------|----------------|

| 1964 | 0.5  | 0.5  | 200<br>(diffused) | 830                     | 892                     | 40       | 70 × 70        |

| 1965 | 0.3  | 0.3  | 1000<br>(film)    | 45                      | 451                     | 45       | 40 	imes 40    |

| 1966 | 0.2  | 0.2  | 3000<br>(film)    | 14.8                    | 257                     | 50       | 30 × 30        |

| 1967 | 0.1  | 0.2  | 10 000<br>(film)  | 4.4                     | 200                     | 55       | $25 \times 25$ |

Resistors.

ohms

Total

Resistor

Total

Transistor

Surface

Efficiency,

Projected

Die Size,

capacity greater than one billion bits with cycle times as fast as one microsecond. In this particular application these films appear to have no peers but for general circuit use they do not seem to have the promise of achieving the performance, cost, or size of either the silicon monolithic circuit or the general thin-film circuit in which passive circuit elements are deposited on an insulating substrate.

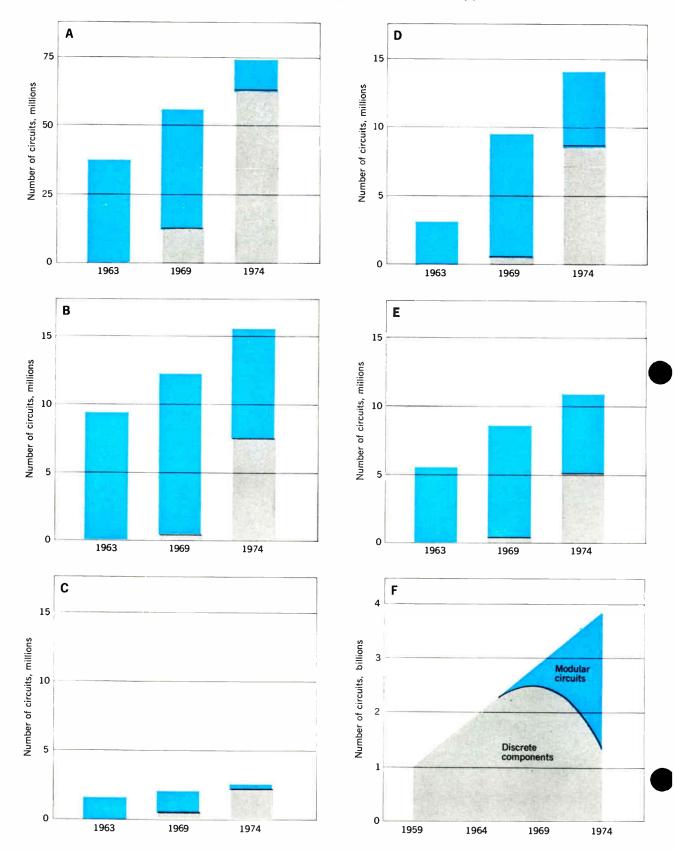

After surveying the field, one is left with two types of circuits that promise to have general-purpose use for integrated circuits of the future. These are thin-film circuits and monolithic silicon circuits. Each has its special field of application but it appears that monolithic silicon will have the edge in digital circuit applications through cost alone.

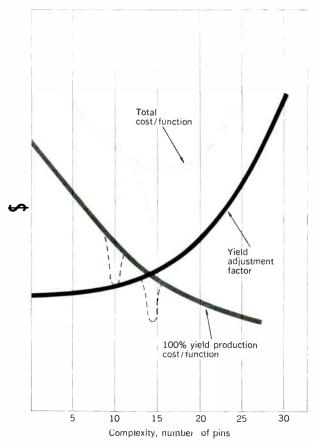

Very complex silicon circuits can now be constructed on a chip approximately 50 by 50 mils. The cost to carry a wafer through all steps of diffusion and metalization, provided it is run at a moderately high volume and at a 100 per cent yield, is about \$10 per wafer including normal overhead. Assuming that a one-inch-square wafer can be processed at a 100 per cent yield before packaging, each wafer will contain 400 individual circuits which would then cost 2½ cents apiece. Even if the ultimate yield is as low as 50 per cent, the cost of the finished silicon monolithic integrated circuit, before packaging, will be less than 5 cents.

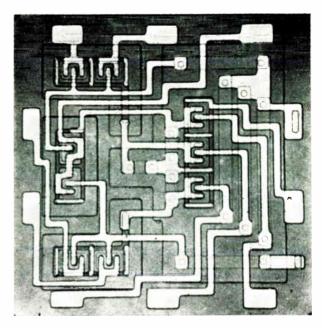

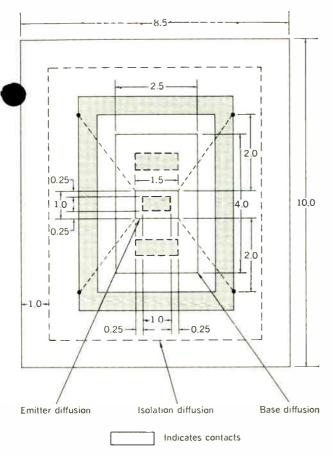

Over the next three years, the resolution with which silicon circuits can be built will steadily improve. In the research and development laboratories, one bit of a twophase-shift register has been placed successfully on a 70mil-square die. Again assuming a 50 per cent yield, this entire circuit consisting of 33 transistors, 27 resistors, and 2 diodes, could be built for less than 10 cents.

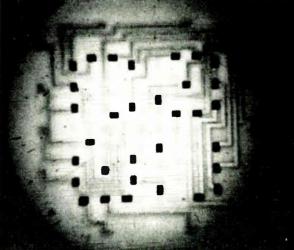

A reasonable projection of what may be achieved shortly is illustrated by Fig. 10. This circuit—a J K flipflop--contains 14 transistors, 10 resistors, and 2 capacitors. It has already been placed on a 70-mil square die; see Table II. The possibility of placing it on a 25-milsquare die by 1967 may be questioned but there is little doubt that the circuit will be placed on a 30-mil-square die by 1966. At a 50 per cent yield, with a reasonably high volume before packaging, this circuit will cost less than 2 cents to process, including factory overhead.

Basically, the cost of producing a silicon monolithic integrated circuit or a silicon transistor is related both to die size and yield. One cannot talk about die sizes much less than 20 mils square because the difficulty in handling and alignment during packaging and attachment of leads mitigates against smaller die sizes. Thus, assuming we are attempting to build transistors on a one-inch wafer rather than integrated circuits and assuming an ultimate die size of 20 mils square, one is led to individual transistor costs in excess of one cent apiece as compared to a complete J K flip-flop for two cents. All these costs, of course, refer to a device before lead attachment and packaging.

Any method that requires the construction and attachment of individual transistors to a circuit can never achieve the low cost of the monolithic silicon approach to integrated circuits, provided the yield percentages are comparable.

Whenever one builds any device through the successive diffusion of impurities into silicon, the resulting devices show a distribution of parameters. In testing transistors, one can divide the distribution into a reasonable set of limits and hopefully find a market for all the devices which come off the production line.

In building integrated circuits, it does not seem feasible to segregate the devices into different categories (as is done with transistors) to accommodate the wide variations that occur from device to device. Also, the yield

Fig. 10. This J K flip-flop silicon integrated circuit contains 14 transistors, 10 resistors, and 2 capacitors.

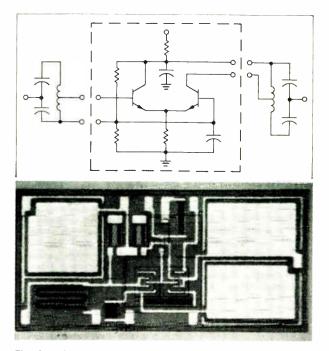

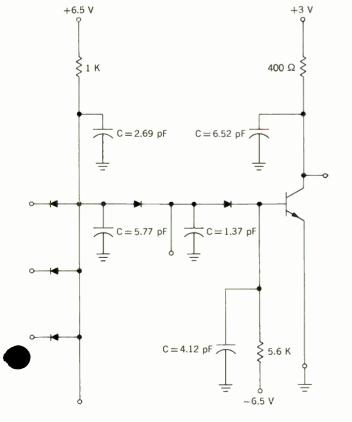

Fig. 11. Circuit diagram and silicon monolithic integrated circuit for a 120 Mc/s RF amplifier. Specifications for the circuit are: B<sup>+</sup> voltage, +12 V; drain, 2.3 mA; power gain, 18 dB at 120 Mc/s; noise figure (1000-ohm source), 6.0 dB at 120 Mc/s; input resistance, 1200 ohms; input capacitance, 4.5 pF; output resistance, 2500 ohms; and output capacitance, 5 pF.

of any device, whether it be a circuit or component, is related exponentially to the area it covers on a silicon chip. Integrated circuits must by nature cover more area than an individual transistor contained within the circuit and, therefore, one should expect for some time to come that more good transistors than integrated circuits will be obtained per wafer.

Present transistor production, however, must strike a balance between a variety of extremely tight specification limits, with the result that realistic yields are often much lower than most of us care to admit. A transistor is usually specified in extreme detail. We don't make the selection from just one distribution curve and its resultant yield loss; we make successive selections from 20 to 40 different distribution curves. Conflicting requirements such as high breakdown voltage, low saturation resistance, high current gain, and low storage time, are all specified. If the distribution curves are so tight that 90 per cent of the transistors fall within the specification limits for 20 specified parameters, the resulting yield to all specifications will be about 12 per cent.

This situation need not occur with integrated circuits since the circuit designer is concerned with black-box specifications concerning circuit performance and not with detailed characteristics of the individual components within the circuit. If the integrated circuit functions at all, it usually meets all the specifications placed on it, once one has learned how to make it using the proper mask design, the proper processing steps, and the proper resistivity of the starting wafers. To illustrate what has been achieved, Fig. 11 shows both the circuit diagram of a 120 Mc/s RF amplifier and its appearance as a silicon monolithic integrated circuit. Several thousand of these circuits have been built with an actual yield of 90 per cent where yield is measured in terms of the direct-current operating levels and gain vs. frequency of the amplifier. The 90 per cent yield is measured relative to the specifications shown in the caption of Fig. 11. These simple specifications are the kind that might become realistic when one deals with circuits instead of individual devices.

We have accumulated vast data on the yields of our standard integrated circuit and transistor lines. The yield on the former is about the same as that for the very critical transistors now being produced. Hence, from these data, it seems reasonable to assume that monolithic silicon integrated circuit yields and transistor yields are comparable for similar size dies.

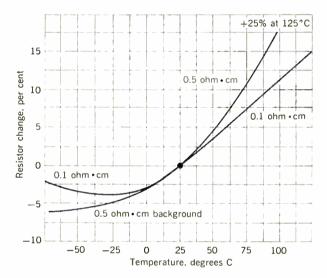

These factors may give the impression that monolithic silicon integrated circuits will eventually eliminate thinfilm elements, but this is not the case. Diffused resistors have such a large temperature coefficient and the maintenance of microscopic mechanical tolerances is so difficult that one cannot build such resistors with tolerances less than 20 per cent with any reasonable yield. Critical circuits, which require closer resistance control, therefore must be made by thin-film or other techniques. The characteristics of various resistors for use in integrated circuits is detailed in Table III.

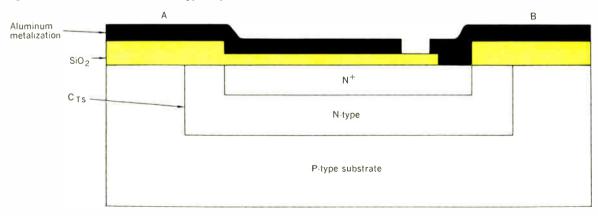

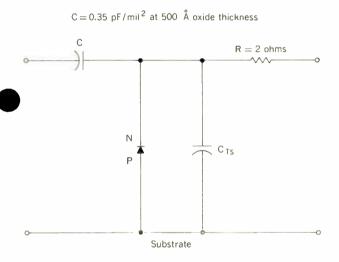

Capacitors made with diffused p-n junctions have very low Q, are voltage sensitive, are polar, and can be subjected only to relatively low voltage. For these reasons, thermally grown silicon dioxide or other glass is usually used as a dielectric rather than the junction capacitance. Properties of such capacitors are detailed in Table IV.

The major disadvantage of silicon substrate capacitors, however, is their cost. If thermally grown silicon dioxide is used as the dielectric, Table IV indicates that capacitance values of about 0.25 pF/mil<sup>2</sup> can be obtained. Again considering our \$10 one-inch wafer, we see that a capacitor built on a silicon substrate would cost about 0.008 mill per picofarad at 50 per cent yield. Therefore, capacitors placed on silicon substrates must be limited to rather small values.

For comparison, we can calculate the cost of a thinfilm capacitor that uses pyrolytically deposited boroaluminosilicate glass as the dielectric:

| 1/2 by 1/2-inch substrate | \$0.12 |

|---------------------------|--------|

| Aluminum interconnect     | 0.04   |

| Boroaluminosilicate       | 0.02   |

| Aluminum counterelectrode | 0.04   |

|                           | \$0.22 |

Assuming a 90 per cent yield on this process, the actual cost is 24 cents. Again, if the capacitor covered the entire area, the capacitance value would be 0.1  $\mu$ F, or a cost of 2.4  $\times$  10<sup>-4</sup> cents/pF. Thus, it costs about 30 times more to make a capacitor on a silicon substrate than on an insulating substrate using thin-film techniques.

Completely passive circuits (those requiring no transistors or diodes) with large capacitance and resistance values will be cheaper to construct on insulating substrates. However, this restriction applies principally to *large* capacitors and *large* resistors. If the values required are small enough so that the capacitors and resistors

World Radio History

can fit on a 50-mil silicon chip, it may be cheaper to build on silicon because it is difficult to obtain very small ceramic substrate.

The problem of determining whether to put passive components on silicon or to place them on an insulating ubstrate and attach the silicon active elements to them is a complex problem involving the actual size of the finished circuit and the cost of the attachment procedure.

If the passive components require an area that is trivial compared with the area needed for the transistors and diodes in the circuit, the use of the silicon substrate will provide an excellent economy. But if the area required for the passive components is greater than that needed for the active components, packaging and interconnecting techniques will determine whether it is cheaper to use the silicon substrate or an insulating substrate. And, if the circuit's passive components, when placed on the silicon substrate, occupy essentially the entire area and there are relatively few active components, the thin-film technique for passive components with active elements attached would be the best approach.

A basic guide is to determine whether the passive components will occupy more than the minimum die size that can be used otherwise. There is a gray area between the two extremes where interconnection, packaging techniques, and actual substrate costs will determine the approach. To illustrate, assume that the split in this gray area occurs when the passive com-

#### III. Integrated circuit resistor characteristics

|                                            | Monolithic Silico | n Components | Thin Film               |          |  |

|--------------------------------------------|-------------------|--------------|-------------------------|----------|--|

|                                            | Diffused Diffused |              | Components              |          |  |

| Parameter                                  | р                 | n            | Nichrome                | Cermet   |  |

| Sheet resistance, ohms/square              | 100-300           | 2.5          | 40-400                  | 100-1000 |  |

| Resistance per substrate area*,            |                   |              |                         |          |  |

| ohms/mil²                                  | 50-150            | 1.25         | 20-200                  | 50-500   |  |

| Temperature coefficient, ppm/              |                   |              | $\pm 100$ adjustable to |          |  |

| °C                                         | +2800 to 1500     | +100         | within $\pm 10\%$       |          |  |

| Power dissipation per                      |                   |              |                         |          |  |

| active resistor area†, mW/mil <sup>2</sup> | 3                 | 3            | 2                       |          |  |

| Maximum voltage, volts                     | 20                | 6            | _                       |          |  |

| Tolerance for high yield, ‡ per            |                   |              |                         |          |  |

| cent                                       | ±20               | _            | ±8                      | ±8       |  |

| Distributed capacitance§, pF/              |                   |              |                         |          |  |

| mil <sup>2</sup>                           | 0.2               | 0.6          | _                       | _        |  |

Assumes 1-mil-wide stripe, and 1-mil-wide spacing.

Depends upon package and heat sinking.

Tighter tolerances available at higher cost.

Negligible using recent EPIC techniques.

#### IV. Integrated circuit capacitor characteristics

|                                                   | Monolithic Silicon Components         |                                       |                                        | Thin-Film Components |                                   |                   |  |

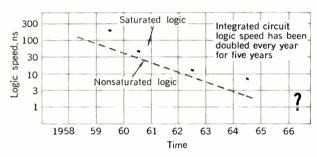

|---------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|----------------------|-----------------------------------|-------------------|--|