#### articles

#### **Spectral lines** 33

#### Energy crisis: seeking the real alternatives, II Donald Christiansen

Technologists must address the energy situation in "bite-size" pieces; electronics, itself, may contribute solutions

#### Computer report I Hard-soft tradeoffs 34

#### Howard Falk

Large-scale integrated gates and read-only memories are displacing software from many of its traditional roles

#### Computer report II More power by networking 40

#### C. Gordon Bell

Whether computers communicate as equals or in a superior -subordinate mode, the outcome is usually positive

#### Computer report III Data by the packet 46

Lawrence G. Roberts

Because computing costs are now so low, a new concept of data communications is feasible

#### Computer report IV A checkup: minicomputer 52 software

Howard Falk Great expectations for new applications hinge on the usefulness of software packages

#### **Computer report V** 57 Power supplies: how to trim the budget Don Mennie

Orphaned in the world of decreasing cost-per-bit, power supplies cry for cost reduction

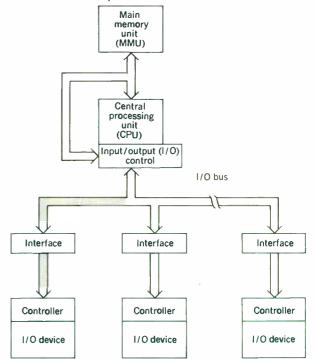

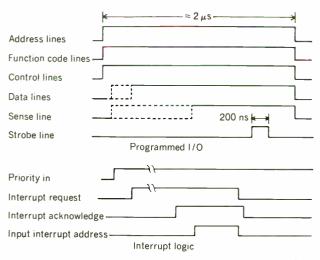

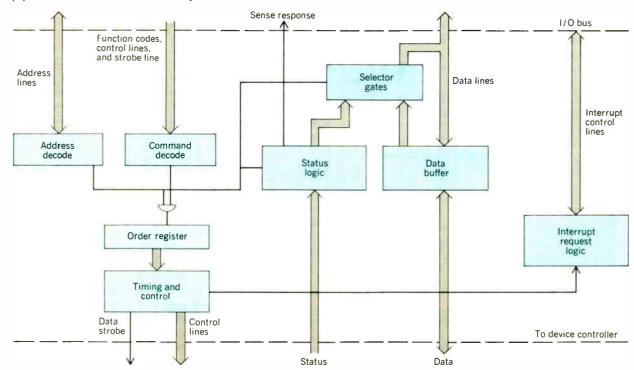

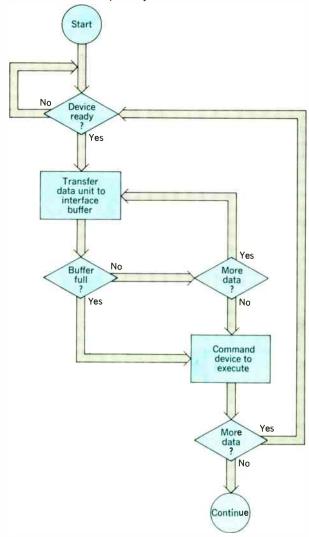

#### **Computer report VI** 64 Minicomputer interfaces: know more, save more A. A. J. Hoffman, Robert L. French, Guy M. Lang

When a standard interface is inadequate, you can pay for custom design-or do it yourself

#### **Computer report VII** 70

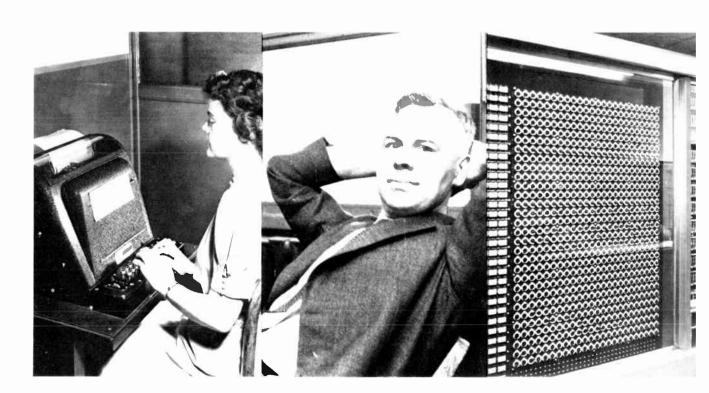

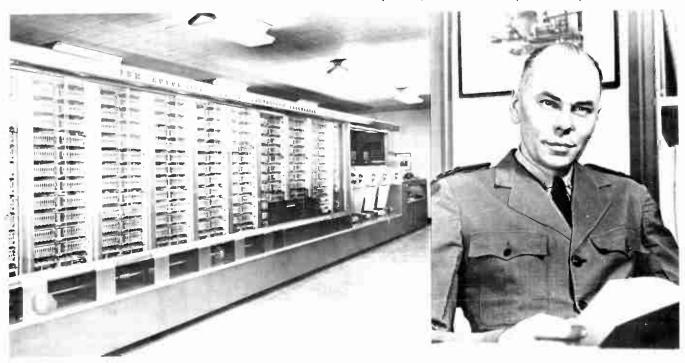

#### The effervescent years: a retrospective Henry Tropp

Behind the Computer Revolution lay the vision and perseverance of a handful of pioneers committed to open information exchange

#### departments

- 10 Meetings

- 13 News from Washington

- 14 Energy report

- 111 News from industry

- 112 Regional news

- 16 Calendar

- 22 Focal points

- 26 Forum

- 94 Inside IEEE

- 103 Scanning the issues

- 106 IEEE tables of contents

- 110 Future special issues

- 116 IEEE Standards

- 116 Special publications

- 117 Educational aids

- 118 Book reviews

- 122 People

- 124 In future issues

Copyright © 1974 by THE INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS. INC.

IEEE spectrum FEBRUARY 1974

When we were designing our first computer, we decided to put as big a subsystem as we could on each PC board.

Within three years, the accepted way to build small computers was the Data General way.

And when we were working on our second computer, we made it completely compatible with our first. So all our software and peripherals could run on both computers. And the interfacing would be just as easy.

And we held on to that idea. The nine computers we've made since then are fully compatible, too. For the same reasons.

In other words, we invented what's now known as a "family" of small computers.

We're at it again with our Nova 2. Only this time we're helping you get your products out into the marketplace faster.

We've given the Nova 2 the operating systems you'll need to develop your software and run your hardware. So you won't have to come up with your own.

We're offering low-cost 16K memory so your programmers can work in high-level languages. And write software faster.

We have the general purpose interfaces you'll need to make that job go faster.

And we have the support organization you can call anytime you need help.

Making computers easier for you to work with isn't exactly standard in the industry.

Someday it may be.

At Data General, that day is now.

## DataGeneral

### The computer company you can understand.

• Data General Corporation Southboro, Massachusetts 01772, (617) 485-9100. Datagen of Gunada Ltd., Hull, Quebec (819) 770-2030 Data General Europe, Paris, France 504-23-44.

#### **IEEE spectrum FEBRUARY** 1974

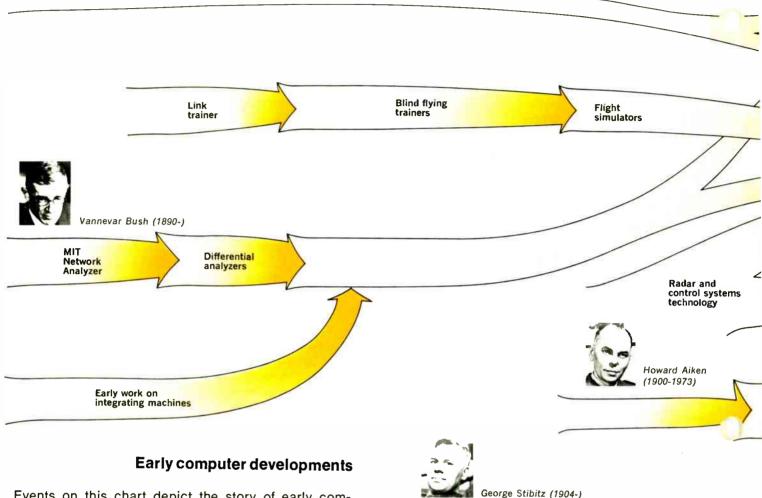

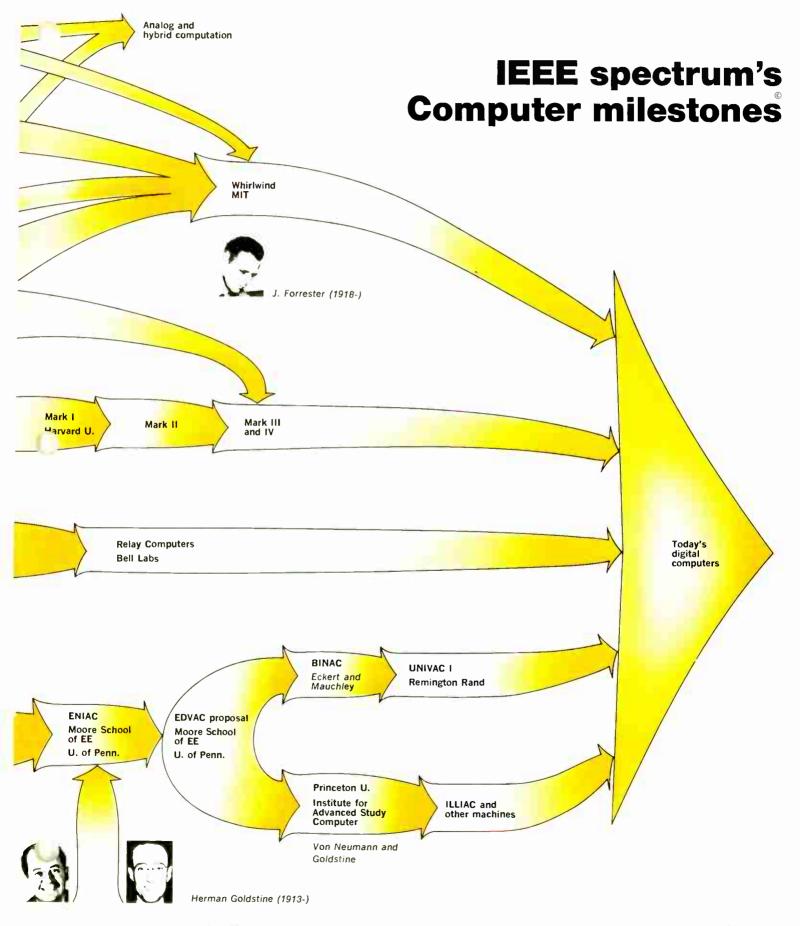

#### 80 Special chart Computer milestones

**IEEE Spectrum Staff** Early computer developments are called out in a two-page pictorial spread

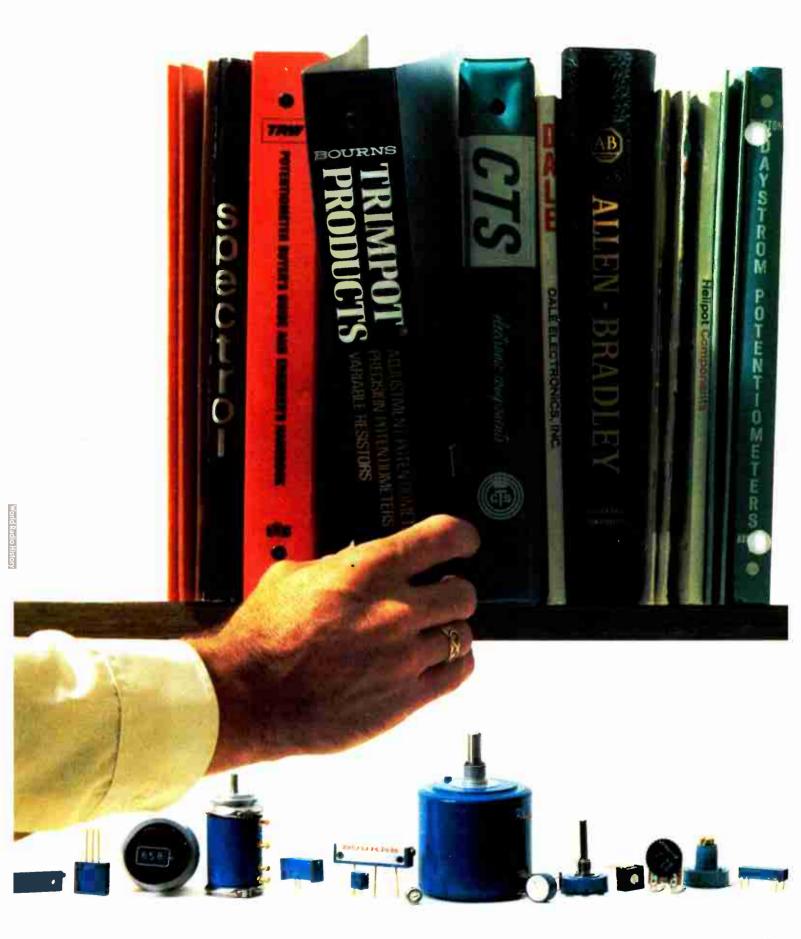

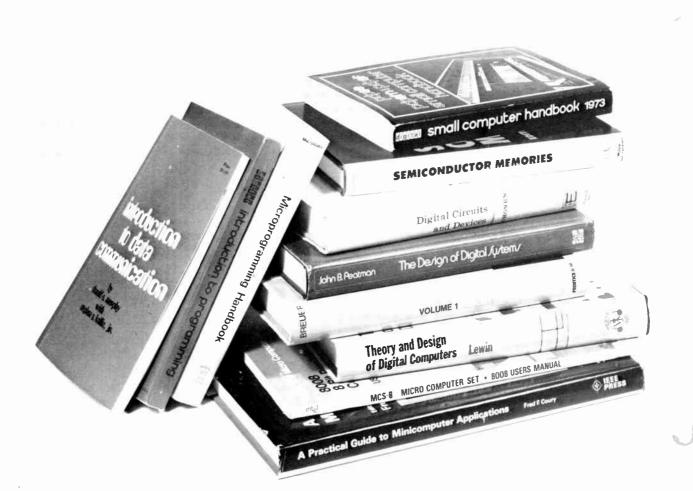

#### 82 Computer report VIII An \$88 book shelf W. R. Beam

Twelve volumes, selected from hundreds available, form this digital engineers' compact reference and study library

#### 85 Energy/power

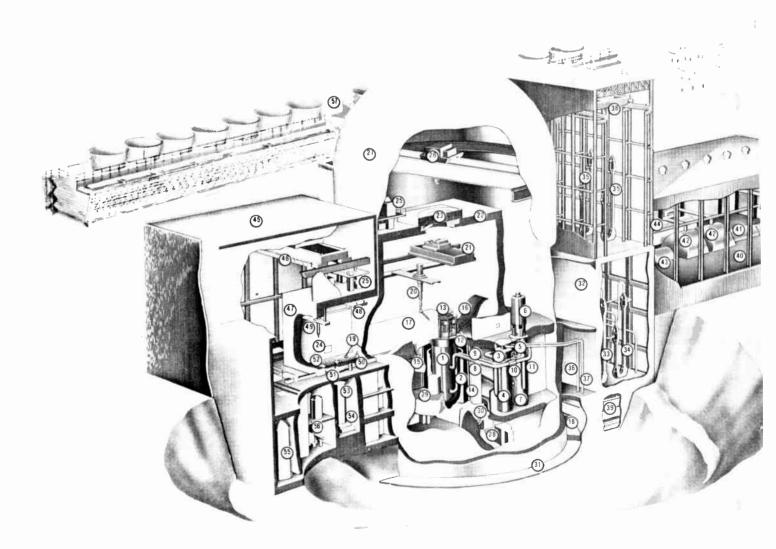

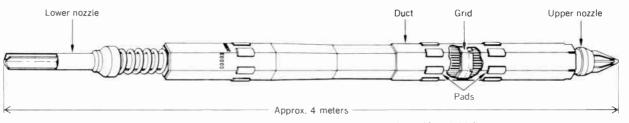

#### The fast-breeder reactor: when, where, why, and how? Gordon D. Friedlander

An LMFBR pilot plant will be built and the HTGR is under study; the main factors involved are efficiency and safety

#### 90 Special report INTERCON '74: getting down to business

Gerald Lapidus

Conference program organizers are serious about new products, new markets, and about solving society's problems, too

#### 96 New product applications

Power sources, solid-state devices, and other products now available that give the engineer greater scope for design and application are described

#### 101 Spectrum's hardware review

A listing of new products and manufacturers, about which readers may obtain information

#### 102 Applications literature

Brochures, manuals, and applications handbooks selected by the editors

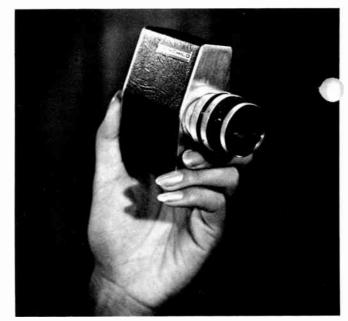

#### the cover

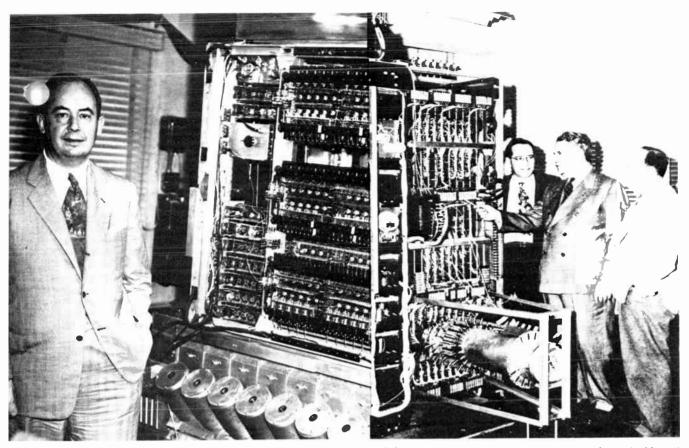

The assemblage that keynotes Spectrum's 48-page computer report hangs in the office of the Director of Communications, General Telephone and Electronics Information Systems. GTE commissioned artist Vin Giuliani to construct it.

#### spectrum

#### EDITORIAL STAFF

Managing Editor: Ronald K. Jurgen; Senior Staff Writer: Gordon D. Friedlander; Staff Writer: Marce Eleccion; Associate Editors: Howard Falk, Gerald Lapidus, Don Mennie; News Editor: Evelyn Tucker; Contributing Editors: Alexander A. McKenzie, Michael F. Wolff; Copy Editor: Ellis Rubinstein; Editorial Assistants: Ann L. Battiste, Stella Grazda; Production Manager: Ruth M. Edmiston; Art Director: Herbert Taylor; Assistant Art Director: Janet Mannheimer; Technical Graphic Artist: Morris Khan; Art Assistant: T. Dale Goodwin; Business Manager: Carl Maier

#### EDITORIAL BOARD

Chairman: Donald Christiansen Norman Abramson, Roy Amara, Norman Balabanian, F. E. Borgnis, L. M. Cole, Charles Concordia, J. M. Early, A. A. J. Hoffman, Eugene Mittelmann, E. N. Procter, Shigebumi Saito, R. L. Schoenfeld, Harold Sobol, A. J. Stegeman, J. J. Suran, A. S. Taylor, F. E. Terman, W. H. Ware

World Radio History

#### Editor: Donald Christiansen

### Need to know where it's at?

CVI video instruments provide X-Y coordinate information from TV signals produce boresight reticules – digitize target location - analyse scenes - and more. If you use television and need to reduce data, add special markers, or perform other operations, please call us.

We make things like:

- 304 Motion Detector

- 321 Video Analyser

- 603 Data Insertion Generator

- 610 Video Pointer

- 621 X-Y Indicator

- 622 X-Y Digitizer

- 630 Anomaly Detector

Colorado Video, Incorporated P.O. Box 928 Boulder, Colorado 80302 (303) 444-3972

Video instruments for data acquisition, processing, Transmission, and display.

Circle No. 2 on Reader Service Card

#### **IEEE** Publications Operations

#### **IEEE PUBLICATIONS BOARD**

F. S. Barnes, Chairman

| STAFE               |               |               |

|---------------------|---------------|---------------|

| Charles Concordia   | S. J. Kahne   | W. J. Spencer |

| Donald Christiansen | A. L. Hopkins | A. C. Schell  |

| W. R. Beam          | R. C. Hansen  | J. E. Rowe    |

| J. J. Baruch        | J. M. Early   | R. W. Lucky   |

|                     |               |               |

#### STAFF

Elwood K. Gannett, Director, Publishing Services Patricia Penick, Administrative Assistant to the Director H. James Carter, Manager, Editorial Services Lawrence Liebman, Manager, Printing Services William R. Saunders, Advertising Director Henry Prins, Research Manager

Carl Majer, Advertising Production Manager

Carol D'Avanzo, Assistant Advertising Production Manager

**IEEE SPECTRUM** is published monthly by The Institute of Electri-cal and Electronics Engineers, Inc. Headquarters address: 345 East 47 Street, New York, N.Y. 10017. Cable address: ITRIPLEE. Tele-phone: 212—752-6800. Published at 20th and Northampton Sts., Easton, Pa. 18042. **Change of address** must be received by the first of a month to be effective for the following month's issue. Please use the change of address form below. **Annual subscription:** IEEE mem-bers, first subscription \$3.00 included in dues. Single copies \$3.00. Nonmember subscriptions and additional member subscriptions availbers, first subscription \$3.00 included in dues. Single copies \$3.00. Nonmember subscriptions and additional member subscriptions avail-able in either microfiche or printed form. Prices obtainable on re-quest. Editorial correspondence should be addressed to IEEE SPECTRUM at IEEE Headquarters. Advertising correspondence should be addressed to IEEE Advertising Department, at IEEE Head-quarters. Telephone: 212-752-6800. Responsibility for the contents of papers published rests upon the authors, and not the IEEE or its members. All republication rights, including translations, are reserved by the IEEE. Abstracting is per-mitted with mention of source. Second-class postage paid at New York, N.Y., and at additional

mitted with mention of source. Second-class postage paid at New York, N.Y., and at additional mailing offices. Printed in U.S.A. Copyright© 1974 by The Institute of Electrical and Electronics Engineers, Inc. IEEE spectrum is a registered trademark owned by The Institute of Electrical and Electronics Engineers, Inc.

V. P. Kodali

**OTHER IEEE PUBLICATIONS:** IEEE also publishes the PROCEED-INGS OF THE IEEE and more than 30 Transactions for IEEE Societies and Groups with specialized interests within the electrical and elec-tronics field. Manuscripts for any IEEE publication should be sent to the editor of that publication whose name and address are shown on pp. 101-102 of the January 1974 issue of *Spectrum*. When in doubt, send the manuscript to E. K. Gannett. Publishing Services, at IEEE Headquarters, for forwarding to the correct party.

IEEE also copublishes, with the Institution of Electrical Engineers of London, England, Electrical & Electronics Abstracts and Com-puter & Control Abstracts, as well as their companion titles journals, Current Papers in Electrical & Electronics Engineering and Current Papers on Computers and Control.

| Name (Plea                       | <b>ING?</b> PLEASE NOTIFY<br>US 4 WEEKS<br>IN ADVANCE                                                                                                                                                                                                                                     |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address<br>City<br>MAIL TO: IEEE | State/Country Zip                                                                                                                                                                                                                                                                         |

| ACH<br>3EL<br>.RE                | <ul> <li>reet, New York, N.Y. 10017</li> <li>This notice of address change will apply to all publications to which you subscribe.</li> <li>List new address above.</li> <li>If you have a question about your subscription place label here and clip this form to your letter.</li> </ul> |

### Energy crisis: seeking the real alternatives, II

In January we addressed the allied problems of (1) determining the options available in the current and continuing energy situation, and (2) educating the general public to those options and their probable consequences.

Underlying this discussion was the premise that what the public thinks and how it reacts can significantly affect the overall situation. As an easily understood example, prediction of long lines at gasoline stations becomes, in part, self-fulfilling simply because drivers are gassing up three or four times more frequently than they normally would. And shortages at filling stations result in part because lots more gas is in auto tanks and owners' gas cans, not in station storage tanks.

On a grander scale, the reactions of thought leaders and pressure groups among the citizenry can influence the Government to assume certain postures with respect to global politics—which in turn may aid or hinder the flow of oil to the U.S. And the interactions of various interest groups can spawn new, unanticipated problems.

While there may be little reason to question the goal of educating the public on its options, a serious question does arise concerning whether the technological community can, indeed, define the options and attach to them possible consequences with any degree of certainty. Do we not have enough difficulty in determining what will be the probable effects of the energy crisis, at its current level of complexity, on our own electrical/electronics industries?

Already, the city of Los Angeles has enacted emergency legislation that would cut back consumption of power supplied by its municipal utility company. West Coast semiconductor manufacturers are worried that arbitrary cutbacks could do irreparable harm, as, for example, in the case of diffusion tubes which cannot be switched off and on at will. And customers of computer service bureaus are wondering just how likely are the possibilities of power blackouts damaging transistors, rotating memories, and read/write heads, as has been predicted by the service bureaus themselves in hearings before the California Senate Public Utilities and Corporations Committee.

Engineers concerned with possibilities such as those just mentioned may feel their problem unique—that new regulations and legislation touch them but not the power utilities themselves. Such is not the case, as underscored in a statement filed with the Federal Energy Office by the Edison Electric Institute on December 20. It concludes, concerning the allocation of middle distillates for use by the electric utility industry, that proposed mandatory allocation regulations do not provide priority status to the electric utility industry as intended by the Emergency Petroleum Allocation Act of 1973. Electric utilities have been classified in the lowest categories for middle distillate and residual fuel oils, the report asserts, noting that the utilities are now using about 100 million barrels of middle distillate fuel oil each year. most of it for combustion turbines and internal combustion engines. Such fuel oil is also used as ignition fuel for coal-fired generating units and for flame stabilization under low-load conditions.

The availability of residual fuels is just one of the many complexities facing the power industry that place it in the position of brother-in-arms with the electronics industries.

On the other hand, what bodes ill for some industries may prove just the opposite for others, like the communications industry. For now the incentives to communicate instead of travel are enhanced. Telephone utilities and video and data transmission services may come into even greater demand. And what about the semiconductor industry? Since solid state is an energy-saving technology, is it not possible to provide incentives to manufacturer and customer alike to "go solid state" faster, and in ways not previously considered? In this regard, one recalls that the Japanese Government subsidized all-solid-state television for domestic consumption because, compared to hybrid sets, it saved energy.

Today, microprocessors can be exploited to control energy-producing or energy-consuming processes at their sources to increase efficiency of energy usage. And, compared to cores, semiconductor memories are conservative of power. These examples suggest that electronics technology, if not itself stifled by materials or energy shortages, may operate in a positive mode insofar as the overall energy picture is concerned.

Such optimistic possibilities notwithstanding, in view of the many energy scenarios that can be constructed based on known options, it is clear that the energy crisis cannot be readily defined. If it could be, it would doubtless be representable by some multiloop nonlinear feedback system—which, unfortunately, is itself time-dependent.

In the meantime, we technologists shall have to address the situation piecewise, the best way we can—in pieces small enough to handle, but large enough to have lasting results. *Donald Christiansen, Editor*

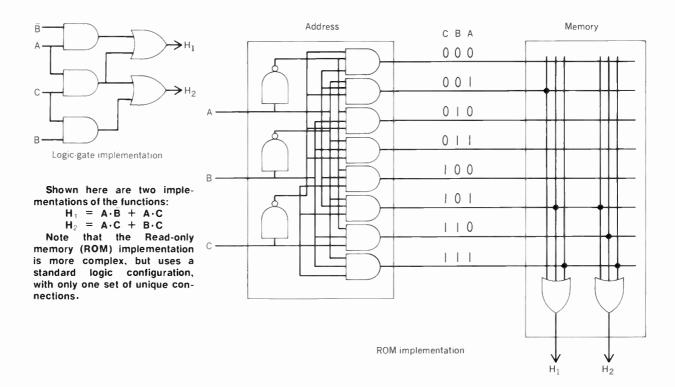

### Hard-soft tradeoffs

### Large-scale integrated gates and read-only memories are displacing software from many of its traditional roles

From the system cost viewpoint, hardware and software have exchanged roles during the past two decades. In the early '60s, hardware used to account for well over 50 percent of system costs. Today, the hardware portion is substantially below 50 percent and that portion is declining more rapidly today than in the past.

There has been much attention given to the idea that large-scale integrated (LSI) circuits can economically provide computer functions that would otherwise be performed by software. Experience had demonstrated that this is indeed the case. In fact, a wide variety of such functions have been and are being implemented in hardware form.

Two all-hardware computer systems—SYMBOL and the HP-35 calculator—are discussed in separate sections of this article, as key examples of the extent to which hardware has been finding new roles in computing. But the role of hardware is also increasing in many more-conventional computer systems.

#### Hardware is used in many roles

Simple arithmetic functions—such as binary addition—were traditionally hardware implemented. Today, efficient computations for such complex functions as floating point arithmetic are being widely implemented in hardware form, and this is economically feasible because of the low cost of LSI hardware. For example, a floating-point hardware unit manufactured for use with a popular minicomputer—the Nova 800—reduces the execution time of a floatingpoint divide from about 900  $\mu$ s to about 40  $\mu$ s.

And hardware substitutes, for functions traditionally performed by software, are finding applications far beyond arithmetic computations. Fast Fourier transform analysis, for instance, can be done using software and a general-purpose computer, but it is much more efficiently performed by hardware specially designed for FFT calculation.

Memory operations. Memory management seems to be one of the most important newer hardware application areas. The SYMBOL computer system, discussed in the box labeled "Probing the limits of hardware." was a pioneering effort that helped to demonstrate the feasibility of hardware memory management.

Allocating, reclaiming, and managing complex memory resources in systems using combinations of core, semiconductor, and disk memories is a very complex task. Many existing software-operated memory systems are the end-product of a long design and (*Text continued on page 38*)

| Memory allocation                                | Symbolic addressing                     |

|--------------------------------------------------|-----------------------------------------|

| Memory reclamation                               | Variable field lengths                  |

| Virtual memory management                        | Variable data structures                |

| Paging                                           | Alphanumeric field manipulation         |

| Segmentation; absent segment interrupt           | Context switching                       |

| Memory and data protection                       | Emulation                               |

| Stack operations                                 | Queues                                  |

| Address generation                               | Links                                   |

| Indexing                                         | Compilation                             |

| Indirect addressing                              | Task dispatching                        |

| Storage protection                               | Next software instruction fetch         |

| Multiple precision arithmetic                    | Interrupts; interrupt checking          |

| Decimal multiply and divide                      | Trap catchers                           |

| Floating point arithmetic                        | Peripheral data transfer                |

| Sorting                                          | Time-sharing supervision                |

| Data manipulation algorithms                     | Text editing                            |

|                                                  | Control command instructions            |

| Program linking and binding                      | Format checking                         |

| Program relocation                               | Peripheral data transfer                |

| Data relocation                                  |                                         |

| Data structure                                   | Parity checks                           |

| Format checking                                  | Error-control coding                    |

| Format checking<br>Character string manipulation | Error-control coding<br>Automatic retry |

| Data-type conversion                             | Automatic diagnosis                     |

Howard Falk Associate Editor

#### Probing the limits of hardware

All-hardware memory management was a key aim of the SYMBOL project from its inception in the early 1960s. Rex Rice and his colleagues at the Fairchild R&D Laboratory were convinced then, that the potential computing power of hardware had not yet been fully tapped, so they decided to build an experimental working system to explore the limits of computer hardware functional capabilities.

After six years of development, construction, testing, and operation at Fairchild and, later, at Iowa State University, SYMBOL had demonstrated the feasibility of constructing a high-level language, virtualmemory time-sharing system that can operate entirely without benefit of system software. To see just how this has been accomplished, let's take a look at the operation of the SYMBOL system.

#### How SYMBOL works

Users write programs for SYMBOL in a language called SPL—a high-level language somewhat similar to Fortran, Algol, or PL-1. Compared to these more conventional languages, SPL is more oriented towards users needs and less oriented towards controlling machine computation processes. For example, SPL has none of the word-length limitations imposed on the user by the other languages, and SPL makes no distinctions between data types such as real, integer, or Boolean.

For most computers, the machine and the language are designed quite separately and then brought together late in the design process. In the SYMBOL system, the starting point for the design was, in fact, the SPL language.

Unlike general-purpose computers that can execute many languages, the SYMBOL system can execute only SPL—but this single language is handled very efficiently. One of the main objectives of the SYMBOL system designers was to find out just how efficiently a powerful language could be executed.

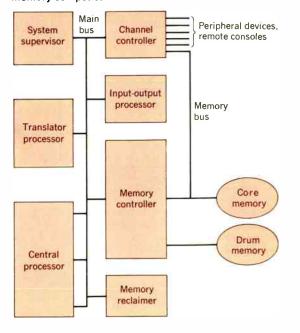

Several distinct hardwired processors work together in the SYMBOL mainframe.

The Central Processor unit was designed specifically to execute SPL programs. It carries out arithmetic operations and manipulates character strings as well as performing such functions as array-referencing and procedure-activation.

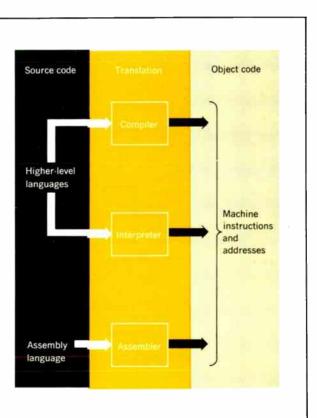

For greater efficiency, the Central Processor executes preprocessed versions of programs. These are produced by the *Translator Processor*, which accepts the user's programs in character-string form (source code) and produces object code, ready for the Central Processor. Symbolic references in source code are replaced by memory addresses in object code. Also, in object code, expressions are rearranged into "Polish postfix" order that lends itself to efficient execution using a last-in first-out stack.

A similar process takes place in almost all conventional computers. However, in SYMBOL, the translation is performed separately—freeing the Central Processor for program execution. Furthermore, in SYMBOL, the object code is very similar to the source code, and the translation process is relatively simple to implement in hardware form.

Together, the *Input-Output Processor* and the *Channel Controller* handle the loading and editing of programs and the input and output of character strings as directed by user programs.

The System Supervisor coordinates the other SYMBOL processors and multiplexes tasks among them from up to 31 users. The Supervisor manages the transition of each task from one state to the next. At the heart of the system is the Memory Controller. In addition to the conventional functions of referencing and replacement of words in memory, this unit also provides the automatic allocation, link tracing, and memory reclamation functions that are usually performed by software in other systems.

Virtual memory for the system is derived from a small core memory and a larger drum memory, managed by a drum controller and a page table that maps virtual memory addresses into core memory addresses. A section of the System Supervisor directs the drum controller to bring pages in and out as needed. All these functions are performed by hardware.

#### Machines for specialized problems

One major objection to the SYMBOL approach is that use of hardware implies a lack of flexibility since it is harder to modify than software. However, if flexibility is needed to correct serious design errors—such as those in basic data structure organization—system programs can be as difficult to change as system hardware.

Computation tasks that were not foreseen when a system was designed often cannot be handled rapidly and inexpensively. But the solution to this problem need not be new software for a general-purpose computer. It may be more economical to use an entirely new machine designed for the task at hand.

When hardware was very expensive, it was necessary to make each computer so it could handle a great variety of user problems. Today, hardware is very cheap and there are many different machines to choose from. Through computer communications networks a user in Illinois can even do his computing on a machine in San Diego.

With many specialized machines available there is no need for overlapping general-purpose capability.

Hamilton Richards, Jr. Iowa State University

#### SYMBOL system. Processors are shown as squares, memory components as circles.

#### Tradeoffs in electronic calculator design

One of the basic objectives, in the design of the Hewlett-Packard 35 and 45 electronic calculators, was to develop an architecture suitable for a family of machines, each of which would be directed to a specific group of users. Thus, the initial HP-35/45 designs were "slide rule" calculators for engineers and scientists, while the HP-80---released in 1973—was a business-financial calculator. Operating speed, fabrication cost, and design-production turnaround time were driving factors that influenced many of the design choices.

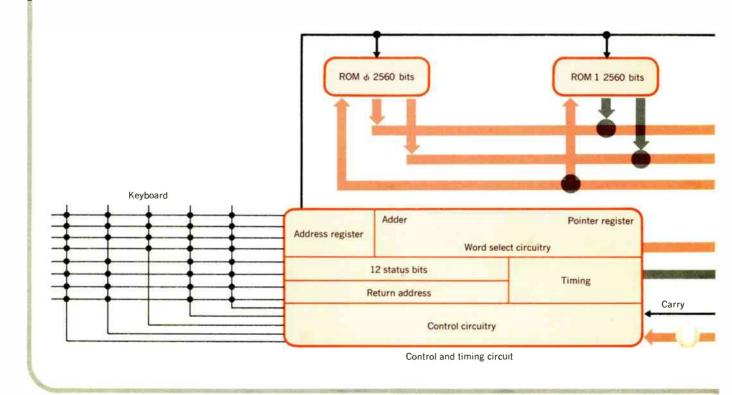

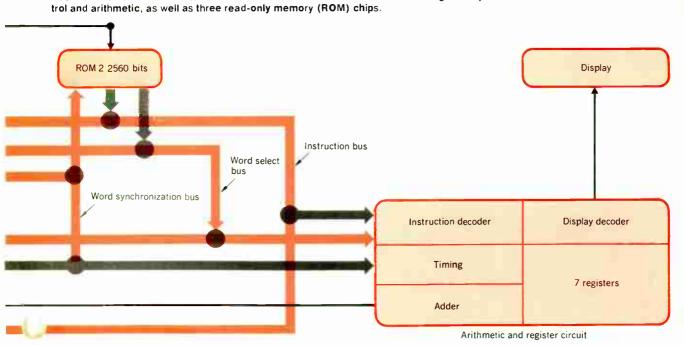

The architecture finally chosen—illustrated by the blockdiagram of the HP-35—was implemented entirely in hardware, using two custom-wired gate-logic chips and three read-only memory (ROM) chips.

#### Software was too slow

It makes no difference how I start thinking about the question, "Why did you implement the HP-35/45 all in hardware instead of using software?" The answer always comes out the same: speed is the primary reason. We used hardware because software is too slow.

P-channel MOS integrated circuits, like those used in the HP-35 and 45, can be operated at clock frequencies of 50–200 kHz. Even at 200 kHz, the add time of these machines is 60 ms and the multiply time is 400 ms. These times are adequate for manual arithmetic, but are completely unacceptable for software routines to evaluate elementary functions like sin x or cos x, or for square roots.

For example, consider the time needed to evaluate sin x using a continued-product version of a MacLaurin series. To obtain accuracy of 10 significant digits from  $-\pi/2$  to  $\pi/2$ , requires 9 multiplications, 8 divisions, and 8 subtractions. More than seven seconds would be needed for this computation, without even considering the time needed to convert from degrees to radians, resolve large arguments, and correctly assign the sign.

With a somewhat more sophisticated program, the time to compute sin x might be reduced to five seconds but, using ROM-microprogrammed routines, the computation takes less than one second.

The technique we actually used, called a cordic algo-

rithm, relies on the ability of the microprogram to manipulate the internal registers of the calculator. While the relationship between registers is maintained by a simple stored algorithm, one of these registers is driven towards the input argument x. Because of the fixed algorithmic relationship another register is automatically forced towards sin x. Almost all cordic routines can be executed in 2 or 3 divide times.

For the electronic calculator designer, microprogramming allows great flexibility compared to keyboard-function programming. The designer is able to select any of the individual bits within a number with the same ease he can perform an addition on an entire register. Similarly, he can extract the integer or fractional parts of a number, or multiply a number by 10 simply by changing its exponent.

#### **ROM-gate tradeoffs**

Large-scale integrated circuit (LSI) chips with customwired gates operate at speeds about twice as fast as those of LSI-ROM circuits. As we have seen, speed can be a key design consideration—especially where time-consuming algorithms are used. Even the difference between a half second and a full second is quite noticeable to users.

If speed were the only consideration, custom-wired gates would have been used. However, the economics of integrated circuits dictate the use of as many copies as possible of each individual circuit chip. Using all customwired gate chips, each of the Hewlett-Packard calculators would have been a little faster and the chips would have been somewhat smaller, but the overall investment would have been significantly higher for those lower-volume unique chips in each calculator.

What we did was to separate out the logic functions we knew would be common to all the calculators. These were implemented in the form of two custom-wired LSI chips: the control and timing circuit, and the arithmetic and register circuit shown in the HP-35 block diagram.

The remaining logic, including all functions that were to be unique to each individual calculator design, was implemented in LSI-ROM chips. On these chips, the logic bitpattern is determined by the final processing mask. The

unfinished ROM chips, ready for that final processing step, are standard high-volume units

By using this mix of custom-wired and ROM chips, we achieved an architecture that gave reasonable processing speed along with flexibility and-equally as important-a shorter design and production turnaround time.

#### Turnaround time: a competitive necessity

If historians ask, 100 years from now, why a certain calculator design using random wired chips was unsuccessful, the answer will probably be that it just wasn't ready for production in time. There is a fantastic amount of market pressure in calculator design. Furthermore, the privilege of being first brings with it the right to set the ground rules.

If you make a design error in a chip custom-wired with gates, the turnaround time needed to change the chip is substantial. This time is at least five times greater for a custom-wired gate chip than it is to change the bit-pattern on a ROM chip, and even ROM turnaround time can sometimes be a problem. Depending on the production situation and the backlog of work semiconductor vendors have on hand. ROM turnaround time may be two to three weeks, or it may stretch to a couple of months.

In general, if large quantities of a particular logic chip are wanted-given sufficient design and development time -custom-wired gate chips can usually be designed for lower cost than the equivalent ROM versions. But the extra time needed to design and debug a gate-chip can be disastrous in a competitive market like the one for electronic calculators

Add to this the fact that prices of standard ROM chips are continuing to drop-much more rapidly than the prices of custom-wired logic gates-and the pressures for using ROM implementations are overwhelming.

#### A healthy discipline for the designer

System designers tend to worry a lot when a computational routine is about to be locked up in hardware form.

One bug in the system can mean recall of the product because there is no such thing as a software fix. In the case of products like the HP-35 or -45 electronic calculators, there is the nightmare vision of thousands of units being shipped back to the factory.

With such possibilities before him, the designer becomes extremely scrupulous about verifying his algorithms and the circuit implementation of each function. The end result is higher quality routines and circuitry. But, the design process is often a laborious one.

The initial euphoria a hardware designer feels when he is first given the freedom to use microinstructions can rapidly fade as he realizes he can now make mistakes in innumerable new ways. With the flexibility of microprogramming comes an ability to assemble a whole wheelbarrow full of new parts in seemingly endless combinations, but many of these can create subtle errors.

There is one microprogramming question I have used to check out new hardware designers. My question to them sounds simple: "Assume that numbers are expressed in scientific notation. Can you describe an efficient algorithm for adding two numbers?

Those on the right track realize quickly that if the exponents differ by more than n digits—where n is the length of the numbers used in the computation-then it is a waste of time to perform the addition, because the sum will be the number with the more positive exponent. Most designers progress this far, but few inexperienced microprogrammers escape the trap that occurs when the number with the more positive exponent equals zero. I have seen more than one machine that gives the sum of  $10^{-30}$  plus zero, as zero. An experienced designer will handle the problem by including a check to see if the most significant digit of either number is zero. If it is, then the sum is the other number

> Tom Osborne Hewlett-Packard Palo Alto, Calif.

Basic architecture of Hewlett-Packard calculators includes two custom-wired gate chips for con-

redesign process. Because of the complexity of the programming tasks and the constant need to maintain compatibility with previous systems, such software tends to become a relatively inefficient patchwork of old and new pieces.

Hardware memory management allows the system designer to incorporate the best features of existing software systems with a technique that uses no memory space for stored supervisory programs, employs the most efficient available methods, and operates at hardware speeds.

On a smaller scale, hardware techniques are increasingly used to format data for disk memories and control disk operations. In stack and queue operations—where part of the computer memory provides special controls for efficient processing—hardware is likewise replacing software.

Any computer operation performed frequently and repetitively is a possible candidate for hardware implementation. For example, error control functions, like cyclic redundancy character-checking for magnetic tapes, are now performed by bipolar LSl chips. At Iowa State University, an algorithm for recognizing hand-printed characters—programmed in the PL-1 language on an IBM 360/65—took 7 seconds to run. A hard-wired processor ran the same algorithm in 7 ms—a gain of 1000 to 1 in processing speed.

In computer peripheral devices, hardware functions are helping much more than in the past to lighten the load on central processor software. Communications controllers use modular multiplexer hardware to scan groups of lines in parallel, and in some systems, input-output bus signals are directly interpreted by hardware to activate such peripherals as phototypesetting machines.

Taking a more general approach, computer programs can be analyzed as they run, to determine which groups of instructions are used most often and consume the most program time. These groups can then be implemented by special-purpose hardware, to be called into operation whenever the main program needs them. For example, if the programming language used were Fortran, the commonly used argumenttransfer routines might best be put in hardware form because these routines are so time consuming. Similarly, subscript calculations might be put in hardware, particularly if there was a good deal of array manipulation to be done. At Burroughs Corp., when fine-tuning techniques were implemented, programs that typically ran for 24 minutes were reduced to about 6-minute run times.

#### **Reasons for using hardware**

Sheer computational speed is often the basic reason for substituting hardware for software. For complex computations, involving a large number of operations, the speed improvement of hardware implementations can be considerable. This is true of specialized operations such as sorting and fast Fourier transforms; it is also true for general operations like floating-point arithmetic.

Enhanced system reliability is another frequent goal of hardware use. Hardware is less subject to inadvertent modification, and hardware monitoring of system and software operation offers practical debugging assistance.

According to Hamilton Richards of lowa State University, experience with the all-hardware SYMBOL system suggests that there are significant payoffs in starting computer system designs with thorough exploration of all possibilities for hardware implementations. A hardware-first orientation focuses attention, at an early stage, on crucial system design questions that otherwise tend to be postponed—until late in the design process—with painful consequences. In SYM-BOL, problems of memory allocation and garbage-collection, for instance, received early attention and this led to very satisfactory solutions.

#### The choice: custom-wiring or ROMs

As the integrated circuit art has matured, and larger arrays of circuits have become available in economical chip form, two basic hardware methods for implementing traditional software functions have evolved: custom-wired logic gates and read-only memories (ROMs).

Many software functions can be implemented by circuit gates that perform elementary Boolean logic, and these gates can be wired together with connection patterns determined by the particular function that is to be performed. When the gates are produced in integrated circuit form, the result is a custom-wired chip capable of performing only those specific functions for which it was designed.

Integrated circuit chips can also be produced as standard arrays of read-only memory (ROM) elements. Desired connections between these elements are made in the final processing step of the chips. The result is a stored pattern of zeros and ones which can function in the same way as a stored program in a traditional computer memory. The sequence of small logical events that are set into motion by this stored pattern is called a microprogram.

Custom-wired gates can perform computation functions faster than ROMs, and both of these hardware techniques are considerably faster than software. On the other hand, considerable design-time is necessary to lay out the connections for a complex custom-wired function. ROM design is a bit easier, but still requires greater manpower investment than an equivalent software routine would. This is in part due to microprogram coding difficulty. To effect a simple operation, such as adding two numbers, for instance, every step, including such details as operand fetch and data transfer, must be specified in the microprogram. Generally three to ten microinstructions and, in some cases, up to 50 microinstructions must be executed to perform an operation that would otherwise be specified by a single software instruction.

Since a capital investment of thousands of dollars is needed to begin fabrication of a single custom-wired chip, these chips can usually be considered only for applications where they will get large-volume use, and where design turnaround times of several months can be tolerated. ROM chips come close to being standard semiconductor-house production items because only one custom-designed interconnection layer is needed. They can economically be used in small quantities, and can often be obtained with design turnaround times of a few weeks.

#### Microprogramming for speed with flexibility

An interesting example of the great flexibility of microprogramming is provided by the Burroughs B1700 computer. This protean machine was designed to act as if it were almost any computer the user wants, and to run a wide variety of programs and languages efficiently.

The general concept of a machine like the B1700 is a simple one. It contains a microprogrammable memory that controls its effective internal architecture so it can play the role of another (target) computer—one for which the user, presumably, has software already on hand.

In practice, hardware details can cause consider-

able performance problems, particularly if the microprogrammed machine and the target computer are quite dissimilar at the hardware level. Typical problems that have arisen in the past are those involving system synchronization, time delays, word length, and techniques for handling data overflow or discard. Many of these problems have been solved in the Burroughs design.

At present, microprogramming is an elite activity, performed effectively only by a small number of expert practitioners. The work is detailed, precise, time-consuming, and considerably more expensive than present-day software programming. But, computer manufacturers have found they can get dramatic improvements in system performance by converting software into microprogrammed form.

For example, at Hewlett-Packard part of the Fortran-8 package for HP-2100 minicomputers was converted to firmware, including such items as extended precision, call sequences, address pointers, and address compilation. With these items performed by firmware, benchmark measurements have indicated throughput increases of from 5 to 20 times. Similar improvements in system performance have been obtained by many computer manufacturers using firmware to implement their computer designs.

There seems to be general agreement in the industry that microprogramming will continue to find increasing use in computer system design. More controversial is the worth of microprogramming performed by computer users. One manufacturer feels that usermicroprogramming is ineffective and capable of producing little, if any, improvement in performance. Companies like IBM and Digital Equipment Corp. tend to discourage those customers who want to do their own microprogramming.

Nevertheless, users continue to have strong reasons for using microprogramming. It is true that the computer manufacturer is likely to know the best ways to microprogram his system to make it most generally useful to a very broad spectrum of possible users. But that does not necessarily mean that the needs of every user will be best met by that system.

For example, control of a petroleum cracking operation may require checking a complex equation many times each second—a function that would be better performed by microprogramming than by software. It is unlikely that standard firmware supplied by a computer manufacturer could meet this user's needs as effectively as they could be met by custom-designed microprogramming.

With microprogramming, the user can also fine tune his programs. It has been said that many, perhaps most, user programs spend a large amount of their time running and rerunning a very small amount of their code. By microprogramming the often-used sections of such programs, significant improvements in performance have been obtained. But such results depend on intimate knowledge of the particular program and its application, and they cannot be realized unless the user gets customized microprogramming.

Information for this article was received from many sources. Special thanks are due to Michael Sporer (Prime Computer, Inc.) and Ming T. Miu (Honeywell Information Systems).

### More power by networking

### Whether computers communicate as equals or in a superior-subordinate mode, the outcome is usually positive

Computer networks have evolved for reasons of economics and efficiency to permit information resident in one computer to be shared with others, to enable large numbers of users to have remote access to a computing center, and to control the flow of information from one point to another. Not surprisingly, computer networks have evolved in much the same way as other types of networks in our society such as those in communications, power, and transportation. The evolutionary pattern has been to begin with pairs, which are expanded to chains, which in turn lead to series-parallel arrangements such as trees and loops. The networks are interconnected in a variety of ways-they may be based on superior-subordinate relationships, such as commonly found in task-oriented organizations (e.g., industrial or government networks), or else they may be predicated on a more democratic relationship because of more general goals (e.g., networks for research and education).

In all networks, communication is initiated by one computer. However, the ensuing transactions with respect to the initiator can be as a superior demanding a task be done by a subordinate or simply as a request for help.

#### C. Gordon Bell Digital Equipment Corp.

#### Overview of Network Structures

|                | Direct connection                                                                                            | Independent store-<br>and-forward network                                                             |

|----------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Cost           | Cost small for simple net-<br>works                                                                          | Additional machines needed                                                                            |

| Limitations    | Not applicable to large<br>nets or long distances.<br>Applicable to limited traf-<br>fic matrix (e.g., STAR) |                                                                                                       |

| Ease of design | Simple                                                                                                       | Functionally independent<br>of host and its operating<br>system, but the net is<br>costly and complex |

| Reliability    | Based on redundancy                                                                                          | Can be made arbitrarily<br>large and therefore reli-<br>able                                          |

| Performance    | Fixed performance which<br>can be modified using<br>dial-up to assist in over-<br>loads                      | A network can increase<br>performance with more<br>links                                              |

| Applicability  | For small minis                                                                                              | Large interconnection<br>nets where communica-<br>tion costs are small frac-<br>tion of overall cost  |

Some networks consist of a number of small computers used as an alternative to a single large computer. This is done to ensure that the computer structure is operational at all times. It also can simplify system development if functions are partitioned carefully. Such a network permits greater economy by selecting machines that are the most cost-effective for each part of the problem being solved, and then distributing the processes according to costs and capabilities. Such a network may be under control of either a large or small computer.

A key element in all networks is intercomputer and computer-to-terminal communications. A well-established trend is the use of minicomputers connected to larger machines to handle the communications line control functions, commonly called front-end processors. (The minis replace hardwired, inflexible communications control units.) In addition, the minicomputer may perform a variety of simple data processing tasks on a more cost-effective basis than a large machine. The tasks include editing, calculations, and interpretation of languages such as BASIC. Although such a simple pairwise intercommunication could hardly be called a network, there is a trend to use interconnected computers whose functions are specialized. Another similar trend is to use remote job entry computers as intelligent terminals, connected in the form of a one-level tree (or star).

Some of the tasks performed by minicomputers in controlling communications include transforming and controlling the communications lines and modems, controlling a wide variety of terminals (e.g., performing character code conversion, echoing, error checking, and speed selection). and multiplexing characters from multiple incoming lines into a single outgoing line to a host computer.

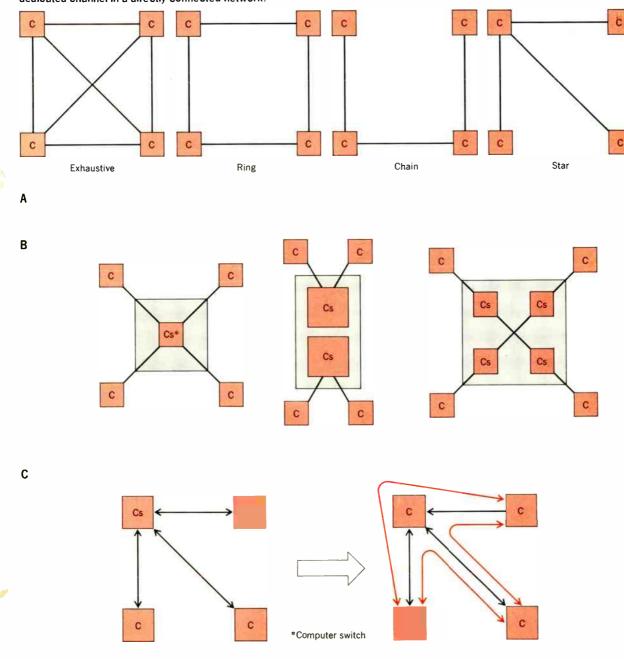

#### **Network configurations**

There are three basic types of network structures (Fig. 1): directly connected networks, store-and-forward networks, and hybrid networks. The direct-connected structure provides for a direct communications link between the transmitter and receiver. Most of today's networks operate in this manner because it offers the simplicity of a fixed communications pattern. The structure may be a one-level hierarchy (called a one-level tree or star), most often in the form of a central site connected to a number of satellites. Strictly speaking, a tree is not a network, since there are no closed loops for alternative routes among the links. The characteristics of directly connected networks are listed in Table I.

Store-and-forward networks contain separate switching computers, which provide buffering to assure that the networks operate smoothly regardless of the speeds or data formats of the machines involved. This type of network also permits any machine to communicate with any other in the network. The ARPA network (covered later in this article) is a good example of this type of structure and, in the author's opinion, large-scale networks will inevitably follow this approach.

A hybrid configuration is a direct-connected network, but with the intermediate computer nodes providing store-and-forward capabilities. This approach has seen little use.

[1] Network structures. Direct-connected networks (A) may be configured in a number of different ways, but most often they take the form of a star (a central computer connected to satellites). Store-and-forward networks (B) contain independent switching computers to optimize the data flow and work assignments. In a hybrid configuration, (C), the store-and-forward function is performed by a single, dedicated channel in a directly connected network.

#### Considerations in network design

An important element to successful network design is a thorough knowledge of computer components, together with a proper definition of the information processing problem over the life of the network. The most important component parameters are link capacities, error rates, costs, and reliability. Processing capacity also is an important factor and it must be measured, not on the basic hardware, but in terms of the operating system and languages specifying the information processing problem.

The information processing problem should be defined both in terms of data processing needs and the location of hardware. The processing needs should be based on the number of statements, file sizes, and the delay time that can be tolerated for the processing services.

The physical location requirements are based on the economics of whether the processing equipment

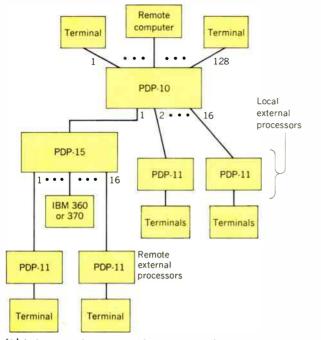

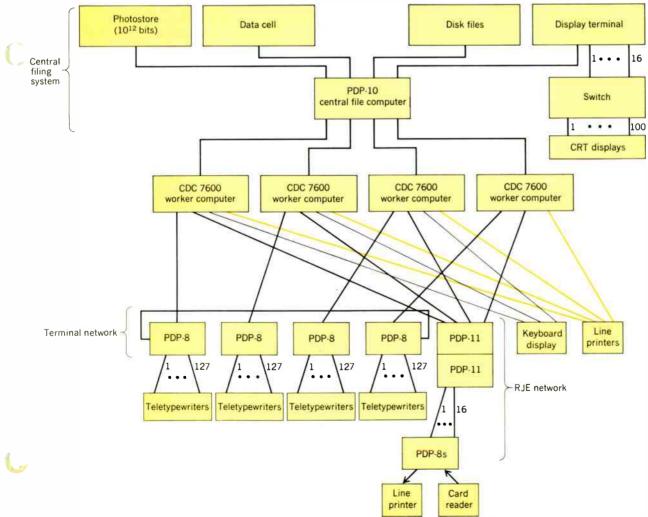

[2] Laboratory interconnection programming system is designed for control of diverse computers. At the heart of the system is a PDP-10, which functions as the central computer. Its purpose is to file, to provide central support of satellite computers, and to switch information.

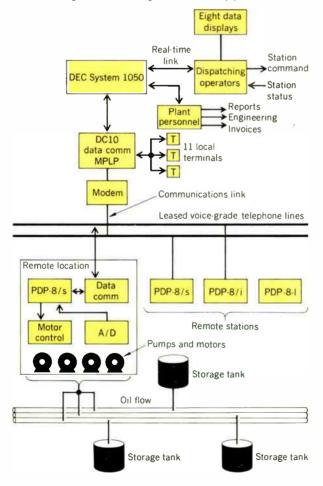

[3] Canadian International pipeline network communicates with minicomputers over voice-grade telephone lines. The minicomputers are located at remote, unattended pumping and oil storage stations along the 1900-mile pipeline.

should be local or remote. For example, suppose it is desired to display the output of a flow-rate meter and there are switches with which an operator can enter the flow-rate limits. Processing of this problem can be handled entirely locally or at a remote computer—or possibly even distributed among several machines (if the information is needed elsewhere).

In designing a network, the criteria that usually apply to components—i.e. cost, performance, and reliability—also apply to networks. Several additional guidelines are:

• Minimizing the number of computers and computer types tends to decrease programming costs.

• Designing a network, where possible, with identical components allows a variety of functions for backup.

• Duplicating functionally specialized computers offers reliability.

• Unless the node is replicated or made into a duplexed tree, tree-structured (star) networks are not satisfactory for most networks that require high reliability.

• Communication links and the protocols that establish error-free transmission are probably the least understood by computer engineers.

• Never build a structure before competing, alternative structures have been considered.

#### Typical networks in use today

Several networks in use today illustrate the various network approaches. Those covered below are the DEC Laboratory Interconnection Programming System (LIPS), a simple tree structure; the Lawrence Livermore Laboratory system, a directly connected network with some switching (hybrid) capability; and the ARPA network, designed for computer network research.

The DEC LIPS System is a general purpose, PDP-10 computer for controlling a network of diverse computers. Strictly speaking, it is a one-level tree, which permits a number of independent satellite computers to be connected to a large central computer, as shown in Fig. 2. Its overall function is to file, to provide central support of satellite computers, and to switch information among the computers. The network has been implemented at Oak Ridge National Laboratory (IBM 360/91, 360/75, 2780, three Systems Engineering Labs 817/840s, seven PDP-4/7/15s), the Abbott Laboratory, Knolls Atomic Power Laboratory (two Control Data Corp. 6600s, one 7600), and Rolls Royce Engine Testing Laboratory (two English Electric KDF-9s, one IBM 360, eight PDP-8/11s).

The LIPS network has appeared in various laboratories that use a number of large, scientific computers. The functions being performed by the relatively large, general-purpose time-sharing system are:

• Scheduling and loading of the large satellite computers. In several cases (e.g., Oak Ridge and Knolls), the PDP-10 appears to other machines as a remote job entry terminal. In the case of Rolls Royce, where the PDP-10 schedules two KDF-9s, utilization of the latter was increased from 25 percent to 75 percent and the number of supporting operators was reduced from 22 to 10.

• Switching. Since there are several large machines available, a given job can be routed to the machine that can best handle load.

• Editing. Since the files reside in the PDP-10, they can be edited locally, avoiding costly movement of the files and trivial processing of them.

• Interactive processing of small jobs. These tasks are carried out in a manner akin to editing, using either interactive interpreters (e.g., APL) or load-and-go compilers (e.g., BASIC).

• Pooled specialized central facilities. Printing, punching, display, film reading, and specialized plotting are provided by the central facility.

The LIPS approach has also been used in minicomputer networks. It has seen service in laboratories where minicomputer nodes are employed to meet real time and preprocessing demands. These structures are similar to the industrial control systems in which minicomputers control individual, real time processes. The need for such a network is predicated on the poor adaptability of a single, large computer to meet real time response demands; poor reliability of a single site; the high cost of simple, short wordlength calculations required in real time preprocessing; and the physically isolated inputs and outputs associated with a process.

The functions usually performed at a LIPS central

computer site include:

• Management of a central data base. Usually a significant economy results from removing file devices from the local computers and placing them in a single site. Overall, there is less hardware and software for operating systems in the individual machines.

• Centralized editing and language translation (program preparation). Large machines, which contain large primary memories, usually provide the best facilities for minicomputer program preparation.

• Pooling of specialized facilities (e.g., printers, punches, tapes, displays, plotters).

• Significant computations that cannot be handled at the minicomputer nodes. This permits the use of more extensive languages such as COBOL and PL/1, which usually are not supported by minicomputers.

The Canadian Interprovincial Pipeline (IPL) network (Fig. 3) is a one-level tree in which 44 PDP-8 minicomputers are connected to a central PDP-10 computer via several polled, synchronous, communication links. The minicomputers are located at remote, unattended pumping and oil storage stations along the 1900 miles of the pipeline. Each minicomputer controls several large pumps, and monitors

[4] Lawrence Livermore Laboratory's Octopus network gives several hundred subscribers access to four worker computers and a central file computer. The terminal network accommodates 500 teletypewriters, 16 remote job entry consoles, keyboard-displays, and printers.

pressures. flow rates, gravity, viscosity, power, and other station parameters. The central site also contains a minicomputer to back up the central central computer, but with fewer monitoring functions. The central computer monitors and records the behavior of the pipeline and controls the individual sections. One advantage of such centralized control is that the amount of electrical energy supplied to move the oil can be optimized. Thus, the network has both local and global control.

An alternative approach would be to multiplex all inputs and outputs, and then transmit them to a cen-

#### The computer utility

To date, computer networks have been built by special classes of users. However, the next logical step is an information utility for whole "communities," such as businesses, homes, and government departments, which would provide services such as credit card transactions, printed message delivery, news distribution, and library information retrieval. Such a utility network might take advantage of the economy of scale by assigning information processing tasks to machines best able to handle a given processing task or else they could distribute the work load among many machines for optimum efficiency. Computer networks already take advantage of geographic time zones to assign jobs to machines during offhours.

In the nearer future, the existence of specialized data bases will begin to make program and file sharing desirable because of the excessive time and costs involved in shipping data in physical form and in the costs of maintaining and updating redundant files. For example, we might expect to see specialized networks for libraries as a first step in retrieval networks. Indeed, computer networks may eventually provide the only economical solution to the problem of maintaining and disseminating the information in libraries. tral site for control. This would require that communications lines always be operational, whereas the existing structure carries out local control at each site without frequent intervention from the central control computers.

The Lawrence Livermore Laboratory's Octopus network, started in 1964, appears to be the earliest, and most general, of the general-purpose computer networks, because it provides a wide range of functions with different computers. Several hundred simultaneous on-line users are given access to four worker computers.

At the heart of the network (Fig. 4) are four large worker computers (three CDC 7600s and one CDC 6600) and a central file computer (a DEC dual processor PDP-10) with access to a data cell, disk files, and a  $10^{12}$ -bit IBM photostore (controlled by an IBM 1800 computer).

Hardwired 10-Mb/s links connect the large computers to the file computer. The terminal computers and the large file are connected to the switching computer via high data rate links. The terminal network connects over 500 teletypewriters to the four worker computers via four PDP-8s, and the remote job entry (RJE) network connects up to 16 remote job entry consoles. In addition. a set of keyboard displays and line printers are connected to all the large computers in the system.

The main purpose of the network is to permit any user to have access to any of the large computers so that the network will operate even with a number of machines down.

The Advanced Research Projects Agency (ARPA) network was conceived in 1968 and placed in operation at four sites in 1969. As of January, 1973, 34 centers had been connected.

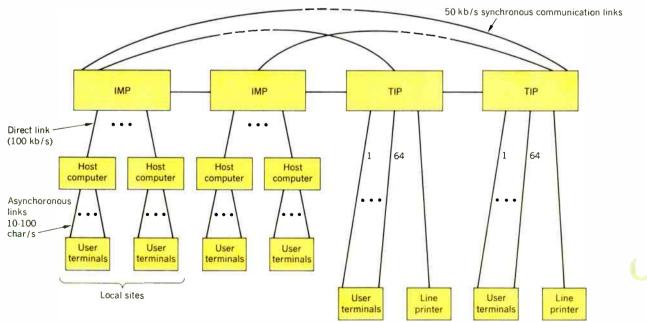

[5] The ARPA network structure consists of large-scale central computers (hosts) and interface computers (IMPs and TIPs). The TIPs were added after the network was initially designed.

#### For more on networks

Bell, C. G., Habermann, A. N., McCredie, J., Rutledge, R., and Wulf, W., "Computer networks," *Computer*. Oct./Sept. 1971, pp. 14–23.

Cady, G. M., and Luther, G., "Trade-off studies in computer networks," *IEEE Compcon.* 1973, pp. 147-150.

Frank, H., and Frisch, I. I., Communication, Transmission, and Transportation Networks. Reading, Mass.: Addison-Wesley, 1971.

Ornstein, S. M., Heart, F. E., Crowther, W. R., Rising, H. K., Russell, S. B., and Michael, A., "The terminal IMP for the ARPA computer network," *Proc. AFIPS SJCC*. 1972, vol. 40, pp. 271–280.

Roberts, L. G., and Wessler, B. D., "Computer network development to achieve resource sharing," *Proc. AFIPS SJCC*, 1970, vol. 36, pp. 543-567.

Roberts, L. G., "Network rationale: a 5-year re-evaluation," *IEEE Compcon*. 1973, pp. 3-5 and pp. 39-44.

Speers, G. S., "Monitoring control by distributed computing," *Datamation*. July 1973, pp. 47-49.

Wecker, S., "A design for a multiple processor operating environment," *IEEE Compcon.* 1973, pp. 143–146.

The purpose of this system is to investigate broadly the use of a computer network; to explore an alternative method of message switching; to provide a wide range of computing facilities to a community of computer and physical scientists, for program and file sharing; and to permit the users to communicate with each other in a variety of ways.

The ARPA network (Fig. 5) is a packet switching, store-and-forward network, whose nodes consist of interface processor computers (IMPs). The computers are linked together by up to four 50-kb/s synchronous communication lines. Messages of up to 8000 bits are transmitted among central (host) computers on a packet basis (up to 1000 bits/packet), with a packet delay of approximately 0.1 second when several IMPs are involved.

A TIP (terminal interface processor) is an IMP without a host computer, but with the capability for up to 64 terminal users to access other hosts. TIPs were added after the initial network was designed, and are used at about one third of the sites.

The hosts are either standard, large-scale computers (e.g., PDP-10s or 360/370s using the same operating systems) or else specialized computers. The latter type includes the ILLIAC-IV at NASA Ames, a large 360, a CDC 7600, a Burroughs B6700, the MIT Multics System, and one or two large 10<sup>12</sup>-bit files. In addition, hosts monitor and report the network activity, provide information about documentation and programs of interest, and hold user "mailboxes" through which individuals communicate with each other.

The network has been operated in the following ways:

• Remote use of computers either from a termination on a host or via a TIP, or else on a batch or interactive basis. Since computers can be used over long distances, the network functions as a broker for computing facilities. In this way, a particular site can choose not to own and manage a facility, but instead to buy file storage and computation at a variety of other sites. Since ARPA controls the operation of the individual sites, when a site becomes overloaded, the agency can expand the configuration or move some of the users to another site.

• File movement and printing. A user may retain text or programs at one or more sites and then transfer files to particular sites for program execution. Some of the sites have elaborate printing devices for both arbitrary character sets and graphics.

• Personal messages. Users can communicate with each other in various ways. A message for another user may be placed in a "mailbox" located at a host. For example, a message was placed in a mailbox of another user at 11 p.m., requesting latest information on the ARPA network use. By 10 a.m. the next morning, the information was available. This form of communication is faster than a letter or telegram; it is low-cost; and it doesn't require the simultaneous availability of the communicants. Still another advantage of the mailbox is that it permits batch processing of messages by each user.

On the other hand, users can be directly linked via terminals, for both direct two-way and conference real time communication. In the conference mode, a message is broadcast to all attendees.

Finally, terminals may be cross-connected to a single program. In this mode, multiple terminals can have their inputs and outputs connected in parallel. Thus, one user can demonstrate a program by taking several users through a "scenario."

• Machine-to-machine subroutines. In the simplest case, a user has access to a program in a given machine. If the user program requires a program on *an*-other machine, the first program calls it in a manner akin to subroutines stored in a single computer.

• Access to a large common data base. For example, a 10<sup>11</sup>-bit meteorological data base is being prepared to be shared among six research sites.

The ARPA Network is important because it provides multiple links per node, so that nodes and links can fail, but the network still functions. Although it could have been built earlier, it requires high-reliability, high-performance minicomputers; time-shared system modes; and 50-kHz synchronous communication links that became available in the past few years. The network design was carried out in an exemplary fashion with extensive analysis, internal documentation, and technical papers. As it became operational, measurement experiments were conducted to verify the analytical tools it developed. It is clearly the archetype for future large-scale networks.

C. Gordon Bell (F) is vice president of engineering for Digital Equipment Corp., Maynard, Mass., on leave as professor of electrical engineering and computer science at Carnegie-Mellon University. Pittsburgh, Pa. He received the B.S. and M.S. degrees in electrical engineering from the Massachusetts Institute of Technology in 1956 and 1957, respectively. Mr. Bell is the holder of several patents in digital systems, the designer of several computers, and he has published books and papers on computer architecture.

### Data by the packet

#### Because computing costs are now so low, an unusual new concept of data communications is feasible

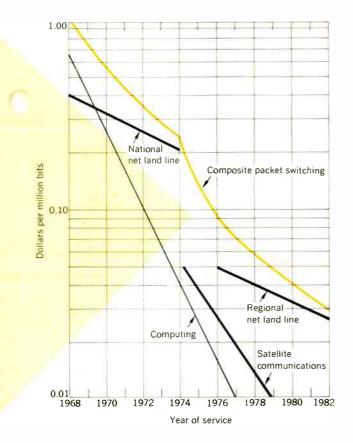

The most dominant force over the past 20 years in both computer and communications architecture has been the continuous and rapid decrease in the cost of computer hardware. Not only has this electronics revolution affected the capability and design of computer systems, but it has also made possible a radically new concept of data communications. Called *packet switching*, this concept is strongly dependent on the cost of computing since it uses computers to correct transmission errors, to provide high reliability through alternate routing, and to allocate communication bandwidth dynamically on a demand basis rather than as a preassigned bandwidth.

The impact of widespread packet-switched communications networks on the computer field should be momentous. With data communications priced on a distance-independent basis, it should become economically feasible for terminals and computers throughout the country to access efficiently-on demand-a wide variety of computer services. The economics of resource sharing will undoubtedly eliminate the need for many medium-scale data processing centers and permit a considerably higher degree of specialization for the larger service centers. Moreover, packet switching will make possible far more economic realization of a comprehensive electronic fundstransfer system, on-line credit authorization, integrated corporate data networks, as well as nationwide access to all forms of data banks and retrieval services.

All these developments hinge on the availability of low-cost computer communications. Although packet switching economizes on transmission costs by maintaining high line utilization, until recently the cost of computer hardware had continued to be too high to permit practical packet-switching networks. The price of computing has been decreasing far more rapidly than the price of communications, however, and one could have anticipated a crossover point where the cost of using computers to allocate bandwidth became cheaper than the cost of the communications themselves. According to my estimate, this crossover occurred during 1969. As a result, packet switching has now become quite an economic and viable technology, permitting the establishment of large, cost-effective networks nationwide. This development in data communications will in turn have substantial effect on the course of computer technology as preliminarily indicated by results from the United States ARPA (Advanced Research Projects Agency) network research activity.

One of the main reasons for the great interest in

Lawrence G. Roberts Telenet Communications Corporation

computer networks today is the considerable economies that can be achieved through resource sharing. With a computer network that is reliable and responsive enough to permit the full resources of a remote computer to be employed locally, it becomes possible for organizations to consider the elimination or reduction of local computing facilities and the utilization of remote service centers instead. This not only can lead to considerable cost savings, as we shall see, but also has many additional advantages, including increased reliability of a multicomputer service center, improved service from a variety of competing suppliers, and increased flexibility for expansion. The main incentive for an organization changing over, however, is the cost saving. To get a feel for the magnitude of this effect, it is useful to examine the initial experience in an environment-the ARPA Computer Network (AR-PANET)-where remote use of computing has been fostered by providing adequate communications facilities.1-3

#### Cost-effective remote-access computing

Although initiated in 1969, the ARPANET was not sufficiently developed to permit useful resource sharing activity until mid-1971. As network reliability and effectiveness proved out, ARPA and its contractors found many cases where newly required computer capacity could effectively be obtained through the network rather than by adding local computing resources. By March 1973, several contractors were making substantial use of the network for a majority or all of their computing resources. Several of the computer centers on the network had grown to become substantial suppliers of computer service, providing not only time-sharing service but also remote batch service. At that time, an accounting was made of the total computer usage obtained through the network, and an estimate was made for each user of the cost of purchasing comparable time on outside computers or leasing the necessary in-house computer facilities to do the same job apparently being done through the network. Table I tabulates this information by user organization, identifying both the cost of computing with and without the network. A total of \$2 million a year was being spent on computing resources accessed through the network-resources that would have cost \$6 million per year if the network had not existed! This savings of \$4 million per year more than offset the \$3.5 million annual cost of the network.\*

At this stage in its development, the network was only using 20 percent of its capacity; thus, at the

<sup>\*</sup> This cost includes amortization of the system's IMP (interface message processor) minicomputer units.

same communication cost, the ANTAINET could permit five times as much remote computing to be performed. At full traffic load, the network cost would be 35 percent of the actual computing cost, or 11 percent of the original computing cost. Clearly, for a moderate investment in communications, a computing cost reduction factor of three can be achieved through resource sharing.

Examining the ARPA data, it is useful to identify a few of the different categories of network usage and explore the sources of the cost savings. The largest individual user organization was the University of Illinois, which before the network came into full operation leased its own Burroughs 6700 computer to develop programs for the ILLIAC IV computer. After the University of California at San Diego put its large B6700 complex on the network, Illinois was able to terminate its computer lease and obtain the computing support far more economically from the larger installation through the network. Moreover, Illinois required access to the ILLIAC IV computer that it obtained from the NASA Ames Research Center through the network, remote batch service on the IBM 360/91 at U.C.L.A., and time-sharing services from U.S.C. and M.I.T. To obtain this collection of services locally, Illinois would have had to continue leasing the Burroughs computer, purchase time on a local IBM 360, and either purchase a time-sharing machine or obtain service from a commercial vendor. Therefore, not only would it cost the University three times as much to obtain equivalent computing power locally, but it would not have had a convenient way of accessing these machines and transferring data and programs between them.

This case is an excellent example of a user requiring many different types of service, each being most efficiently provided by a large specialized service center. For example, program development and debugging is extremely cost-effective on a time-sharing computer, but the execution of large numerical applications programs can often be done a factor of ten less expensively on a large batch processing machine.

Another type of saving is exemplified by Massachusetts Computer Associates, a small computer software firm. This group would use the equivalent of one third of the capacity of a PDP-10 time-sharing system, if they operated locally on a dedicated basis. The required facilities, however, were provided through the network from the University of Southern California, taking advantage of the fact that peak usage hours on the east and west coasts of the U.S. do not coincide due to the time zone difference. A large number of such users of various sizes can be accommodated by a single service center with considerably greater economy of operation than with a number of independent centers. The consolidation of maintenance, software, and operational personnel in one location considerably reduces costs, as most of the time-sharing companies have found. and nationwide operation increases the machine utilization considerably due to the time zone spread.

Although there are many other combinations of resource sharing represented within the ARPA network community, these two examples illustrate the main sources of cost savings resulting from hardware sharing. Additionally, large but less easily quantifiable

| User Organization                                                          | Activity                                  | Remote<br>Usage, in<br>thousands | Projected<br>Cost for<br>Local Re-<br>placement,<br>in thousands |

|----------------------------------------------------------------------------|-------------------------------------------|----------------------------------|------------------------------------------------------------------|

| University of Illinois                                                     | Parallel processing research              | \$ 360                           | \$1100                                                           |

| NASA Ames Research Center                                                  | Air foil design and ILLIAC                | 328                              | 570                                                              |