# Getting Acquainted With the IC

by Rufus P. Turner, PhD

Howard W. Sams & Co., Inc. 4300 WEST 62ND ST. INDIANA POLIS, INDIANA 46268 USA ANERICAN TELEPHONE & TELEGRAPH CO. 17 WEST 1641 STREET ERLE CERNSVLVANIA HINL

Copyright © 1978 by Howard W. Sams & Co., Inc., Indianapolis, Indiana 46268

FIRST EDITION FIRST PRINTING—1978

All rights reserved. Reproduction or use, without express permission, of editorial or pictorial content, in any manner, is prohibited. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-672-21520-9 Library of Congress Catalog Card Number: 78-65668

#### Printed in the United States of America.

# Preface

This book is addressed to those who wish to become familiar with the integrated circuit as quickly as possible and who prefer a "handson" approach. Our method is to have the reader test an IC for its various electrical characteristics, thus determining how it works. This approach has enjoyed success in the teaching of tube and transistor fundamentals.

Part 1 offers a brief introduction to the integrated circuit. This is the only theory discussed in the book; we assume that the reader is already familiar with diodes, transistors, rectifiers, and general semiconductor theory.

Part 2 is devoted entirely to practical tests and measurements. The cookbook-type presentation in this section aims to hold the IC novice on the preferred path and to keep him and his equipment out of trouble. The seasoned experimenter who just happens to be new to ICs should at least review our step-by-step procedure before he embarks upon a procedure of his own design.

Part 3 offers a series of simple applications of the IC used throughout Part 2. These will enable the reader to put the IC to work immediately.

**RUFUS P. TURNER**

# Contents

#### PART 1

| INTRODU | JCTION                              | Do | -  |      |   | di. |      | 11 |

|---------|-------------------------------------|----|----|------|---|-----|------|----|

| 1.1     | Nature of the Integrated Circuit .  | 30 | SE |      |   |     | . 11 |    |

|         | The IC as a Unit                    |    |    |      |   |     |      |    |

| 1.3     | IC Symbols                          |    |    | 1.85 |   |     | . 16 |    |

| 1.4     | Differential Amplifier in ICs       |    |    |      |   |     | . 17 |    |

|         | Operational-Amplifier IC            |    |    |      |   |     |      |    |

| 1.6     | Economics of the Integrated Circuit | •  |    | •,   |   |     | . 21 |    |

| 1.7     | Precautions in Handling ICs         |    |    |      |   |     | . 21 |    |

| 1.8     | IC Used in This Book                |    | 51 |      | 4 |     | . 22 |    |

| 1.9     | Nature of Experiments in This Book  | č  | 1  | ,    |   |     | . 23 |    |

|         |                                     |    |    |      |   |     |      |    |

## PART 2

| EXPERIMENTS .  |                                     | 19 | Υ.   | Ag ( | 27   |

|----------------|-------------------------------------|----|------|------|------|

| Experiment 1.  | DC Operating Voltages.              |    |      |      | . 29 |

| Experiment 2.  | Operating Current                   |    |      |      | . 30 |

| Experiment 3.  | Output Offset Voltage               |    |      |      | . 31 |

| Experiment 4.  | Output Polarity                     |    |      |      | . 32 |

| Experiment 5.  | Offset Null Adjustment              |    | à    |      | . 34 |

| Experiment 6.  | Input Offset Voltage                |    |      |      | . 37 |

| Experiment 7.  | Input Offset Current                |    |      |      | . 38 |

| Experiment 8.  | Closed-Loop DC Voltage Gain         |    |      |      | . 39 |

| Experiment 9.  | Open-Loop AC Voltage Gain .         |    |      |      | . 42 |

| Experiment 10. | Closed-Loop AC Voltage Gain         |    |      |      | . 43 |

| Experiment 11. | <b>Open-Loop Frequency Response</b> |    | sa s |      | 44   |

# PART 1

# Introduction

and the second second

### PART 1

# Introduction

Within a relatively short time, the integrated circuit (IC) has brought many improvements to electronics. Not only has it shortened the time needed to assemble a system, but it has also reduced the bulk, weight, and cost of the system. All electronics people must be on intimate terms with the IC.

This introduction offers a brief, elementary description of the IC. For a more comprehensive treatment, see *abc's of Integrated Circuits* by Rufus P. Turner (published by Howard W. Sams & Co., Inc., 1971).

# 1.1 NATURE OF THE INTEGRATED CIRCUIT

A semiconductor device, an integrated circuit is a silicon chip which contains microscopic components (diodes, transistors, resistors, and capacitors; as needed) and the interconnections ("wiring") between them. These are created inside the chip by electrochemical and photochemical processing of various areas of the chip. Integrated circuits run the gamut from simplicity to complexity. Thus, an IC may contain only a pair of diodes, it may be a multistage amplifier having several dozen components and all of their interconnections (and still be no larger than a small discrete transistor), or it may contain the complete heart of a digital timepiece or a microcomputer. Very often, the IC performs a function by itself, requiring only the application of dc voltages and the connection of input and output. In other instances, only a few outboard components (e.g., resistors, capacitors; inductors, potentiometers, etc.) are needed.

There are two general classes of integrated circuits: linear ICs include such analog devices as amplifiers, modulators, detectors, and so on; digital ICs include such switching devices as flip-flops, gates, adders, encoders, decoders, and so on.

Small size is not the only advantage of the IC; another is stability. Since all components in the IC are formed near each other in the chip, they are easily matched through controlled fabrication processes, and during operation they experience nearly the same temperature changes. Still another advantage is the labor saving afforded by the IC. Since all of the internal connections are provided in the simple plug-in integrated circuit, only external connections actually need to be wired.

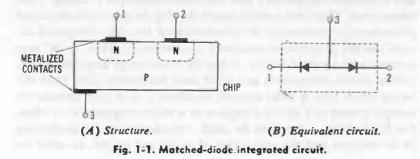

This discussion will not explain how ICs are manufactured, for that is beyond the scope of this book. Instead, a simple description of IC structure will be given. Figs. 1-1 through 1-5 show this structure. These sketches do not show proportions accurately, since it would be difficult to preserve exact scales and still keep the various parts of the IC visible to the reader, but the sketches are sufficiently true for purposes of illustration.

Fig. 1-1 shows a dual-diode (common-anode) IC. In Fig. 1-1A, two n regions have been diffused into a p-type chip to provide the pn junctions of the diodes. A thin spot of metal has been deposited on each n region and on the chip to provide contacts, and attached to these contacts are leads 1, 2, and 3. Fig. 1-1B shows the equivalent circuit.

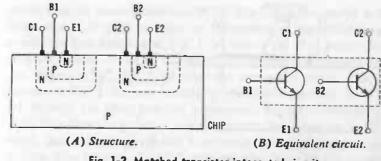

Fig. 1-2 shows an IC containing two matched npn transistors. Here (Fig. 1-2A), the chip is p-type silicon into which n and p regions have been diffused for the emitters (E1, E2), bases (B1, B2), and collectors (C1, C2) of the transistors. A thin spot of metal deposited

Fig. 1-2. Matched-transistor integrated circuit.

on each n region and on each p region provides contact, and attached to these contacts are leads C1, E1, and B1 for the first transistor; and C2, B2, and E2 for the second transistor. Fig. 1-2B shows the equivalent circuit.

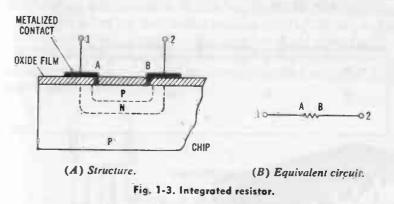

Fig. 1-3 shows how a resistor is formed in an IC. In Fig. 1-3A, the resistive element is the p region; a desired resistance value is obtained by suitably processing this region. An n layer isolates this resistor from the p-type chip. A thin oxide layer has been grown on the surface of the chip for protection, and this layer is penetrated through holes at A and B by thin deposits of metal which contact the ends of the integrated resistor. Leads 1 and 2 are connected to these contacts.

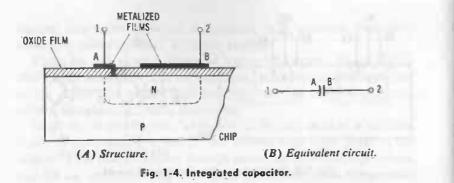

Fig. 1-4 shows how a capacitor is formed in an IC. In Fig. 1-4A, an n region has been processed into the p-type chip, and a thin oxide film then has been grown on the surface of the chip. The n region constitutes one plate of the capacitor, and the oxide film is the dielectric. A thin metallic film (B) deposited on the oxide film is the other plate of the capacitor. A thin metallic spot (A) has been deposited on

the film, which it penetrates through a hole to contact one end of the n region. Leads 1 and 2 are attached to these film-type contacts. The area of plate B is chosen for a desired capacitance (for a given oxide-film thickness, the greater the area the higher the capacitance).

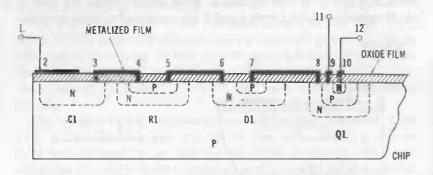

Integrated diodes, transistors, resistors, and capacitors—such as those in Figs. 1-1 through 1-4—may be combined in a number of ways to build into the chip any desired electronic device employing those components. Fig. 1-5, for example, shows how a single capacitor, resistor, diode, and transistor may be integrated into a chip to-

(A) Structure.

gether with all interconnections. While this is not necessarily a functional circuit, it gives as clear an illustration of the structure as is possible in two dimensions. Fig. 1-5A shows the cross section of the integrated series circuit of capacitor C1, resistor R1, diode D1, and npn transistor Q1. Fig. 1-5B gives the equivalent circuit. The components in Fig. 1-5A may readily be identified separately from Figs. 1-1 through 1-4. Note how the components are interconnected: The metal film between points 3 and 4 connects the capacitor to the resistor, the film between 5 and 6 connects the resistor to the diode, and the film between 7 and 8 connects the diode to the transistor. External leads 1, 11, and 12 are connected to the film at points 2, 9, and 10, respectively.

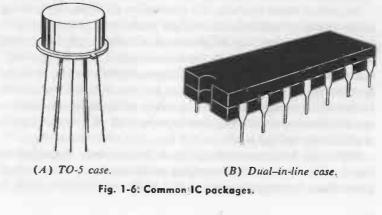

#### 1.2 THE IC AS A UNIT

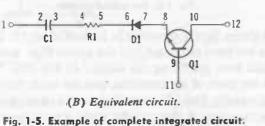

An integrated circuit is equipped with leads or lugs, so that it may be plugged into a small socket or soldered to points on a foundation, such as a printed circuit board. Several different IC packages are obtainable. Two of the most common of these are shown in Fig. 1-6.

Fig. 1-6A shows the TO-5 style of metal case, which is very familiar as a transistor package. The IC shown has eight leads, but 10and 12-lead ICs also are available in TO-5 cans. The diameter of the TO-5 can is a little more than  $\frac{1}{4}$  inch, and the leads are  $\frac{1}{2}$ -inch long.

Fig. 1-6B shows the dual-in-line package (DIP). This is a molded plastic housing having terminal pins (seven or eight) along each long edge. The 14-pin package is approximately 34-inch long and 34-inch wide. Similar rectangular packages also are supplied: *mini-DIP* (eight leads) and *flat pack* (10 leads).

#### **1.3 IC SYMBOLS**

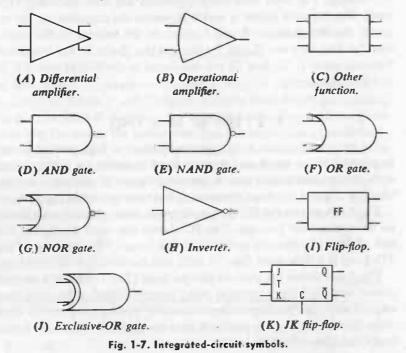

Fig. 1-7 shows circuit symbols for a representative sampling of integrated circuits, according to function. Figs. 1-7A and 1-7B represent linear ICs. Figs. 1-7D through 1-7G and 1-7I through 1-7K represent digital ICs. Figs. 1-7C and 1-7H can be used to represent either linear or digital applications.

In each of these symbols, the convention of input terminals on the left and output terminals on the right is observed. The symbol in Fig. 1-7C can represent any IC (such as a voltage regulator, multiple transistors, etc.) for which there is no other specific symbol. The block must be labeled with the IC type number, and each lead must be appropriately numbered to correspond to the IC base numbering. It should be mentioned here that some publications do not use the specific functional symbols, but represent all ICs with a simple triangle similar to Fig. 1-7A.

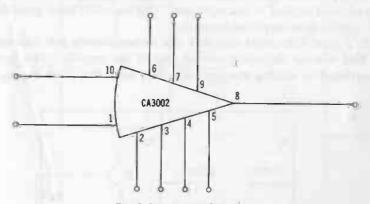

While the basic symbols in Fig. 1-7 show only input and output signal connections, all connections must be shown in a wiring diagram. Such a complete presentation is illustrated in Fig. 1-8. Here, a CA3002 integrated circuit is shown with all ten of its leads. Although the numbering corresponds to that of the leads of the actual

Fig. 1-8. Labeled IC symbol.

IC, it is not always shown consecutively in a schematic. Instead, the *correctly numbered* leads (except input and output) are drawn wherever clarity will be ensured in the schematic.

#### **1.4 DIFFERENTIAL AMPLIFIER IN ICs**

A great many ICs employ a differential amplifier in the input stage, and some have differential amplifiers in other direct-coupled stages, as well. The differential amplifier is used because it is inherently one that reduces drift caused by shifts in current and temperature and the aging of components, and it does this without inadvertently cancelling out the input signal. Some ICs, such as the Type CA3000, consist only of a differential amplifier.

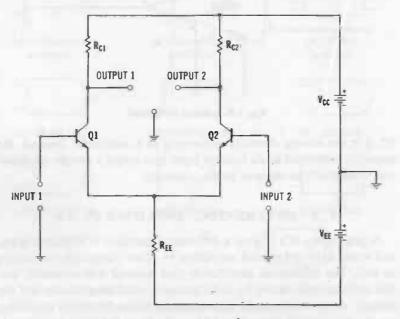

Fig. 1-9 shows a bare-bones version of the differential amplifier, offered here for discussion. The two transistors (Q1, Q2) and the two collector resistors ( $R_{C1}$ ,  $R_{C2}$ ) are closely matched, and collector bias voltage  $V_{CC}$  equals emitter bias voltage  $V_{EE}$ . Because of this matching and the bridge-like symmetry of the circuit, any drift in the left leg of the circuit is cancelled by an equal drift in the right leg. If a separate signal is applied to each input, the output will be proportional to the difference between the two, and this accounts for the name differential amplifier. If, however, the same signal is applied to both inputs, ideally it will be cancelled and the output will be zero. This brings up several terms: Performance with the signal applied simultaneously to

both inputs is called *common-mode operation*. If the circuit is really balanced, it will transmit no signal in this condition, and the *common-mode gain* is zero. Conversely, the *common-mode rejection* is infinite. If a signal is applied to one input only, with the other input grounded, the signal will be amplified normally.

In a good differential amplifier, the common-mode rejection must be high without degrading normal gain of the amplifier. This is accomplished by making resistance  $R_{EE}$  very high. But when  $R_{EE}$  is in-

Fig. 1-9. Basic differential amplifiers

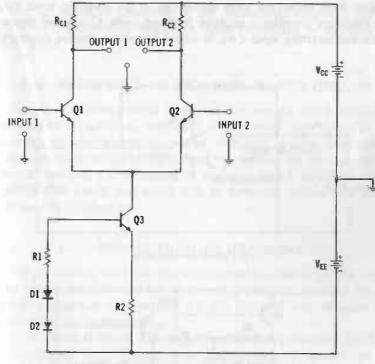

creased, voltage  $V_{EE}$  also must be increased. High  $V_{EE}$  in combination with high  $R_{EE}$  constitutes a constant-current supply, which shows that the ideal situation is to drive the differential amplifier from a controlled constant-current source. A far more efficient method than high voltage plus high resistance is to use a constant-current device with a low voltage. The normal value of  $V_{EE}$  (equal to  $V_{CC}$ ) then may be used. This arrangement is shown in Fig. 1-10, where the constant-current conduction characteristic of common-emitter transistor Q3 is exploited. The combination of this transistor, resistors R1 and R2, and diodes D1 and D2 constitutes the constant-current sink. (In some ICs, the sink is somewhat more elaborate than this example.)

#### **1.5 OPERATIONAL-AMPLIFIER IC**

A large number of ICs are operational amplifiers (op amps). The typical operational amplifier has differential input and single-ended output. Its input impedance is high, and its output impedance is low. The open-loop voltage gain of the op amp is extremely high, so that large amounts of external feedback may be employed without reducing the gain below a useful level. This allows the transmission characteristic of the amplifier to be shaped by the feedback network. Extremely high input impedance is achieved in some op amps through the use of field-effect transistors (JFETs or MOSFETs) in the input differential-amplifier stage.

Fig. 1-11A shows a typical op-amp setup. The two inputs of the device are termed *inverting* and *noninverting*. This means that when a signal is applied to the noninverting input, the signal emerges in the same phase at the output, but when the signal is applied to the inverting input, the output signal has the opposite phase. External

resistor  $R_t$  is connected from the output to the inverting input (-) and therefore provides a negative feedback path. Connected instead to the noninverting input (+), it would introduce positive feedback.

o + Vcc INVERTING INPUT OUTPUT VEF NONINVERTING SIGNAL INPUT SIGNAL OUTPUT INPUT (A) Typical op-amp setup. ¥+ Z D3 D5 🛨 04 D2 07 04 05 09 08 OUTPUT INVERTING INPUT Q10 NON-3 INVERTING O INPUT AMPLIFIER 5 03 011 **BIAS INPUT** 01 D6 (B) Internal circuit of representative op amp.

Fig. 1-11. Operational-amplifier IC.

The closed-loop voltage gain in Fig. 1-11A is determined by the ratio of feedback resistance  $(R_t)$  to amplifier input resistance  $(R_i)$ :  $A_r = R_t/R_i$ . Fig. 1-11B shows the internal circuit of a representative op amp (RCA Type CA3080).

For an extensive treatment of the operational amplifier, see *IC* Op-Amp Cookbook by Walter G. Jung (published by Howard W. Sams & Co., Inc., 1974).

# **1.6 ECONOMICS OF THE INTEGRATED CIRCUIT**

Integrated circuits provide significant size, weight, and labor-saving advantages. In addition, they offer a substantial cost bonus in the assembly of larger electronic systems. A typical example is an operational amplifier selling at the time of this writing for 80 cents retail. This IC contains 20 transistors, 11 resistors, and 1 capacitor—components that would cost about \$33 in the retail market and would still need to be wired up.

# **1.7 PRECAUTIONS IN HANDLING ICs**

Before starting the tests and experiments in Part 2 of this book, read closely the following tips on handling integrated circuits. Proper handling will not only protect the IC, but will also enhance the progress of the experiment.

A. Mechanical Shock. Like other semiconductor devices, the IC is a surprisingly rugged component. Nevertheless, it should not be abused by dropping, hammering, squeezing, pulling, and so on. Treatit as if it were a more delicate component.

B. Input Protection. When the IC contains an unprotected MOSFET input stage, keep the short-circuiting device in place until the IC is completely installed. A gate-protected IC, such as Type CA3140, has self-contained protective zener diodes and does not require this special handling.

C. Installation. Most ICs are tiny devices having a number of leads or pins spaced closely together. This demands considerable manual dexterity in handling the IC and in making connections to it. Be sure the leads do not touch each other; use tweezers to separate them. In a test setup, it is better to plug the IC into a socket or breadboard than to connect it with clip leads. Use the full length of IC leads; do not clip them unless you are sure you can straighten and align the shortened leads. Check all wiring in a setup carefully, and install the IC last. When the test is over, remove the IC first.

D. Soldering. Heat-sink the leads of an IC before soldering. If it is impracticable to use a heat sink, then solder rapidly and blow cool air on the joint immediately afterward.

E. Power-Supply Polarity. Carefully observe the polarities of the dc supplies. Reversing positive and negative may damage the IC.

F. Sequence in Energizing. Apply the dc operating voltage(s) after the IC has been installed in a setup. When the test is finished, disconnect the dc before the IC is removed. When a dual dc supply is used, open and close both dc circuits simultaneously. Apply the signal after the power is on.

G. Maximum Ratings. Keep all signal and bias voltages and currents and the power dissipation within the maximum limits specified by the IC manufacturer.

H. Input/Output Isolation. Keep the signal input and output circuits isolated from each other; otherwise, the high gain of the IC may encourage undesired output-to-input coupling.

1. Temperature. Like other semiconductor devices, the IC has some sensitivity to temperature. The operating temperature of the device therefore must be kept within the limits specified by the manufacturer. Unless a temperature-effect test is under way, keep the IC at room temperature; in any test setup, keep the IC away from hot components. During a temperature test, hold the temperature of the IC at each level only so long as is needed for the electrical characteristic under study to stabilize at that level.

J. Fields. Keep the IC out of intense magnetic and electric fields, both af and rf.

#### **1.8 IC USED IN THIS BOOK**

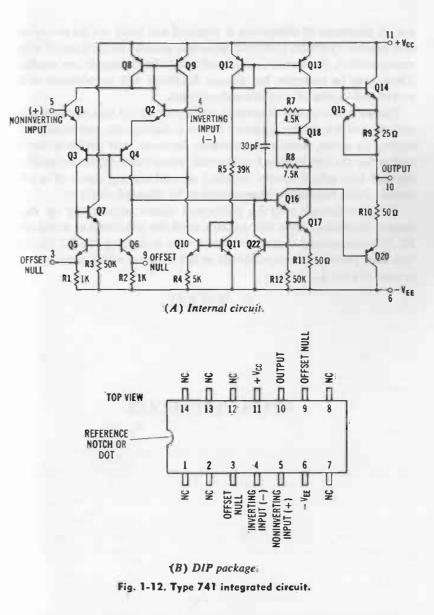

The Type 741 integrated circuit is used in the experiments in this book. This device is an inexpensive, general-purpose op amp that is widely available on a single-unit retail basis. The internal circuit of the 741 is shown in Fig. 1-12A, and a top view of the 14-contact, dual-in-line package (DIP) is shown in Fig. 1-12B. It is worth noting here that the 741 is obtainable also in a TO-5 can (8 leads), a flat pack (10 leads), and a mini-DIP package (8 leads). However, the lead numbering in Fig. 1-12 pertains only to the DIP package.

The 741 has some important advantages. Among these are: (A) its output is short-circuit protected, (B) this IC is internally compensated (by means of a 30-pF integrated capacitor between transistors Q16 and Q18 in Fig. 1-12A), (C) provision is made for offset null (terminals 3 and 9 in Fig. 1-12), and (D) the 741 is free from latchup (the condition in which the input stage is held in saturation by feedback which has changed from negative to positive).

#### **1.9 NATURE OF EXPERIMENTS IN THIS BOOK**

The purpose of the experiments in Part 2 is to test the electrical characteristics of the IC and in this way to obtain a hands-on familiarity with the device. The 741 integrated circuit is employed through-

out. A minimum of equipment is required and need not be of expensive laboratory grade. Required apparatus is listed at the head of each experiment. A positive dc supply and a negative dc supply are needed. These may be batteries, but greater flexibility will be obtained with power-line-operated variable-voltage units.

Except where noted otherwise, the layout of the test circuit is not critical, and the reader therefore is free to indulge his preferences. In setting up a test, most experimenters, however, will probably favor one of the modern plug-in breadboards, since these require no soldering and they afford speedy building up and tearing down of a test circuit. Also, they allow components to be changed easily.

The experiments may be performed either sequentially or randomly, depending upon the reader's need for information about the IC. We recommend that the beginner who is meeting the IC for the first time perform the experiments in the order in which they are arranged in Part 2.

# PART 2

# Experiments

### PART 2

# Experiments

The following pointers are offered for the guidance of the experimenter. Please read them carefully before embarking upon the experiments. In addition to containing material essential to the success of experiments, they offer certain information which will not be repeated in individual experiments.

1. Sequence. The experiments are arranged in an order which uncovers various information concerning the IC, starting with the simplest characteristics and proceeding through more sophisticated ones. The reader is not compelled to follow this sequence, but the newcomer to ICs doubtless will find it helpful to do so.

2. Step-by-Step Procedure. The cookbook-type directions in this part were developed to insure success of the experiment and to minimize the chance of damaging the apparatus. The reader is strongly urged to follow the procedures as they are given.

3. Integrated Circuit. The same type of IC is used in each experiment: the Type 741 operational amplifier. Use a new IC. Surplus ones sometimes are rejects having high offset which will ruin some of the experiments. See Section 1.7 in Part 1 for precautions in working with ICs.

4. Terminal Labeling. Numbering of the IC terminals in the schematics is not in the sequence in which the terminals of the actual unit are arranged (Fig. 1-12, Part 1), but has been chosen for clarity of the diagram. Unused terminals are omitted from the drawing.

5. DC Supply. A split dc supply is shown in each experiment. For drafting convenience, batteries are shown, and their use is permissible. However, low-ripple, power-line-operated supplies also can be

used and are preferred in most instances. Several excellent, smallsized units are available which supply separate, variable positive and negative outputs. In the experiments, the voltages must be set to the levels shown in the schematics.

6. DC Test Signal. A dc input signal is required in a number of experiments. This signal is supplied by a  $1\frac{1}{2}$ -volt cell. A fresh size-C flashlight cell is satisfactory for this purpose.

7. AC Test Signal. See 10. Signal Generators.

8. Meters. Service-type meters are satisfactory. Voltmeters for dc should be 20,000 ohms per volt or higher. (Use an electronic voltmeter—vacuum-tube, transistor, or FET—where specified.) Voltmeters for ac should be of the electronic type. Millivoltmeters for dc also must be electronic, as the nonelectronic type has too low an internal resistance. An accuracy of  $\pm 2\%$  of full scale is satisfactory for the nonelectronic meters;  $\pm 5\%$  of full scale is satisfactory for the electronic meters.

9. Instrument Switching. In some circuits (such as Fig. 2-16), a single meter is switched alternately between input and output. In other circuits (such as Fig. 2-17), separate input and output meters are shown. Where separate meters appear, the circuit is susceptible to oscillation arising from feedback through switch wiring, so the use of a meter switch is discouraged.

10. Signal Generators. Most required ac signals are sine waves or square waves in the audio-frequency range. Only a few experiments call for a 100- or 200-kHz signal. The maximum frequency in any experiment is 1 MHz. A reliable sine/square-wave audio generator may be used for the lower frequencies (most such instruments tune up to 200 kHz), and an rf signal generator having up to 1 volt rms output may be used for the 1-MHz signal. Generators used in the experiments should have low output impedance (500 ohms is good; 50 ohms is better). A good function generator will satisfy all requirements: frequency, waveform, and impedance.

11. Oscilloscope. Some experiments—specifically Nos. 9, 11, 15, 20, and 22—call for an oscilloscope having a voltage-calibrated vertical axis; and one experiment (No. 23) calls for one with a time-calibrated horizontal axis, as well. In any other instance, a basic oscilloscope will suffice.

12. Leads. Keep all leads as short as practicable, and run them as directly as possible even when a plug-in breadboard is used.

13. Resistors. All fixed resistors are 5% or 10% 4-watt composition units. 14. Capacitors. Capacitors are nonelectrolytic (minimum rating, 50 V). Ceramics and Mylars are suitable.

15. Potentiometers. Potentiometers are composition type, exceptwhere noted ("ww") as wirewound

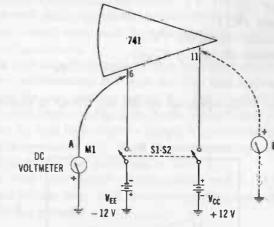

EXPERIMENT 1. DC OPERATING VOLTAGES Required Equipment (Fig. 2-1)

1 741 integrated circuit 1 dc voltmeter (M1) 1 dpst switch (S1-S2)

1 + 12 V dc supply (V<sub>cc</sub>)

1 - 12 V dc supply (V<sub>EE</sub>)

Fig. 2-1. Dc operating voltages.

### **Test Procedure**

- 1. With switch S1-S2 open, set up the test circuit as shown in Fig. 2-1.

- 2. Close switch S1-S2.

- 3. With voltmeter M1 in position A and with its positive lead grounded, check the voltage at terminal 6 of the IC. Record. This is the negative voltage of the IC.

- 4. With voltmeter M1 in position B and with its negative lead grounded, check the voltage *at* terminal 11 of the IC. Record. This is the positive voltage of the IC.

(In all measurements of operating voltage in IC circuits, check the voltage in the above manner, i.e., at the IC contact. When the voltage

is measured at the dc supply or at an input terminal on the chassis, error can be caused by series outboard components or faulty leads.

#### Sample Results

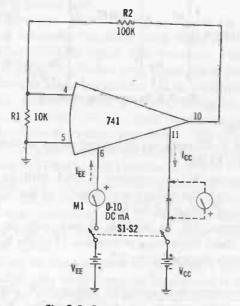

# **EXPERIMENT 2. OPERATING CURRENT**

# Required Equipment (Fig. 2-2)

- 1 741 integrated circuit

- 1 0-10 dc milliammeter (M1)

- 1 dpst switch (S1-S2)

- 1 10K resistor (R1)

- 1 100K resistor (R2)

- 1 + 15 V variable dc supply (V<sub>cc</sub>)

- 1 15 V variable dc supply (V<sub>EE</sub>)

#### **Test Procedure**

1. With switch S1-S2 open, set up the test circuit as shown in Fig. 2-2.

Fig. 2-2. Operating current.

## Table 2-1. Sample Results, Operating Current

| Supply Voltage | loc    | IER    |

|----------------|--------|--------|

| ±15 V          | 2.2 mA | 2.2 mA |

| ±12 V          | 1.9 mA | 1.9 mA |

| ±9 V           | 1.5 mA | 1.5 mA |

| ±6 V           | 1.0 mA | 1.0 mA |

- 2. Set both dc supplies to zero.

- 3. Insert milliammeter M1 into the lead between negative supply  $V_{EE}$  and terminal 6 of the IC. Be careful of meter polarity.

- 4. Set both supplies to 6 V. Read the corresponding current value and record it under  $I_{EE}$  (see column 3 in Table 2-1).

- 5. Repeat with both supplies set successively to 9 V, 12 V, and 15 V. At each voltage step, read the corresponding current, and record it in the  $I_{EE}$  column.

- 6. Return both supply voltages to zero, and open switch S1-S2.

- 7. Remove milliammeter M1 from the  $V_{EE}$  lead and reconnect it in the lead between positive supply  $V_{CC}$  and terminal 11 of the IC (see dashed symbol in Fig. 2-2). Again, be careful of meter polarity. Restore the lead from negative supply  $V_{EE}$  to terminal 6 of the IC.

- 8. Set both supplies to 6 V. Read the corresponding current, and record it under I<sub>cc</sub> (see column 2 in Table 2-1).

- 9. Repeat with both supplies set successively to 9 V, 12 V, and 15 V. At each voltage step, read the corresponding current, and record it in the  $I_{CC}$  column.

#### Sample Results

See Table 2-1.

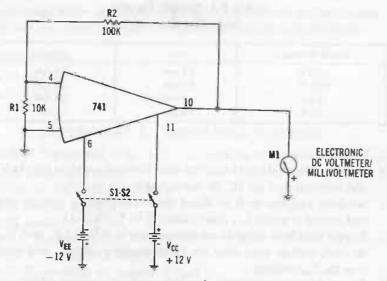

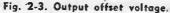

# **EXPERIMENT 3. OUTPUT OFFSET VOLTAGE**

# Required Equipment (Fig. 2-3)

- 1 741 integrated circuit 1 electronic dc voltmeter/millivoltmeter (M1)

- 1 dpst switch (S1-S2)

- 1 10K resistor (R1)

- 1 100K resistor (R2)

- 1 + 12 V dc supply (V<sub>cc</sub>)

- 1 12 V dc supply (V<sub>EE</sub>)

#### **Test Procedure**

- 1. With switch S1-S2 open, set up the test circuit as shown in Fig: 2-3.

- 2. Close switch S1-S2.

- 3. Note the deflection of meter M1 and the polarity of the offset voltage. (If the meter deflects downward, reverse its polarity. The offset voltage can be positive or negative, depending on the type of unbalance inside the IC.)

#### Sample Results

$V_{offset} = 10 mV$

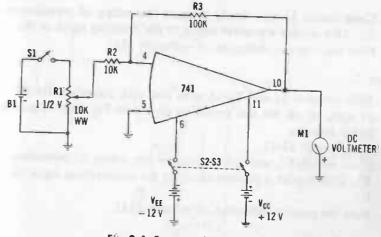

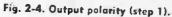

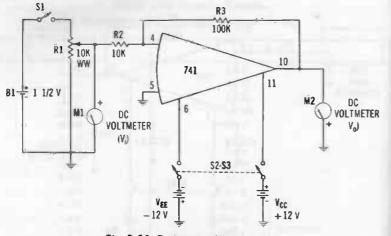

# **EXPERIMENT 4. OUTPUT POLARITY**

Required Equipment (Figs. 2-4 and 2-5).

741 integrated circuit

dc voltmeter (M1)

spst switch (S1)

dpst switch (S2-S3)

10K wirewound potentiometer (R1)

10K resistor (R2)

100K resistor (R3)

+12 V dc supply (V<sub>cc</sub>)

1 - 12 V dc supply (V<sub>EE</sub>) 1 1<sup>1</sup>/<sub>2</sub> V size-C cell (B1)

# Test Procedure

#### Step 1

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to zero, set up the test circuit as shown in Fig. 2-4. Watch the meter polarity.

- 2. Close switch S2-S3.

Fig. 2-5. Output polarity (step 2)

- 3. Close switch S1 and slowly increase the setting of potentiometer R1. This applies a positive signal to the inverting input of the IC.

- 4. Note the negative deflection of voltmeter M1.

#### Step 2

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to zero, set up the test circuit as shown in Fig. 2-5. Watch the meter polarity.

- 2. Close switch S2-S3.

- 3. Close switch S1, and slowly increase the setting of potentiometer R1. This applies a positive signal to the noninverting input of the IC.

- 4. Note the positive deflection of voltmeter M1.

#### Sample Results

In Step 1, a positive signal applied to the inverting input (terminal 4 of the IC) gives a negative output signal. In Step 2, the same positive signal applied to the noninverting input (terminal 5 of the IC) gives a positive output signal.

# **EXPERIMENT 5. OFFSET NULL ADJUSTMENT**

#### **Required Equipment**

This experiment consists of three steps, each requiring a different test circuit.

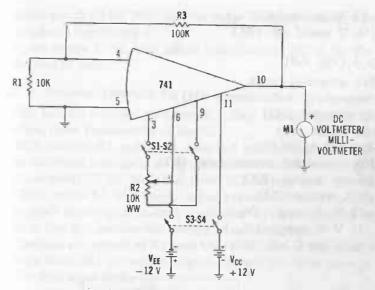

Step 1 (Fig. 2-6)

741 integrated circuit

dc voltmeter/millivoltmeter (M1)

dpst switches (S1-S2, S3-S4)

10K resistor (R1)

100K resistor (R3)

10K wirewound potentiometer (R2)

+12 V dc supply (V<sub>CC</sub>)

-12 V dc supply (V<sub>EE</sub>)

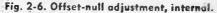

### Step 2 (Fig. 2-7)

1 741 integrated circuit 1 electronic dc millivoltmeter (M1) 1 dc voltmeter (M2)

1 spst switch (S1)

- 1 dpst switch (S2-S3)

- 1 10K wirewound potentiometer (R1)

- 1 10-ohm resistor (R2)

- 1 10K resistor (R3)

- 1 100K resistor (R4)

- 1 + 12 V dc supply (V<sub>cc</sub>)

Fig. 2-7. Offset-null adjustment, external (method 1).

# 1 -12 V dc supply ( $V_{EE}$ ) 1 1<sup>1</sup>/<sub>2</sub> V size-C cell (B1)

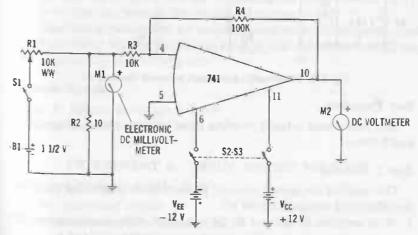

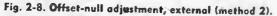

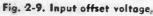

#### Step 3 (Fig. 2-8)

- 741 integrated circuit

electronic dc millivoltmeter (M1)

dc voltmeter (M2)

spst switch (S1)

dpst switch (S2-S3)

10K wirewound potentiometer (R1)

10-ohm resistor (R2)

100K resistor (R3)

+12 V dc supply (V<sub>cc</sub>)

- 1 12 V dc supply (V<sub>EE</sub>)

- 1 11/2 V size-C cell (B1)

### **Test Procedure**

This experiment actually involves three test procedures, Steps 1, 2, and 3 below.

#### Step 1. Internal

This method employs a zero-set potentiometer connected between the offset-null terminals of the IC.

1. With switches S1-S2 and S3-S4 open and with potentiometer R2 set to midrange, set up the test circuit as shown in Fig. 2-6.

- 2. Close switch \$3-\$4. Note that the meter is slightly deflected owing to offset (Experiment 3).

- 3. Close switch S1-S2, and adjust potentiometer R2 to set the deflection to zero.

# Step 2. External (Method 1)

This method employs an external nulling voltage applied to the inverting input (terminal 4) of the IC.

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to maximum resistance, set up the test circuit as shown in Fig. 2-7.

- 2. Close switch S2-S3. Note that meter M2 deflects, indicating offset.

- 3. Close switch S1, and slowly adjust potentiometer R1 to apply a positive input-signal voltage (indicated by millivoltmeter M1). Note that this reduces the reading of voltmeter M2.

- 4. Continue adjustment of R1 until M2 reads zero. At this point, read from meter M1 the voltage required to null the offset through the inverting input of the IC.

# Step 3. External (Method 2)

This method employs an external nulling voltage applied to the noninverting input (terminal 5) of the IC.

- 1. With switches S1 and S2-S3 open and potentiometer R1 set to maximum resistance, set up the test circuit as shown in Fig. 2-8.

- 2. Close switch S2-S3. Note that meter M2 deflects, indicating offset.

- 3. Close switch S1, and slowly adjust potentiometer R1 to apply a positive input-signal voltage (indicated by millivoltmeter M1). Note that this reduces the reading of voltmeter M2.

- 4. Continue adjustment of R1 until M2 reads zero. At this point, read from meter M1 the voltage required to null the offset through the noninverting input of the IC.

# Sample Results

Step 2: Input null voltage = 1 mVStep 3: Input null voltage = 10 mV

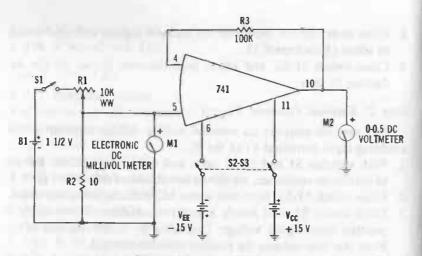

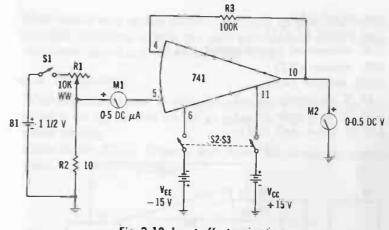

# EXPERIMENT 6. INPUT OFFSET VOLTAGE Required Equipment (Fig. 2-9)

741 integrated circuit

electronic dc millivoltmeter (M1)

dc voltmeter (M2)

- 1 spst switch (S1)

- 1 dpst switch (S2-S3)

- 1 10K wirewound potentiometer (R1)

- 1 10-ohm resistor (R2)

- 1 100K resistor (R3)

- 1 + 15 V dc supply (V<sub>cc</sub>)

- 1 15 V dc supply (V<sub>EE</sub>)

- 1 11/2 V size-C cell (B1)

#### **Test Procedure**

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to maximum resistance, set up the test circuit as shown in Fig. 2-9.

- 2. Close switch S2-S3, noting that meter M2 is deflected by offset.

- 3. Close switch S1, and slowly adjust potentiometer R1 to set meter M2 to zero. At this point, note the deflection of meter M1; this voltage is equal to the input offset voltage which it balances out.

#### Sample Result

$V_{io} = 1 mV$

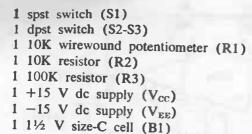

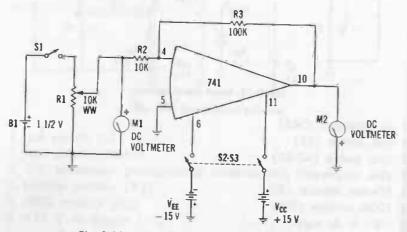

**EXPERIMENT 7. INPUT OFFSET CURRENT**

Required Equipment (Fig. 2-10)

- 1 741 integrated circuit

- 1 low-range dc microammeter (M1)

1 dc voltmeter (M2) 1 spst switch (S1) 1 dpst switch (S2-S3) 1 10K wirewound potentiometer (R1) 1 10-ohm resistor (R2) 1 100K resistor (R3) 1 +15 V dc supply ( $V_{CC}$ ) 1 -15 V dc supply ( $V_{EE}$ ) 1 1<sup>1</sup>/<sub>2</sub> V size-C cell (B1)

#### **Test Procedure**

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to maximum resistance, set up the test circuit of Fig. 2-10.

- 2. Close switch S2-S3, noting that meter M2 is deflected by offset.

- 3. Close switch S1, and slowly adjust potentiometer R1 to set meter M2 to zero. At this point, note the deflection of meter M1; this reading is equal to the input offset current.

### Sample Result

$I_{io} = 0.1 \ \mu A = 100 \ nA$

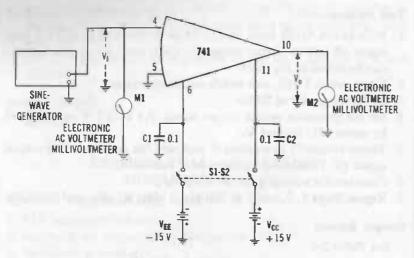

# **EXPERIMENT 8.** CLOSED-LOOP DC VOLTAGE GAIN Required Equipment (Figs. 2-11 and 2-12)

1 741 integrated circuit 2 dc voltmeters (M1, M2)

Fig. 2-11. Closed-loop dc voltage gain (inverting).

### **Test Procedure**

This experiment actually involves two test procedures, Steps 1 and 2 below.

# Step 1. Inverting

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to zero, set up the test circuit as shown in Fig. 2-11. Watch the meter polarity.

- 2. Close switch S2-S3. Observe that meter M2 is slightly deflected, owing to offset (Experiment 3).

- 3. Close switch S1, and adjust potentiometer R1 for a dc input signal (V<sub>1</sub>) of 0.1 V indicated by meter M1.

- 4. Read the corresponding dc output-signal voltage  $(V_o)$  indicated by meter M2. Note that the output-signal polarity is negative, whereas the input-signal polarity is positive. This is the result of signal inversion in the IC.

- 5. Calculate the voltage gain:  $A = V_o/V_i$ .

6. Note that A also equals R3/R2, the ratio of feedback resistance to input resistance. Check the gain with various other values of resistance substituted for the original 100K.

# Step 2. Noninverting

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to zero, set up the test circuit as shown in Fig. 2-12. Watch the meter polarity.

- 2. Close switch S2-S3. Observe that meter M2 is slightly deflected, owing to offset (Experiment 3).

Fig. 2-12. Closed-loop dc voltage gain (noninverting).

- 3. Close switch S1, and adjust potentiometer R1 for a dc input signal (V<sub>1</sub>) of 0.1 V indicated by meter M1.

- Read the corresponding dc output signal (V<sub>o</sub>) indicated by meter M2. Note that the output-signal polarity is positive, the same as the input signal (noninversion in the IC).

- 5. Calculate the voltage gain:  $A = V_o/V_i$ .

- Note that A also equals R3/R2, the ratio of feedback resistance to input resistance. Check the gain with various other values of resistance substituted for the original 100K.

# Sample Results

Step 1:  $A = V_o/V_i = 1/0.1 = 10$ , inverting Step 2:  $A = V_o/V_i = 1/0.1 = 10$ , noninverting

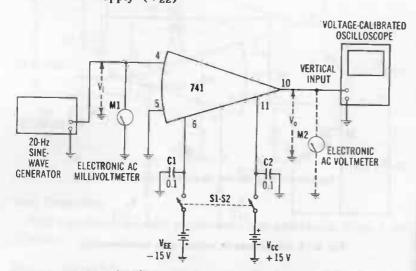

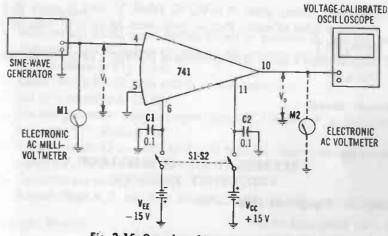

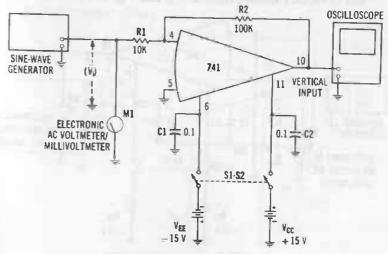

# **EXPERIMENT 9. OPEN-LOOP AC VOLTAGE GAIN**

## Required Equipment (Fig. 2-13)

741 integrated circuit

electronic ac millivoltmeter (M1)

electronic ac voltmeter (M2)—optional

voltage-calibrated oscilloscope

sine-wave generator

0.1-μF capacitors (C1, C2)

dpst switch (S1-S2)

+15 V dc supply (V<sub>cc</sub>)

-15 V dc supply (V<sub>EE</sub>)

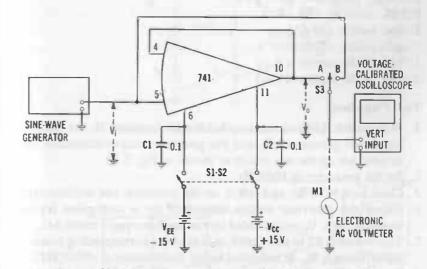

Fig. 2-13. Open-loop.ac voltage gain.

#### **Test Procedure**

- 1. With switch S1-S2 open, the generator off and its output attenuator set to zero, and the oscilloscope off, set up the test circuit as shown in Fig. 2-13. (In this experiment, the IC runs "wide open" and is "touchy." Keep all leads short and direct.)

- 2. Close switch S1-S2, switch on the generator, and switch on the oscilloscope.

- 3. Set the generator to 20 Hz.

- 4. Set the generator output (input signal  $V_i$ ) for maximum undistorted output ( $V_o$ ) indicated by the oscilloscope. Read the corresponding input-signal voltage ( $V_i$ ) from meter M1. (Alterna-

tively, output voltage  $V_o$  may be read with an electronic ac voltmeter, M2. However, the meter does not readily show the exact point at which distortion of  $V_o$  begins.)

5. Calculate the voltage gain:  $A = V_o/V_i$ . (Both  $V_o$  and  $V_i$  must be in the same kind of units; that is, both must be in volts rms; volts peak, etc.)

#### Sample Result

$V_i = 0.3 \text{ mV}$   $V_o = 1 \text{ V}$ A = 3333

This is not the maximum amplification obtainable with open-loop operation. Individual ICs and individual test setups can afford much higher values than the above sample. Note also that this is the lowfrequency (20-Hz) gain, relatively close to dc; open-loop gain falls rapidly with frequency (see Experiment 11).

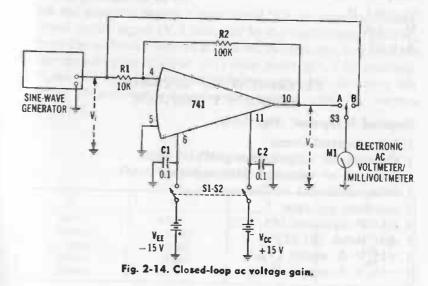

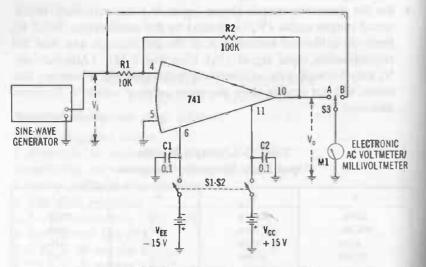

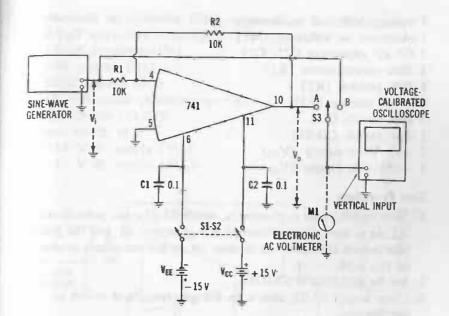

# EXPERIMENT 10. CLOSED-LOOP AC VOLTAGE GAIN Required Equipment (Fig. 2-14)

- 1 741 integrated circuit

- 1 electronic ac voltmeter/millivoltmeter (M1).

- 1 sine-wave generator

2 0.1- $\mu$ F capacitors (C1, C2) 1 dpst switch (S1-S2) 1 spdt switch (S3) 1 10K resistor (R1) 1 100K resistor (R2) 1 +15 V dc supply (V<sub>CC</sub>) 1 -15 V dc supply (V<sub>EE</sub>)

#### **Test Procedure**

- 1. With switch S1-S2 open, switch S3 in position B, and the generator off and its attenuator set to zero, set up the test circuit as shown in Fig. 2-14.

- 2. Close switch S1-S2, and switch on the generator.

- 3. Set the generator to 1000 Hz.

- 4. Set the generator output (input signal V<sub>1</sub>) to 0.1 V indicated by meter M1. Record V<sub>1</sub>.

- 5. Throw switch S3 to position A, and read the corresponding output signal (V<sub>o</sub>) indicated by meter M1. Record V<sub>o</sub>.

- 6. Calculate the voltage gain:  $A = V_o/V_i$ .

- Note that A also equals R2/R1, the ratio of feedback resistance to input resistance. Check the gain with various other values of resistance substituted for the original 100K.

#### Sample Result

$V_i = 0.1 V$  $V_o = 1 V$ A = 10

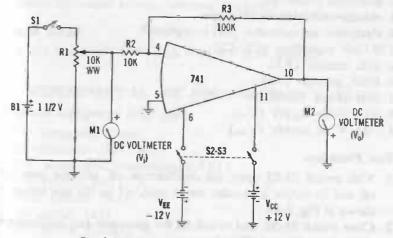

# EXPERIMENT 11. OPEN-LOOP FREQUENCY RESPONSE

# Required Equipment (Fig. 2-15)

1 741 integrated circuit

- 1 electronic ac millivoltmeter (M1)

- 1 electronic ac voltmeter (M2)-optional

- 1 voltage-calibrated oscilloscope

- 1 sine-wave generator

- 2 0.1- $\mu$ F capacitors (C1, C2)

- 1 dpst switch (S1-S2)

- 1 +15 V dc supply (V<sub>cc</sub>)

- 1 15 V dc supply (V<sub>EE</sub>)

#### **Test Procedure**

- 1. With switch S1-S2 open, the generator off and its output attenuator set to zero, and the oscilloscope off, set up the test circuit as shown in Fig. 2-15. (In this experiment, the IC runs "wide open" and is "touchy." Keep all leads short and direct.)

- 2. Close switch S1-S2, and switch on the generator and oscilloscope

- 3. Set the generator to 20 Hz.

- 4. Set the generator output (input signal V<sub>1</sub>) for maximum undistorted output signal (V<sub>0</sub>) indicated by the oscilloscope. Read V<sub>0</sub> from the calibrated vertical axis of the oscilloscope, and read the corresponding input signal (V<sub>1</sub>) from meter M1. (Alternatively, V<sub>0</sub> may be read with an electronic voltmeter, M2. However, this meter will not readily show the exact point at which V<sub>0</sub> becomes distorted.)

#### Table 2-2. Sample Results, Open-Loop Frequency Response

| F       | V <sub>t</sub> | V.  | Ay   |

|---------|----------------|-----|------|

| 20 Hz   | -0.3 mV        | 1.V | 3333 |

| 200 Hz  | 1 mV           | 1.V | 1000 |

| 2 kHz   | 7 mV           | 17  | 142  |

| 20 kHz  | 20 mV          | 1V  | 50   |

| 200 kHz | 0.1 V          | 1V  | 10   |

- 5. Calculate voltage gain:  $A = V_o/V_i$ . (Both  $V_o$  and  $V_i$  must be in the same kind of units; that is, both must be in volts rms, volts peak, etc.)

- 6. Repeat Steps 4 and 5 at frequencies of 200 Hz, 2 kHz, 20 kHz, and 200 kHz.

#### Sample Results

See Table 2-2.

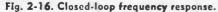

### EXPERIMENT 12. CLOSED-LOOP FREQUENCY RESPONSE

#### Required Equipment (Fig. 2-16)

1 741 integrated circuit

- 1 electronic ac voltmeter/millivoltmeter (M1)

- 1 sine-wave generator

- 2 0.1- $\mu$ F capacitors (C1, C2)

- 1 10K resistor (R1)

- 1 100K resistor (R2)

- 1 dpst switch (S1-S2)

- 1 spdt switch (S3)

- 1 + 15 V dc supply (V<sub>cc</sub>)

- 1 15 V dc supply (V<sub>EE</sub>)

# **Test Procedure**

- 1. With switch S1-S2 open, switch S3 set to position B, and the generator off and its output attenuator set to zero, set up the test circuit as shown in Fig. 2-16.

- 2. Close switch S1-S2, and switch on the generator.

- 3. Set the generator to 20 Hz.

- 4. Set the generator output (input signal V<sub>1</sub>) to 0.1 V as indicated by meter M1. Record V<sub>1</sub>.

- 5. Throw switch S3 to position A and read the corresponding output signal ( $V_o$ ) indicated by meter M1. Record  $V_o$ :

- 6. Calculate the voltage gain:  $A = V_o/V_i$ .

- 7. Repeat Steps 4, 5, and 6 at 200 Hz, 2 kHz, 20 kHz, and 200 kHz.

Sample Results

See Table 2-3.

# Table 2-3. Sample Results, Closed-Loop Frequency Response

| f       | Vi    | V.    | A  |

|---------|-------|-------|----|

| 20 Hz   | 0.1 V | 1V    | 10 |

| 200 Hz  | 0.1 V | τv    | 10 |

| 2 kHz   | 0.1 V | TV    | 10 |

| 20 kHz  | 0.1 V | 1.2 V | 12 |

| 200 kHz | 0.1 V | 0.2 V | 2  |

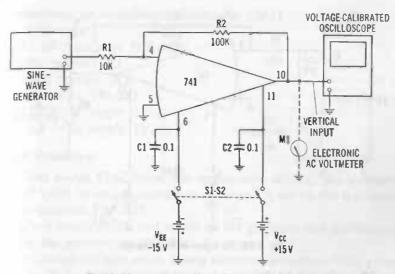

EXPERIMENT 13. UNITY-GAIN FREQUENCY

# Required Equipment (Fig. 2-17)

1 741 integrated circuit

2 electronic ac voltmeter/millivoltmeters (M1, M2)

- 1 sine-wave generator (This instrument must furnish signals from 20 Hz to beyond 1 MHz; otherwise, two separate generators—one af, one rf—will be needed.)

- 2 0.1-µF capacitors (C1, C2)

- 1 dpst switch (S1-S2)

- 1 + 15 V dc supply (V<sub>cc</sub>)

- 1 15 V dc supply (V<sub>EE</sub>)

Fig. 2-17. Unity-gain frequency.

#### **Test Procedure**

- 1. With switch S1-S2 open and the generator off and its attenuator set to zero, set up the test circuit as shown in Fig. 2-17. (In this circuit, the IC runs "wide open" and is "touchy." Keep all leads short and direct.)

- 2. Close switch S1-S2, and switch on the generator.

- 3. Set the generator to 20 Hz.

- 4. Set the generator output (V<sub>1</sub>) to 10 mV as indicated by M1.

- 5. Note the corresponding output voltage ( $V_o$ ) indicated by meter M2. Calculate the 20-Hz voltage gain:  $A = V_o/V_i$ .

- 6. While holding input signal  $V_1$  to 10 mV, tune the generator through its range. Note the frequency at which voltage gain A = 1 ( $V_0 = 10$  mV). This is the unity-gain frequency of the IC.

#### Sample Result

f = 1 MHz

### EXPERIMENT 14. MAXIMUM DC OUTPUT-VOLTAGE SWING

## Required Equipment (Fig. 2-18).

1 741 integrated circuit 2 dc voltmeters (M1, M2) 1 10K wirewound potentiometer (R1) 1 10K resistor (R2) 1 100K resistor (R3) 1 spst switch (S1) 1 dpst switch (S2-S3) 1 +12 V dc supply ( $V_{CC}$ ) 1 -12 V dc supply ( $V_{EE}$ ) 1 1½ V size-C cell (B1)

#### **Test Procedure**

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to zero, set up the test circuit as shown in Fig. 2-18.

- 2. Close switch S2-S3.

- 3. Close switch S1, and adjust potentiometer R1 for an input signal (V<sub>1</sub>) of 0.1 V as indicated by meter M1. Record V<sub>1</sub>.

- 4. Read the corresponding output-signal voltage (V<sub>o</sub>) indicated by meter M2. Record V<sub>o</sub>.

- 5. Repeat Steps 3 and 4 in 0.1-volt steps of input voltage until further increase of  $V_1$  causes no change in  $V_0$  (see last four entries in Table 2-4). The lowest point at which this  $V_0$  saturation occurs is the maximum dc output-voltage swing.

#### Sample Results

$V_{o max} = 10 V dc$  (See Table 2-4.)

Fig. 2-18. Maximum dc output-voltage.swing.

#### Table 2-4. Sample Results, Maximum DC Output-Voltage Swing

| _ | V,    | V.                |

|---|-------|-------------------|

|   | 0.1 V | 1.0 V             |

|   | 0.2 V | 2.0 V             |

|   | 0.3 V | 3.0 V             |

|   | 0.4 V | 4.0 V             |

|   | 0.5 V | 5.0 V             |

|   | 0.6 V | 6.0 V             |

|   | 0.7 V | 7.0 V             |

|   | 0.8 V | 8.0 V             |

|   | 0.9 V | 9.0 V             |

|   | 1.0 V | 9.8 V             |

|   | 1.1 V | 10.0 V            |

|   | 1.2 V | 10.0 V            |

|   | 1.3 V | 10.0 V Saturation |

|   | 1.4 V | 10.0 V            |

This is the condition for  $dc = \pm 12$  V, and R3/R2 = 10.

# EXPERIMENT 15. MAXIMUM AC OUTPUT-VOLTAGE SWING

## Required Equipment (Fig. 2-19)

- 1 741 integrated circuit

- 1 sine-wave generator 1 voltage-calibrated oscilloscope 1 electronic ac voltmeter (M1)—optional 2 0.1- $\mu$ F capacitors (C1, C2) 1 10K resistor (R1) 1 100K resistor (R2) 1 dpst switch (S1-S2) 1 +15 V dc supply (V<sub>CC</sub>)

- 1 15 V dc supply (V<sub>EE</sub>)

#### **Test Procedure**

- 1. With switch S1-S2 open, the oscilloscope off, and the generator off and its output attenuator set to zero, set up the test circuit as shown in Fig. 2-19.

- 2. Close switch S1-S2, and switch on the generator and oscilloscope.

- 3. Set the generator to 1000 Hz.

Fig. 2-19. Maximum ac output-voltage swing.

- 4. Adjust the generator output for maximum undistorted IC output signal, as indicated by the oscilloscope.

- 5. Read the output voltage  $(V_o)$  from the oscilloscope. This value is the maximum output-voltage swing with the IC operating from 15-volt dc supplies and with R2/R1 = 10. (Alternatively, an electronic ac voltmeter, M1, might be used to read the output voltage; however, this meter will not readily show the exact point at which the output voltage becomes distorted.)

#### Sample Result

$V_o = 5.2$  V rms = 7.35 V peak = 14.7 V peak-to-peak

#### **EXPERIMENT 16. DC INPUT-VOLTAGE RANGE**

Required Equipment (Fig. 2-20)

- 1 741 integrated circuit

- 2 dc voltmeters (M1, M2)

- 1 10K wirewound potentiometer (R1)

- 1 10K resistor (R2)

- 1 100K resistor (R3)

- 1 spst switch (S1)

- 1 dpst switch (S2-S3)

- 1 + 12 V dc supply (V<sub>cc</sub>)

- 1 12 V dc supply (V<sub>EE</sub>)

- 1 11/2 V size-C cell (B1)

### **Test Procedure**

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to zero, set up the test circuit as shown in Fig. 2-20.

- 2. Close switch S2-S3.

- 3. Close switch S1, and adjust potentiometer R1 to increase slowly input signal V<sub>i</sub> (as indicated by meter M1).

- Continue to increase V<sub>1</sub> while observing the deflection of meter M2 (output-signal voltage V<sub>0</sub>).

- 5. Increase  $V_1$  to the point at which output voltage  $V_0$  shows no further increase, but levels off. The value of  $V_1$  at this point is the maximum input-signal voltage for the conditions dc supply =  $\pm 12$  V and R3/R2 = 10.

# Sample Result

$V_i = 1.1 V$  for  $V_o = 10 V$  (saturated) Dc input voltage range = 0-1.1 V

# EXPERIMENT 17. AC INPUT-VOLTAGE RANGE Required Equipment (Fig. 2-21)

1 741 integrated circuit 1 sine-wave generator electronic ac voltmeter/millivoltmeter (M1)

oscilloscope

0.1-μF capacitors (C1, C2)

10K resistor (R1)

100K resistor (R2)

dpst switch (S1-S2)

+15 V dc supply (V<sub>CC</sub>)

-15 V dc supply (V<sub>EE</sub>)

#### **Test Procedure**

- 1. With switch S1-S2 open, the oscilloscope off, and the generator off (with its output attenuator set to zero), set up the test circuit as shown in Fig. 2-21.

- 2. Close switch S1-S2, and switch on the generator and oscilloscope.

- 3. Set the generator to 1000 Hz.

- 4. Adjusting the attenuator, slowly increase the output of the generator to the point at which peak clipping just begins in the IC output signal, as shown by the oscilloscope.

- 5. At this point, read the corresponding input signal (V<sub>1</sub>) from meter M1. This value of V<sub>1</sub> is the upper limit of the input-voltage range for the conditions dc supply  $= \pm 15$  V and R2/R1 = 10.

#### Sample Results

$$V_i = 0.5 \text{ V ms} = 0.71 \text{ V peak} = 1.41 \text{ V peak-to-peak}$$

Fig. 2-21. Ac input-voltage range.

#### **EXPERIMENT 18. COMMON-MODE REJECTION**

#### Required Equipment (Fig. 2-22)

- 1 741 integrated circuit

- 1 sine-wave generator

- 2 electronic ac voltmeter/millivoltmeters (M1, M2)

- 1 1- $\mu$ F capacitor (C1)

- 2 0.1- $\mu$ F capacitors (C2, C3)

- 1 500-ohm resistor (R1)

- 1 dpst switch (S1-S2)

- 1 +15 V dc supply ( $V_{cc}$ )

- 1 15 V dc supply (V<sub>EE</sub>)

#### **Test Procedure**

- 1. With switch S1-S2 open and the generator off (with its output attenuator set to zero), set up the test circuit as shown in Fig. 2-22.

- 2. Close switch S1-S2, and turn on the generator.

- 3. Set the generator to 20 Hz.

- 4. Adjust the generator attenuator for two selected successive values of input-signal voltage  $V_{1b}$  as indicated by meter M1. Record these as  $V_{11}$  and  $V_{12}$ .

- 5. Read the corresponding output-signal voltages from meter M2. (This output represents the signal transmitted by the IC as a result of offset.) Record these as  $V_{o1}$  and  $V_{o2}$ .

Fig: 2-22 Common-mode rejection.

- 6. Calculate the input-signal increment:  $\Delta V_i = V_{i2} V_{i1}$ .

- 7. Calculate the output-signal increment:  $\Delta V_0 = V_{02} V_{01}$ .

- 8. Calculate the ratio  $\Delta V_1 / \Delta V_0$ . Convert the resulting value to minus decibels.

- 9. Set the generator to 10 kHz, and repeat Steps 4 through 8.

- 10. Set the generator to 100 kHz, and repeat Steps 4 through 8.

- 11. Note that V<sub>o</sub> increases with frequency, showing that commonmode rejection decreases as the frequency increases.

#### Sample Results

Common-Mode Rejection = -82.5 dB at 20 Hz -78.4 dB at 10 kHz -49.7 dB at 100 kHz

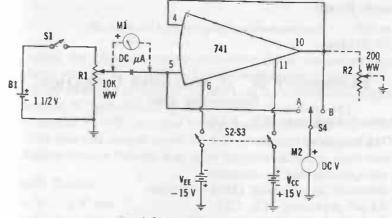

#### **EXPERIMENT 19. DC FOLLOWER OPERATION**

#### **Required Equipment (Fig. 2-23)**

- 1 741 integrated circuit

- 1 dc microammeter (M1)

- 1 dc voltmeter (M2)

- 1 10K wirewound potentiometer (R1)

- 1 200-ohm wirewound potentiometer (R2)

- 1 spst switch (S1)

- 1 dpst switch (S2-S3)

- 1 spdt switch (S4)

- 1 + 15 V dc supply (V<sub>cc</sub>)

1 -15 V dc supply ( $V_{EE}$ ) 1 1<sup>1</sup>/<sub>2</sub> V size-C cell (B1)

#### **Test Procedure**

Note that 100% feedback is provided by the connection between output terminal 10 and inverting input terminal 4.

- 1. With switches S1 and S2-S3 open, switch S4 set to position A, and potentiometer R1 set to zero, set up the test circuit as shown in Fig. 2-23.

- 2. Close switch S2-S3.

- 3. Close switch S1, and set potentiometer R1 for a convenient value of input-signal voltage V<sub>i</sub>, as indicated by voltmeter M2.

- 4. Throw switch S4 to position B, and read corresponding output voltage  $V_0$  from voltmeter M2. Note that  $V_0$  has the same value as  $V_1$  and the same polarity.

- 5. Calculate the voltage gain:  $A = V_0/V_1 = 1$ .

- 6. Repeat Steps 3 through 5 at a number of selected values of input voltage V<sub>i</sub>.

- Temporarily insert the dc microammeter as shown by dash lines. Note that the input-signal current is scarcely discernible at any of the V<sub>i</sub> values.

- 8. Temporarily connect 200-ohm potentiometer R2 from output terminal 10 to ground, as shown by dash lines. At any one of the output voltages (Step 4, above), adjust R2 to the point at which  $V_o$  falls to one-half its value. At this point, the IC-follower output resistance equals the R2 setting.

#### Sample Results

A = 1.0R<sub>o</sub> = 30 ohms

### EXPERIMENT 20. AC FOLLOWER OPERATION Noninverting Type

### Required Equipment (Fig. 2-24)

741 integrated circuit

sine-wave generator

voltage-calibrated oscilloscope

electronic ac voltmeter (M1)—optional

0.1-μF capacitors (C1, C2)

dpst switch (S1-S2)

1 spdt switch (S3) 1 +15 V dc supply ( $V_{cc}$ ) 1 -15 V dc supply ( $V_{EE}$ )

#### **Test Procedure**

- 1. With switch S1-S2 open, switch S3 set to position B, the oscilloscope and generator off, and the generator output attenuator set to zero, set up the test circuit as shown in Fig. 2-24.

- 2. Set the generator to 1000 Hz.

- 3. Close switch S1-S2, switch on the generator, and switch on the oscilloscope.

Fig. 2-24. Ac follower operation (noninverting).

- 4. Adjust the generator output attenuator for a convenient inputsignal voltage, V<sub>b</sub> as indicated by the oscilloscope or meter M1.

- 5. Throw switch S3 to position A, and read the corresponding output voltage, V<sub>o</sub>, as indicated by the oscilloscope or meter M1.

- 6. Note that  $V_0 = V_i$ , and that voltage amplification  $A = V_0/V_i = 1$ . Note also that output signal  $V_0$  is in phase with input voltage  $V_{i_i}$ .

- 7. Repeat Steps 4 through 6 at other frequencies.

#### Sample Results

$V_o = V_1 = 3 V \text{ rms}$ A = V<sub>o</sub>/V<sub>1</sub> = 1.0<sup>o</sup>

#### **Inverting** Type

Since the output-signal polarity here is the opposite of the inputsignal polarity, this circuit (Fig. 2-25) might not be regarded as a follower at all, but simply as an inverting amplifier with unity gain.

### Required Equipment (Fig. 2-25)

741 integrated circuit

sine-wave generator

voltage-calibrated oscilloscope

electronic ac voltmeter (M1)—optional

0.1-μF capacitors (C1, C2)

10K resistors (R1, R2)

dpst switch (S1-S2)

spdt switch (S3)

+15 V dc supply (V<sub>CC</sub>)

-15 V dc supply (V<sub>EE</sub>)

#### **Test Procedure**

- 1. With switch S1-S2 open, switch S3 set to position B, the oscilloscope and generator off, and the generator output attenuator set to zero, set up the test circuit as shown in Fig. 2-25.

- 2. Set the generator to 1000 Hz.

- 3. Close switch S1-S2, and switch on the generator and oscilloscope.

- 4. Adjust the generator output attenuator for a convenient inputsignal voltage, V<sub>1</sub>, as indicated by the oscilloscope or meter M1.

- 5. Throw switch S3 to position A, and read the corresponding outputsignal voltage, V<sub>0</sub>, as indicated by the oscilloscope or meter M1.

- 6. Note that  $V_o = V_i$ , and that voltage amplification  $A = V_o/V_i = 1$ . Note also that  $V_o$  is 180° out of phase with  $V_i$ .

- 7. Repeat Steps 4 through 6 at other frequencies.

#### Sample Results

$V_o = V_i = 2.1 V rms$ A =  $V_o/V_i = 1.0$

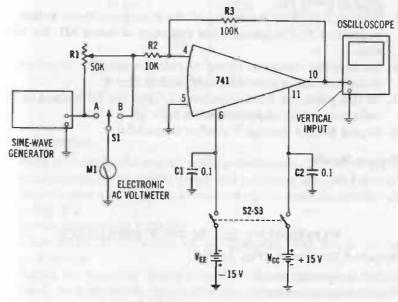

## **EXPERIMENT 21. INPUT IMPEDANCE**

# Required Equipment (Fig. 2-26)

1 741 integrated circuit 1 sine-wave generator

Fig. 2-25. Ac follower operation (inverting).

1 voltage-calibrated oscilloscope 1 electronic ac voltmeter (M1) 2 0.1- $\mu$ F capacitors (C1, C2) 1 50K potentiometer (R1) 1 10K resistor (R2) 1 100K resistor (R3) 1 spdt switch (S1) 1 dpst switch (S2-S3) 1 +15 V dc supply (V<sub>CC</sub>) 1 -15 V dc supply (V<sub>EE</sub>)

#### **Test Procedure**

- 1. With switch S1 set to position A, switch S2-S3 open, potentiometer R1 set to zero, the oscilloscope and generator off, and the generator output attenuator set to zero, set up the test circuit as shown in Fig. 2-26.

- 2. Set the generator to 1000 Hz.

- 3. Close switch S2-S3, switch on the generator, and switch on the oscilloscope.

- 4. Adjust the generator output attenuator for maximum undistorted output signal, as indicated by the oscilloscope. Note the reading  $(V_i)$  of meter M1.

- 5. Without disturbing the setting of the attenuator, throw switch S1 to position B. This changes the deflection of meter M1, but only slightly.

- 6. Increase the resistance setting of potentiometer R1 to reduce  $V_1$  to one-half the original value obtained in Step 4.

- 7. At this point, the input impedance  $(Z_i)$  of the IC is equal to the resistance setting of potentiometer R1.

- 8. Repeat Steps 4 through 7 at other frequencies.

#### Sample Results

$V_i = 0.3 V \text{ rms}$  $Z_i = 5000 \text{ ohms}$

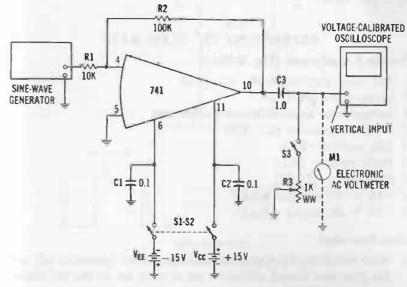

#### **EXPERIMENT 22. OUTPUT IMPEDANCE**

Required Equipment (Fig. 2-27)

- 1 741 integrated circuit

- 1 sine-wave generator

- 1 voltage-calibrated oscilloscope

1 electronic ac voltmeter (M1)—optional 2  $0.1-\mu F$  capacitors (C1, C2) 1  $1.0-\mu F$  capacitor (C3) 1 10K resistor (R1) 1 100K resistor (R2) 1 1K wirewound potentiometer (R3) 1 dpst switch (S1-S2) 1 spst switch (S3) 1 +15 V dc supply (V<sub>CC</sub>) 1 -15 V dc supply (V<sub>EE</sub>)

#### **Test Procedure**

- 1. With switches S1-S2 and S3 open, potentiometer R3 set to maximum resistance, the oscilloscope and generator off, and the generator output attenuator set to zero, set up the test circuit as shown in Fig. 2-27.

- 2. Set the generator to 1000 Hz.

- 3. Close switch S1-S2, switch on the generator, and switch on the oscilloscope.

- 4. Adjust the generator output attenuator for maximum undistorted signal, as indicated by the oscilloscope. Read the value of IC output-signal voltage  $(V_0)$  from the oscilloscope or from meter M1.

- .5. Close switch S3. Note that this disturbs the deflection of meter M1 or the height of the pattern on the oscilloscope screen.

- 6. Adjust potentiometer R3 to restore output voltage V<sub>o</sub> to its original value obtained in Step 4.

- 7. At this point, output impedance  $Z_o$  is equal to the resistance setting of potentiometer R3.

- 8. Repeat Steps 4 through 7 at other frequencies.

#### Sample Results

- $V_o = 3 V rms$

- $Z_o = 250$  ohms

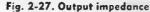

#### **EXPERIMENT 23. SLEW RATE**

#### Required Equipment (Fig. 2-28A)

- 1 741 integrated circuit

- 1 square-wave generator

- 1 voltage- and time-calibrated oscilloscope

- 2 0.1-µF capacitors (C1, C2)

- 1 10K resistor (R1)

- 1 100K resistor (R2)

- 1 dpst switch (S1-S2)

- 1 + 15 V dc supply (V<sub>cc</sub>)

- 1 -15 V dc supply (V\_{\rm EE})

#### **Test Procedure**

- 1. With switch S1-S2 open, the oscilloscope and generator off, and the generator output attenuator set to zero, set up the test circuit as shown in Fig. 2-28A.

- 2. Set the generator to 20 Hz.

- 3. Close switch S1-S2, and switch on the generator and oscilloscope.

- 4. Increase the setting of the generator attenuator, and adjust the oscilloscope controls for a single square wave on the screen.

- 5. Continue to increase the output of the generator until the square wave distorts, as shown by the dash lines in Fig. 2-28B.

- 6. As shown in Fig. 2-28B, from the calibrated screen of the oscilloscope read IC output voltage  $\Delta E$  in volts and rise time  $\Delta t$  in microseconds.

- 7. Calculate the slew rate:  $SR = \Delta E / \Delta t$  volts per microsecond. Correct, if desired, by allowing for the inherent rise times of the generator and oscilloscope.

Sample Result

$SR = 0.5 V/\mu s$

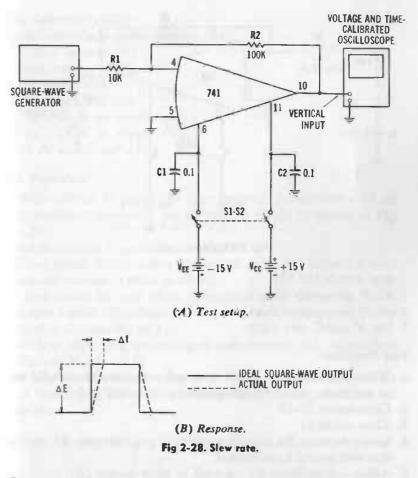

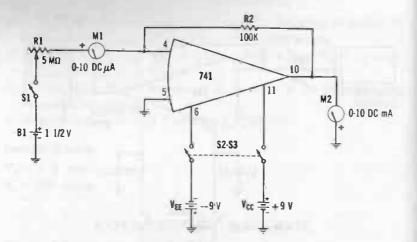

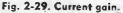

**EXPERIMENT 24. CURRENT GAIN**

#### **Required Equipment (Fig. 2-29)**

- 741 integrated circuit

dc microammeter (M1)

dc milliammeter (M2)

5-megohm potentiometer (R1)

100K resistor (R2)

- 1 spst switch (S1)

1 dpst switch (S2-S3)

- 1 + 9 V dc supply (V<sub>cc</sub>)

- $1 9 V dc supply (V_{EE})$

- 1 11/2 V size-C cell (B1)

#### **Test Procedure**

- 1. With switches S1 and S2-S3 open and with potentiometer R1 set to maximum, set up the test circuit as shown in Fig. 2-29.

- 2. Close switch S2-S3.

- 3. Close switch S1.

- 4. Slowly decrease the resistance setting of potentiometer R1, noting that both meters begin to read.

- 5. Adjust potentiometer R1 for 1  $\mu$ A of input current (I<sub>1</sub>).

- 6. Note the corresponding output current (I<sub>o</sub>) indicated by meter M2.

- 7. Calculate the current gain:  $A_i = I_0/I_i$ .

#### **Typical Results**

$I_i = 1 \ \mu A$ ,  $I_o = 4 \ mA = 4000 \ \mu A$ ;  $A_i = 4000/1 = 4000$

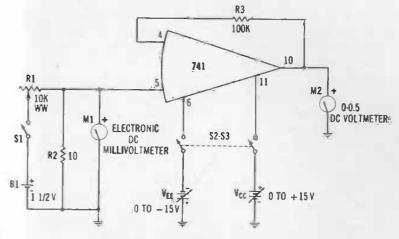

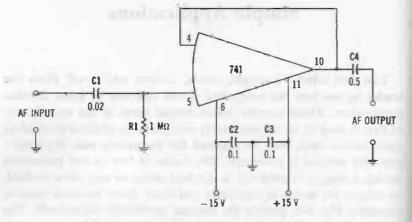

# EXPERIMENT 25. POWER-SUPPLY REJECTION RATIO

# Required Equipment (Fig. 2-30)

- 1 741 integrated circuit

- 1 electronic dc millivoltmeter (M1)

1 dc voltmeter (M2) 1 10K wirewound potentiometer (R1) 1 10-ohm resistor (R2) 1 100K resistor (R3) 1 spst switch (S1) 1 dpst switch (S2-S3) 1 0 to +15 V dc supply ( $V_{CC}$ ) 1 0 to -15 V dc supply ( $V_{EE}$ )

1 11/2 V size-C cell (B1)

#### **Test Procedure**

- 4. With switches S1 and S2-S3 open and with potentiometer R1 set to maximum resistance, set up the test circuit as shown in Fig. 2-30.

- 2. Set dc supplies  $V_{CC}$  and  $V_{EE}$  each to 15 V.

- 3. Close switch S2-S3, noting that output meter M2 deflects a smallamount because of offset in the IC.

- 4. Close switch S1, and adjust potentiometer R1 to reduce the IC, output (meter M2 deflection) to zero. At this point, record the deflection of meter M1 as  $V_{\rm H}$ .

- 5. Without disturbing the setting of potentiometer R1, reduce both  $V_{cc}$  and  $V_{EE}$  to 10 V.

- 6. If Step 5 causes meter M2 again to read, adjust potentiometer R1 to re-null M2. Record the corresponding reading of meter M1 as  $V_{12}$ .

- 7. Calculate  $\Delta V_i = V_{i2} V_{i1}$ . Record the result in microvolts.

- 8. Calculate the power-supply rejection ratio:  $PSRR = \Delta V_t / \Delta V_s$ , where  $\Delta V_s =$  change in supply voltage (in this case, 15 - 10 = 5 V).

- 9. Repeat Steps 2 through 8, first holding  $V_{cc}$  constant and changing  $V_{EE}$ , then by holding  $V_{EE}$  constant and changing  $V_{cc}$ . Note which of these supply-voltage changes affects the IC most.

#### Sample Results

$V_{i1} = 1 \text{ mV}$   $V_{i2} = 1.25 \text{ mV}$   $\Delta V_i = 0.25 \text{ mV} = 250 \mu V$   $\Delta V_s = 15 - 10 = 5 V$ PSRR = 250/5 = 50  $\mu V$  per volt

# PART 3

# **Simple Applications**

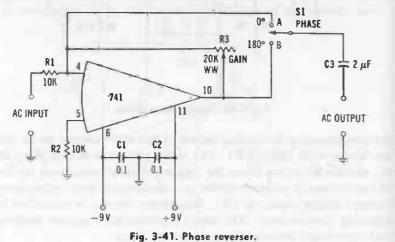

# Simple Applications

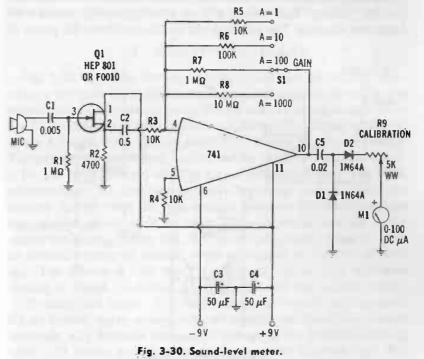

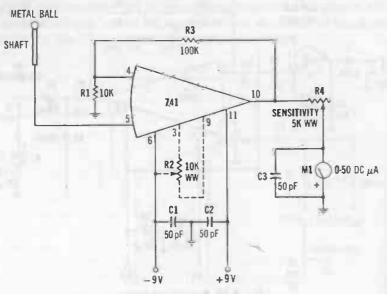

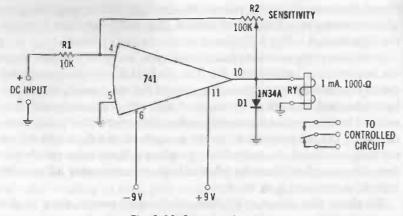

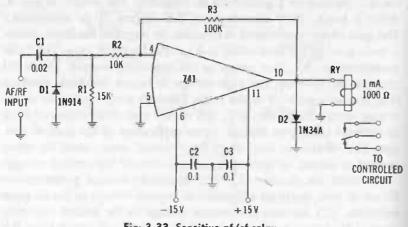

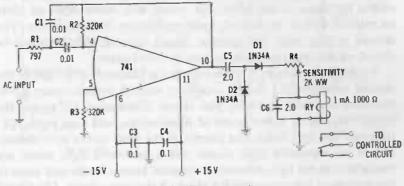

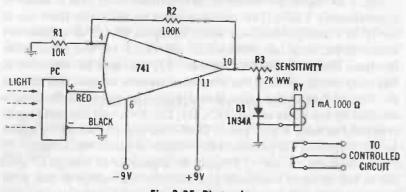

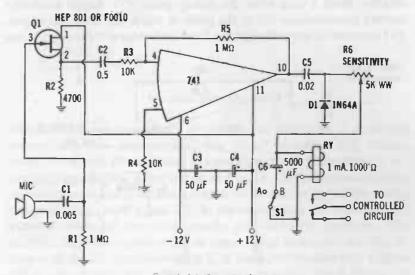

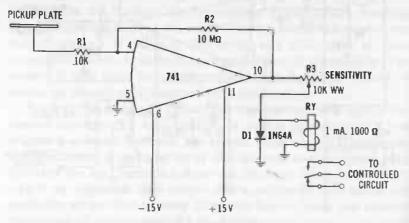

This part offers 41 simple, one-IC circuits which will allow the reader to see how the integrated circuit operates in some familiar applications. These circuits, which extend some of the experiments of Part 2, may be set up reasonably easily and, in addition to yielding performance data, may be retained for permanent use. No special assembly method is necessary. The reader is free to use permanent wiring, a plug-in breadboard, a clip-lead setup, or any other method, so long as the wiring is stationary and short. Some sensitive circuits, especially Fig. 3-4, require the shortest practicable input leads. The pointers given at the beginning of Part 2 apply as well here.

The dc drain of these circuits is very low, and the dc supplies may be either batteries or *low-ripple* ac-operated units. Dual power supplies are required in all circuits except Figs. 3-7 and 3-12, which operate with a single supply.

For testing circuit performance, use the same instruments and equipment employed in the experiments in Part 2.

Except where shown otherwise in the schematics or texte

- 1. All resistances are in ohms.

- 2. All fixed resistors are 1/4-watt composition, 5% tolerance.

- 3. All potentiometers are composition, except where labeled ww (wirewound).

- 4. All capacitances are in microfarads ( $\mu$ F).

- 5. All capacitors are low-voltage nonelectrolytic.

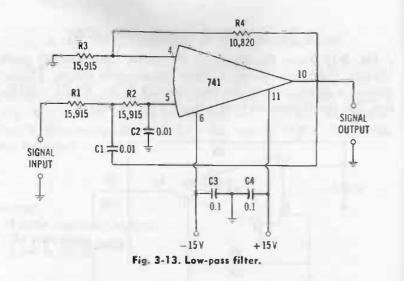

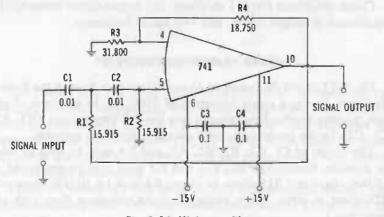

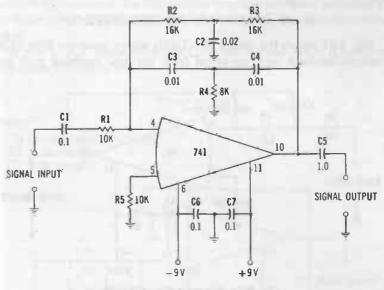

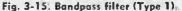

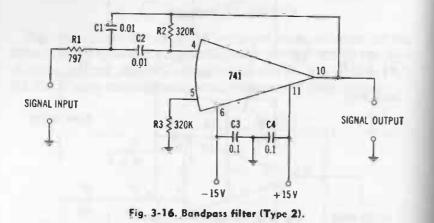

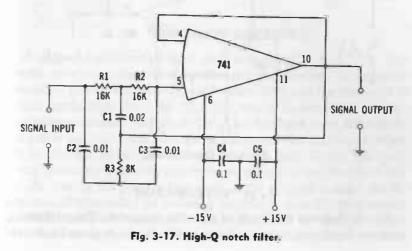

- 6. Capacitors in frequency-determining networks-as in Figs. 3-10,

3-13, 3-14, 3-15, 3-16, and 3-17—are high-Q, close-tolerance mica or ceramic, except where a desired low-frequency operation requires high capacitances that are out of the mica range.

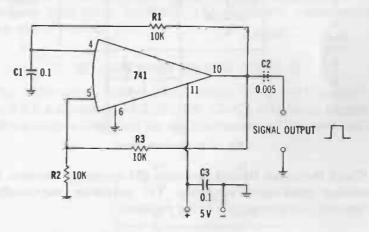

#### 3.1 VOLTAGE-FOLLOWER AMPLIFIER

Fig. 3-1 shows the circuit of an ac voltage follower. This setup is equivalent to the vacuum-tube cathode follower, bipolar-transistor emitter follower, and FET source follower. Unlike the latter circuits, however, the IC follower gives a gain of exactly 1. Followers are very handy for transformerless up/down impedance transformation

Fig. 3-1. Voltage-follower amplifier.

throughout electronics. In Fig. 3-1, 100% inverse feedback is provided by the direct connection between output terminal 10 and invertinginput terminal 4.

Check the circuit for (1) dc drain, (2) maximum input-signal amplitude, (3) maximum output-voltage swing, (4) input impedance, (5) output impedance, (6) voltage gain, (7) frequency response, (8) output/input phase, and (9) total harmonic distortion.

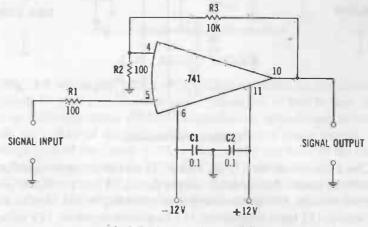

#### 3.2 GAIN-OF-10 AUDIO AMPLIFIER

Fig. 3-2 shows the circuit of an audio amplifier having a voltage gain of 10. Here, the gain is set by negative feedback and is determined by the ratio of the 100K feedback resistance to the 10K input resistance ( $A_r = R2/R1$ ). This unit is usable either as a main ampli-

Fig. 3-2. Gain-of-10 audio amplifier.

fier or as a preamplifier where a stable amplification of 20 dB is, desired.

Check the circuit for (1) dc drain, (2) maximum input-signal amplitude, (3) maximum output-voltage swing, (4) input impedance, (5) output impedance, (6) voltage gain, (7) frequency response, (8) output/input phase, and (9) total harmonic distortion.

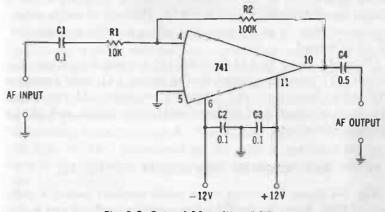

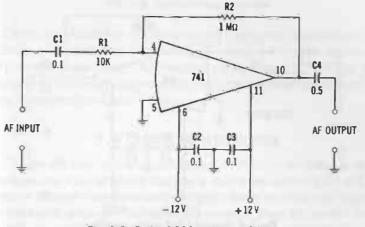

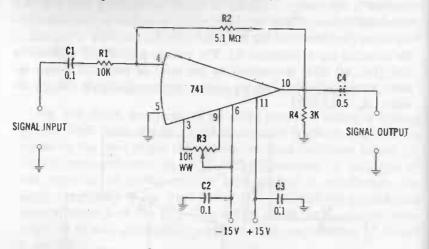

#### 3.3 GAIN-OF-100 AUDIO AMPLIFIER

Fig. 3-3 shows the circuit of an audio amplifier having a voltage gain of 100. Here, the gain is set by negative feedback and is deter-

mined by the ratio of the 1-megohm feedback resistance to the 10kilohm input resistance ( $A_v = R2/R1$ ). This unit is usable either as a main amplifier or as a preamplifier where a stable amplification of 40 dB is desired.

Check the circuit for (1) dc drain, (2) maximum input-signal amplitude, (3) maximum output-voltage swing, (4) input impedance, (5) output impedance, (6) frequency response, (7) voltage gain, (8) phase relationship of the input and output signals, and (9) total harmonic distortion.

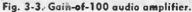

# 3.4 GAIN-OF-1000 AUDIO AMPLIFIER

Fig. 3-4 shows the circuit of an audio amplifier having a voltage gain of 1000. Here, the gain is set by negative feedback and is determined by the ratio of the 10-megohm feedback resistance to the 10kilohm input resistance ( $A_v = R2/R1$ ). Because of the high gain of this amplifier, all wiring must be kept as short as practicable; this applies especially to the input circuit (C1, R1, and the ground lead from terminal 5 of the IC). This unit is usable as a sensitive main amplifier or as a preamplifier where a stable amplification of 60 dB is desired.

Check the circuit for (1) dc drain, (2) maximum input-signal amplitude, (3) maximum output-voltage swing, (4) input impedance, (5) output impedance, (6) frequency response, (7) voltage gain, (8) phase relationship of the input and output signals, and (9) total harmonic distortion.

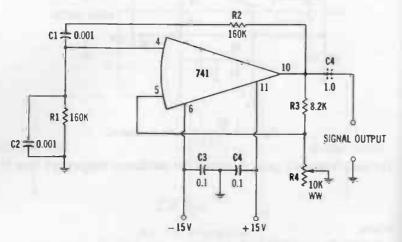

# **3.5** NONINVERTING AMPLIFIER

In the amplifiers described in Sections 3.2, 3.3, and 3.4, the output signal is out of phase with the input signal. This results from applying the input signal to the inverting input terminal of the IC. The phase reversal is not always desirable in some applications, and Fig. 3-5 shows the remedy. Here, the input signal is applied to the *noninverting* input (terminal 5 of the IC), and only the feedback is applied to the inverting input (terminal 4). The voltage gain of this amplifier is 100 (i.e., 40 dB), determined by the ratio of the 10,000-ohm resistor to the 100-ohm resistor in the negative-feedback voltage divider ( $A_v = R3/R2$ ).

Fig. 3-5. Noninverting amplifier.

Check the circuit for (1) dc drain, (2) maximum input-signal amplitude, (3) maximum output-voltage swing, (4) input impedance, (5) output impedance, (6) frequency response, (7) voltage gain, (8) phase relationship between the input and output signals, and (9) total harmonic distortion.

## 3.6 LIMITER AMPLIFIER

The 54-dB gain of the circuit shown in Fig. 3-6 is useful in many applications. This amplifier receives a sine-wave input signal and delivers a clipped-sine-wave output signal; both positive and negative output-signal peaks are limited in this manner. Thus, the circuit limits, as well as amplifies. In this circuit, R3 is an offset-null potentiometer which is set for equal clipping of the positive and negative peaks of the output signal. Output capacitor C4 is needed only when strict ac coupling is demanded. The voltage gain of the amplifier is 510, determined by the ratio of the 5.1-megohm feedback resistance to the 10,000-ohm input resistance ( $A_v = R2/R1$ ).

Fig. 3-6. Limiter amplifier.

Check the circuit for (1) dc drain, (2) maximum input-signal amplitude for good clipping of the output signal, (3) output-signal peak clipped voltage, (4) positive/negative symmetry in the clipped output signal, (5) input impedance, (6) frequency response, (7) voltage gain, and (8) input/output phase.

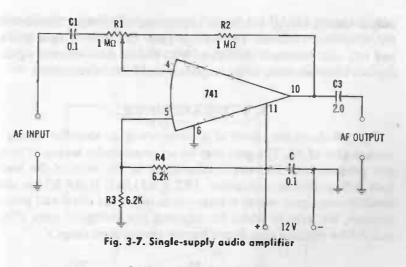

# 3.7 SINGLE-SUPPLY AUDIO AMPLIFIER

Fig. 3-7 shows the circuit of an audio amplifier operated from a single 12-volt dc supply. This circuit employs both negative feedback (through resistors R1 and R2) and positive feedback (through resistors R3 and R4). Potentiometer R1 also serves as a gain control for the amplifier.

Check the circuit for (1) dc drain; and at selected settings of gain control RI, check (2) maximum input-signal amplitude, (3) maximum output-voltage swing, (4) input impedance, (5) output impedance, (6) frequency response, (7) voltage gain, (8) phase relationship between the input signal and output signal, and (9) total harmonic distortion.

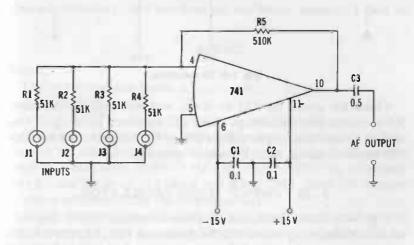

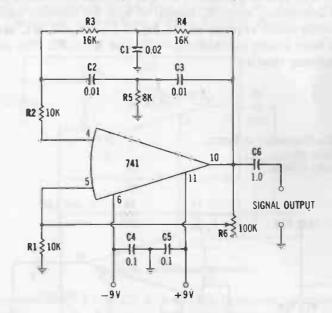

### 3.8 AUDIO MIXER

Fig. 3-8 shows the circuit of a four-input audio mixer. Jacks J1 through J4 may accommodate any combination of two to four similar or dissimilar signal sources (microphones, reproducers, transducers, etc.). Any of the jacks will accommodate a single source. The voltage gain of the circuit is 10, determined by the ratio of the 510K feedback resistance to any of the 51K input resistances.

Check the circuit for (1) dc drain; and for each input (J1 through J4), check (2) maximum input-signal amplitude, (3) maximum

Fig. 3-8. Audio mižer.

output-voltage swing, (4) input impedance, (5) output impedance, (6) frequency response, (7) voltage gain, (8) output/input phase, and (9) total harmonic distortion. With two or more selected signals applied simultaneously to the amplifier, check the mixer action.

#### **3.9 DC AMPLIFIER**

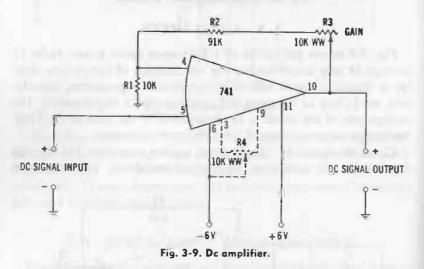

Fig. 3-9 shows the circuit of a noninverting dc amplifier having a voltage gain of 10. The gain may be set precisely by means of trimmer potentiometer R3, and is determined by the ratio of the feedback voltage-divider resistances: (R2 + R3)/R1. If the IC has discernible zero-signal output voltage due to offset, the offset-null potentiometer, R4, may be added for adjusting this voltage to zero. (This null will be effective only over a narrow temperature range.)

Check the circuit for (1) dc drain; and with gain potentiometer R3 at various selected settings, check (2) maximum input-signal voltage, (3) maximum output-voltage swing, (4) output/input linearity, (5) input resistance, and (6) output resistance.

# 3.10 TWIN-T AUDIO OSCILLATOR

Fig. 3-10 shows the circuit of a low-distortion, 1-kHz sine-wave oscillator employing a twin-T RC null network (C1, C2, C3, R3, R4, R5) in the negative-feedback loop as the frequency-determining sec-

tion. Positive feedback is provided through the R1-R6 voltage divider and causes the circuit to oscillate. Potentiometer R6 sets the intensity of positive feedback and thus is the oscillation control.

In the twin-T network,  $C2 = C3 = \frac{1}{2}C1$ , and R3 = R4 = 2R5.

Fig. 3-10. Twin-T audio-oscillator.

The null frequency (and therefore the oscillation frequency) then is:

$$\mathbf{f} = \frac{1}{2\pi R 3 C 2}$$

where,

f is the frequency in hertz, R3 is in ohms, C2 is in farads.

The reader may use these relationships to select resistors and capacitors for other frequencies. The values given in Fig. 3-10 actually result in a frequency of 994.7 Hz. For exactly 1000 Hz, trim resistors R3 and R4 to 15,915 ohms, and R5 to 7957 ohms. (It is easier to prune resistance than high capacitance.)

Check the circuit for (1) dc drain, (2) signal-output voltage, (3) signal frequency, and (4) total harmonic distortion (adjust R6 for lowest distortion and easiest starting of oscillation).

# 3.11 WIEN-BRIDGE AUDIO OSCILLATOR

The low-distortion, 1-kHz sine-wave oscillator shown in Fig. 3-11 employs only four components (C1, C2, R1, R2) in its RC-type frequency-determining network, compared with the previous oscillator (Fig. 3-10) which requires six. In Fig. 3-11, C1, C2, R1, and R2 form a Wien bridge in which C1 = C2, and R1 = R2. The oscillation frequency then is:

$$f = \frac{1}{2\pi R 1 C 1}$$

where,

f is the frequency in hertz, R1 is in ohms, C1 is in farads.

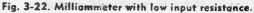

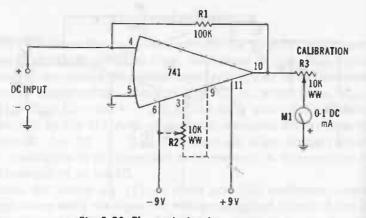

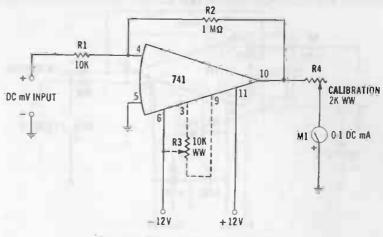

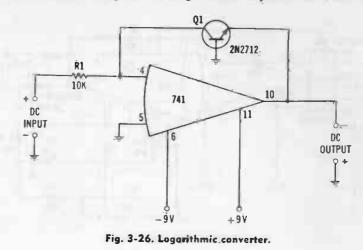

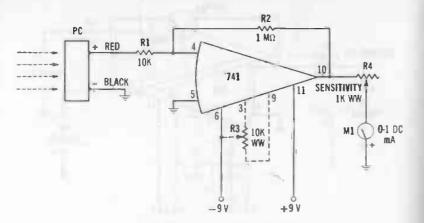

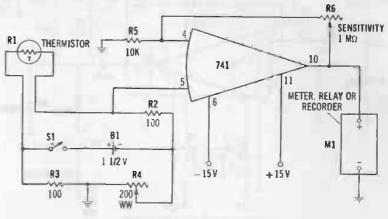

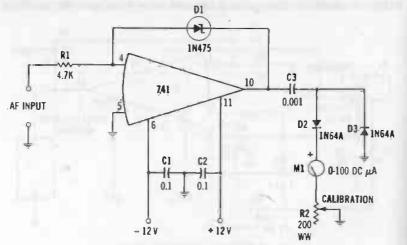

Fig. 3-11. Wien-bridge audio oscillator.