KCA LABORALCRIES

A selection of papers describing research and development work of the Radio Corporation of America as it applies to the theory, fabrication, and application of transistors

**MARCH** 1956

Published by RCA LABORATORIES Princeton, N. J. © 1956 by Radio Corporation of America All Rights Reserved

.

Printed in U. S. A.

#### PREFACE

The Transistor and related semiconductor devices are revolutionizing many aspects of electronics with amazing rapidity Within the Radio Corporation of America, there has been such extensive research and development work on semiconductors, transistors, and their applications that scientific and engineering reports have accumulated in an unprecedented manner. Only a part of this work has appeared in the technical literature.

Because of the high quality and large quantity of the as-yetunpublished material available within RCA, it was concluded that the most effective method of bringing the information to the attention of those who would profit by it would be the publication of this book. It was believed that the addition of a few published papers, and abstracts of others, would help to round out the over-all picture and would considerably enhance the usefulness of the book. Accordingly, the volume is made up of 31 complete papers (496 pages) which have not been published elsewhere, 10 papers (163 pages) which have appeared in periodicals, and 46 abstracts. The papers are grouped into six sections: General, Materials and Techniques, Devices, Fluctuation Noise, Test and Measurement Equipment, and Applications. It should be noted that the word "Transistors" as used in the title is intended to include semiconductor diodes.

The publishers are indebted to the Institute of Radio Engineers and to the Institute of Physics (Great Britain) for granting permission to reproduce papers which have appeared in the journals of these organizations.

### CONTENTS

|                                                                                                                      | Page |

|----------------------------------------------------------------------------------------------------------------------|------|

| Preface                                                                                                              | ili  |

| General                                                                                                              |      |

| Basic Transistor Device Concepts                                                                                     | 1    |

| New Advances in the Junction Transistor E. W. HEROLD                                                                 | 27   |

| Materials and Techniques                                                                                             |      |

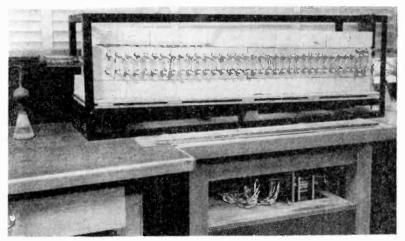

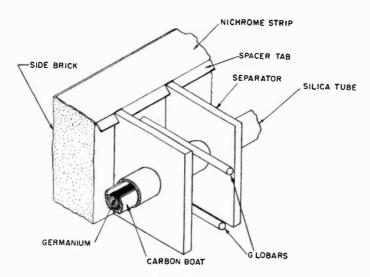

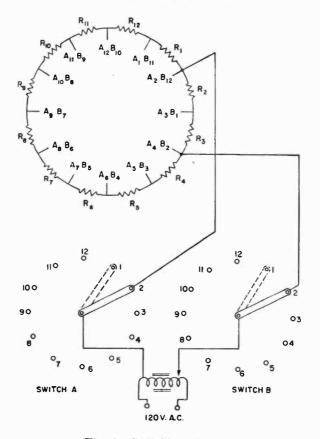

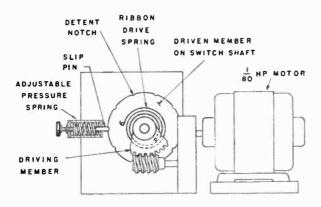

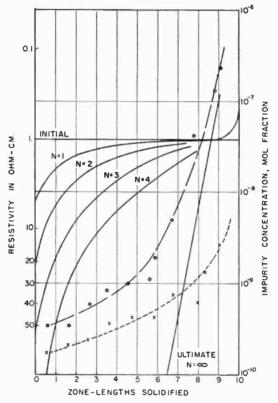

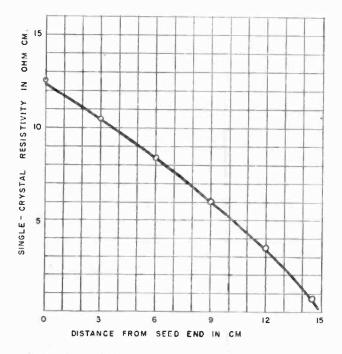

| A Switched-Zone Furnace for Germanium Purification<br>                                                               | 59   |

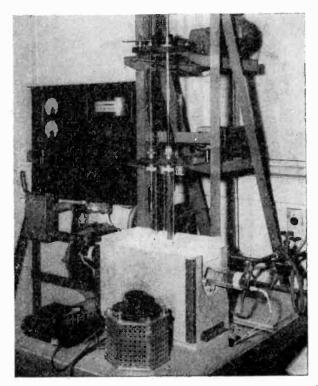

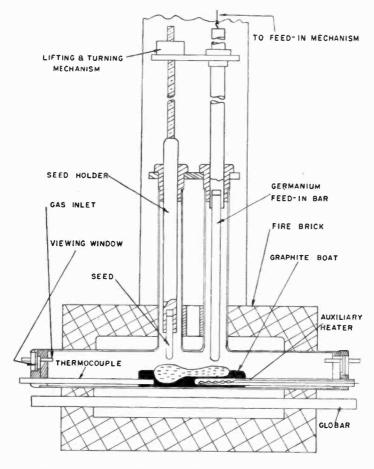

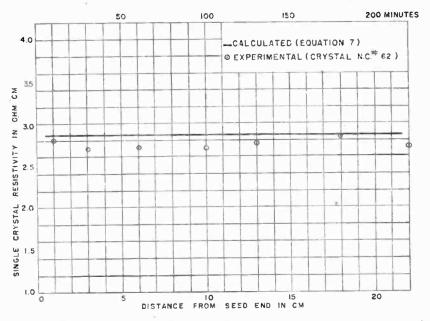

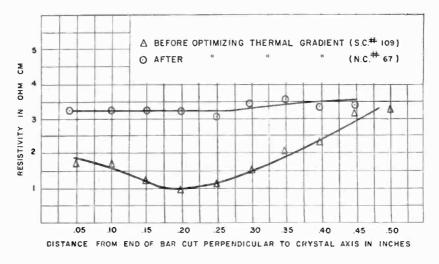

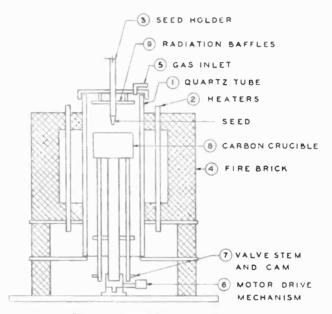

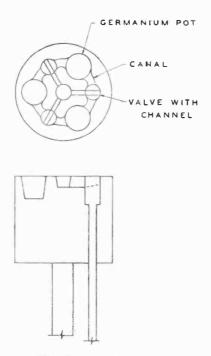

| Continuous-Process Apparatus for Growing Single-Crystal Germanium<br>H. NELSON                                       | 66   |

| The Preparation of Single and Multiple P-N Junctions in Single<br>Crystals of GermaniumA. R. MOORE                   | 77   |

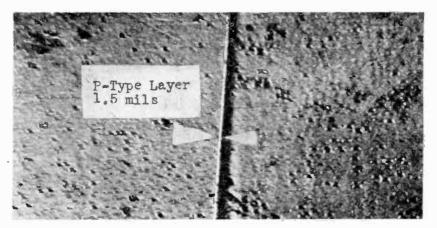

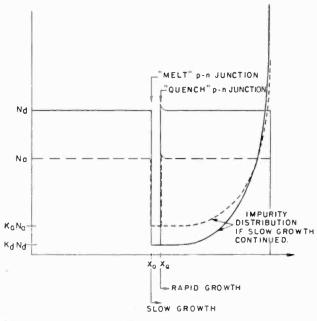

| Transistor Fabrication by the Melt-Quench ProcessJ. I. PANKOVE                                                       | 82   |

| Microscopic Examination of Germanium Crystals and Transistors<br>S. G. ELLIS                                         | 97   |

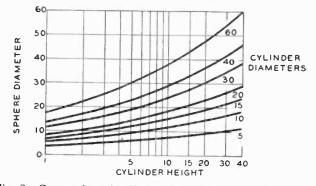

| Calculations of Alloying Depth of Indium in GermaniumL. PENSAK                                                       | 112  |

| Uniform Planar Alloy Junctions for Germanium Transistors<br>C. W. MUELLER AND N. H. DITRICK                          | 121  |

| Some Aspects of Thermal Conversion in GermaniumH. KROEMER                                                            | 132  |

| Surface Treatment of Silicon for Low Recombination Velocity<br>A. R. MOORE AND H. NELSON                             | 136  |

| Devices                                                                                                              |      |

| P-N-P Transistors Using High-Emitter-Efficiency Alloy Materials<br>L. D. ARMSTRONG, C. L. CARLSON, AND M. BENTIVEGNA | 144  |

| Recent Advances in Power Junction TransistorsB. N. SLADE                                                             | 153  |

| A Silicon N-P-N Junction Transistor by the Alloy Process H. NELSON                                                   | 172  |

| Junction Transistor Designed for Iterative Operation at Low Fre-<br>quencies                                         | 182  |

| A P-N-P Triode Alloy Junction Transistor for Radio-Frequency Am-<br>plificationC. W. MUELLER AND J. I. PANKOVE       | 189  |

| The Drift TransistorH. KROEMER                                                                                       | 202  |

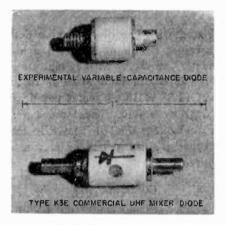

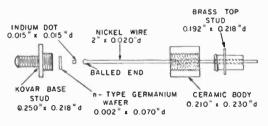

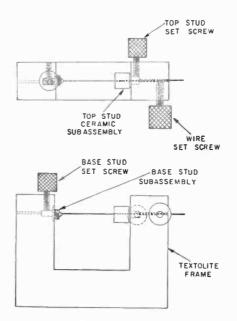

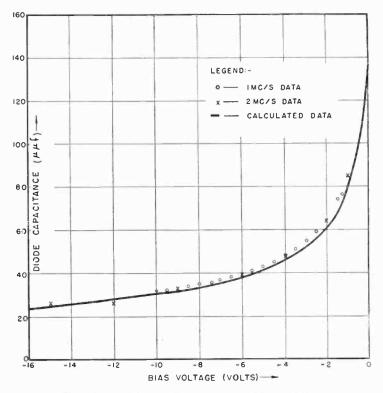

| A Variable-Capacitance Germanium Junction Diode for UHF<br>L. J. GIACOLETTO AND J. O'CONNELL                         | 221  |

| Fluctuation Noise                                                                                                    |      |

| A Determination of 1/f Noise Sources in Semiconductor Diodes and<br>TriodesW. H. FONGER                              | 239  |

The Noise Factor of Junction Transistors ......L. J. GIACOLETTO 296 Noise Considerations of P-N-P Junction Transistors..J. W. ENGLUND 309

- V ---

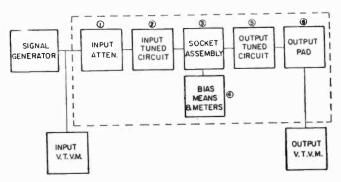

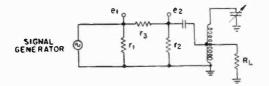

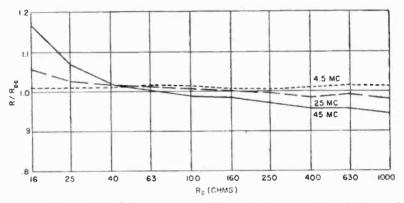

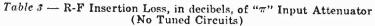

## Test and Measurement Equipment

6

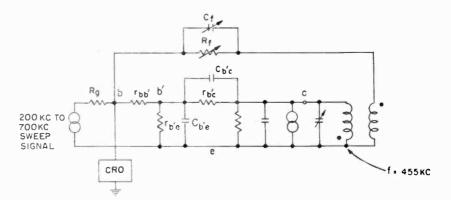

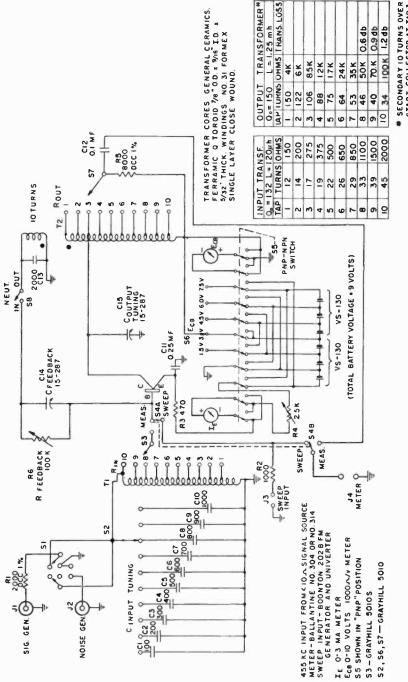

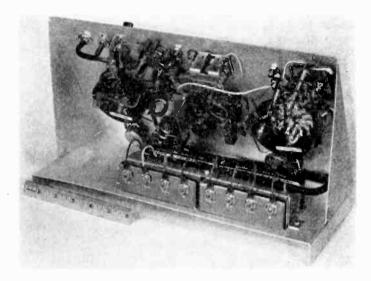

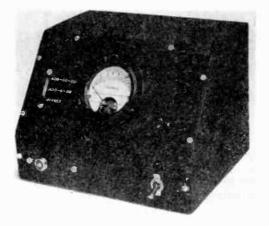

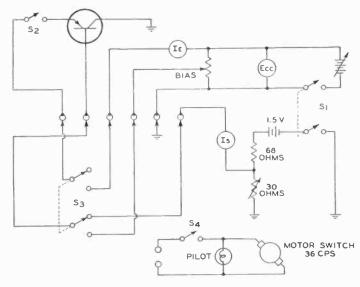

| A Test Set for Transistor Performance Measurement at 455 Kilocycles<br>D. D. Holmes, L. A. FREEDMAN, AND T. M. Scott     | 322         |

|--------------------------------------------------------------------------------------------------------------------------|-------------|

| A High-Frequency Measuring Equipment for Transistors                                                                     | 336         |

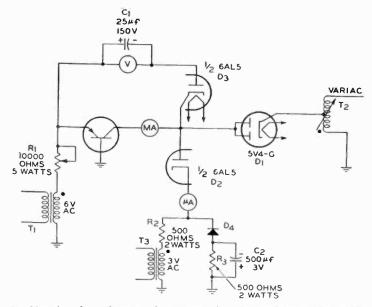

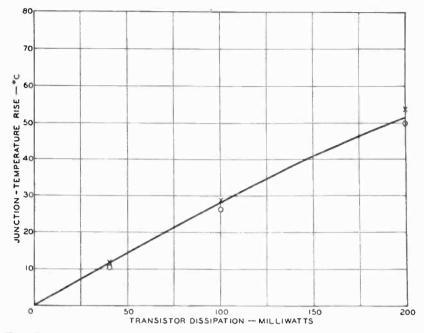

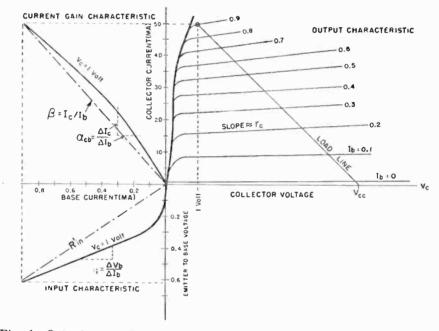

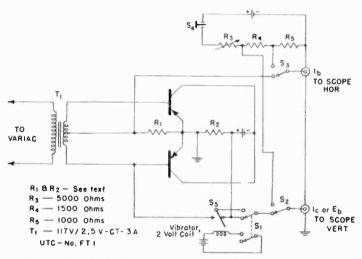

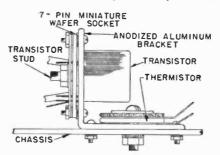

| Equipment for Measuring Junction Temperature of an Operating<br>TransistorJ. OLLENDORF AND K. E. LOOFBOURROW             | 353         |

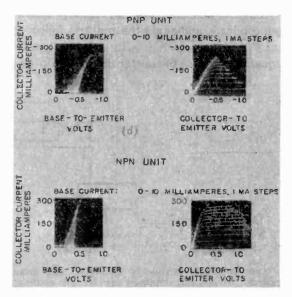

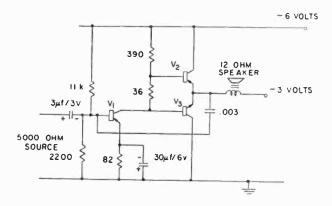

| Evaluation of Transistors for Class-B Power Amplifiers                                                                   | 361         |

| Applications                                                                                                             |             |

| Temperature Effects in Circuits Using Junction Transistors                                                               | <b>3</b> 69 |

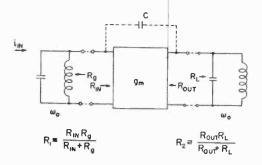

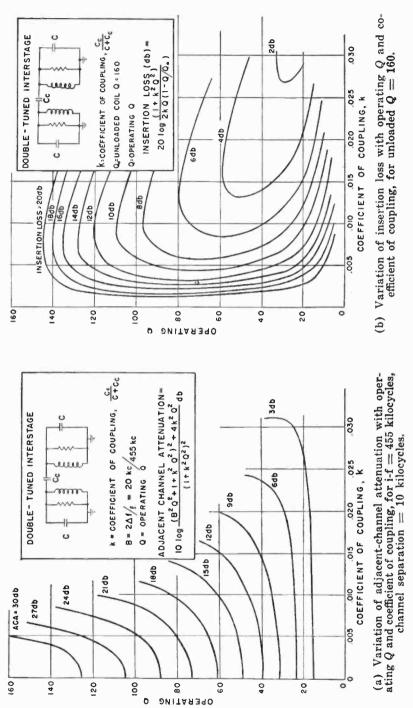

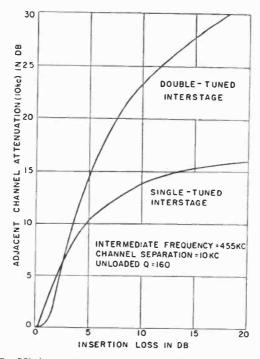

| Stability Considerations in Transistor I-F Amplifiers                                                                    | 403         |

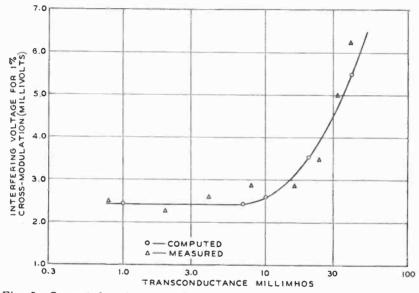

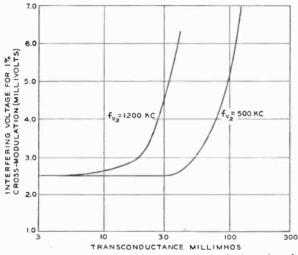

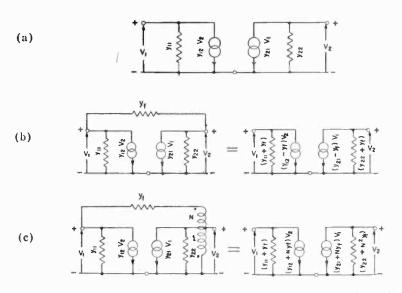

| Cross-Modulation in Transistor R-F AmplifiersD. D. HOLMES                                                                | <b>42</b> 2 |

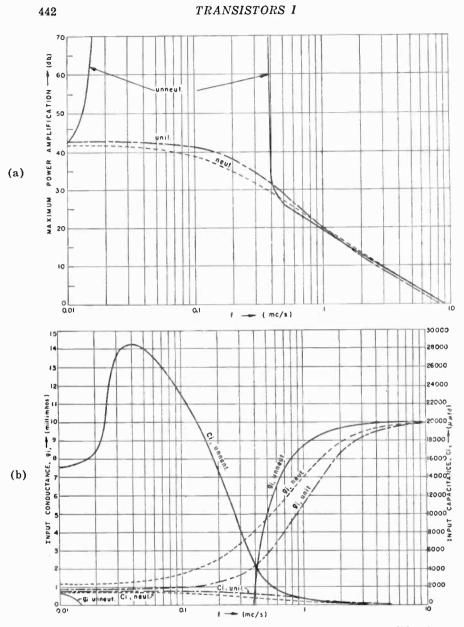

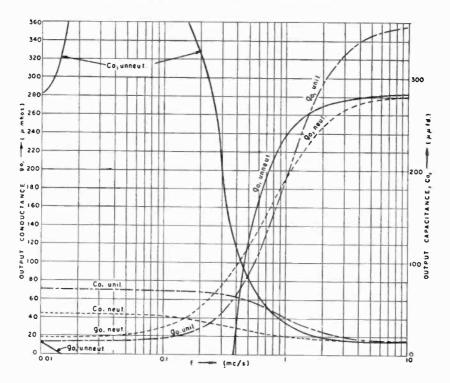

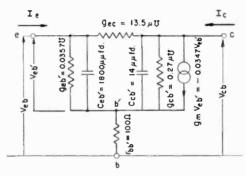

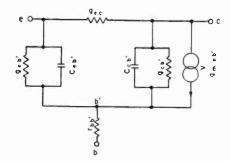

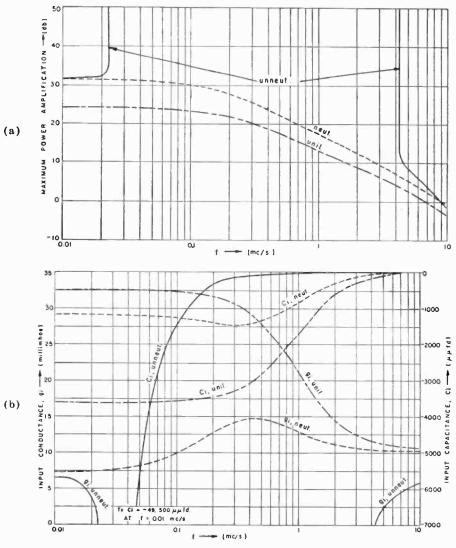

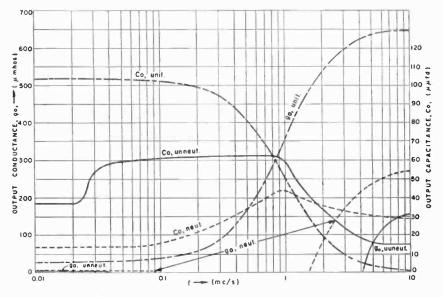

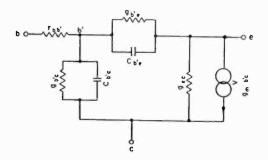

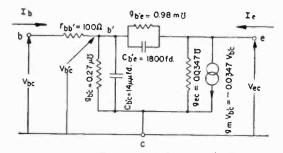

| Performance of a Radio-Frequency Alloy Junction Transistor in Dif-<br>ferent CircuitsL. J. GIACOLETTO                    | 431         |

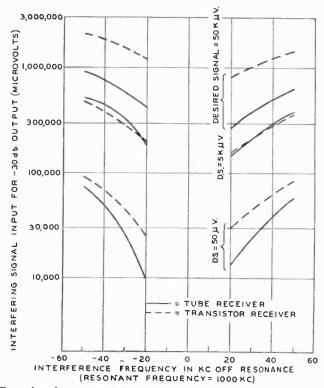

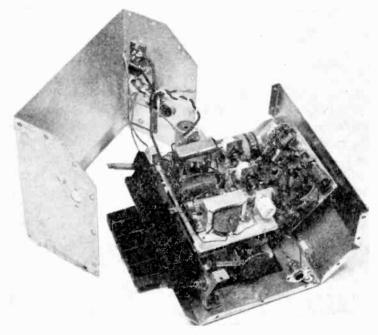

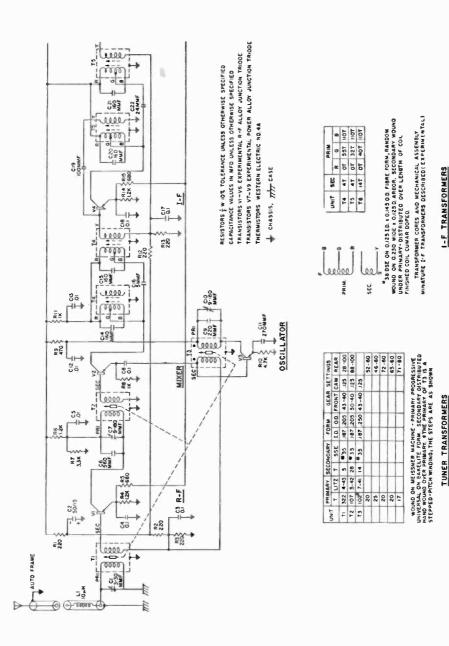

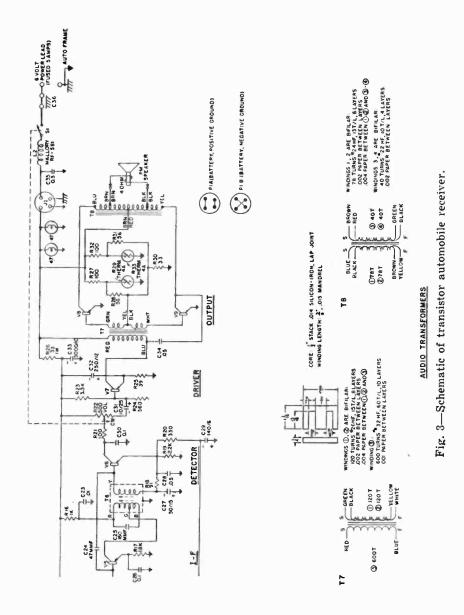

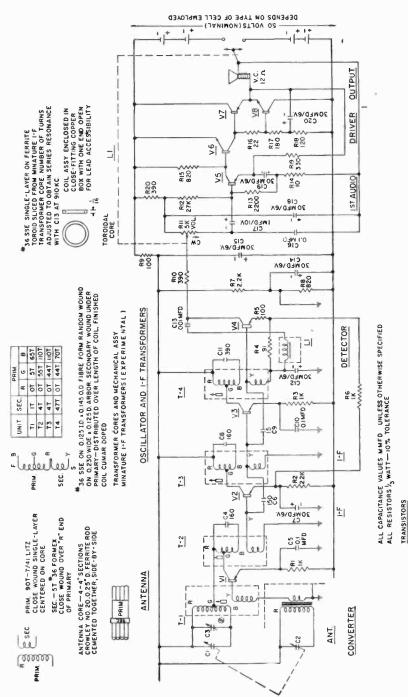

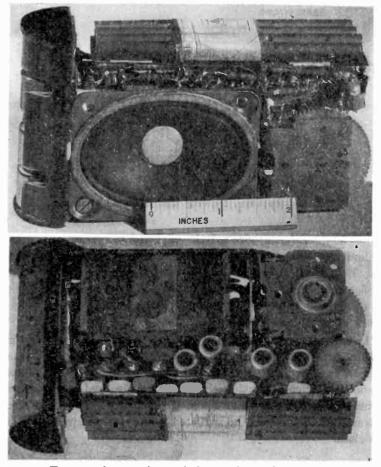

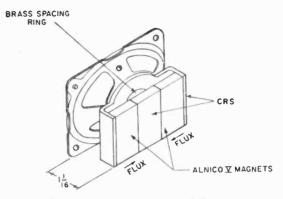

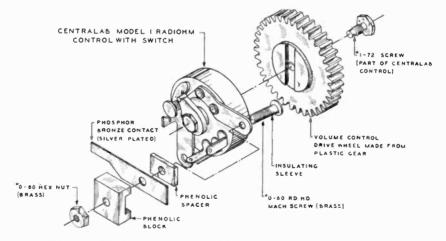

| An Experimental Automobile Receiver Employing Transistors<br>L. A. FREEDMAN, T. O. STANLEY, AND D. D. HOLMES             | 458         |

| A Developmental Pocket-Size Broadcast Receiver Employing Tran-<br>sistorsD. D. HOLMES, T. O. STANLEY, AND L. A. FREEDMAN | 477         |

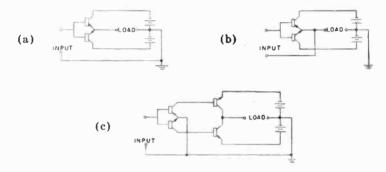

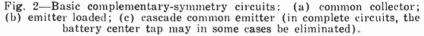

| Design Considerations in Class-B Complementary Symmetry Circuits<br>                                                     | 497         |

| Transistor Audio AmplifiersA. I. ARONSON                                                                                 | 515         |

| A 20-Watt Transistor Audio Amplifier                                                                                     | 536         |

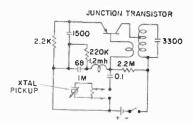

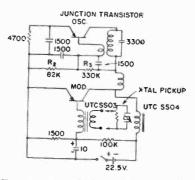

| Modulated Transistor Oscillators and Their ApplicationsH. C. LIN                                                         | 547         |

| Transistorized Sync Separator for Television Receivers                                                                   | 561         |

| Transistorized Vertical Deflection for Television Receivers                                                              | 579         |

| Automatic-Frequency Control of Television Receivers Using Junction<br>DiodesW. Y. PAN AND O. RAMANIS                     | 598         |

| Junction Transistor Switching CharacteristicsD. E. DEUITCH                                                               | 609         |

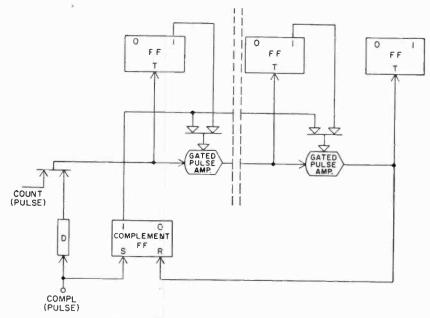

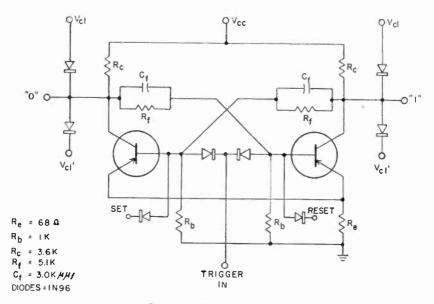

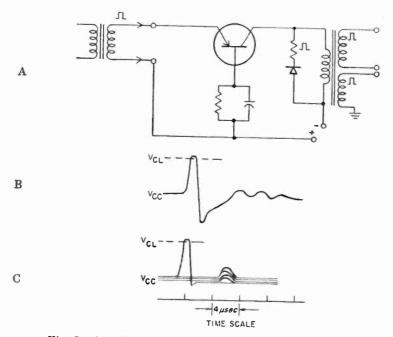

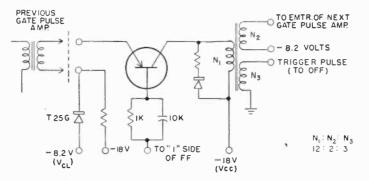

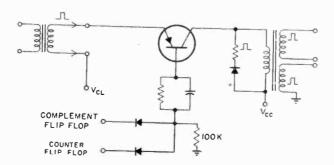

| A Novel Ring Counter Using Junction TransistorsD. E. DEUITCH                                                             | 640         |

| A Junction-Transistor Counter with High-Speed Carry<br>T. P. BOTHWELL, G. W. BOOTH, AND E. P. ENGLISH                    | 646         |

| Abstracts                                                                                                                | 661         |

|                                                                                                                          |             |

— vi —

# BASIC TRANSISTOR DEVICE CONCEPTS

#### By

#### HARWICK JOHNSON

RCA Laboratories, Princeton, N. J.

Summary—The properties of a p-n junction in a semiconductor are developed largely on the basis of physical arguments. From this conceptual point of view, the roles played by the junction barrier and by diffusion phenomena in minority carrier injection, diode conductance, transition capacitance, and diffusion capacitance are developed. This conceptual development is fortified by an elementary analysis. The utilization of these properties of a p-n junction in various transistor devices is discussed in a qualitative fashion.

#### INTRODUCTION

HIS paper considers some of the elementary device concepts which are essential to the physical understanding of the operation of transistor devices. The discussion is descriptive in nature with attempts to fortify the consequences of the physical reasoning with some heuristic analysis. While the results thus obtained have the correct first-order functional dependence, multiplying constants may differ from those obtained from a rigorous analysis. From such physical reasoning and simple analysis, one can develop a sense of understanding that many complicated analyses fail to convey.

Because most transistor devices are based on p-n junctions, a study of their properties constitutes the bulk of this paper; a brief description of how these properties are utilized in the operation of certain transistor devices is included.

#### PHYSICAL CONCEPTS OF A P-N JUNCTION

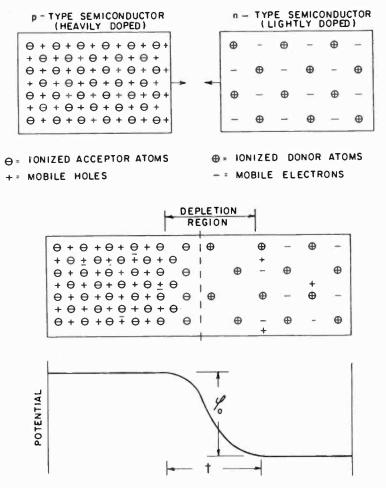

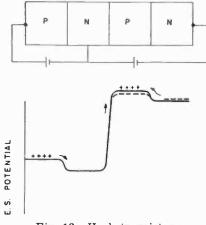

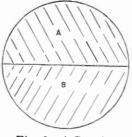

Consider a p-n junction to be formed by bringing together a p-type semiconductor and an n-type semiconductor as in Figure 1. This is not, today, a recommended method of forming a p-n junction. However, as an aid in visualizing the physical processes that go on, this model provides a simple initial state.

The p-type semiconductor contains impurity atoms (acceptors) having one less valence electron each than do the atoms of the host crystal. This robs the normal lattice of one electron for each impurity atom thus creating an electron vacancy or a hole. Since the hole repre-

sents an electron deficiency, it is represented as a positive charge. Since the impurity atom (originally electrically neutral) has acquired an additional electron, it is represented as a negative charge. The impurity atom is fixed in the crystal lattice but the hole is free to move and constitute a current.

Fig. 1-Physical picture of a p-n junction.

The converse situation exists in the n-type semiconductor where the impurity atoms (donors) now each have one extra valence electron over those required by the crystal lattice. This extra electron is given up; whereupon the freed electron wanders through the crystal and is free to constitute a current. The fixed impurity atom having given up an electron becomes charged positively. In the separated semiconductors, the mobile charges (electrons and holes) are uniformly distributed throughout the bulk material.

We now ask, what are the consequences of bringing together these two pieces of semiconductor? It may be expected that the mobile holes and electrons would tend to diffuse throughout the composite crystal. However, we shall see that restraining forces are set up which counteract this tendency so that the bulk of the holes remain in the p-type material and the bulk of the electrons remain in the n-type material. Thus, the charge densities in regions removed from the junction are essentially unaffected by this juncture.

It should be pointed out that the representation in Figure 1 is incomplete in that the holes and electrons are considered to be derived only from the ionization of the impurity atoms. In addition to the carriers thus derived, there are, in both types of semiconductor, additional electron-hole pairs formed by the release of electrons from atoms of the host crystal. The energy for ionization of these atoms comes from the thermal energy of the lattice. At normal temperatures and in material of the type ordinarily used for transistor devices, the number of electron-hole pairs thus generated is relatively small in comparison with the number of charge carriers derived from ionization of the impurity atoms.

Let us return now to a consideration of the mechanism whereby the holes and electrons are restrained from diffusing throughout the composite crystal. For simplicity consider one type of charge - the holes of the p-type region, for example. The holes tend to diffuse out of the p-type region where their density is high into the n-type region where there are but few holes. The fixed charges (negatively ionized acceptors) are then no longer electrically compensated and give rise to a negative charge density near the transition region between the p- and n-type materials. This negative charge being opposite to that of the holes will tend to retard the flow of holes out of the p-type region. Similarly, diffusion of electrons from the n-type region results in an uncompensated positive fixed charge density on the n side of the junction. This further restricts the loss of holes from the p-type region. Thus, under normal equilibrium conditions, the tendency for charges to diffuse across the junction sets up restraining forces in the form of uncompensated fixed charges in the transition region which act to keep the holes in the p-type region and the electrons in the n-type region.

To establish the uncompensated charge densities, the transition region is depleted of mobile charges and this region is often referred to as the depletion region or as the space-charge region. The uncom-

pensated charge densities set up an electric dipole resulting in an electrostatic potential difference,  $\phi_0$ , across the junction. Hence, reference is often made to this region as the barrier region, the thickness of the depletion layer being the barrier thickness, t, and the electrostatic potential,  $\phi_0$ , the barrier height. As in Figure 1, potential energy diagrams will be drawn, in this paper, so that electrons run down hill and holes run up hill.

#### CURRENT FLOW IN A P-N JUNCTION

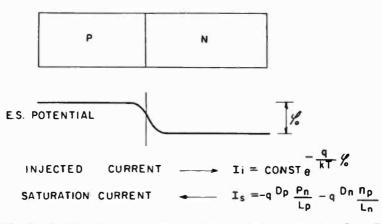

The discussion thus far has referred to a p-n junction under conditions of thermal equilibrium with no applied voltage. Before considering a voltage applied to the junction, let us consider the nature of the currents that might flow.

First we have the picture of holes tending to diffuse across the junction from the p-type region but being hindered by a barrier of height  $\phi_0$ . The number that do succeed in crossing will depend on the density of holes in the p-type region,  $p_p = N_a$  and on the barrier height,  $\phi_0$ . Statistical mechanics tells us that, in situations like this, the dependency on the barrier height is exponential and so we have for the hole density on the n-region side of the barrier,<sup>\*</sup>

$$p_0 = p_p \, e^{-\frac{q}{kT}\,\phi_0} \,. \tag{1}$$

We refer to this as an injected hole density in anticipation of hole injection in transistors. The current will be proportional to the injected charge density, so we write

$$I_i = \text{constant} \times e^{-\frac{q}{kT}\phi_0}.$$

(2)

An analogous flow of electrons into the p region occurs and we may take Equation (2) as being the sum of the hole flow to the right and electron flow to the left. Although the particle flow is conceived of as being in opposite directions for electrons and for holes, the current flow is in the same direction since the holes and electrons are oppositely charged.

Recall that we are still discussing a junction to which no external potentials have been applied. Under equilibrium conditions no net current must flow, so there must be a counter flow to achieve this balance.

<sup>\*</sup> A list of symbols used may be found in the appendix.

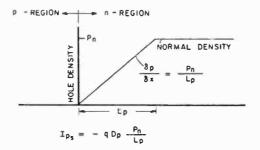

Let us see how this current arises. In the n region small numbers of holes are normally present as a result of electron-hole pair generation by thermal processes. There is also an internal potential established across the junction; this is in the direction to extract holes from the n region and sweep them into the p region. This, then, constitutes a reverse flow of holes which will balance those diffusing over the barrier into the n region. We ask how large is this current? The barrier potential can, of course, only extract those holes in the immediate vicinity, and in order for additional holes to be extracted they must diffuse to the barrier. Thus the magnitude of this current will be governed by the laws of current flow by diffusion. The "Ohms law," so to speak, for diffusion current flow is simply (for holes)

$$I_p = -qD_p \frac{\delta p}{\delta x}, \qquad (3)$$

i.e., the current is proportional to the charge density gradient. This simply says that particles tend to move from regions of high concentration to regions of low concentration. Thus to determine this current we need to determine the density gradient.

A first-order approximation for the density gradient may be obtained by physical arguments concerning the density at the junction and at some distance away from the junction. Referring now to Figure 2; at the junction, it may be argued, the hole density is zero since the holes will be immediately swept away by the barrier potential. Now a charge carrier in a semiconductor leads a rather hazardous life since it was derived from an atom which normally would like to get it (or a similar charge) back. Thus, there is always a probability that an electron will drop back into a vacancy represented by a hole, thus ending its life (for the moment) as a free charge capable of carrying current. The barrier potential cannot collect those carriers which are created so far away that they are lost by recombination before diffusing to the barrier. If  $L_p$  is the average distance a hole in the n-type material can diffuse before recombination, then at a distance  $L_p$  from the junction, the normal hole density,  $p_n$ , will be unaffected by the presence of the junction. The density gradient then is  $p_n/L_p$  and the diffusion current flow is

$$I_{p} = -q D_{p} \frac{p_{n}}{L_{p}} = -\frac{kT}{q} \frac{b}{(1+b)^{2}} \frac{\sigma_{i}^{2}}{\sigma_{n} L_{p}}, \qquad (4)$$

where the latter form may be obtained from simple manipulation using

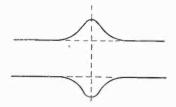

Fig. 2-Hole saturation current. Current flow is to left.

$$\sigma_i = q \ (\mu_p + \mu_n) \ n_i \ ; \ b = \frac{\mu_n}{\mu_p} \ ; \ p_n n_n = n_i^2 \ ; \ \sigma_n = q \mu_n n_n \ ; \ \mu = \frac{q}{kT} D.$$

By analogy the electron flow from the p region to the n region is (Figure 3)

$$I_{n_s} = -q D_n \frac{n_p}{L_n} = -\frac{kT}{q} \frac{b}{(1+b)^2} \frac{\sigma_i^2}{\sigma_p L_n}.$$

(5)

The total counter flow of current under equilibrium conditions is then

$$I_{s} = I_{P_{s}} + I_{n_{s}} = -\frac{kT}{q} \frac{b}{(1+b)^{2}} \sigma_{i}^{2} \left(\frac{1}{\sigma_{n} L_{p}} + \frac{1}{\sigma_{p} L_{n}}\right) .$$

(6)

Note that these currents do not depend on the barrier height. This

Fig. 3—Nature of current flow. Under equilibrium conditions  $I_i = I_i$ .

reverse flow then will not depend on the applied voltage; it is known as the saturation current.

Under equilibrium conditions, the saturation current just balances the injected current [Equation (2)]. The barrier height adjusts itself so that these currents are balanced for both hole and electron flow individually and no net current flows across the junction.

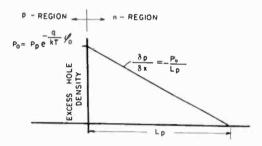

At this point we return to ask what happens to the injected carriers as in Equation (1) that succeed in overcoming the barrier. The injected holes tend to diffuse away from the barrier into the n-type material. As charge carriers, they are subject to the same hazardous life as the holes normally present, and on the average diffuse a distance  $L_p$  before being lost by recombination. Thus, the injected hole density distribution is approximately as shown in Figure 4. Recalling the form for current flow due to diffusion

Fig. 4-Injected hole current.

$$I_p = -q D_p \frac{\delta p}{\delta x}.$$

The hole current due to the injected charge density is simply

$$I_p = q D \frac{p_0}{L_p}$$

where  $p_0$  is related to the barrier height by Equation (1). A similar relation holds for the electrons surmounting the barrier in the opposite direction.

If an external potential is applied to the junction, the effect is to alter the height of the barrier. As noted above, this does not affect the saturation component of current flow but will change the injection current flow. The injection current flow now becomes

$$I_i = \text{constant} \times e^{-\frac{q}{kT}} \stackrel{(\phi_0 \to V)}{}, \qquad (7)$$

where V is taken positive when a positive potential is applied to the p side of the junction, as in Figure 5.

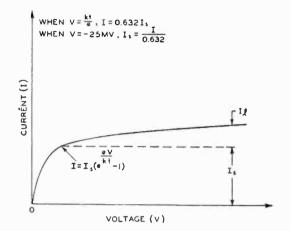

The constant in Equation (7) can readily be evaluated since we know that, when V = 0, the injection current must equal the saturation current. A little manipulation shows that the total flow is

$$I = I_s \left( \frac{q}{e^{kT}} V_{-1} \right) \tag{8}$$

and the same form applies individually to both the electron and hole components of the current. When V is positive a very large current will flow because of the exponential relation. When V is negative the cur-

rent will be extremely small and is the saturation current. It is seen from this relation that the rectification properties of a p-n junction have no direct relation to the proportion of current carried by holes or electrons. The ratio of forward to reverse current being simply

$$\left(\frac{\frac{q}{kT}}{e^{kT}}-1\right).$$

On the other hand for many device applications, the property which enables a p-n junction to inject holes into n-type material or to inject electrons into a p-type material is essential. It will be of interest to discuss these properties further.

Let us first, however, indicate the a-c conductance obtained by differentiation of Equation (8).

$$g = \frac{\delta I}{\delta V} = \frac{q}{kT} I_s \frac{q}{e^{kT}} V.$$

(9)

If  $V \gg \frac{kT}{q}$ ,  $g = \frac{q}{kT} I.$

If  $V \ll 0$ ,  $g \to 0.$

In particular, note the extremely small reverse conductance given by this simple theory. Subsequently we shall see how another phenomenon in a p-n junction leads to a finite a-c conductance.

#### HOLE AND ELECTRON CURRENTS - INJECTION EFFICIENCY

We note from Equation (8), that the current in a p-n junction is proportional to the saturation current. Hence, an inspection of the saturation currents for holes and electrons will give us information on the character of the diode current whether it be in the forward or reverse direction. From Equations (4) and (5) it is seen that the hole current depends only on the properties of the n-type region and the electron current only on the properties of the p-type region. The injection ratio of the hole and electron currents is, from Equations (4) and (5),

$$\frac{I_p}{I_n} = \frac{I_{p_n}}{I_{n_s}} = \frac{\frac{1}{\sigma_n L_p}}{\frac{1}{\sigma_n L_n}} = \frac{\sigma_p L_n}{\sigma_n L_p}.$$

(10)

For diffusion lengths of roughly equal magnitude, the predominant current across the junction corresponds to the majority carrier of the material having the greater conductivity. In this way a p-n junction may be utilized to inject a current of minority carriers into a semiconductor body and to suppress a flow of undesired majority carrier current from that body. This property of the p-n junction forms the basis for the common type of bipolar transistor.

It is common in discussing various aspects of transistor theory to refer to the injection efficiency,  $\gamma$ , rather than the ratio given by Equation (10). The hole injection efficiency is the fraction of the total current across the junction carried by holes, and is

$$\gamma = \frac{I_p}{I} = \frac{I_p}{I_p + I_n} = \frac{1}{1 + \frac{\sigma_n L_p}{\sigma_p L_n}} \approx 1 - \frac{\sigma_n L_p}{\sigma_p L_n}$$

where the approximation is valid for efficiencies near unity. An analogous relation for the electron injection efficiency can be written.

The above discussion of various aspects of the p-n junction has been given on the basis that the currents were small. However, as the currents are increased as would be desirable, for example, in a power transistor or even in the large-signal operation of a low-power transistor, other effects become important. This discussion of the injection efficiency is an opportune place to consider one of these effects, namely, the reduction of injection efficiency with increasing currents. This consideration will also bring to light a basic physical concept which, in the interests of simplicity, has not yet been pointed out.

For clarity, consider a specific type of junction — in particular one in which  $\sigma_p \gg \sigma_n$ , so that the current across the junction is carried principally by holes being injected into the n-type region. At low currents, the ratio of hole to electron current is given by Equation (10). We ask how this is altered at high currents.

When a hole is injected into the n-type region, an electron also enters through the external connection to preserve charge neutrality. Although we have considered principally the injection of one type of charge, this injection is accompanied by an equal flow of carriers of the opposite type. Reference is often made to this fact by stating that one should really speak and think of the injection of electron-hole pairs rather than confining one's attention to the injection of one type of carrier. Indeed, a consequence of this is the reduction of emitter efficiency at high currents.

If, then,  $p_0$  is the injected hole density corresponding to an injected current,  $I_p = qDp_0/L_p$ , as in Figure 6, then an equal compensating charge density,  $n_0 = p_0$  is added to the electron density normally present. Those electrons normally present arise from ionization of the donor atoms,  $N_d$ , so that the total electron density is  $p_0 + N_{d^*}$ . This, then, is the total electron density at the junction being held back from entering the p region by the barrier ( $\phi_0 - V$ ). The number crossing the barrier is

$$(p_0 + N_d) e^{-\frac{q}{kT}(\phi_0 - V)}$$

.

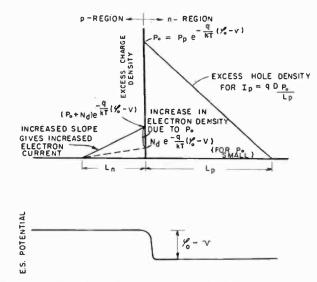

From the earlier calculation of diode current where the increase in

electron density was neglected it will be recalled that for zero applied voltage the injected current was equal to the saturation current so that

$$N_{d} e^{-\frac{q}{kT}\phi_{0}} = I_{ns}$$

From this  $e^{-kT^{-0}}$  can be evaluated so that  $I_n$  becomes approximately

$$I_{n} = \frac{p_{0} + N_{d}}{N_{d}} I_{n_{s}} e^{\frac{q}{kT} V} = \left(1 + \frac{L_{p}}{qD_{p}N_{d}} I_{p}\right) I_{n_{s}} e^{\frac{q}{kT} V},$$

(11)

Fig. 6—Excess charge densities for p-n junction where  $\sigma_p \gg \sigma_n$  and showing how electron current in p-region is increased by injection of  $p_0$  into n region. The proportion of total current carried by holes is thereby reduced.

where, since large currents are assumed, the saturation current flow is omitted. The electron current flow across the junction has been increased by the factor  $(1 + p_0/N_d)$  which is a function of the hole current. A similar argument may be applied to the hole current but for the case  $\sigma_p \gg \sigma_n$  the factor is small and may be neglected for this first-order calculation. The injection ratio is then

$$\frac{I_p}{I_n} = \frac{I_{p_g}}{\left(1 + \frac{p_0}{N_d}\right)I_{n_g}} = \frac{\sigma_p L_n}{\sigma_n L_p} \left(\frac{N_d}{p_0 + N_d}\right).$$

(12)

In this case, the hole injection efficiency is reduced by a disproportionate *increase in the electron current* crossing the junction as the voltage is increased to increase the injected hole current.

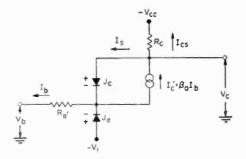

#### BIPOLAR TRANSISTOR

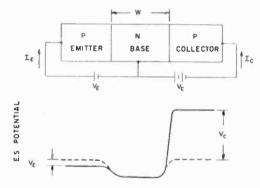

Let us consider how the properties of the p-n junction may be applied to form the conventional bipolar transistor. Consider, as in Figure 7, a p-n-p transistor formed from two p-n junctions placed back to back with a base width, W, which is much less than the diffusion length for holes in this region and with voltages applied as indicated. With a positive voltage applied to the left-hand junction, a large current will flow into the base. If the conductivity of the emitter is much greater than that of the base, this current will be predominantly a hole flow. The injected holes are minority carriers in the base region

Fig. 7-p-n-p transistor.

and will diffuse through the base. Because the base region is thin, most of these will reach the right-hand junction and only a small fraction will be lost by recombination in the base. The right-hand junction is biased negatively, or in a direction to collect holes from the base region and transfer them to the right-hand p region. Thus the hole current injected by the emitter p-n junction diffuses through the base and is collected by the collector junction and the hole current is substantially constant through the device. Electron currents across the junctions are unwanted currents (in a p-n-p transistor) and one of the problems of transistor design concerns the minimization of these currents.

The forward conductance of a p-n junction is large, so that little power is required to inject hole current into the base region. On the other hand, the conductance of a junction biased in the reverse direction is very small. Now, because the same current flows through the small conductance of the collector junction that was injected at the cost of very little power through the emitter junction, a considerably increased power may be developed in an external load.

Transistor action depends primarily on the diffusion of minority carriers through the base region. An analysis of the base region provides the essential features of transistor performance while the properties of the end regions are principally concerned with the flow of unwanted currents. A rigorous analysis then would solve the diffusion equation in the base subject to the boundary conditions imposed by the junctions. This becomes somewhat involved analytically, and therefore a somewhat heuristic approach on the basis of the current flow in p-n junctions discussed above will be followed.

The current flow across the emitter junction can be conceived of as

$I_e = (\text{hole} + \text{electron flow due to } V_e) + (\text{hole} + \text{electron flow due to } V_c),$

and that across the collector junction as

$I_c = (\text{hole} + \text{electron flow due to } V_c) + (\text{hole} + \text{electron flow due to } V_c).$

We might write the first term of  $I_e$  by considering this as a straightforward diode and using Equation (8); however, one modification must be made. The diode relation, Equation (8), was computed on the basis that the diffusion length,  $L_p$ , in the *n* region was smaller than the extent of the region. In the transistor, we have made *W* smaller than  $L_p$ . It will be recalled that  $L_p$  was the distance in which the injected hole density decreased to zero. In the transistor case, the collecting action of the collector junction reduces the hole density to zero at *W*. It is reasonable to replace  $L_p$  by *W* as the factor in determining the gradient giving rise to diffusion flow of current. Similarly, the second term of  $I_c$  can immediately be written down with the above modification. This is essentially the reverse current of the collector junction, i.e., the current for a junction biased negatively.

This leaves the transfer terms to be considered. Consider first the transfer term of  $I_c$ . From our physical explanation of the operation of the transistor this is simply the hole current injected by the emitter junction and collected at the collector (p-n-p transistor). It is given by the hole component of Equation (8) again with the modification of replacing  $L_p$  by W.

Now the structure is quite symmetrical and nothing in the device indicated that the left-hand junction should be the emitter. Thus we

13

must cause the transfer terms to have similar coefficients so that, if we choose, we can interchange the voltage polarities and obtain transistor action using the right-hand junction as the emitter. We therefore write the second term in  $I_e$  in a form similar to the first term in  $I_e$ . Thus we have

$$I_{e} = \frac{kT}{q} \frac{b}{(1+b)^{2}} \sigma_{i}^{2} \left[ \left( \frac{1}{\sigma_{b}W} + \frac{1}{\sigma_{c}L_{e}} \right) \left( e^{\frac{q}{kT} \nabla_{e}} - 1 \right) - \frac{1}{\sigma_{b}W} \left( e^{\frac{q}{kT} \nabla_{e}} - 1 \right) \right]$$

$$I_{e} = \frac{kT}{q} \frac{b}{(1+b)^{2}} \sigma_{i}^{2} \left[ \frac{1}{\sigma_{b}W} \left( e^{\frac{q}{kT} \nabla_{e}} - 1 \right) - \left( \frac{1}{\sigma_{b}W} + \frac{1}{\sigma_{c}L_{c}} \right) \left( e^{\frac{q}{kT} \nabla_{e}} - 1 \right) \right]$$

$$(14)$$

which is the first order approximation to the solution obtained from a rigorous mathematical development. In the rigorous solution the coefficients of  $\begin{pmatrix} q & v \\ e^{-kT} & v \\ e^{-kT} & -1 \end{pmatrix}$  are given in terms of hyperbolic functions and in practice it is the first-order approximation given in Equation (14) that is most often used in calculations.

We will return now to the simple p-n junction for a discussion of other basic properties. Before so doing, and for future use in some brief comments on the origin of temperature effects in transistors, note how temperature enters the transistor equations. While most of the parameters of Equation (14) have some temperature dependence, the most sensitive factor is the intrinsic conductivity,  $\sigma_i$ . This is discussed later.

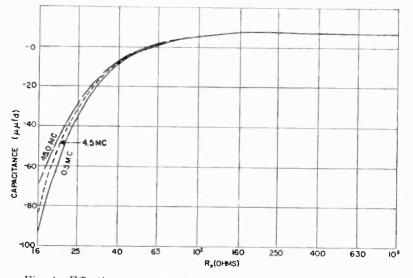

#### CAPACITATIVE EFFECTS IN A P-N JUNCTION

Two phenomena give rise to the flow of capacitive currents in p-n junctions. The first of these, which we will term a diffusion capacitance, is the result of the nature of minority carrier flow in a semiconductor, i.e., a diffusion flow. The second, which we will refer to as a transition capacitance, is a consequence of the depletion of mobile charges near the junction as discussed earlier.

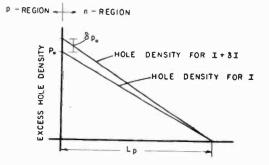

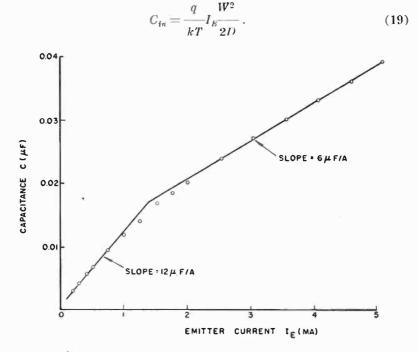

Consider first the diffusion capacitance arising from hole injection into the n region of a p-n junction. The hole flow in the n region corresponds, as we have seen, to a charge density gradient as shown in Figure 8. If the current is altered by changing the applied voltage, the gradient, and hence the charge density distribution, must change thus changing the total charge. This change in total charge with the applied voltage corresponds to a capacitance (a diffusion capacitance).

The total hole charge within a diffusion length of the junction is

$$Q = q \frac{p_0}{2} L_p.$$

The diffusion current is

$$I_p = -qD_p \frac{\delta p}{\delta x} = qD_p \frac{p_0}{L_p}.$$

Fig. 8—Hole density distributions in n region for calculation of hole diffusion capacitance.

Then

$$C = \frac{\delta Q}{\delta V} = \frac{\delta Q}{\delta p_0} \frac{\delta p_0}{\delta I_p} \frac{\delta I_p}{\delta V} = \left(q \frac{L_p}{2}\right) \left(\frac{L_p}{q D_p}\right) \left(\frac{q}{kT} I_p\right)$$

$$= \frac{q}{kT} \frac{L_p^2}{2D_p} I_p, \qquad (15)$$

where the a-c conductance

$$\frac{\delta I_p}{\delta V} = \frac{q}{kT} I_p,$$

was obtained from Equation (9).

An analogous expression exists for the diffusion capacitance for the electron flow into the p region. The total diffusion capacitance is

ordinarily much larger than the transition capacitance and plays an important part in limiting the frequency response of the transistor. In the transistor, however, we must remember the minority carriers are stored in the distance W and not  $L_p$ , since ordinarily  $W \ll L_p$ . We can thus replace  $L_p$  by W in thinking of the diffusion capacitance of the injecting junction of a p-n-p transistor.

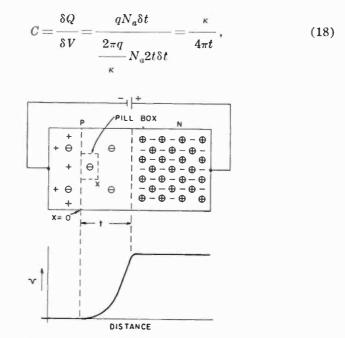

Consider next the transition capacitance which, in a transistor, is important for the collector junction. We have seen earlier how the potential barrier in a p-n junction was a consequence of the depletion of mobile charges in this region leaving uncompensated fixed charges. Further, if the potential drop is varied by an externally applied voltage, these densities must be altered to correspond to the new conditions. This process requires a flow of charge in response to the change in voltage, i.e., a capacitative flow. It is apparent that the exact nature will depend on the distribution of impurity atoms in the transition region. Two cases of practical importance have been much discussed: (1) an abrupt or step transition in which the impurity type changes discontinuously from n to p, and (2) a gradual transition in which the net impurity concentration changes linearly from n to p. We will consider the first case-a discontinuous transition-and, in particular, a junction in which  $\sigma_n \gg \sigma_p$ . This is shown in Figure 9, where the depletion layer is considered to exist only in the p region by virtue of its much lower conductivity. If we construct a pill-box of unit cross sectional area with one face at x = 0 at the edge of the depletion layer where the field is zero and the other face at x = x, the field at x is given by Gauss' Law as

$$\int_{\text{surface}} \mathcal{E}_n dA = \frac{4\pi Q}{\kappa}$$

here  $\mathcal{S}_n$  is the normal surface component of the field and Q is the charge enclosed in the pill-box. Upon integration,

$$\mathcal{E} = \frac{4\pi}{\kappa} q N_a x.$$

The potential can be found by integration over the barrier thickness, t:

$$V = \int \mathcal{E}dx = \frac{2\pi q}{\kappa} N_a t^2, \qquad (16)$$

so the barrier thickness is

ŝ,

$$t^2 = \frac{\kappa \mu_p}{2\pi \sigma_p} V. \tag{17}$$

The capacitance can then be determined by taking the incremental change in charge with voltage, i.e.,

Fig. 9—Figure for calculation of transition capacitance when  $\sigma_n \gg \sigma_p$ .

which is the capacitance per unit area of a parallel plane capacitor with electrode spacing t filled with a material of dielectric constant,  $\kappa$ .

If one performs a similar analysis for the depletion region in the n region (which we neglected above in the interests of simplicity), the total depletion region thickness is given by

$$t^{2} = \frac{\kappa \mu_{p}}{2\pi} \left( \frac{b}{\sigma_{n}} + \frac{1}{\sigma_{p}} \right) V, \qquad (19)$$

where V is the total barrier potential including both the internal electrostatic potential and the applied voltage. In many practical transitions, such as those characteristic of alloyed junctions, one of the conductivities is much greater than the other and one term may be dropped, as in our example.

For a linear transition, the barrier thickness is given by

$$t^2 = \frac{3\kappa}{4\pi q a} V, \tag{20}$$

where a is the net impurity density gradient.

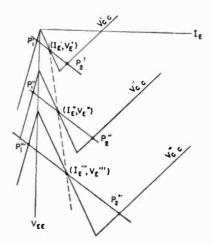

# SOME CONSEQUENCES OF VARIABLE BARRIER THICKNESS

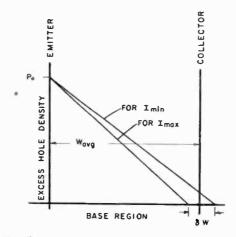

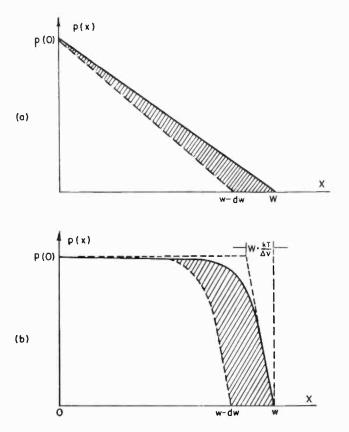

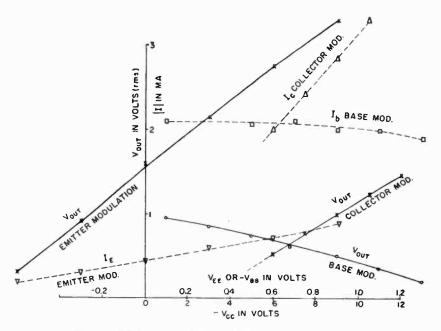

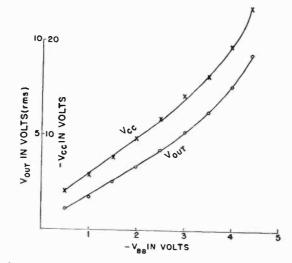

Because the barrier thickness depends on the applied voltages, the simple picture of transistor operation we have given earlier must be modified in detail. Consider, for example, the effect of a variable voltage across the collector junction. Such a voltage is present when the transistor is operating into a load across which an a-c voltage is developed. The "electrical" thickness of the collector junction now varies with the instantaneous voltage and in so doing, alters the base width of the transistor (base width modulation). This effect modifies both the apparent conductance and susceptance of the collector junction. Let us consider a physical picture of these phenomena. Figure 10 shows the situation in the base region of the transistor as the effective position of the collector junction is varied.

Remembering that the diffusion current is proportional to the density gradient

$$I = -qD_{p} \frac{\delta p}{\delta x},$$

$$I_{\text{max}} = qD_{p}p_{0} \frac{1}{W - \frac{\delta W}{2}}, \qquad I_{\text{min}} = qD_{p}p_{0} \frac{1}{W + \frac{\delta W}{2}}.$$

Then

$$g = \frac{\delta I}{\delta V} = \frac{I_{\max} - I_{\min}}{\delta V} = q \frac{D_p p_0}{W} \frac{1}{W} \frac{\delta W}{\delta V} = I \frac{1}{W} \frac{\delta W}{\delta V}, \quad (21)$$

giving an approximate expression for the a-c conductance due to modulation of the base width, W, by an applied signal. As we have seen earlier, the simple theory gave a conductance for a reversed bias junction of the form  $e^{\frac{q}{kT}}$ . Even for relatively small negative values of V, this conductance is extremely small. The conductance developed

18

above turns out to be much greater and, for a practical unit with negligible leakage, does express the finite conductances found.

The situation of Figure 10 shows that the charge in the base region also varies as the effective position of the collector junction moves. This variation of charge with voltage may be interpreted as a capacitance which adds in parallel to the junction transition capacitance discussed above. This capacitance is derived as follows:

$$Q_{\max} = q \frac{p_0}{2} \left( W + \frac{\delta W}{2} \right), \qquad Q_{\min} = q \frac{p_0}{2} \left( W - \frac{\delta W}{2} \right)$$

$$C = \frac{\delta Q}{\delta V} = \frac{Q_{\max} - Q_{\min}}{\delta V} = \frac{q p_0}{2} \frac{\delta W}{\delta V} = I \frac{W^2}{2D_0} \frac{1}{W} \frac{\delta W}{\delta V}. \tag{22}$$

Fig. 10—Hole distributions in base of p-n-p transistor as effective base width is varied by variation in collector voltage.

This is similar in form to the diffusion capacitance associated with the emitter due to the flow of holes into the base. However, in this case the additional factor (1/W) ( $\delta W/\delta V$ ) makes this capacitance small and in practice it is but a fraction of the transition capacitance.

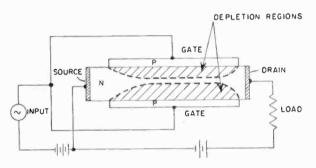

#### FIELD-EFFECT TRANSISTOR

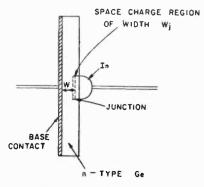

This phenomenon of a variable barrier thickness has formed the basis for a different type of transistor device — the field-effect transistor. Such a device, which is shown in Figure 11, consists of a thin piece of semiconductor on the opposite sides of which are two p-n junctions. An ohmic contact is located at either end of the semicon-

ductor. It is seen that a conducting channel exists between the two ohmic contacts. This channel is defined by the two p-n junctions. If a reverse bias is applied to the two junctions, the conducting channel becomes still further limited by the depletion layers of the junctions. Thus the channel conductance may be varied by modulating its cross section through a variable voltage applied to the p-n junction. In this way the signal applied to the p-n junction controls the current flow between the ohmic contacts and through the load.

Fig. 11—Field-effect transistor.

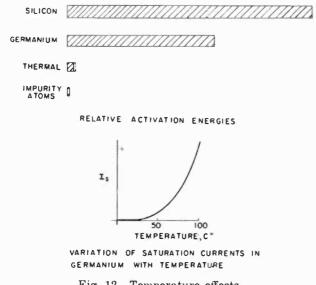

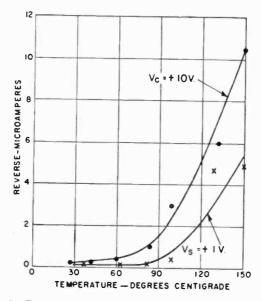

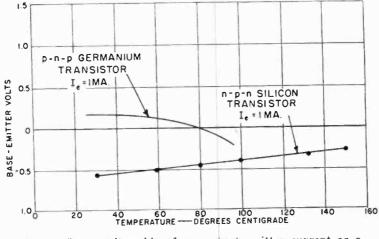

#### ORIGIN OF TEMPERATURE EFFECTS

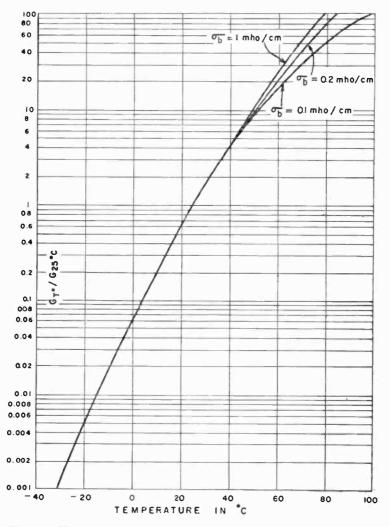

We will briefly examine the origin of the most important factor in determining temperature effects in transistors. In connection with the transistor equations, it was previously stated that the intrinsic conductivity was the most sensitive factor. Let us see how this comes about. Recalling that the diode currents were proportional to the saturation currents, we will look at the hole saturation current,

$$I_{p_s} = -q D_p \frac{p_n}{L_p},$$

where  $p_n$  is the density of holes of thermal origin in the n-type material. These holes are created by the loss of an electron from an atom of the host crystal. Writing this in another fashion, using the relation  $n_i^2 = n_n p_n$ ,

$$I_{P_s} = -q \frac{D_p}{L_p} \frac{n_i^2}{n_n},$$

where  $n_i$  is the density of electrons (or holes) in intrinsic material and

$n_n$  is the density of electrons in the n-type material which come principally from the donor atoms.

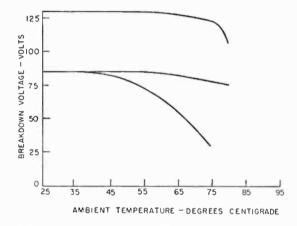

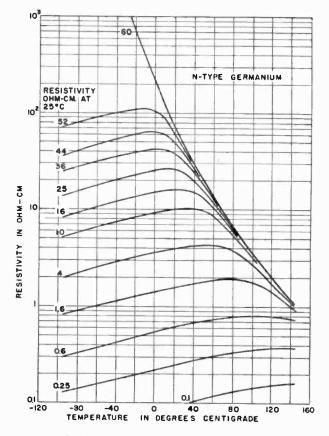

Figure 12 shows, relative to thermal energy at room temperature (shaded) and  $100^{\circ}$ C (dotted), the energy required to release an electron from an impurity atom normally used in doping germanium and from a germanium atom and from a silicon atom. It is seen that thermal energy is somewhat larger than that required to release an electron from an impurity atom. It is for this reason that at normal temperatures we can assume that all of the impurity atoms are ionized and consequently that the normal electron density in n-type material,  $n_n$ , is equal to the donor density,  $N_d$ . Furthermore, having ionized all

of the donor atoms at normal temperatures, further increases in temperature do not change the number of electrons obtainable from this source. Then in  $I_{\nu_s}$  above,  $n_n$  does not vary rapidly with temperature.

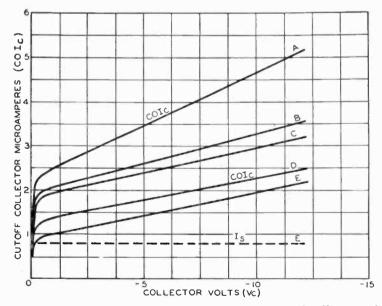

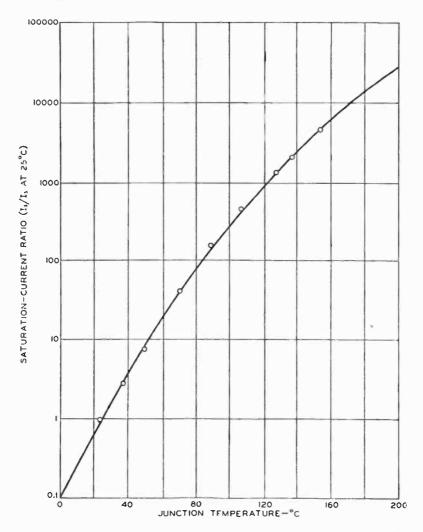

On the other hand, normal thermal energies are much smaller than the energy required to extract an electron from either a germanium or silicon atom. The number of electrons that will surmount a barrier as we have discussed in connection with the barrier in a p-n junction, is an exponential function of the barrier height in terms of thermal energy. Indeed,

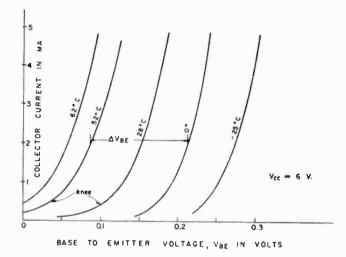

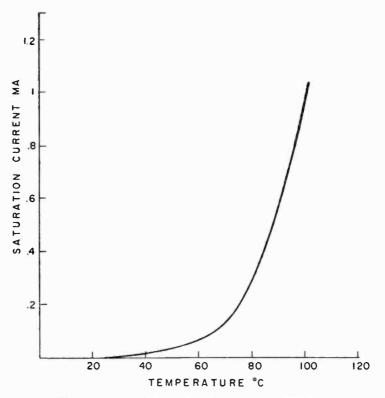

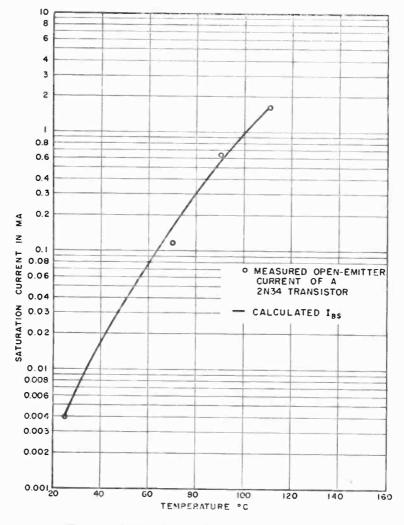

$$n_i^2 \alpha c - \frac{q}{kT} E_0$$

where  $E_{G}$  is the "band gap" or activation energy shown relatively in Figure 12. Although the numbers are relatively small in comparison with  $n_n$  in practical transistors, the variation with temperature, due principally to the exponential dependence, is extremely rapid. The graph of Figure 12 illustrates the temperature dependence of the saturation current in germanium between zero and 100°C. This corresponds to the reverse collector current,  $I_{co}$  or  $COI_o$ . Because the activation energy in silicon is greater than that in germanium, the density of intrinsic electrons (and holes) at the same temperature is much less (again because of the exponential dependence on barrier height). However, the variation is similar in form and is about the same percentage-wise, but, because the density at normal temperatures is so small, the currents are unobjectionable until the temperature is increased considerably.

#### OTHER TRANSISTOR DEVICES

Let us consider briefly the mode of operation of a few other transistor devices made of an assemblage of p-n junctions.

The hook transistor shown in Figure 13 illustrates a different principle that provides a possible explanation for a certain behavior of point contact transistors. The hook transistor shown is a p-n-p-n structure with no external connection made to the internal p-region. The left hand junction is biased in the forward direction as an emitter. A negative potential is applied to the right-hand n-region. This biases the internal p-region negatively with respect to the base - in the direction to collect the holes emitted by the emitter. Under static conditions the internal p-region floats at a potential such that the currents entering and leaving it are equal. If holes are injected at the emitter and collected by the internal p-region, they are essentially trapped there - for we recall that holes tend to run uphill. The accumulation of holes lowers the potential of the internal p region biasing it in a forward direction with respect to the right hand n region. This permits an even greater number of electrons to be injected from the right which diffuse through the p-region and are collected by the n-type base. In this fashion the current injected by the left hand junction can control an even greater current flowing across the right-hand junction. Thus, a current-gain factor, alpha, which is greater than unity may be obtained. This is in contrast to the p-n-p junction transistor in which the collector current could at most be equal to the injected current, i.e., alpha is unity.

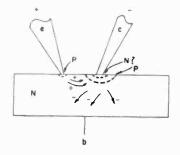

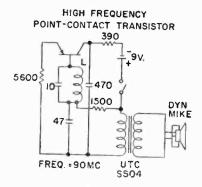

Figure 14 shows a point-contact transistor. Its operation can be at least qualitatively explained in terms of p-n junction theory. However, the details of its operation are not developed to the relatively refined

Fig. 13-Hook transistor.

state of the junction transistor. Here the emitter is a metal-to-semiconductor contact which, with the aid of surface states on the crystal, is able to create an electron-deficient or p-type region in the vicinity of the contact. Such a contact, similar to the p-n junction, can inject holes into the body of the germanium. The collector junction of a point contact is normally "formed" by pulsing it with an electric current. This forms a p-type region somewhat under the surface of the crystal. Biased negatively this acts as a collector for the holes injected by the emitter. Thus far we have something not much different than a p-n-p junction transistor except for geometry. However, point contact transistors, as it is well known, have current-gain factors (alphas) greater than unity. Just how this is achieved has not yet been completely determined. If one considers that between the formed p-region and the contact there exists an n-type region, then the structure is serially similar to the junction hook transistor discussed above. The reasoning

Fig. 14-Point contact transistor.

23

that gave the junction hook transistor a current-gain factor greater than unity can be invoked to "explain" this behavior of the pointcontact transistor. This has not been entirely successful. An alternative proposal has been made that the collector forming process introduces traps in the region near the collector point. These traps are temporarily filled by holes injected by the emitter and in this state represent an accumulation of positive charge directly in front of the metallic collector point. The metallic collector point can supply an abundance of electrons and these are extracted from the metal by the collection of positive holes in the traps. This electron current flow may be much larger than the hole current injected by the emitter to give current-gain factors greater than unity.

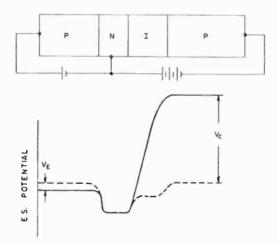

Fig. 15-p-n-i-p transistor.

A p-n-i-p transistor is shown in Figure 15. This may be considered much like a usual p-n-p junction transistor with a modified collector region. The modification in this case consists of the intrinsic region interposed between the n-type base and the p-type collector. In our discussion of depletion layers, we saw how the depletion layer extended principally into the low-conductivity material. The p-n-i-p transistor may be viewed as a p-n-p transistor in which the conductivity of the side of the base region near the collector has been made extremely low. When a potential is applied to the collector, the field extends through the intrinsic layer to the base. This provides a collector junction whose barrier thickness is very wide — the thickness of the intrinsic layer. Because the applied potential is distributed over a larger region, this

#### BASIC TRANSISTOR DEVICE CONCEPTS

type of junction can withstand a high reverse voltage and has a lower capacitance. The low collector capacitance improves the high-frequency operation. The high-frequency operation of this type also depends, as in the conventional p-n-p transistor, upon making the n-type base region very thin. High-frequency operation also demands that the n-type region have a high conductivity which may seriously limit the voltage that may be applied to the collector junction of a conventional unit. In the p-n-i-p structure higher conductivity may be used in the n-type base with improved high-frequency performance without compromising the collector breakdown voltage.

#### CONCLUSIONS

This paper has discussed, largely on the basis of physical arguments, some of the basic transistor device concepts. The discussion has examined the various electrical properties of the p-n junction and pointed out the important roles played by the junction barrier and by diffusion phenomena. There has also been indicated in an elementary fashion how the properties of a p-n junction are utilized in a few transistor devices.

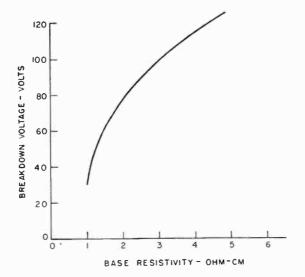

In other papers of the present volume, these concepts are further extended and applied to new and improved devices. Thus, E. W. Herold's "New Advances in the Junction Transistor" includes discussions of the alloy process of transistor fabrication, the effects of transistor geometry and an equivalent circuit for the transistor, among other topics. The limitations of diffusion phenomena on the frequency response of transistors are further developed by H. Kroemer. In his paper, "The Drift Transistor," a new transistor structure is described which uses a nonuniform impurity distribution in the base region to avoid the limitations of carrier diffusion. At the same time, this structure elegantly satisfies the other requirements for high-frequency operation. The capacitance of a p-n junction barrier is utilized by L. J. Giacoletto and J. J. O'Connell in "A Variable-Capacitance Germanium Junction Diode for UHF." Considerations of the injection efficiency of emitter junctions are invoked in two papers, "P-N-P Transistors Using High Emitter-Efficiency Alloy Materials," by L. D. Armstrong, C. L. Carlson, and M. Bentivegna, and "Recent Advances in Power Junction Transistors," by B. N. Slade; methods of improving injection efficiencies are described. Thus, the basic properties of a p-n junction discussed in the present paper are of general application throughout the transistor field, and it is hoped that the present discussion will provide a background for the important advances in the transistor art described in other papers in this book.

25

#### APPENDIX --- SYMBOLS

- I = current density

- V = voltage

- p = hole density

- n = electron density

- $N_a =$ acceptor impurity density

- $N_d =$ donor impurity density

- k = Boltzmanns constant

- T =Kelvin temperature

- $\phi =$ barrier potential

- $q = \underset{charge}{\text{magnitude of electronic}}$

- D = diffusion constant

- $\mu = \text{mobility}$

- L = diffusion length

- $\sigma =$ conductivity

- $b = \mu_n/\mu_p$  = ratio of electron to hole mobility

- g = a-c conductance

- C = capacitance per unit area

- Q = charge

- t =barrier thickness

- W =base region width

- $\kappa = dielectric constant$

- $\mathcal{E} = \text{electric field intensity}$

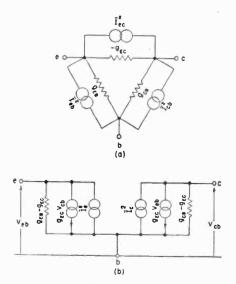

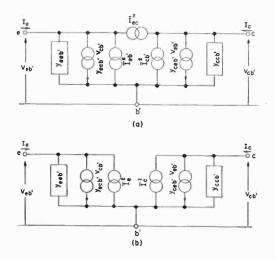

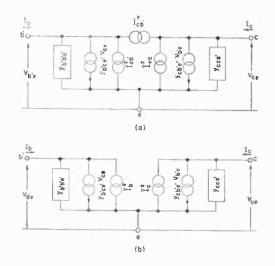

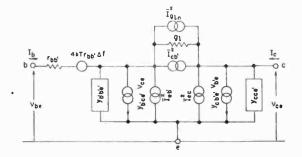

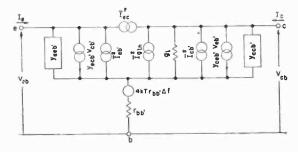

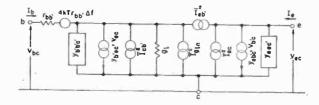

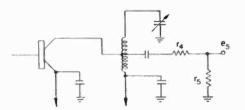

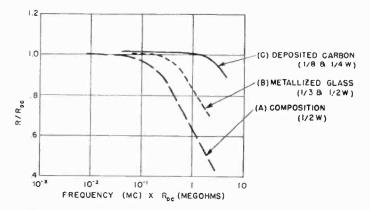

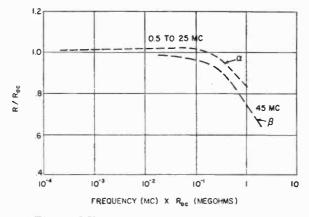

# NEW ADVANCES IN THE JUNCTION TRANSISTOR<sup>†</sup> By

#### E. W. HEROLD

RCA Laboratories, Princeton, N. J.

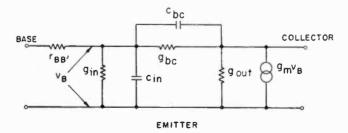

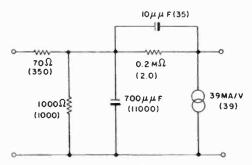

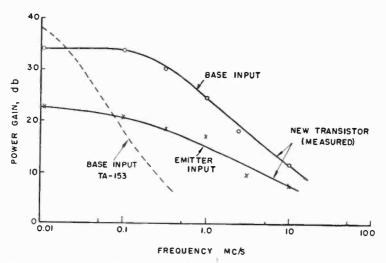

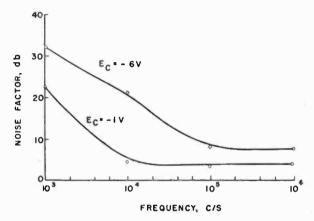

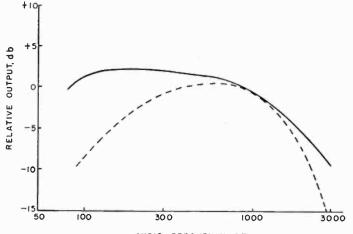

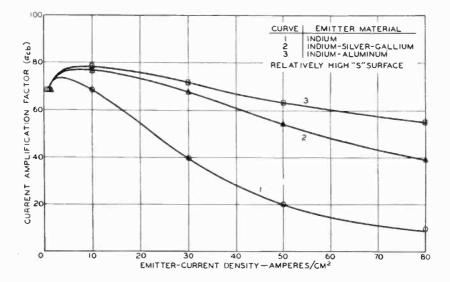

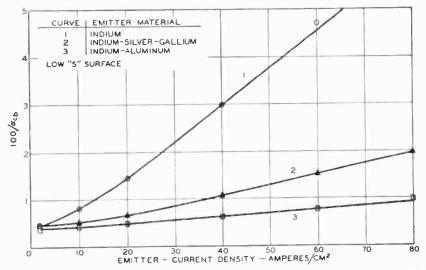

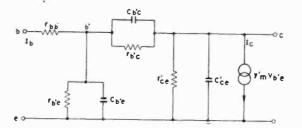

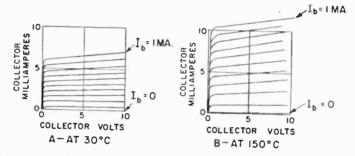

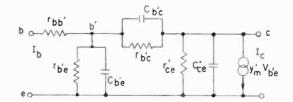

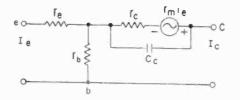

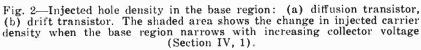

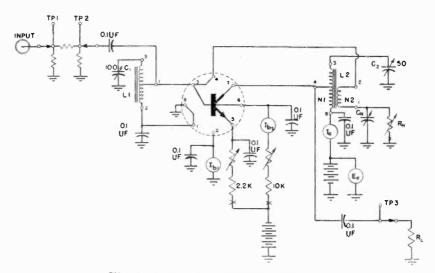

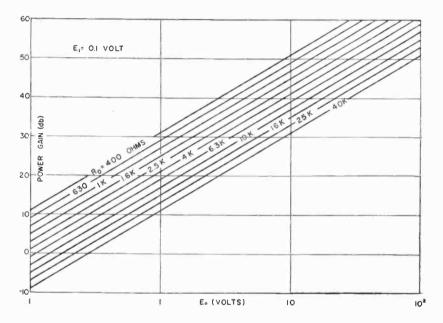

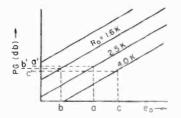

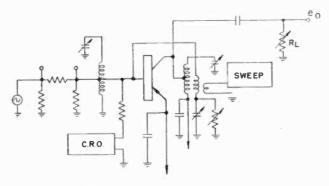

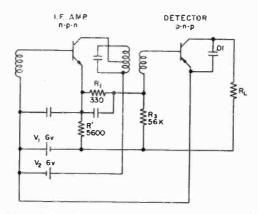

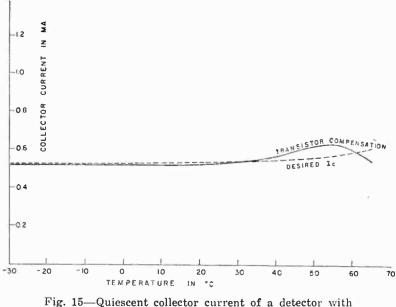

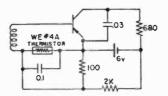

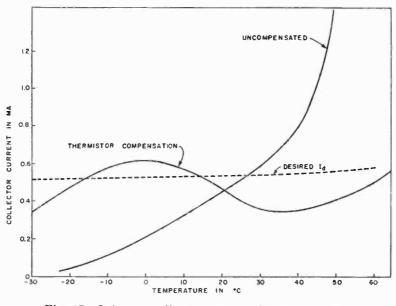

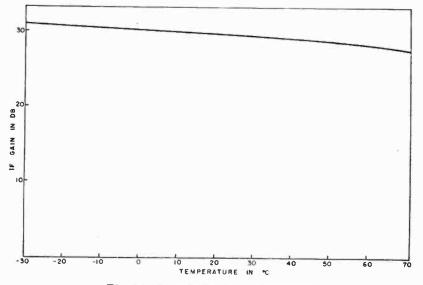

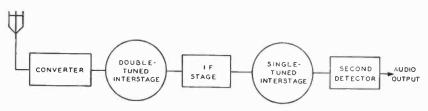

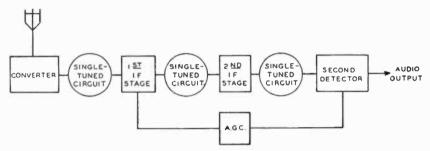

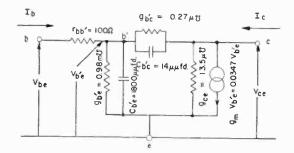

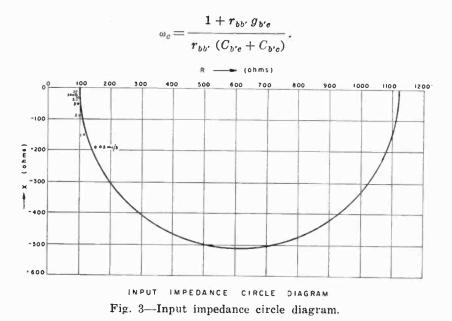

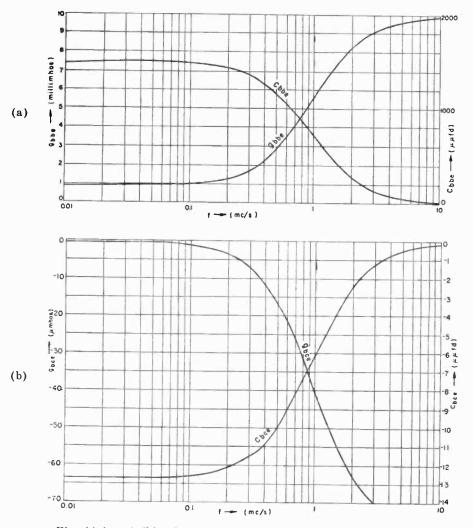

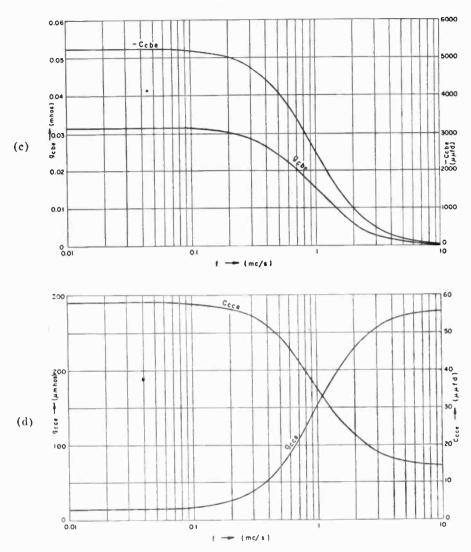

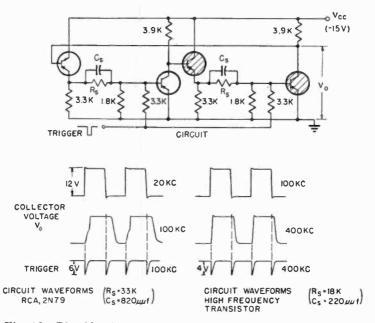

Summary—This paper presents a survey of some recent RCA research on the alloy junction transistor. The alloy process is described and analyses are given showing how the current amplification factor,  $\alpha$ , varies with geometry, surface recombination and emitter current injection. A simple equivalent circuit is derived, based on the physical constants of the transistor. It is then shown that the chief factors limiting frequency response can be reduced in magnitude in an improved radio-frequency amplifier transistor, which also oscillates at frequencies as high as 75 megacycles. A battery-operated, portable broadcast receiver uses these transistors to obtain performance equal to or exceeding that of tube receivers.

#### INTRODUCTION

HE point-contact transistor, now 5 years old, seems destined to be supplanted for many applications by a slightly more recent device, the junction transistor.<sup>1</sup> The latter type of amplifier was initially difficult to fabricate but can now be made, by a relatively simple alloy process, in either the p-n-p type<sup>2</sup> or the n-p-n type.<sup>3</sup> Because such a transistor had properties and geometry which differed from those assumed in available theories, studies were undertaken in this laboratory to clarify the operation and improve the frequency response. The present paper reviews the salient points of these researches as a whole; detailed descriptions of some parts of the work are being published elsewhere.<sup>4-6</sup>

<sup>1</sup> W. Shockley, U.S. Patent 2,569,347, applied for June 26, 1948.

<sup>&</sup>lt;sup>†</sup>Reprinted from the British Journal of Applied Physics, April, 1954; based on a lecture delivered in London, October 20, 1953.

<sup>&</sup>lt;sup>2</sup> R. R. Law, C. W. Mueller, J. I. Pankove, and L. D. Armstrong, "A Developmental Germanium p-n-p Junction Transistor," *Proc. I.R.E.*, Vol. 40, p. 1352, November, 1952.

<sup>&</sup>lt;sup>3</sup> D. A. Jenny, "A Germanium n-p-n Alloy Junction Transistor," Proc. I.R.E., Vol. 41, p. 1728, December, 1953.

<sup>&</sup>lt;sup>4</sup> A. R. Moore and J. I. Pankove, "The Effect of Junction Shape and Surface Recombination on Transistor Current Gain," *Proc. I.R.E.*, Vol. 42, p. 907, June, 1954.

<sup>&</sup>lt;sup>5</sup> W. M. Webster, "On the Variation of Junction-Emitter Current-Amplification Factor with Emitter Current," *Proc. I.R.E.*, Vol. 42, pp. 914-920, June, 1954.

<sup>&</sup>lt;sup>6</sup>C. W. Mueller and J. I. Pankove, "A p-n-p Triode Alloy Junction Transistor for Radio-Frequency Amplification," *RCA Review*, Vol. 14, p. 586, December, 1953.

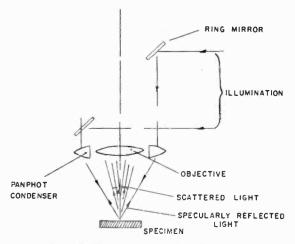

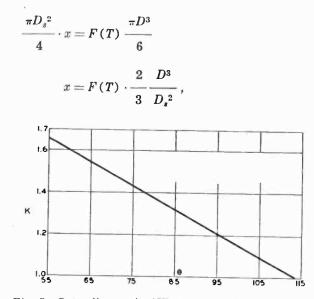

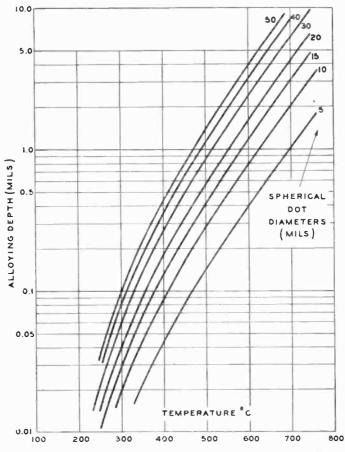

#### THE ALLOY JUNCTION<sup>†</sup>

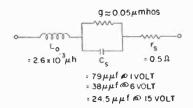

The rectifying properties of the p-n junction were derived theoretically some years ago.<sup>7</sup> Shockley's application of such junctions to an amplifying device came much later<sup>8</sup>; in the Shockley patent,<sup>1</sup> reference is made to diffusing an impurity into a semiconductor so as to produce a junction. A diffusion technique for making rectifying junctions was more fully described by Hall and Dunlap,<sup>9</sup> but subsequent publications from the same laboratory indicate that diffusion in the solid state is extremely small.<sup>10, 11</sup> Successful methods for making transistor junctions may utilize a different technique involving alloying. This has already been recognized<sup>2, 3</sup> and is confirmed by experimental evidence to be discussed in the present paper.

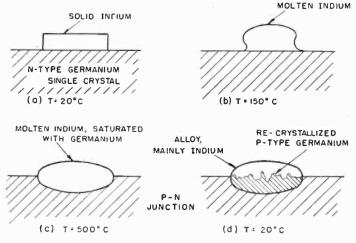

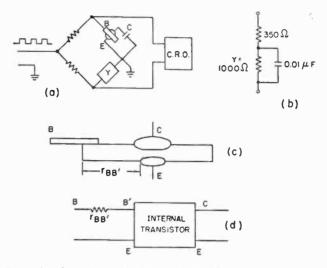

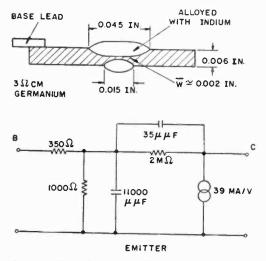

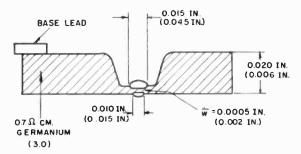

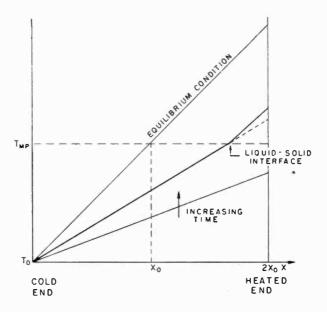

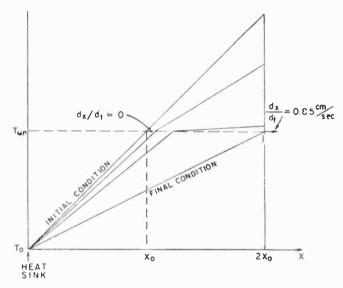

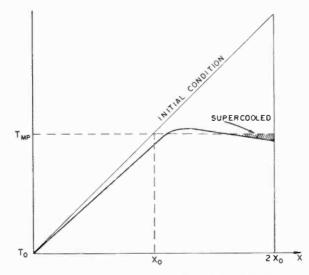

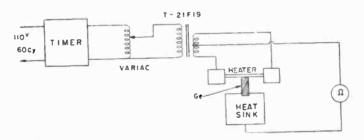

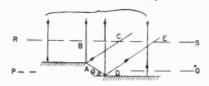

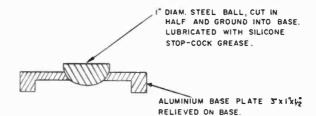

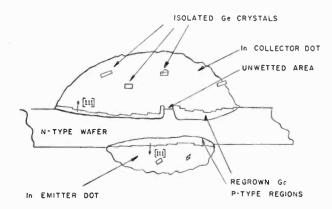

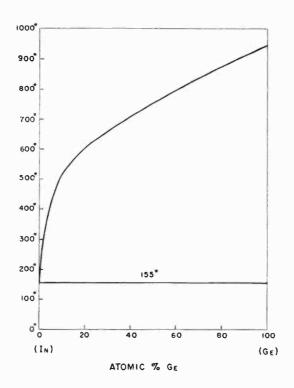

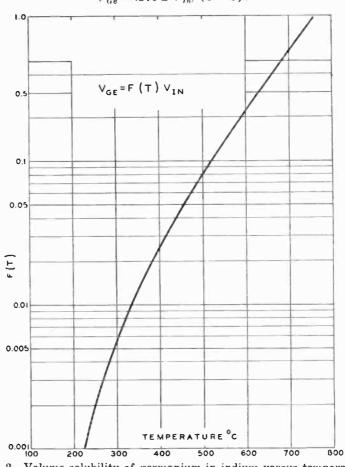

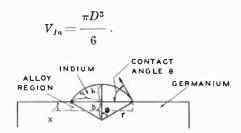

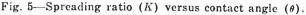

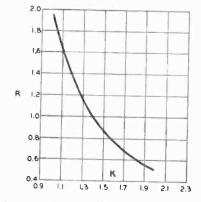

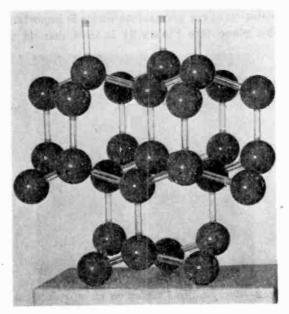

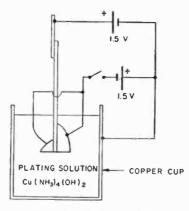

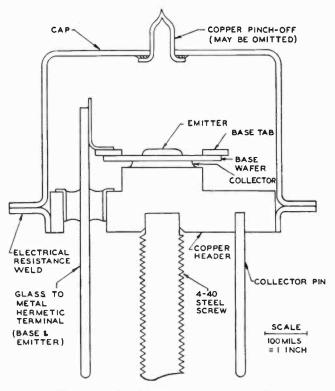

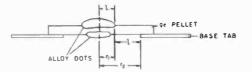

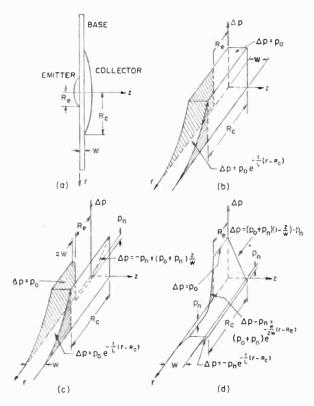

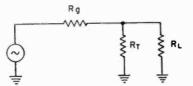

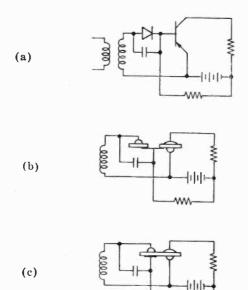

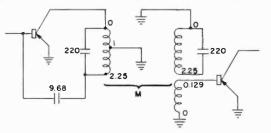

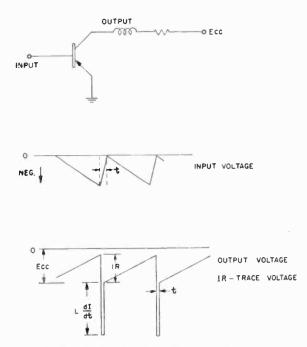

Figure 1 shows the steps which take place in forming a junction by the alloy process, for example, using n-type, single-crystal germanium and indium as an impurity. In Figure 1(a) a piece of indium is placed on the germanium. The temperature is raised (Figure 1(b)) and the indium melts. Germanium is soluble in liquid indium, the solubility depending on the temperature. When the temperature is further raised, as in Figure 1(c), enough of the germanium is dissolved in the indium to cause a small depression in the crystal. In principle, the size of this depression does not depend on the time (provided equilibrium is reached in the germanium-indium solution) but only on the area, the volume, and the highest temperature reached by the molten indium. Subsequent lowering of the temperature reduces the solubility of germanium in the indium and the germanium crystallizes out, in indium-contaminated, p-type form. The important factor at this stage is that the nucleation centers come from the original single-crystal base. As a result, the p-type germanium recrystallizes in single-crystal form on top of the base material, and in crystallographic alinement with it. The p-n junction forms at approximately the original solid-liquid interface as a flat, abrupt transition of the Schottky type (Figure 1(d)). The

<sup>9</sup> R. N. Hall and W. C. Dunlap, "p-n Junctions Prepared by Impurity Diffusion," *Phys. Rev.*, Vol. 80, p. 467, November 1, 1950.

<sup>10</sup> W. C. Dunlap, "Measurement of Diffusion in Germanium by Means of p-n Junctions," *Phys. Rev.*, Vol. 86, p. 615, April-June, 1952.

<sup>&</sup>lt;sup>†</sup> Some of the research referred to in this section was done by J. Pankove, "Recrystallization of Germanium from Indium Solution," *RCA Review*, Vol. 15, pp. 78-85, March, 1954.

<sup>&</sup>lt;sup>7</sup> B. Davydov, "On the Rectification of Current at the Boundary between Two Semiconductors," C. R. Acad. Sci. (U.S.S.R.), Vol. 21, p. 279, 1938.

<sup>&</sup>lt;sup>8</sup> W. Shockley, "The Theory of p-n Junctions in Semiconductors and p-n Junction Transistors," *Bell Sys. Tech. Jour.*, Vol. 28, p. 435, July, 1949.

<sup>&</sup>lt;sup>11</sup> J. S. Saby and W. C. Dunlap, "Impurity Diffusion and Space Charge Layers in 'Fused-Impurity' p-n Junctions," *Phys. Rev.*, Vol. 90, p. 630, May 15, 1953.

resistivity of the recrystallized p-type germanium is about 0.001 ohmcm, so that it forms an excellent emitter of holes into n-type material of 1 to 3 ohm-centimeter.

It is to be emphasized that, in principle, the position and shape of the junction are closely controllable by variation of the contact area, the volume of indium, and the maximum firing temperature. In practice, surface wetting is a possible variant which must also be controlled. Also of note is that any solid-state diffusion will play only a minor part in the junction position, changing it perhaps by a few tens of angstrom units.

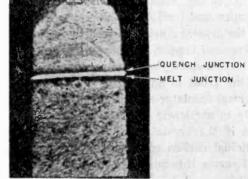

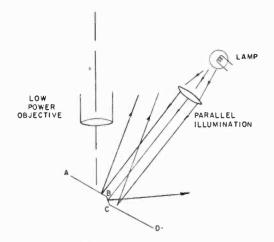

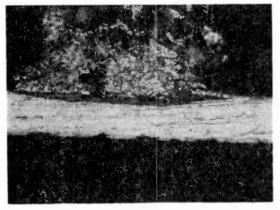

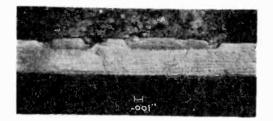

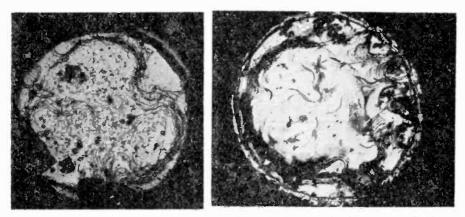

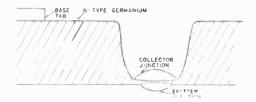

The first evidence to indicate the nature of the alloy process was obtained by embedding an actual junction in plastic, cutting it in

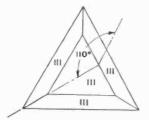

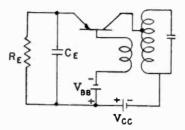

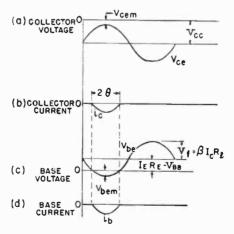

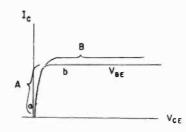

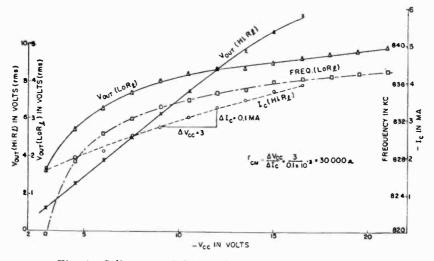

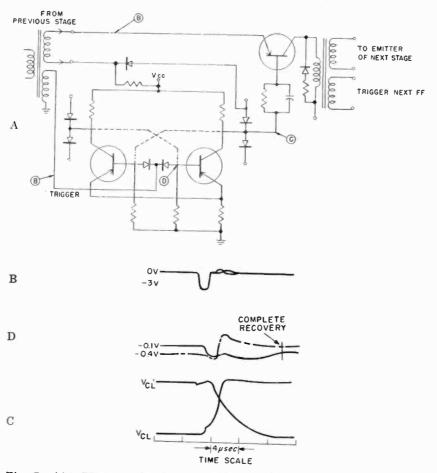

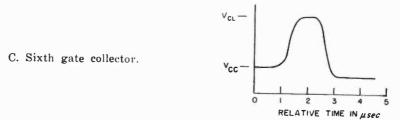

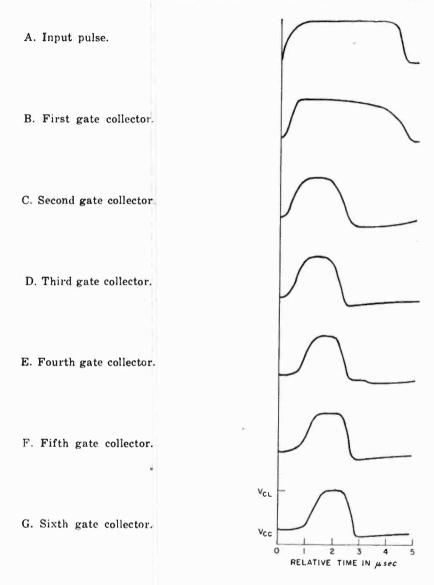

Fig. 1-Steps in the formation of an alloy junction.

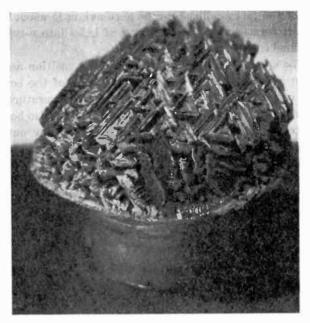

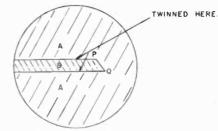

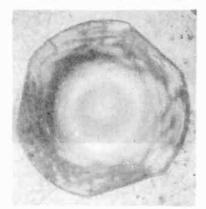

cross section and studying it under a microscope. Better results were obtained by first dissolving out the indium with mercury followed by a final nitric acid wash. Some interesting pictures were also made of a rod-like, n-type, germanium crystal after it was dipped into molten indium, allowed time for equilibrium, and then cooled to room temperature. Correct choice of crystal direction in the rod permitted observation of recrystallized germanium on several crystal faces. After removing the indium, the end of the rod looked as in Figure 2. The typical crystal structure of the base material is clearly evident in the recrystallized germanium. A view from another angle, i.e., another crystal face, is shown in Figure 3. X-ray diffraction studies confirmed the basic single-crystal nature of the entire specimen.

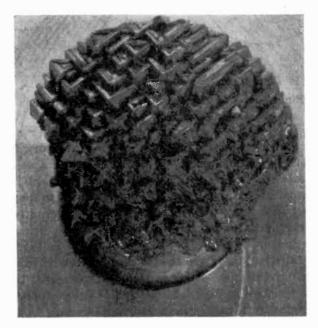

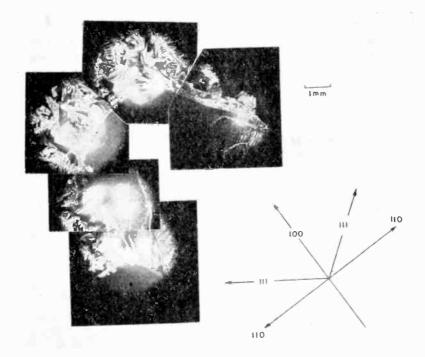

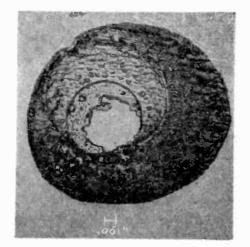

After these photographs were taken, the end of the rod was cut in

29

Fig. 2—View of end of single-crystal germanium rod after recrystallization from an indium melt and removal of the indium.

Fig. 3-Same rod as shown in Figure 2 viewed from another angle.

cross section, etched, and a series of low-power microscope pictures taken, to form the montage of Figure 4. The various crystal axes are identified by the arrows. By means of thermal probes it was found that a p-n junction had formed at a sharp line at about the boundary of the unmelted germanium. This junction line is visible in Figure 4 and is particularly clear at the (110) faces. The junction is more obscure at the (100) face. Although it may be only a coincidence, it is of interest that this crystal orientation is often avoided by those

Fig. 4—Montage of cross-sectional views of end of rod shown in Figures 2 and 3. The p-n junction is seen as a fine white line inside the recrystallized portion.

making alloy transistors because it is said to yield less satisfactory junctions.

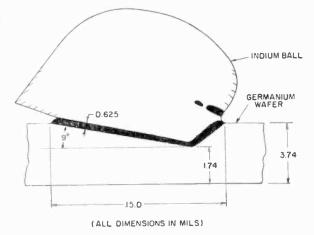

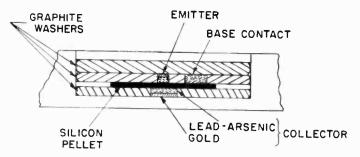

## THE ALLOY JUNCTION TRANSISTOR

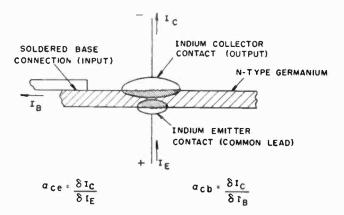

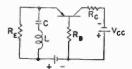

The p-n-p alloy junction transistor is made by using two such junctions on opposite sides of a thin germanium wafer. In cross section, a transistor is shown in Figure 5. Ordinarily, at least at low frequencies, an input signal is connected to the base lead, the output is taken from the collector, and the emitter, like the cathode of the electron

#### TRANSISTORS 1

tube, is the common connection. The simplest single criterion of performance applicable to the junction transistor is its value of  $\alpha$ , or current-gain factor. This is because any change in emitter current, which fails to reach the collector, contributes to a change in base current and this must be supplied in the form of input power. Ordinarily one thinks of two such current-gain factors,  $\alpha_{ee}$ , the ratio of collectorcurrent change to emitter-current change, and  $\alpha_{eb}$ , the ratio of collectorcurrent change to base-current change. We want  $\alpha_{ee}$  to be unity and  $\alpha_{eb}$  to be infinite. It is frequently most convenient to use  $\alpha_{eb}$  because it is a more sensitive parameter than the other.

If  $\alpha_{cb}$  is to be large, every source of base current must be a minimum. In the main, there are three sources: one is due to imperfect emitter efficiency, a second is bulk recombination of the injected holes in the

Fig. 5—Cross-sectional view of a p-n-p alloy junction transistor.

n-type base, and the third is surface recombination on the free surfaces of the base material. Let us examine these in turn.

Any part of the emitter current carried by electrons will not be able to arrive at the collector, and so represents base current. Primarily, this electron current is due to the free electrons in the n-type base. However, if the base conductivity is very small compared with the emitter conductivity, the emitter efficiency will be high. In the alloy transistor the emitter to base conductivity ratio is of the order of 10<sup>3</sup>. Except for the high-current-density case (e.g., power transistors), which will be examined later, a first approximation allows one to neglect emitter efficiency as a major source of base current.

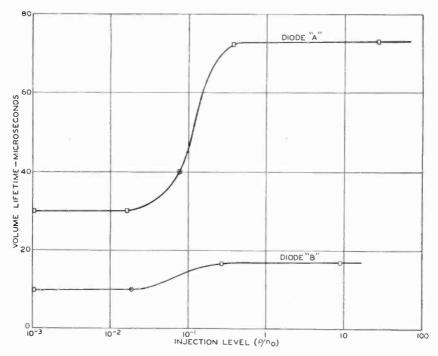

Appreciable bulk recombination (i.e., short lifetime of minority carriers) in the base material prevents some of the injected holes from

arriving at the collector. In most transistor theory, this source of base current is emphasized. However, experience with the low-power alloy transistor indicated that bulk lifetimes of 5, 100, or 1000 microseconds alike gave equally good results. Since it is a poor sample of germanium indeed whose lifetime does not fall above 5 microseconds, one must assume that bulk recombination, again to a first approximation, is not a major source of base current in practical alloy transistors.

We are left with surface recombination to explain the base current in the alloy transistor. Early experiments showed that surface treatment of these units was one of the most crucial and critical parts of the processing technique, and confirm that this source of recombination is a major item in determining  $\alpha$ .

Figure 5 shows why the surface may play such an important role. It is observed that the over-all transistor geometry is not parallel plane, as hitherto assumed in most transistor theory. Also one notes that the collector is larger than the emitter. The latter feature was incorporated because it was found to lead to high and more uniform values of  $\alpha$ , and it is clear that it results in capturing much of the hole current at the top of the figure which might otherwise be surface recombination current. It is also seen that there is appreciable surface area surrounding both emitter and collector.

In the next section of the paper, the special geometry of the alloy transistor will be examined in the light of surface recombination, in order to explain observed values of  $\alpha$ . Fortunately, with bulk recombination neglected, all conditions are on the boundaries and powerful analogue methods can be employed to effect a practical solution.

## EFFECT OF GEOMETRY ON ALPHA\*

The minority carriers (holes) flow in the base region primarily as a result of diffusion. The diffusion equation tells us that the current density in the base region is proportional to the gradient of the charge density. Thus

$$I = -qD_p \nabla P, \tag{1}$$

where q is the charge of a "hole,"  $D_p$  is its diffusion constant, and P is the excess hole density, i.e., the hole density in excess of the thermal equilibrium value. Taking the divergence of each side

div

$$I = -qD_p \nabla^2 P$$

.

<sup>\*</sup>See Moore and Pankove, Reference (4). For later work, see K. E. Stripp and A. R. Moore, "The Effects of Junction Shape-Part II," Proc. I.R.E., Vol. 43, pp. 856-866, July, 1955.

In the steady state, if there is no bulk recombination,  $\operatorname{div} I = 0$  throughout the solid, so that

$$\nabla^2 P = 0, \tag{2}$$

a well-known equation for which powerful solution methods are available.

Let us compare this Laplace equation with one similarly derived for a conducting solid of bulk resistivity  $\rho$ . If  $\phi$  is the potential.

$$i = -1/\rho \nabla \phi, \tag{3}$$

$$\operatorname{div} i = -(1/\rho) \nabla^2 \phi = 0. \tag{4}$$

We see, then, an analogy in which  $1/\rho$  corresponds with  $qD_p$ , and the potential corresponds with excess hole density.

To solve either the transistor or its conducting solid analogue, the boundary conditions must be set up. For the transistor,  $P = P_0$ , a constant over the emitter electrode surface and, for the usual highly efficient collector surface P = 0. In the analogue, corresponding surfaces are connected to a battery which places the emitter analogue at a potential  $\phi_0$ , the collector at potential zero. At the free semiconductor surface, if there were no surface recombination, there would be no current flow into this surface; the electrical analogue is an insulating surface. When surface recombination takes place, a current density flow proportional to the total charge, qP, takes place

$$I = qPs \tag{5}$$

where s is the proportionality constant, known as the surface recombination velocity. In the electrical analogue, such a surface current can be caused to flow by placing many small electrodes over the entire free surface, and connecting them through resistances back to the zero of potential. If A is the area of each small electrode, and R the value of each resistance, the surface current density is

$$i = \frac{1}{AR} \phi. \tag{6}$$

Simple division of the normal component of the general current Equations, (1) and (3) by the surface-current Equations (5) and (6) shows that

$$\frac{\nabla P_n}{P} = -\frac{s}{D_p} \tag{7}$$

and

$$\frac{\nabla \phi_n}{\phi} = -\frac{\rho}{AR} \,. \tag{8}$$

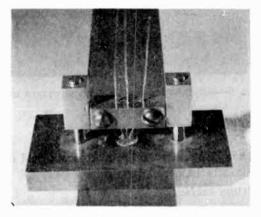

By making  $\rho/AR$  equal to  $s/D_p$  the analogy is preserved. We could solve the transistor equation, then, by building a solid conducting model, attaching a battery and measuring the ratio of collector current to emitter or base current.

Fortunately, the thin wafer geometry is such that the powerful tools of two-dimensional analogue solutions, such as the electrolytic tank or conducting sheet, can also be used. Figure 6 shows the cross section of a transistor, together with a conducting sheet analogue. If  $s/D_p$  is made equal to  $\rho_s/aR$ , where  $\rho_s$  is the surface resistance of the conducting sheet, and a is the length of each free boundary segment, the analogy is approximately applicable. The current-flow lines of the analogy are hole-flow paths in the transistor. To take into account the circular nature of the actual transistor surfaces, we may find the current density at each radius in the model and calculate the over-all emitter and collector current by weighting each current density value by  $2\pi r$ . Thus the corrected total emitter current is

$$i_e = \int_0^{r_e} 2\pi r i_e(r) \, dr,$$

and the total collector current

$$i_o = \int_0^{r_o} 2\pi r i_o(r) \, dr,$$

where  $r_c$  and  $r_c$  are maximum radii of emitter and collector electrodes. The ratio  $i_c/i_e$  is  $\alpha_{ce}$  so that  $\alpha_{cb}$  is readily computed as well.

Although not employed in the present investigation, it is clear that the resistance network analogy board<sup>12</sup> would permit a direct measurement of the cylindrical geometry; in addition, there is enough flexibility to allow the introduction of bulk recombination effects by use of bleeder resistors plugged in at intermediate points between emitter and collector.

<sup>&</sup>lt;sup>12</sup> G. Liebmann, "Electrical Analogues," British Journal of Applied Physics, Vol. 4, p. 193, July, 1953.

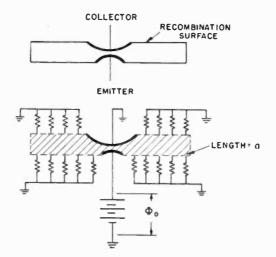

Fig. 6-Two-dimensional analogy to transistor using a conducting sheet. The transistor cross section is shown above, the analogy arrangement below.

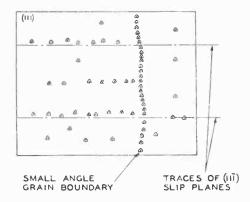

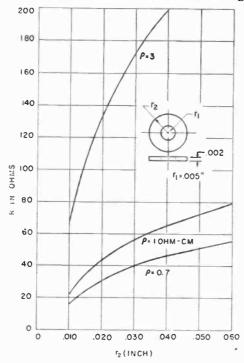

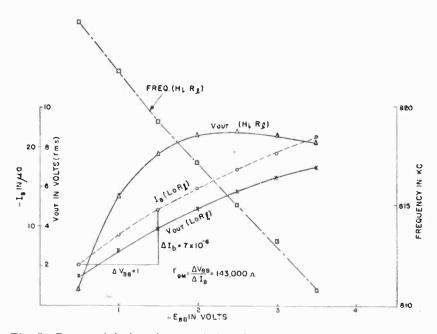

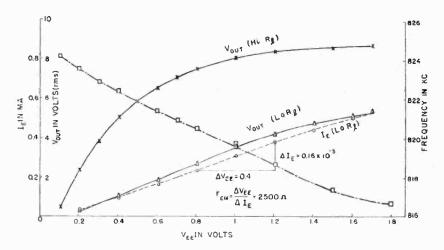

Returning to the resistance-paper solution, Moore and Pankove took data on a variety of geometries and surface conditions.<sup>4</sup> In Figure 7, a hole-flow map for a typical transistor geometry is shown. One junction is 0.045 inch in diameter, the other 0.015 inch, and the minimum

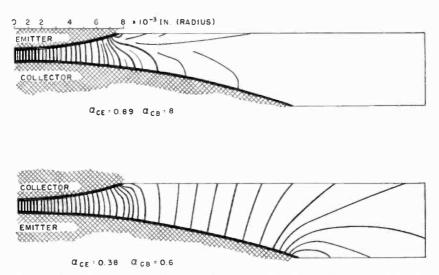

Fig. 7—Hole-flow maps with a surface recombination of 5000 centimeters per second. The upper figure shows normal connection of emitter (0.015inch diameter) and collector (0.045-inch diameter); the lower figure shows these connections reversed, i.e., collector diameter 0.015 inch, emitter diameter 0.045 inch. separation is 0.001 inch. Two plots are shown, corresponding to normal and reverse connections of emitter and collector. A surface recombination velocity of 5000 centimeters per second was chosen to correspond with some early transistor data. The surface currents are clearly delineated. The calculated collector-to-base  $\alpha$  value was 8 in the normal connection, but only 0.6 in the reverse connection.

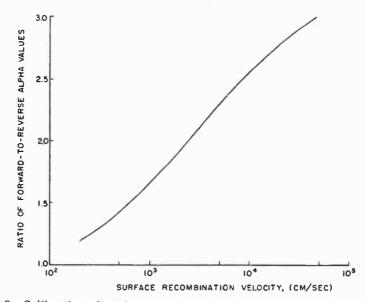

If there were no surface recombination, the normal and reverse  $\alpha$  values would be the same. We arrive, therefore, at a very interesting suggestion. By measuring the ratio of forward-to-reverse  $\alpha$  values in an actual transistor, we have a quantitative measure of the surface

Fig. 8—Calibration of surface recombination for unsymmetrical transistors with 0.015-inch emitter, 0.045-inch collector, 0.001-inch minimum junction spacing and 0.0022-inch average junction spacing.

recombination. The electric analogue solution may be used to supply the calibration curve.

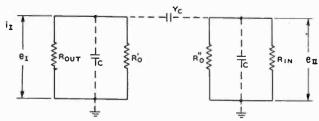

Figure 8 shows such a calibration curve, calculated for a minimum junction spacing of 0.001 inch (average spacing of 0.0022 inch), and for the typical geometry with one 0.045 inch and one 0.015 inch junction. In practice, transistors vary in both junction spacing as well as surface recombination, and both factors affect  $\alpha$ . However, measurement of the emitter-to-base diffusion capacitance, to be discussed later in this paper, permits an independent evaluation of junction spacing. The forward-to-reverse  $\alpha$  ratio, in conjunction with the diffusion

#### TRANSISTORS I

capacitance, provides a means of quantitatively determining junction spacing and surface recombination velocity, even in a finished and already encapsulated transistor.

Many actual transistors have been measured, and it is found that the surface recombination velocity varies from as little as a hundred to many thousands of centimeters per second. Very instructive experiments have been performed with a given transistor, open to the air, by observing forward-to-back  $\alpha$  values while the surface treatment is varied.<sup>4</sup>

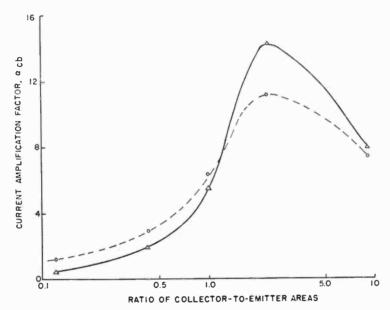

Fig. 9—Comparison of experimental and calculated values of  $\alpha$  for p-n-p transistor with various area ratios. Largest junction diameter is always 0.045 inch. Surface recombination is 5000 centimeters per second. Average junction spacing is 0.0022 inch.

Hole-flow maps for different transistor geometries have explained the experimental results which showed the advantage of a large collector area. In Figure 9, the dotted curve shows a series of early experiments by Pankove in which alloy junction transistors were built with varying geometry. Each point is the average of a number of units. It is seen that highest  $\alpha$  value is obtained when the collector area is about twice that of the emitter. The unbroken curve shows the computed values using the current-sheet analogue. Reasonable agreement is found.

It should be noted that lack of exact centering of the two junctions,

in practice, favors a larger area ratio than the optimum one shown in Figure 9. A 3:1 diameter ratio, therefore, has been widely used. Because modern alloy transistors with a 3:1 diameter ratio are found to have surface recombination velocities below 500 centimeters per second, the  $\alpha$  values are in the range up to a hundred. The difference over early units is entirely due to improved etching and surface treatment.

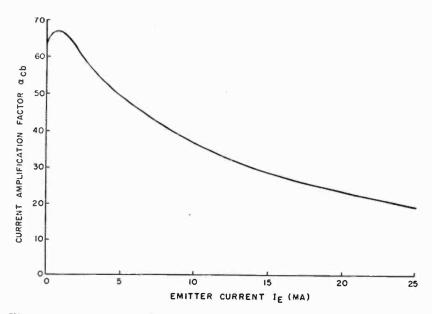

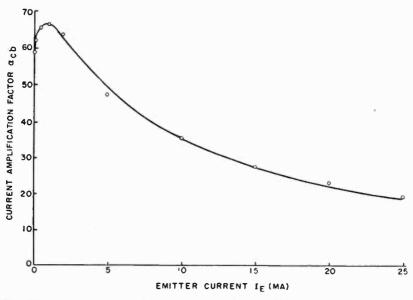

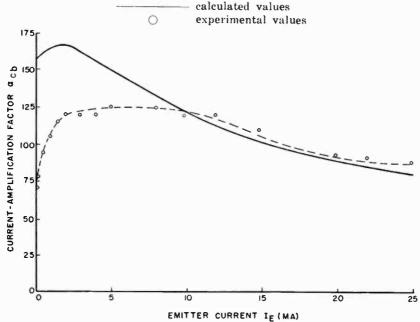

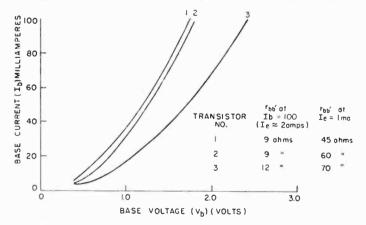

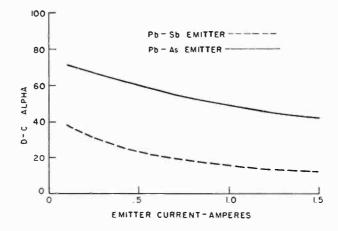

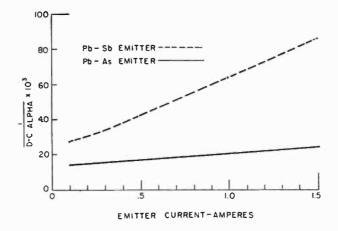

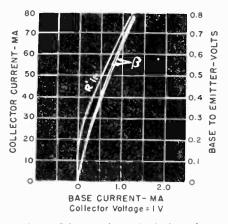

Fig. 10—Curve showing how  $\alpha$  varies with emitter current in p-n-p alloy junction transistor. Collector diameter 0.045 inch, emitter diameter 0.015 inch.

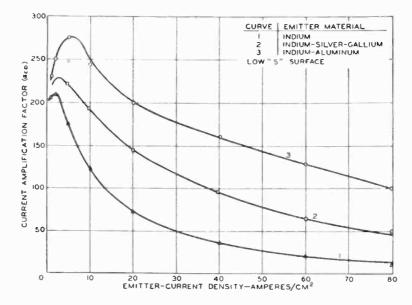

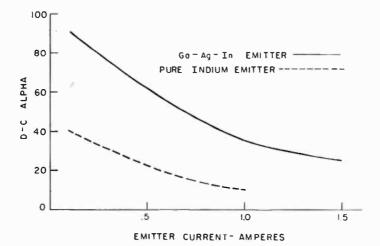

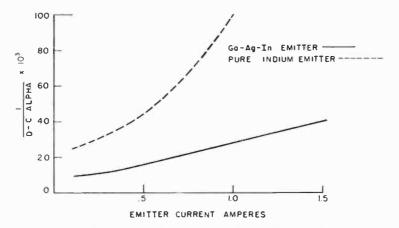

#### EFFECT OF EMITTER CURRENT ON ALPHA\*

Up to this point, transistor current gain,  $\alpha$ , has been discussed under what might be called low-power conditions, i.e., the minority carrier charge density in the base region does not greatly exceed the donor concentration. In power transistors this is not always the case. If the collector-to-base current-amplification factor of a typical p-n-p alloy unit is measured, a curve similar to that shown in Figure 10 is obtained when the emitter current is varied. Low-power operation is below a few milliamperes and high  $\alpha$  values are found. At high currents, the  $\alpha$  value falls off substantially.

<sup>\*</sup>The research referred to in this section was undertaken by W. M. Webster, Reference (4).

# TRANSISTORS I

It is of interest to derive a relationship for  $\alpha$  in terms of emitter efficiency, surface and bulk recombination and then to examine how these terms may vary when the emitter current density is increased. To make the problem amenable to solution, suitable approximations will be made, such as parallel-plane geometry; judicious interpretation makes the results applicable to the alloy transistor as well.

In Figure 5 a junction transistor is shown. An input variation on the base causes a collector current variation in the load, and we are interested in the ratio of the two current variations. The direct currents are  $I_E$ ,  $I_B$ , and  $I_C$ . The emitter current is comprised of two parts, that due to holes,  $I_{Ep}$ , and that due to electrons,  $I_{Ee}$ ,

$$I_E = I_{Ep} + I_{Ec}$$

With high emitter-to-base conductivity ratio, however,

$$I_E \simeq I_{Ep}$$

.

The base current is the sum of the three factors discussed in an earlier section,

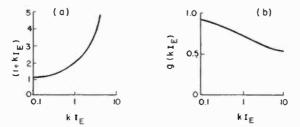

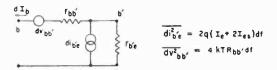

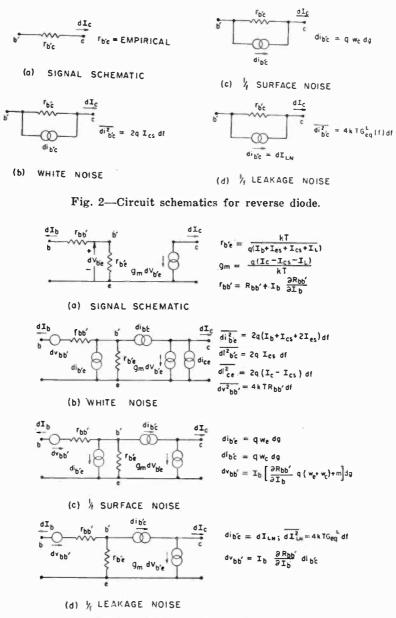

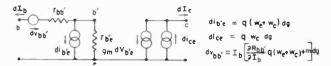

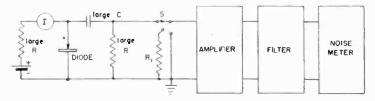

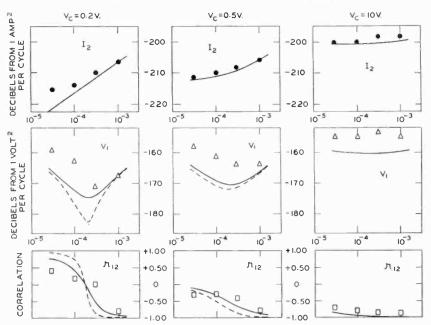

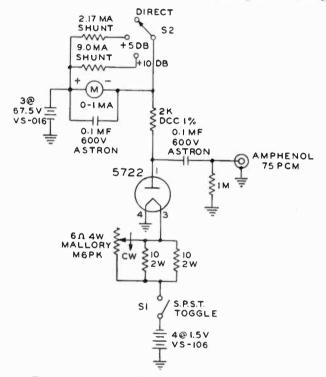

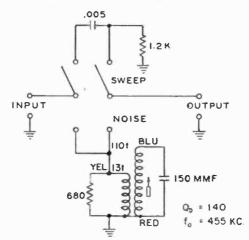

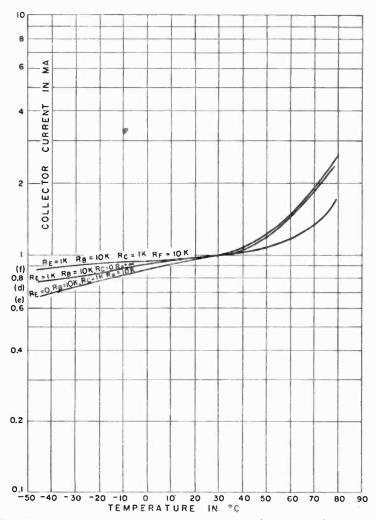

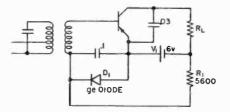

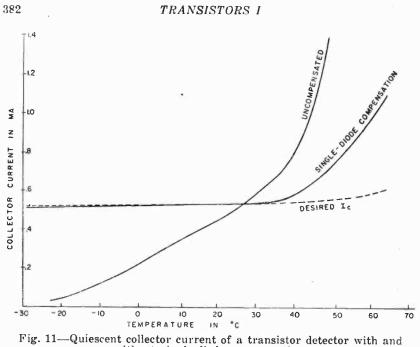

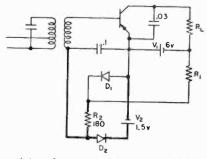

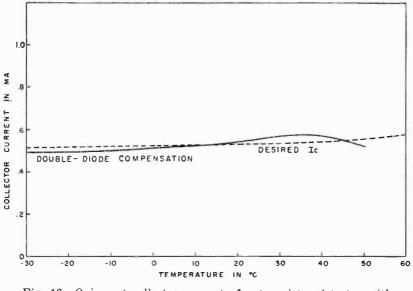

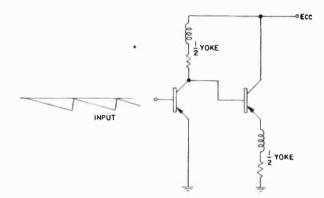

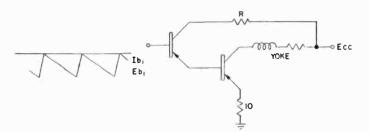

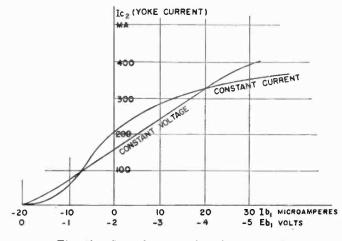

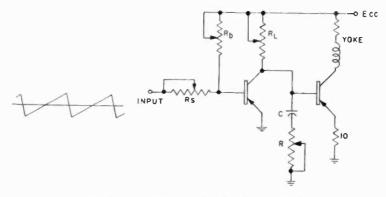

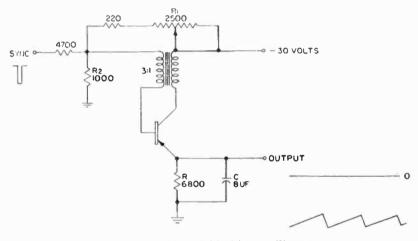

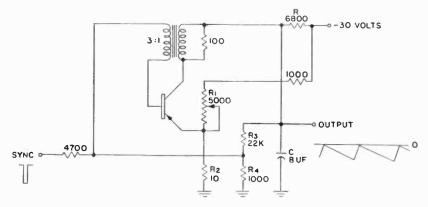

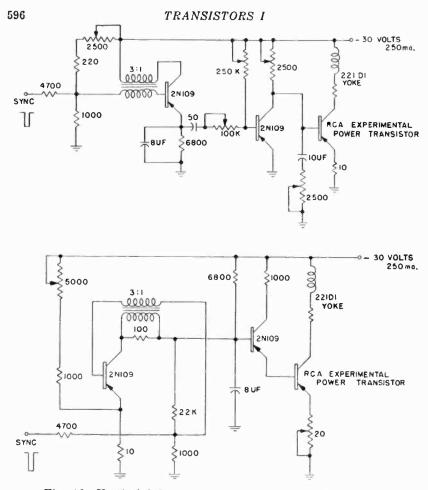

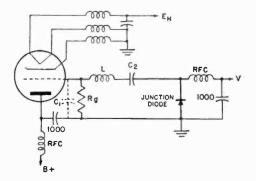

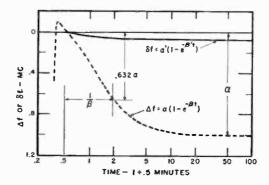

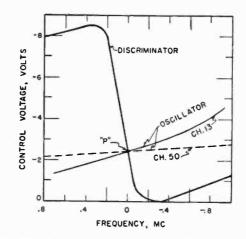

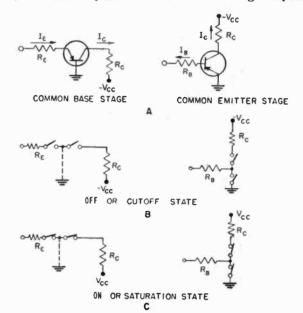

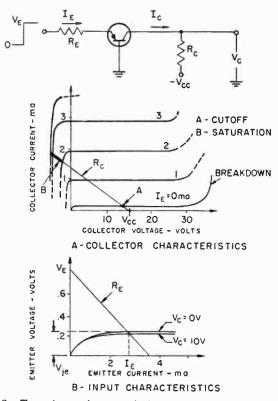

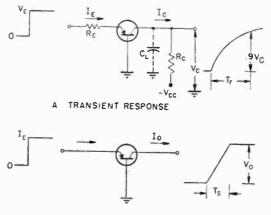

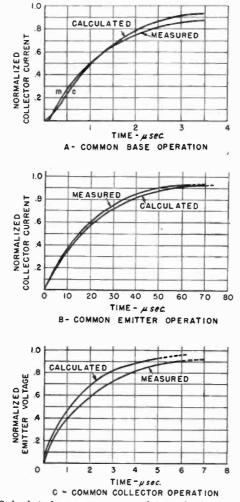

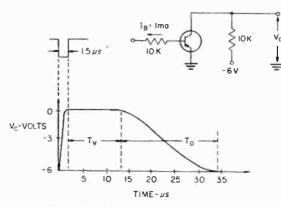

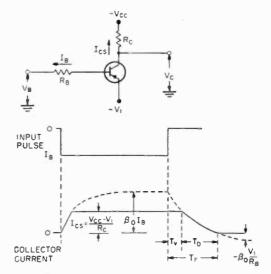

$$I_b = I_{Ec} + I_{VR} + I_{SR},$$