# Digitals in Broadcasting

by

Harold E. Ennes

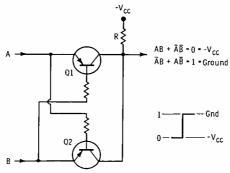

Howard W. Sams & Co., Inc. 4300 WEST 62ND ST. INDIANA 96268 USA Copyright © 1977 by Howard W. Sams & Co., Inc. Indianapolis, Indiana 46268

FIRST EDITION FIRST PRINTING-1977

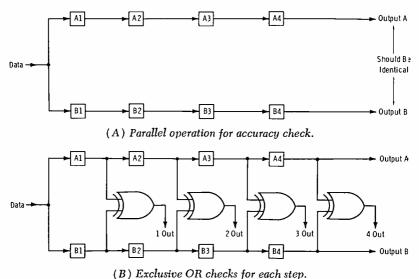

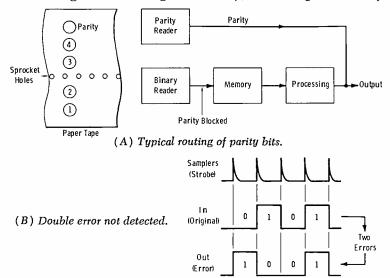

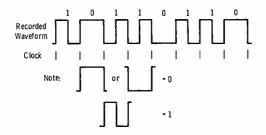

All rights reserved. Reproduction or use, without express permission, of editorial or pictorial content, in any manner, is prohibited. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

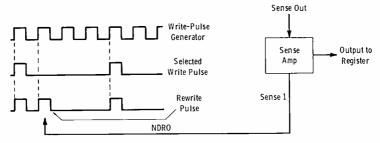

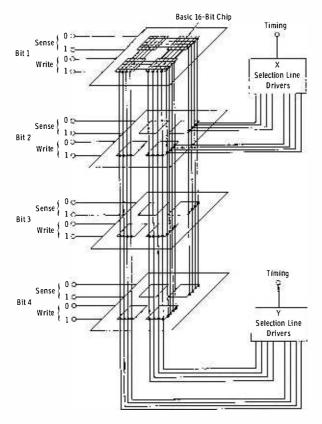

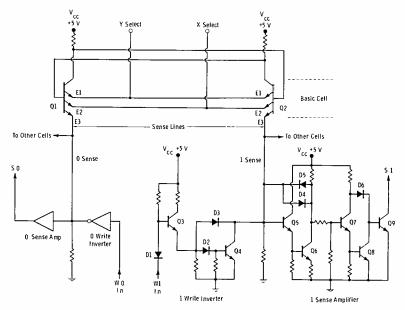

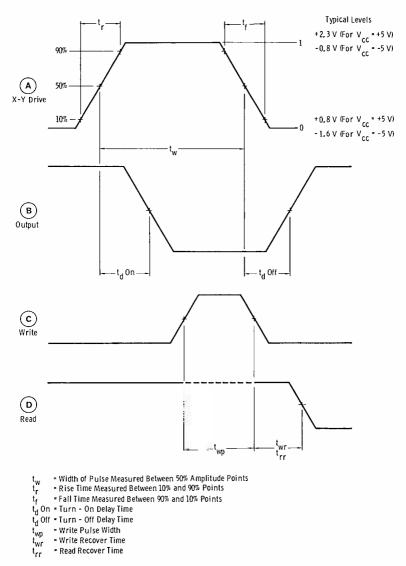

International Standard Book Number: 0-672-21414-8 Library of Congress Catalog Card Number: 77-73922

Printed in the United States of America.

## Preface

Digital systems as considered in this book are currently being used in two broad areas of application: (1) digital control of analog systems and (2) digitized audio and video equipment for specific purposes. Digital control has been with us for some time, but it is still not thoroughly understood by many in the communications field. Digitized audio and video is an entirely new field at the time of this writing, and it promises to revolutionize system concepts. Digital processing of analog signals can perform many tasks that are difficult or impossible to achieve by strictly analog techniques.

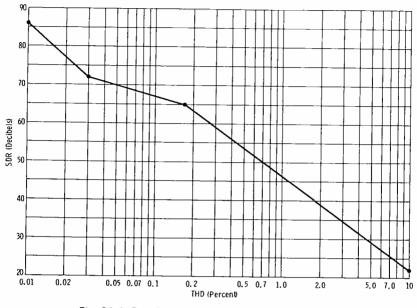

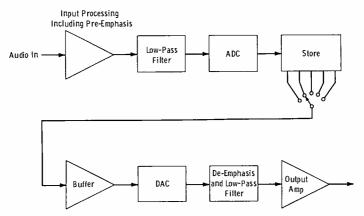

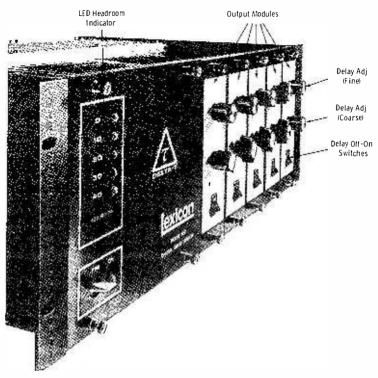

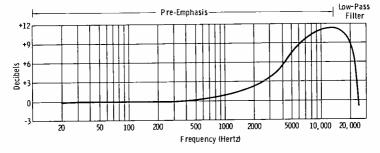

Like stereo in fm and color in tv, digitals are emphasizing the continual need for technicians to update their knowledge. Unfortunately, because of the rapid influx of digital devices into the broadcasting, recording, and general communications fields, students and practicing technicians have been faced with a scarcity of necessary background information relative to digital technology. *Digitals in Broadcasting* has been written to meet the need for a practical source of such information.

This text is *not* a rigorous treatment of the field of digitals. Rather, it is slanted to the practicing technician (or student) who has not had formal computer training. A simple building-block approach is used to provide a practical and effective marriage of analog and digital worlds in the mind of the reader who has had little or no exposure to digital technology. As such, the treatment is as basic as possible, while providing the necessary engineering background to enable a technician to feel more at home with the instruction books that accompany modern digital equipment. Computer training, in itself, is not geared to the specific needs of the broadcast and general communications aspects of digital technology. While computertype equipment is involved, the practical applications are different. I have, therefore, deliberately bypassed many details relative to spe-

#### PREFACE

cific computer applications and have emphasized only those characteristics of analog-digital functions most important to the intended field.

Besides serving as a basic reference, this book will provide a quick refresher course for the more advanced digital technician. A basic electronics background is assumed.

It is my sincere wish that this text not only will serve as an effective introduction to digital techniques, but also will inspire the reader to more advanced studies in the field. Equipment will change with new discoveries and improved techniques; however, the fundamental steps taken in this book will serve as a solid foundation for a continued training program. Comments and constructive criticisms by readers are welcomed.

Acknowledgments: A technical book carrying a single author's name is almost always the result of research and development from many different sources: individuals, companies, and technical organizations. This is certainly true of this book. My purpose has been to coordinate basic theory with the original research and development accomplished by others, and to organize this material into an effective and practical training program for the intended reader.

My special thanks to Frank Thompson, J. Diermann, M. O. Felix, Mark Sanders, and Charles Anderson, all of the Ampex Corporation, for their invaluable assistance.

My sincere appreciation is extended to the following companies, corporations, and organizations for their contributions that have made this book possible: Ampex Corp.; Consolidated Video Systems, Inc.; Datavision Video Products Div., 3M Co.; Electronic Engineering Co. of California; Hewlett-Packard; Ikegami Electronics (USA), Inc.; Lexicon, Inc.; Moseley Associates, Inc.; Oliver Audio Engineering; Philips Broadcast Equipment Corp.; SMPTE Journal; TeleMation, Inc.; and Visual Electronics Corp.

HAROLD E. ENNES

## Contents

## CHAPTER 1

| ORIENTAT | ION IN BITS, BYTES, BAUDS, AND BANDWIDTH | • |   | • | . 11 |

|----------|------------------------------------------|---|---|---|------|

| 1-1.     | Introduction to the Binary System        | • | • | • | 12   |

| 1-2.     | Signaling Speed Versus Bits per Second   | ٠ | • | · | 13   |

| 1-3.     | Pulse Formats                            | • | · | • | 15   |

| 1-4.     | Basic Digital System Theory              | • | ٠ | • | 17   |

| 1-5.     | Automation                               | • | ٠ | · | 21   |

| 1-6.     | Remote Control of Transmitters           | • | ٠ | · | 23   |

| 1-7.     | Digitized Audio and Video                | • | • | • | 24   |

## CHAPTER 2

| Binary M | Гатн                                      | • |   | • |   | . 28 |

|----------|-------------------------------------------|---|---|---|---|------|

| 2-1.     | Thinking Binary                           | • | • | • | • | 28   |

| 2-2.     | The Bistable Flip-Flop                    | • | • | • | • | 28   |

| 2-3      | Powers of Numbers (Exponents)             | • |   |   |   | 31   |

| 2-4.     | Adding Binary Zeros and Ones              | • | • | • | • | 33   |

| 2-5.     | Subtracting Binary Zeros and Ones         | • | ٠ | ٠ | • | 35   |

| 2-6.     | Handling Positive and Negative Binaries   | • |   | • | • | 37   |

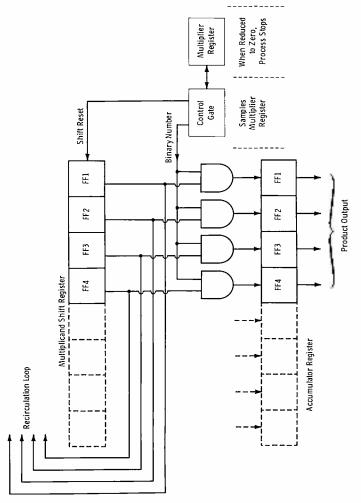

|          | Binary Multiplication                     |   |   |   |   | 40   |

| 2-8.     | Binary Division                           | • | • | ٠ | • | 43   |

| 2-9.     | Converting and Simplifying Number Systems |   | • |   | • | 45   |

| 2-10.    | The Flexible Binary                       |   |   |   | • | 49   |

## CHAPTER 3

---

|      |                  |  |   |   |   |   |   |   |   |   |   |   |   |    | 52 |

|------|------------------|--|---|---|---|---|---|---|---|---|---|---|---|----|----|

|      | Prerequisite     |  |   |   |   |   |   |   |   |   |   |   | • |    |    |

| 3-2. | Logic Statements |  | • | • | • | • | • | • | • | ٠ | ٠ | • | · | 52 |    |

| 3-3.  | The Connective (Operator) AND     |     |    |   |   |   |   |   |   | 53 |

|-------|-----------------------------------|-----|----|---|---|---|---|---|---|----|

| 3-4.  | The Connective on                 |     |    |   |   |   |   |   |   | 55 |

| 3-5.  | Variations on the Connective AND  |     |    |   |   |   |   |   |   | 58 |

| 3-6.  | Variations on the Connective on   |     | ÷  |   |   |   |   |   | · | 61 |

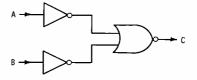

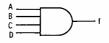

| 3-7.  | Equivalences (Duality) of Logic ( | Gat | es |   | ÷ | · |   |   | • | 63 |

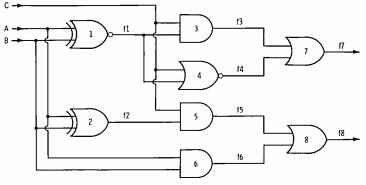

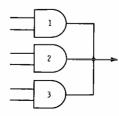

| 3-8.  | Logic Networks                    |     |    |   | ż |   |   |   | • | 64 |

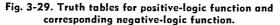

| 3-9.  | Negative Logic                    | ÷   |    |   |   |   |   | • | • | 71 |

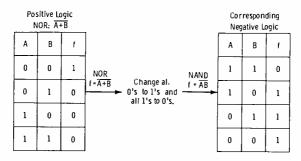

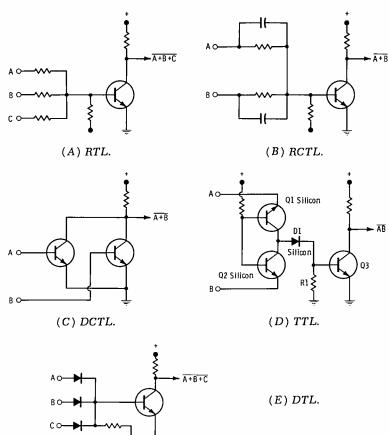

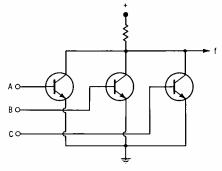

| 3-10. | Logic Families                    |     |    |   |   | ÷ | · | • | • | 72 |

| 3-11. | Interfacing Logic Families        |     |    |   | ż |   |   |   |   | 75 |

| 3-12. | Fanout Capability                 | ÷   | ÷  | ÷ |   | · | • | · | • | 77 |

| 3-13. | How To Read IC Designations .     |     | ·  | ÷ | · | · | • | • | • | 79 |

|       |                                   | -   | •  | • | • | • | • | • | • | 10 |

### **CHAPTER 4**

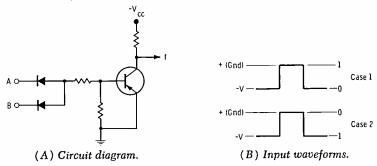

| LOGIC NE | TWORKS WITH FLIP-FLOPS AND ]     | Dīs | PL | AYS |  |   |     | 81 |

|----------|----------------------------------|-----|----|-----|--|---|-----|----|

| 4-1.     | The Toggle                       |     |    |     |  | • | 81  | 01 |

| 4-2.     | The Gated-D Type                 |     |    |     |  |   | 82  |    |

| 4-3.     | The Set-Reset Flip-Flop          |     |    |     |  |   | 81  |    |

| 4-4.     | Ine JK Flip-Flop                 |     |    |     |  |   | 86  |    |

| 4-5.     | Master-Slave Operation           |     |    |     |  |   | 87  |    |

| 4-6.     | The Binary Counter               |     |    |     |  |   | 89  |    |

| 4-7.     | The Decade Counter               |     |    |     |  |   | 93  |    |

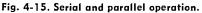

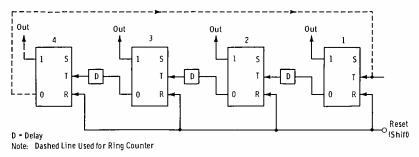

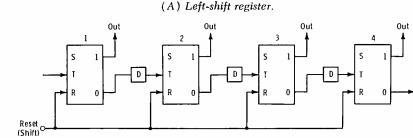

| 4-8.     | Serial and Parallel Operation    |     |    |     |  |   | 93  |    |

| 4-9.     | Shift Registers                  |     |    |     |  |   | 94  |    |

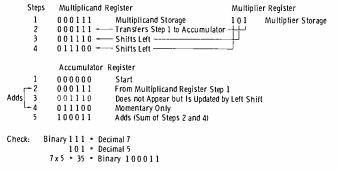

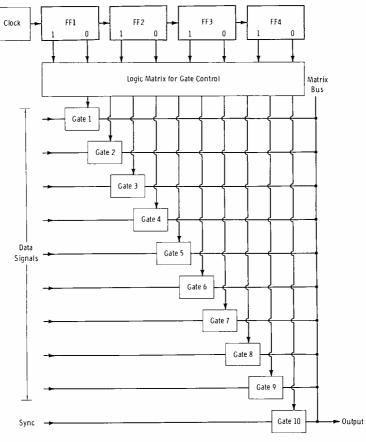

| 4-10.    | The Matrix and Encoding-Decoding | g.  |    |     |  |   | 98  |    |

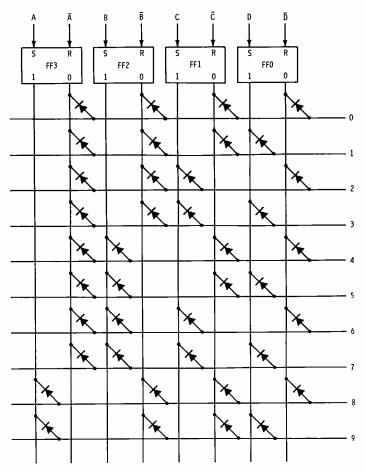

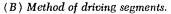

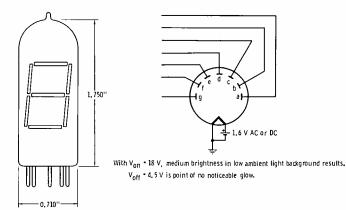

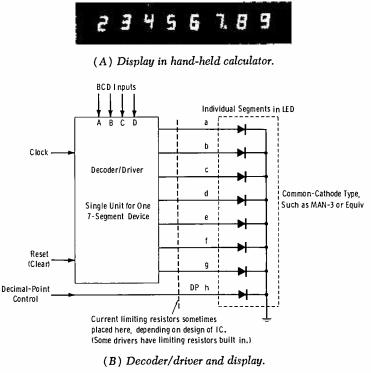

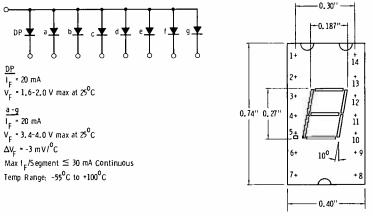

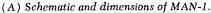

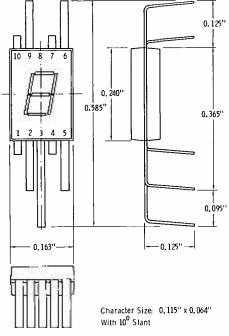

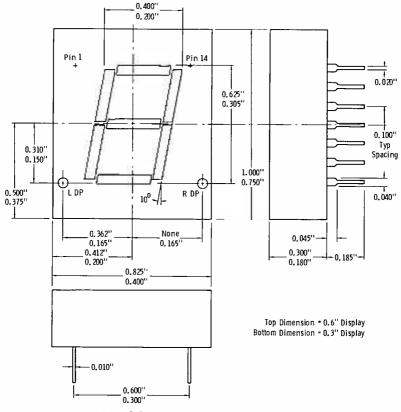

| 4-11.    | Indicating Devices and Circuitry |     |    |     |  |   | 101 |    |

## CHAPTER 5

| DES                  |                                                                                                                                                |                                                                                                                                            |                                                                                                                                               |                                                                                                                                               |                                  |                |                |                |                |                |                |                |                | . 115                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Weighted Codes .     |                                                                                                                                                |                                                                                                                                            | •                                                                                                                                             |                                                                                                                                               |                                  |                |                |                |                |                |                |                |                | 115                                                                                                                                                                                                                                                                                                                                                                                               |

| Nonweighted Codes    |                                                                                                                                                |                                                                                                                                            |                                                                                                                                               |                                                                                                                                               |                                  |                |                |                |                |                |                |                |                | 117                                                                                                                                                                                                                                                                                                                                                                                               |

| Error Detection .    |                                                                                                                                                |                                                                                                                                            |                                                                                                                                               |                                                                                                                                               |                                  |                |                |                |                | ÷              |                |                |                | 117                                                                                                                                                                                                                                                                                                                                                                                               |

| Error Correction .   |                                                                                                                                                |                                                                                                                                            |                                                                                                                                               |                                                                                                                                               |                                  |                |                |                |                |                |                |                | ÷              | 120                                                                                                                                                                                                                                                                                                                                                                                               |

| The ASCII Code .     |                                                                                                                                                |                                                                                                                                            |                                                                                                                                               |                                                                                                                                               |                                  |                |                |                |                |                |                |                |                | 123                                                                                                                                                                                                                                                                                                                                                                                               |

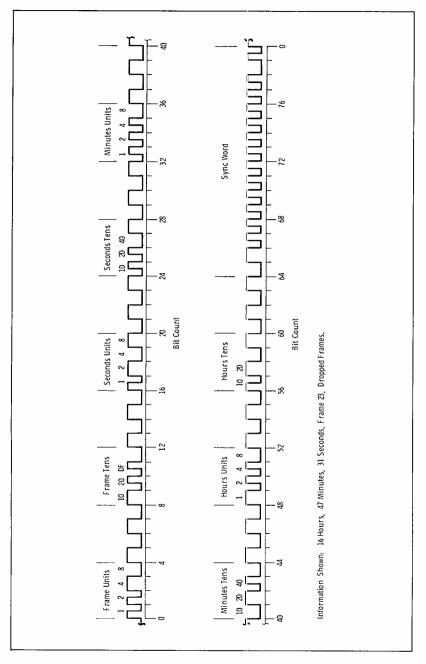

| The SMPTE Code       |                                                                                                                                                |                                                                                                                                            |                                                                                                                                               |                                                                                                                                               |                                  |                |                | ÷              |                |                |                |                | ÷              | 128                                                                                                                                                                                                                                                                                                                                                                                               |

| Efficiency of Coding | S                                                                                                                                              | che                                                                                                                                        | me                                                                                                                                            | s                                                                                                                                             |                                  |                |                |                |                |                |                |                | ÷              | 132                                                                                                                                                                                                                                                                                                                                                                                               |

| Information Capacity | 7                                                                                                                                              |                                                                                                                                            |                                                                                                                                               |                                                                                                                                               |                                  |                |                |                |                |                |                |                |                | 133                                                                                                                                                                                                                                                                                                                                                                                               |

|                      | Weighted Codes .<br>Nonweighted Codes<br>Error Detection .<br>Error Correction .<br>The ASCII Code .<br>The SMPTE Code<br>Efficiency of Coding | Weighted Codes<br>Nonweighted Codes<br>Error Detection<br>Error Correction<br>The ASCII Code<br>The SMPTE Code .<br>Efficiency of Coding S | Weighted Codes<br>Nonweighted Codes .<br>Error Detection<br>Error Correction<br>The ASCII Code<br>The SMPTE Code<br>Efficiency of Coding Sche | Weighted Codes<br>Nonweighted Codes<br>Error Detection<br>Error Correction<br>The ASCII Code<br>The SMPTE Code<br>Efficiency of Coding Scheme | Weighted Codes Nonweighted Codes | Weighted Codes | DES       Weighted Codes       Nonweighted Codes         Nonweighted Codes       Error Detection       Error Correction         Error Correction       Error Correction       Error Correction         The ASCII Code       Error Code       Error Code         The SMPTE Code       Efficiency of Coding Schemes       Error Code         Information Capacity       Efficiency       Efficiency |

## CHAPTER 6

| Memory, | STORAGE, AND PERIPHE   | RAL | L D | )ev | 'ICI | ES |   |  |  |     | 136 |

|---------|------------------------|-----|-----|-----|------|----|---|--|--|-----|-----|

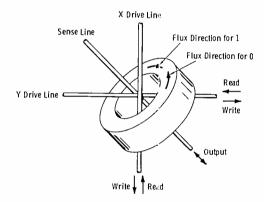

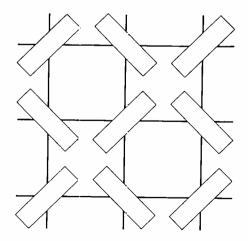

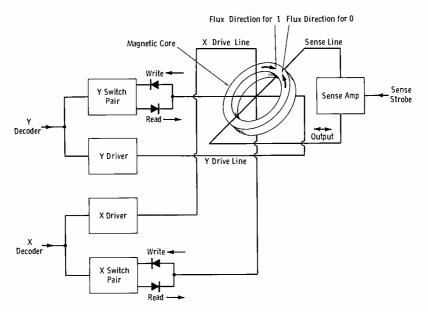

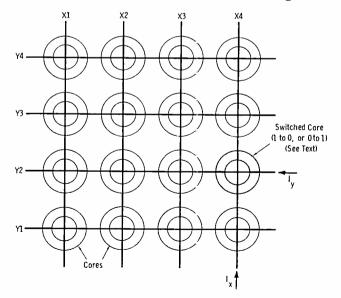

| 6-1.    | Magnetic-Core Memory   |     |     |     |      |    |   |  |  | 136 |     |

| 6-2.    | IC Memory (Flip-Flops) |     |     | •   |      | •  | • |  |  | 141 |     |

#### CONTENTS

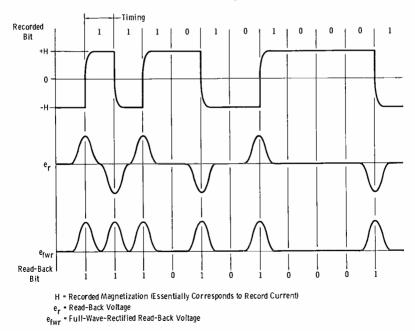

| 6-3. | Magnetic Recording for Peripheral | De | evi | ces |  |   | 145 |

|------|-----------------------------------|----|-----|-----|--|---|-----|

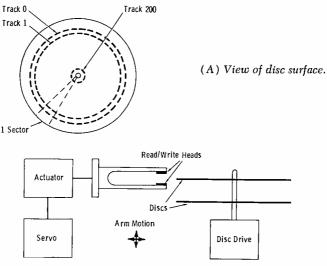

| 6-4. | The Magnetic Disc                 |    |     |     |  |   | 147 |

| 6-5. | Other Magnetic Storage Devices    |    |     |     |  |   | 151 |

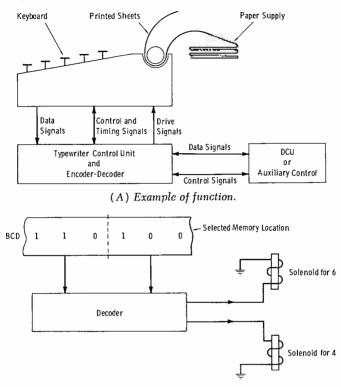

| 6-6. | The Electric Typewriter           |    |     |     |  |   | 154 |

| 6-7. | Punched Cards and Paper Tape .    |    |     |     |  | • | 154 |

## CHAPTER 7

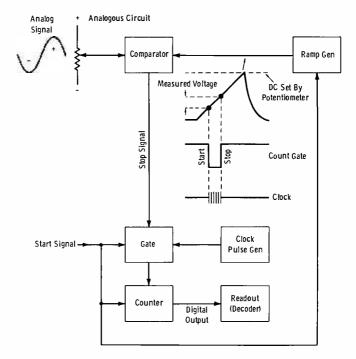

| A/D AND | D/A Conversion Techniques          | 7 |

|---------|------------------------------------|---|

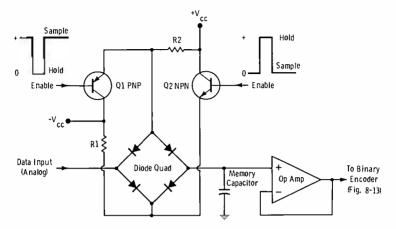

| 7-1.    | Fundamentals of Codec Theory       |   |

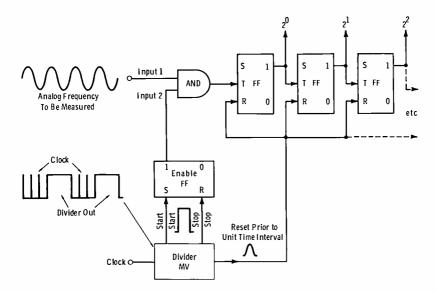

| 7-2.    | The Basic Digital Frequency Meter  |   |

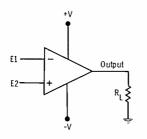

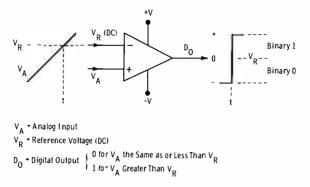

| 7-3.    | The Basic Comparator               |   |

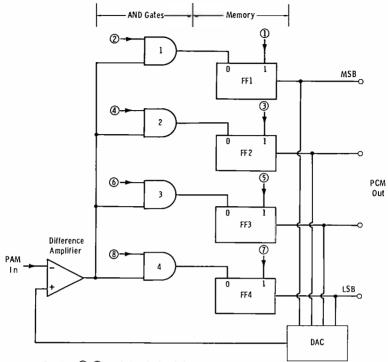

| 7-4.    | Basic Codec With Comparator        |   |

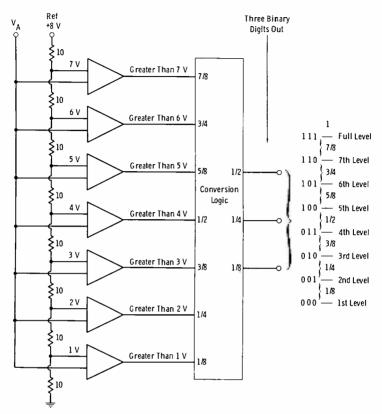

| 7-5.    | ADC by Direct Comparison           |   |

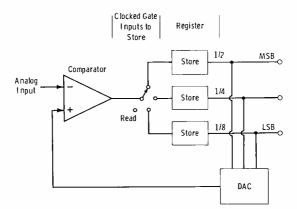

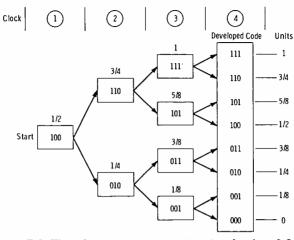

| 7-6.    | Successive Approximation           |   |

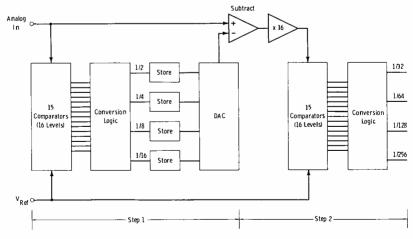

| 7-7.    | Multiple-Comparison Subranging ADC |   |

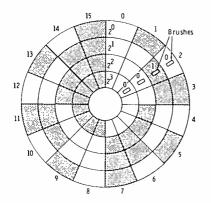

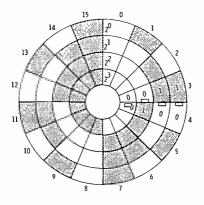

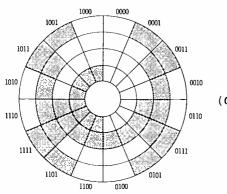

| 7-8.    | Mechanical ADC                     |   |

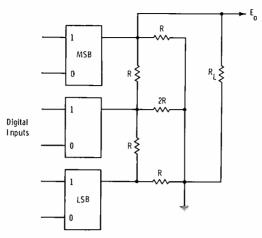

| 7-9.    | DAC Principles                     |   |

|         |                                    |   |

## CHAPTER 8

| LIN  | IKS                                                         | •                                   |                      |                      |                      |                      |                      |                      | . 175 |

|------|-------------------------------------------------------------|-------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------|

| -1.  | Baseband Systems                                            |                                     | •                    |                      |                      |                      |                      |                      | 176   |

| -2.  | The Need for Modulation                                     |                                     |                      |                      |                      |                      |                      |                      | 178   |

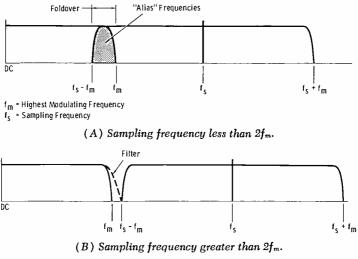

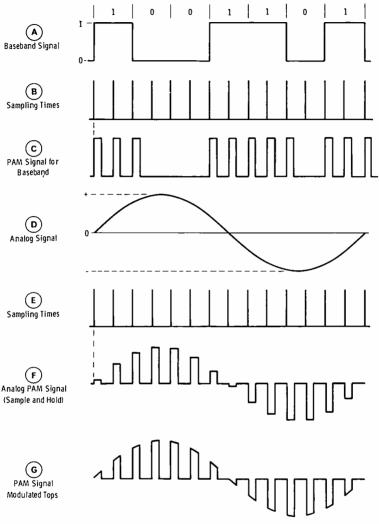

| -3.  | The Sampling Process                                        | •                                   |                      |                      |                      |                      |                      |                      | 179   |

| -4.  | Pulse-Amplitude Modulation (PAM)                            |                                     |                      |                      |                      |                      |                      |                      | 182   |

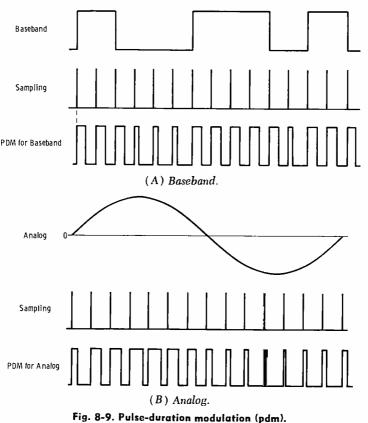

| -5.  | Pulse-Duration Modulation (PDM)                             |                                     |                      |                      |                      |                      |                      |                      | 184   |

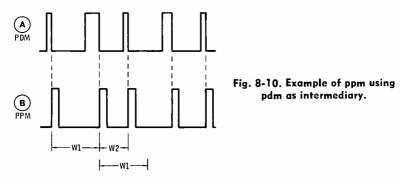

| -6.  | Pulse-Position Modulation (PPM) .                           |                                     |                      |                      |                      |                      |                      |                      | 185   |

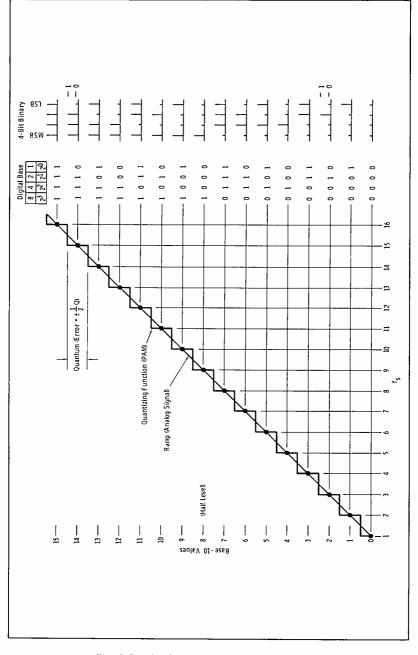

| -7.  | Pulse-Code Modulation (PCM)                                 |                                     |                      |                      |                      |                      |                      |                      | 186   |

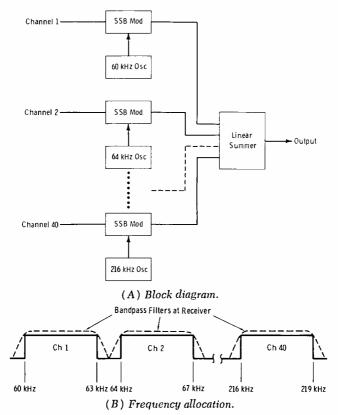

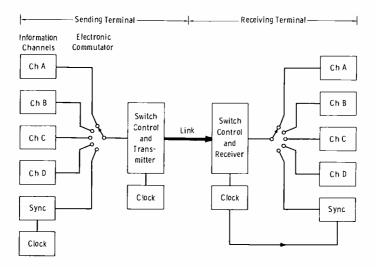

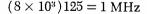

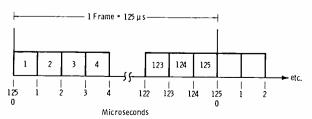

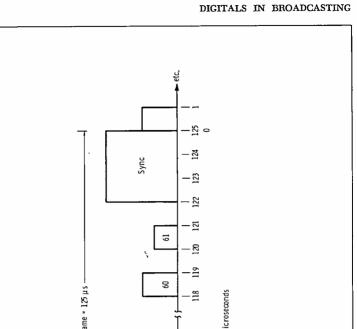

| -8.  | Multiplexing                                                |                                     |                      |                      |                      |                      |                      |                      | 191   |

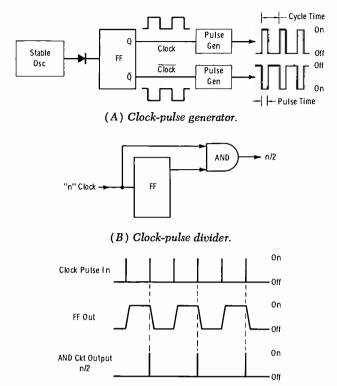

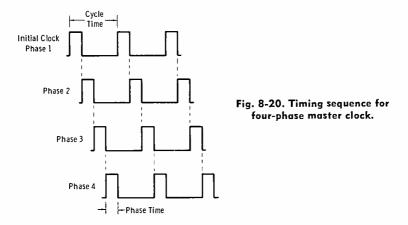

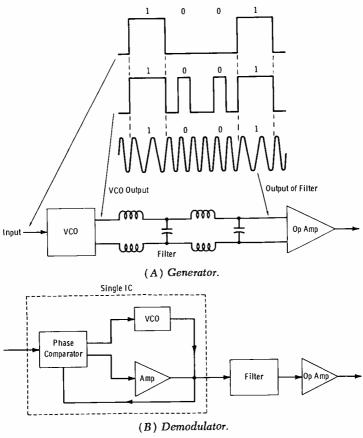

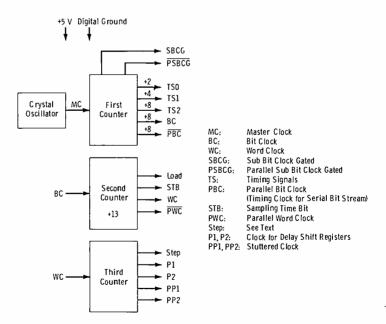

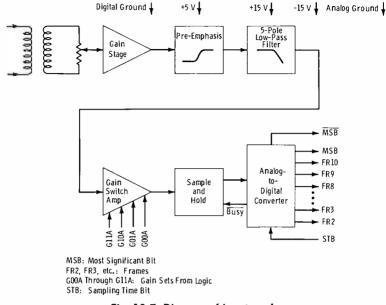

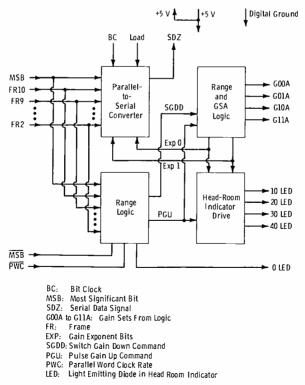

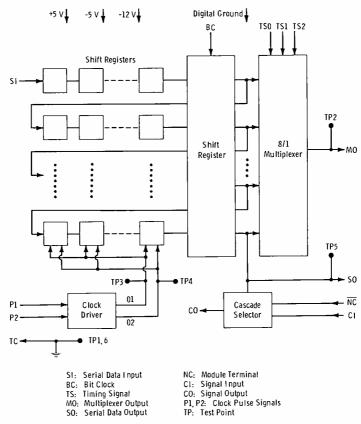

| -9.  | Clock Generators                                            |                                     |                      |                      |                      |                      |                      |                      | 197   |

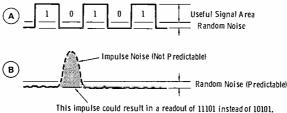

| -10. | Random and Impulse Noise                                    |                                     |                      |                      |                      |                      |                      |                      | 198   |

|      | -1.<br>-2.<br>-3.<br>-4.<br>-5.<br>-6.<br>-7.<br>-8.<br>-9. | <ol> <li>Baseband Systems</li></ol> | -1. Baseband Systems | LINKS |

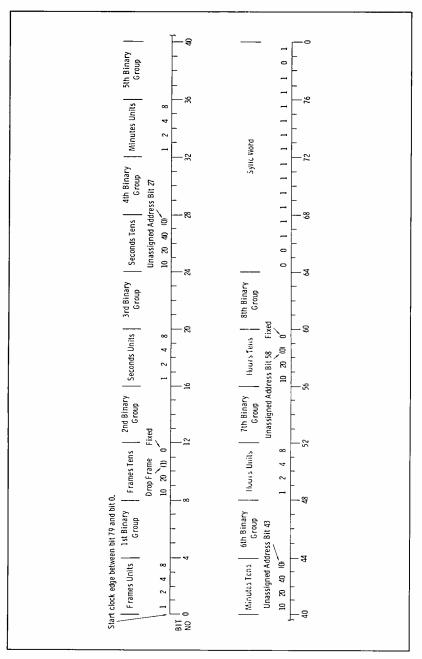

### CHAPTER 9

| DIGITAL ( | Control Systems                    | • |  |  |   | . 201 |

|-----------|------------------------------------|---|--|--|---|-------|

| 9-1.      | Remote Transmitter Control         |   |  |  | • | 201   |

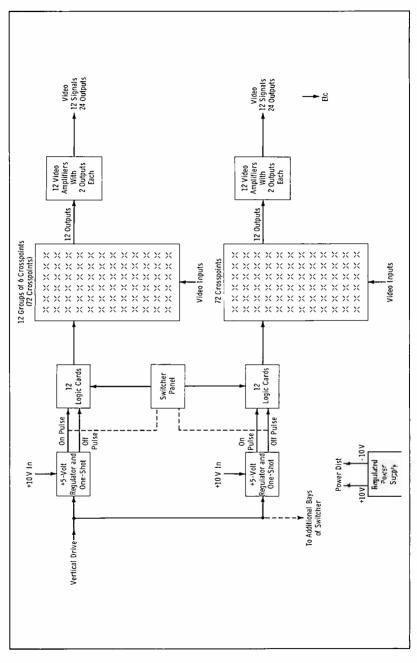

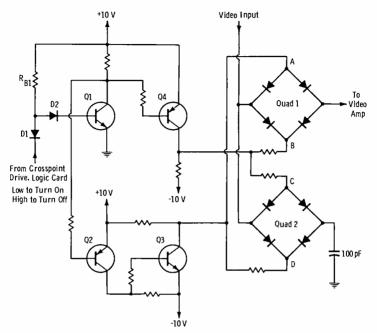

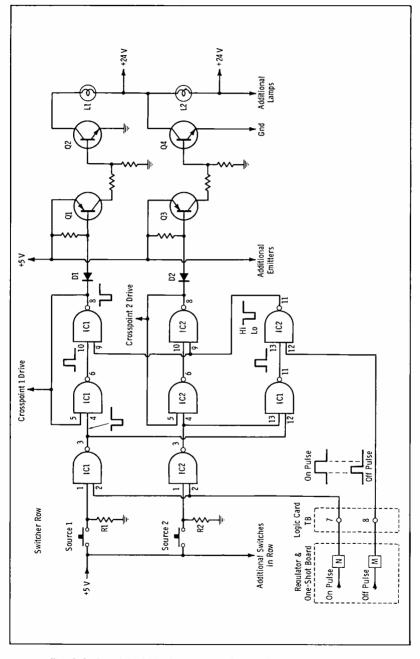

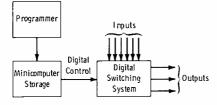

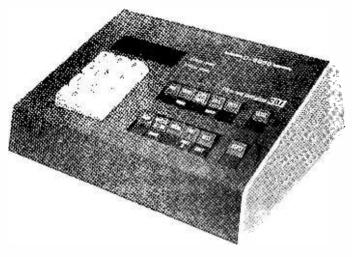

| 9-2.      | Audio and Video Logic Switchers .  |   |  |  |   | 209   |

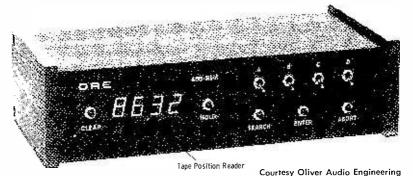

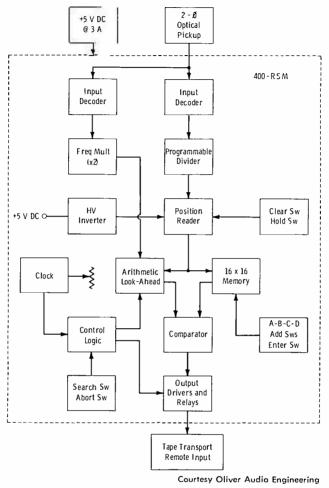

| 9-3.      | Digital Tape-Transport Control     |   |  |  |   | 214   |

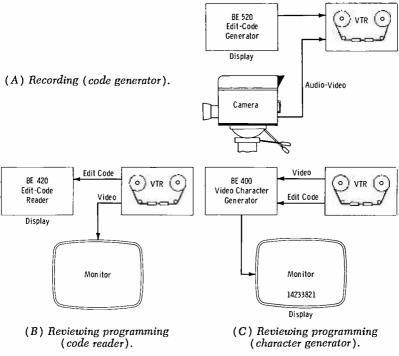

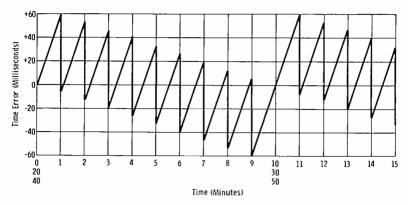

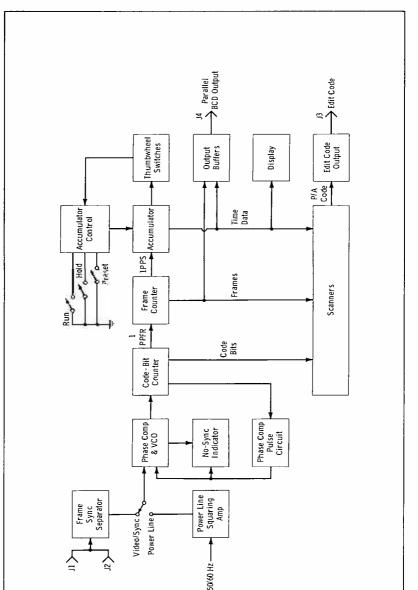

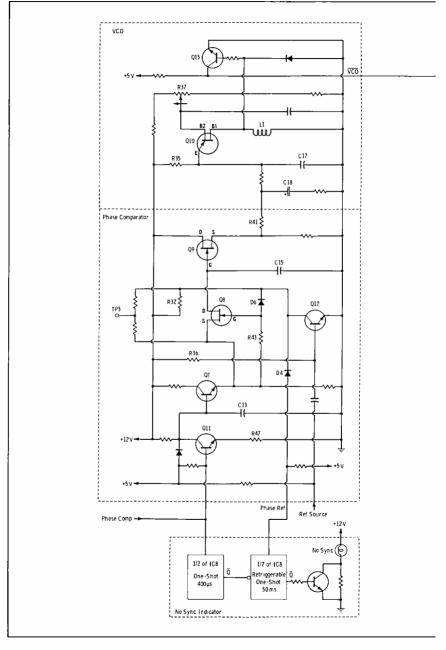

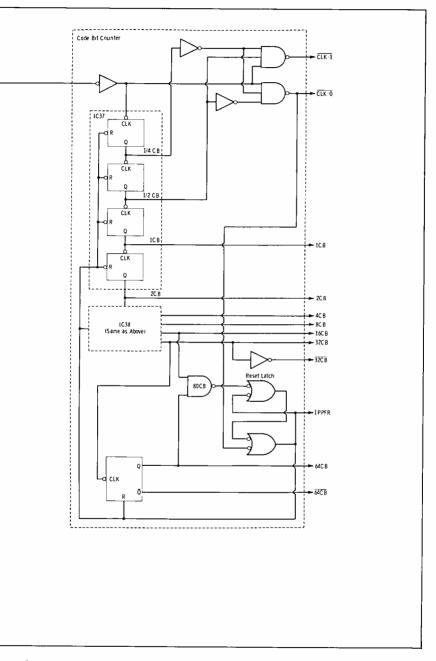

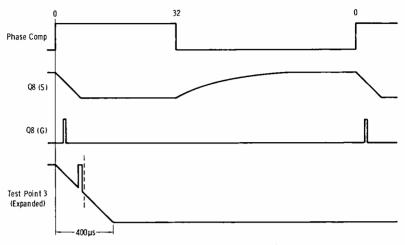

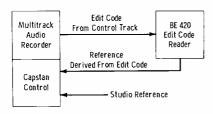

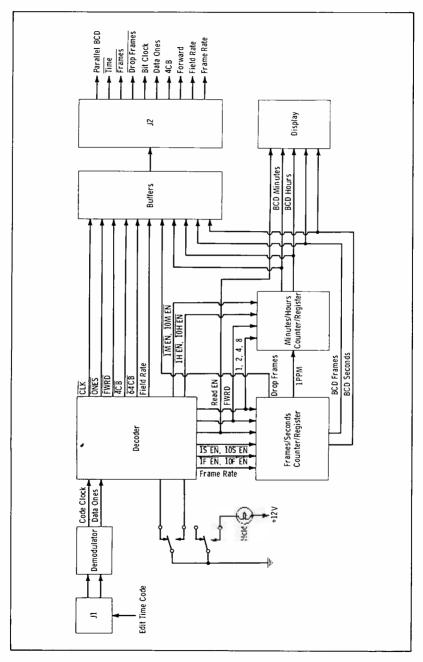

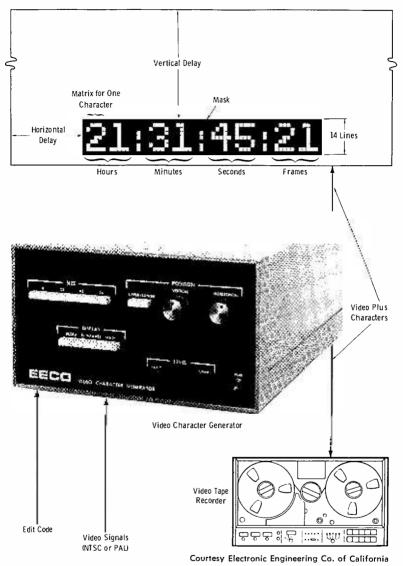

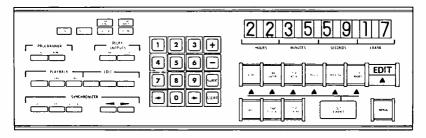

| 9-4.      | Programmed Video-Tape Editing .    |   |  |  |   | 217   |

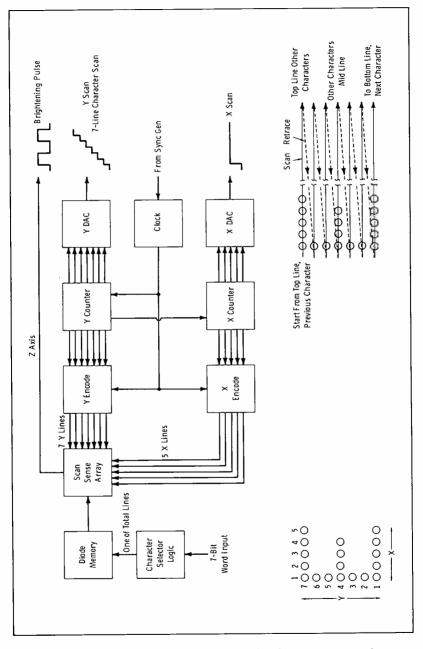

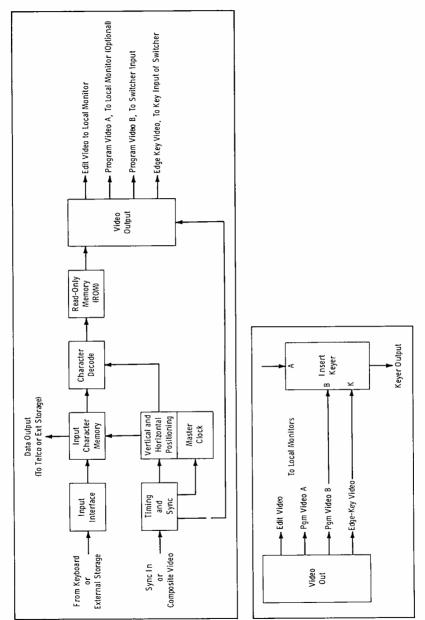

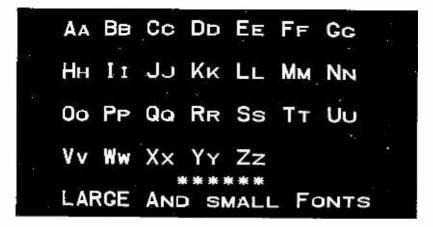

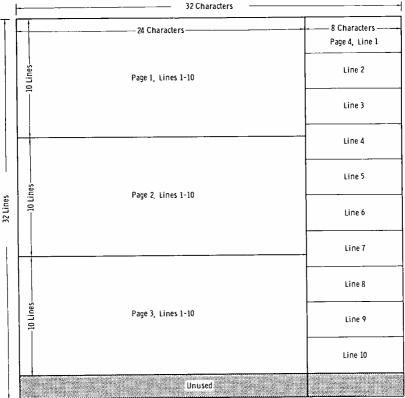

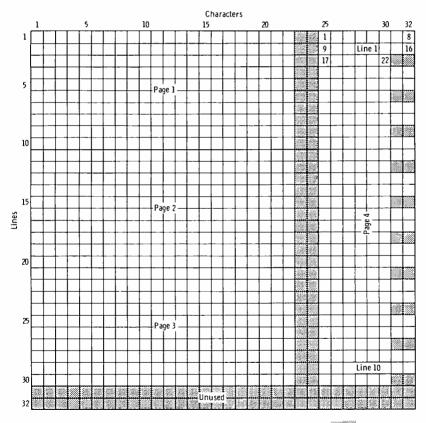

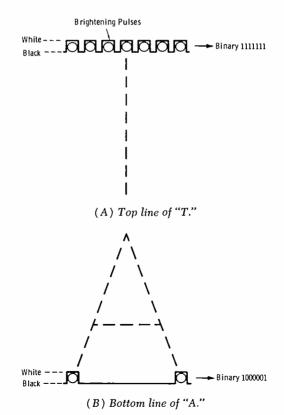

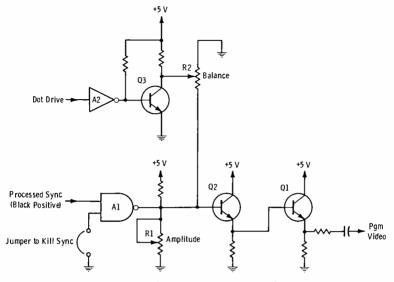

| 9-5.      | Digital Character Generators       |   |  |  |   | 235   |

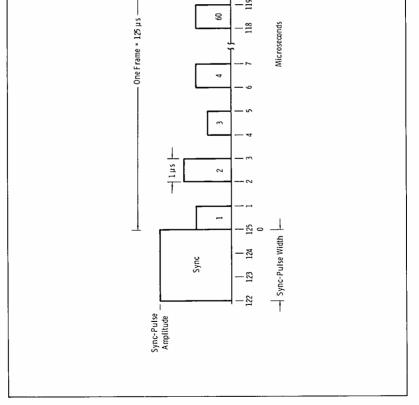

| 9-6.      | Digital Sync Generators            |   |  |  |   | 245   |

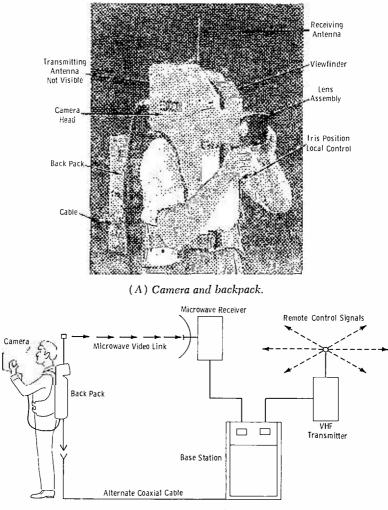

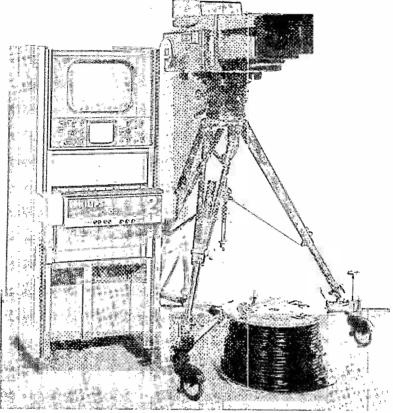

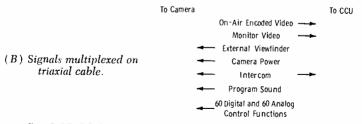

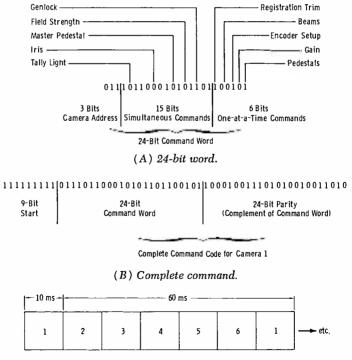

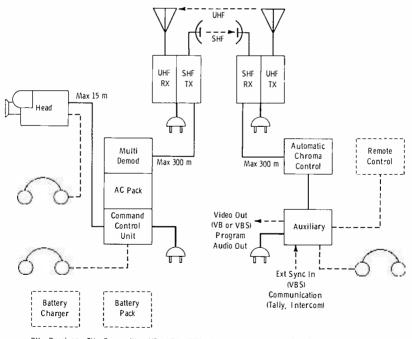

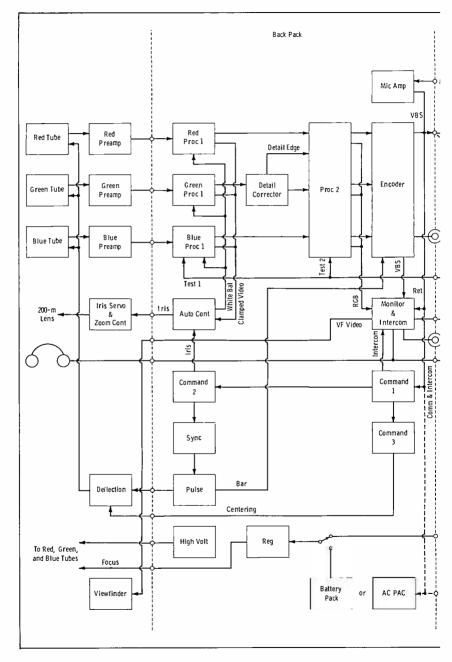

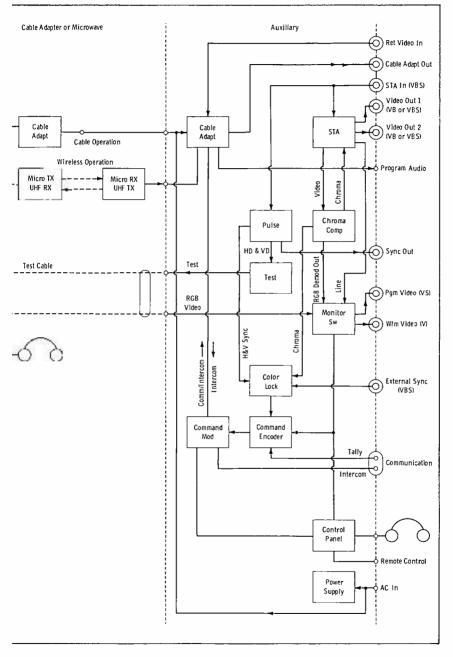

| 9-7.      | Digitally Controlled Color Cameras |   |  |  |   | 247   |

|           |                                    |   |  |  |   |       |

## CHAPTER 10

| DIGITIZED AUDIO AND VIDEO TECHNIQUES           |  |

|------------------------------------------------|--|

| 10-1. Basic Digital Audio Technique            |  |

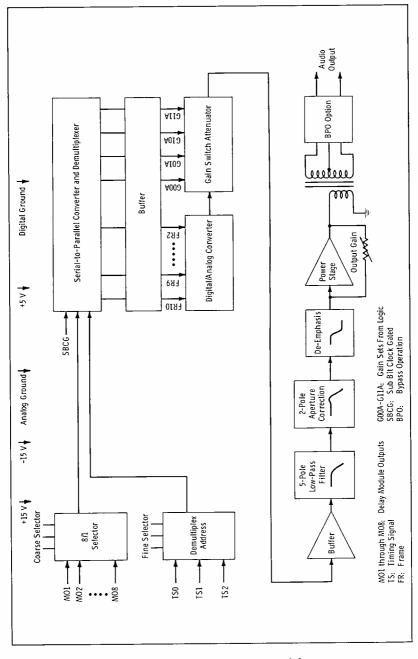

| 10-2. Digital Audio Delay                      |  |

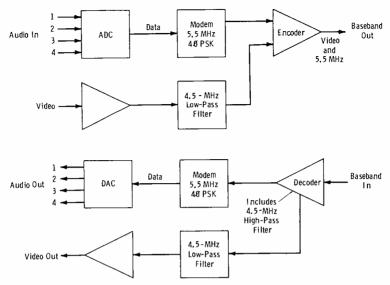

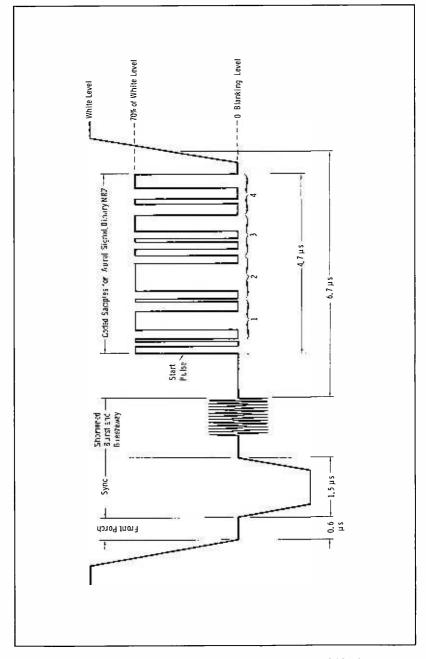

| 10-3. Digitized Audio With TV Transmission     |  |

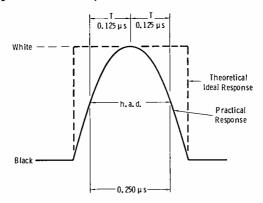

| 10-4. Basic Digitized Video Technique          |  |

| 10-5. Automatic Synchronizers                  |  |

| 10-6. Digital Time-Base Correctors (DTBCs) 299 |  |

| 10-7. Electronic Still Store (ESS)             |  |

## CHAPTER 11

| TROUBLESHOOTING DIGITAL CIRCUITRY             | • | • | • | • |   | . 322 |

|-----------------------------------------------|---|---|---|---|---|-------|

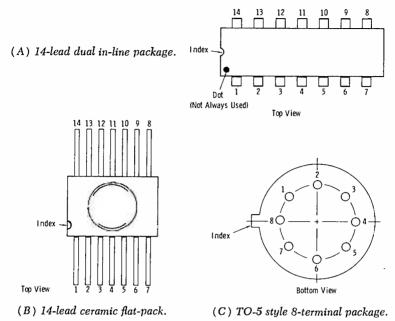

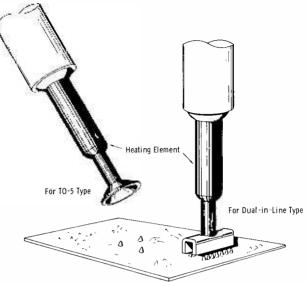

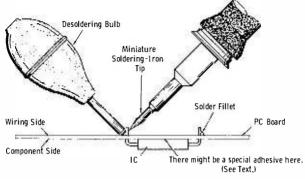

| 11-1. IC Replacement                          |   |   |   | • | • | 322   |

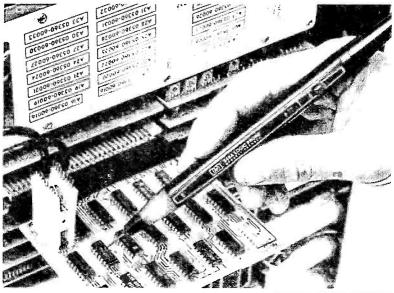

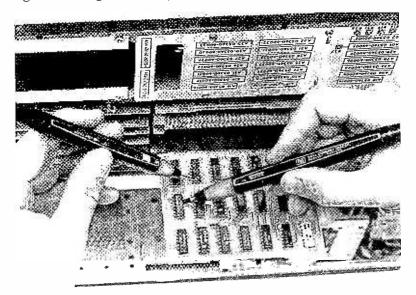

| 11-2. Basic Approach to Troubleshooting       |   |   |   |   |   |       |

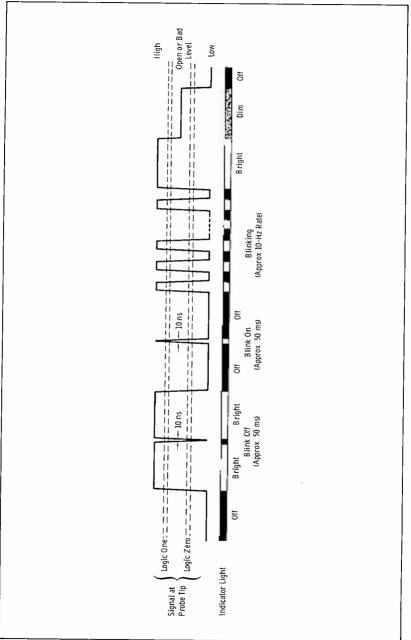

| 11-3. The Logic Probe                         | • | • | • | • | • | 327   |

| 11-4. The Oscilloscope                        | • | • |   | • | • | 332   |

| 11-5. Troubleshooting Procedures              |   |   |   |   | • | 334   |

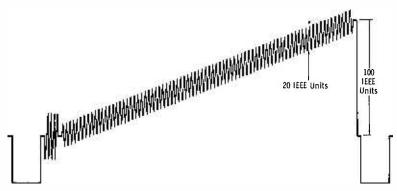

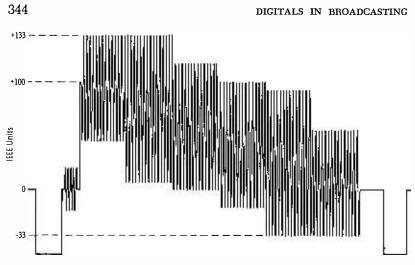

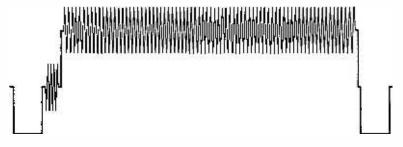

| 11-6. Measurements on Digitized Video Systems | • | • | • | • | • | 341   |

### APPENDIX A

| GLOSSARY               | • | •         | •   | •  | •  | • | • | • | • | • | • | • | • | • | 350 |

|------------------------|---|-----------|-----|----|----|---|---|---|---|---|---|---|---|---|-----|

|                        | , | ٩P        | PEI | ٩N | IX | B |   |   |   |   |   |   |   |   |     |

| Answers to Exercises . | • | •         | •   | •  | •  | • | • | • | • | • | • | • | • | • | 363 |

|                        | 1 | <b>AP</b> | PEI | ٩D | IX | с |   |   |   |   |   |   |   |   |     |

| Logarithms to Base 2   | • | •         | •   |    | •  | • | • | • | • | • | • | • | • | • | 380 |

| INDEX                  |   |           |     |    | •  |   |   |   | • |   | • | • | • |   | 381 |

## CHAPTER ]

## Orientation in Bits, Bytes, Bauds, and Bandwidth

As the term *digital* implies, digital technology involves "doing it by the numbers." In digital technology, the accuracy is determined in the initial system concept; the "readout" is in no way subject to an operator's estimate.

There are two basic applications for digital systems:

- 1. Digital control circuitry. This is already well established in the field, but the penetration into broadcasting has been so broad and so rapid that the subject is not thoroughly understood by many.

- 2. Digital data (information) transmission, such as the conversion of analog (continuously varying) audio, video, or other information to digital (number) form. This is a new and rapidly developing field.

The purpose of Chapter 1 is to give an overview of these digital applications in broadcasting, with implications in the sound-recording and general communications fields. It is like stepping back from a painting in order to appreciate the beauty: Rather than going directly into a complex system analysis, we will first step back and take a look at the entire philosophy of digital and digital-analog technology.

One of the first hurdles to clear is the mystery of terminology. There is nothing so frustrating as reading a text full of terms that do not appear at all in a regular dictionary but require a special glossary or dictionary of scientific terms. After learning the terminology, you are ready to view the overall picture more realistically.

Table 1-1 lists standards prefixes as used in this text, along with the most common applications.

| Prefix                           | Definition                                                                                                                                                                                                                            | Power of Ten<br>Multiplier            |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| atto                             | millionth of millionth of millionth part                                                                                                                                                                                              | 10-18                                 |

| pico<br>(preferred)              | millionth of one millionth part                                                                                                                                                                                                       | 10 <sup>-12</sup>                     |

| micromicro<br>(obsolete)<br>nano | millionth of one millionth part<br>thousandth of a millionth                                                                                                                                                                          | 10 <sup>-12</sup><br>10 <sup>-9</sup> |

| micro<br>milli                   | millionth of one part<br>thousandth of one part                                                                                                                                                                                       | 10 <sup>-6</sup><br>10 <sup>-3</sup>  |

| centi<br>deci                    | hundredth of one part<br>tenth of one part                                                                                                                                                                                            | 10 <sup>-2</sup>                      |

| deka<br>hecto                    | ten<br>one hundred                                                                                                                                                                                                                    | 10 <sup>1</sup><br>10 <sup>2</sup>    |

| kilo                             | one thousand<br>one million                                                                                                                                                                                                           | 10 <sup>3</sup>                       |

| mega<br>giga<br>tera             | one billion<br>one trillion                                                                                                                                                                                                           | 10 <sup>9</sup><br>10 <sup>12</sup>   |

| ns<br>μs<br>ms<br>μF<br>pF       | Most commonly used letter symbols:         manosecond       kHz = kilohe         microsecond       MHz = megal         millisecond       GHz = gigahe         microfarad       picofarad         Hz = 1 cycle per second       Karana | nertz*                                |

Table 1-1. Prefixes

#### 1-1. INTRODUCTION TO THE BINARY SYSTEM

You have been working with digitals all your life. Your usual method has been "base 10" arithmetic (also termed *decimal* arithmetic). This means that the columns under which you start your new 1s are headed 1, 10, 100, 1000, etc. The decimal system has ten digits, 0 through 9. This system is handy, because you first learned to count on your digital appendages, 10 fingers and 10 toes. But you will learn to interface this system with a system that recognizes only two numbers, 0 and 1. This is *binary*, or base-2, arithmetic.

You will be surprised how easily the binary system can be learned and put to use. When you become familiar with it, the math is not as involved as that required for basic electronics. For example, binary logic can say that 1 = true and 0 = false. Or 1 is "high" and 0 is "low." Or 1 = + and 0 = 0 (ground). Or 1 = 0 and 0 = minus. Or 1 = Jill and 0 = Jack.

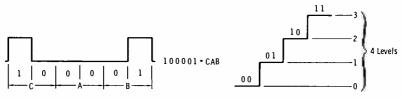

The binary system is the simplest possible number system. A single digit in the decimal system can be any digit from 0 to 9. A single binary digit (called a *bit*, as a contraction of *binary* digit) can be only a 0 or a 1 (in electronic parlance, a "pulse"). This is extremely

valuable in electronic circuitry because a 0 can be an open switch (no current) and a 1 can be a closed switch (maximum current). Thus, a single bit has just two possible *levels*, 0 or 1.

Just as the base 10 has ascending powers of 10, the binary system has ascending powers of 2: 2, 4, 8, 16, 32, etc. Note an important point: misplacing the decimal point by one place results in an error of a power of ten; misplacing the binary point by one place results in an error of only a power of two. In addition to this, since the binary system employs only zeros and ones, a technique known as a *parity check* can be used to detect an error. Finally, there are *error correction codes* (Chapter 5) that make the binary system virtually foolproof, except from human errors in initial programming.

Since a single bit is only a 0 or a 1, groups of bits are required to define any number greater than 1, or any character, such as letters of the alphabet, teletypewriter signals, signs, symbols, etc. This group of bits is termed a byte. The number of bits in a byte depends on the total number of characters required for the entire code being used. For example, if you have a total of 128 numbers and characters to be defined, you need a 7-bit byte  $(2^{\tau} = 128)$ .

A word in computer parlance is an ordered set of characters which depends on the specific system design. For example, a digitally controlled color camera (Chapter 9) employs a 24-bit command word. Since up to six cameras can be controlled, the first 3-bit byte addresses the particular camera to be commanded in the immediately following part of the word. This is followed by a 15-bit byte of simultaneous commands, and then by six bits of one-at-a-time commands.

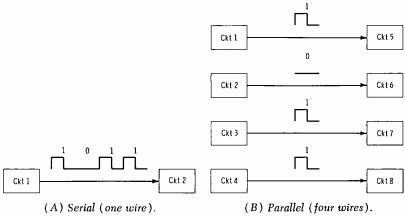

In the above example, transmission bit-by-bit is done on one wire (serially). In some systems, you can also have parallel feed, one wire for each bit. Thus, eight wires would be required for eight bits. Or, you might have 24 wires with three groups of eight bits on each wire. This 24-bit group may be called a word. Each 8-bit subgroup is called a byte. In general, the terminology is spelled out for each specific system. In some systems, the group of bits forming a byte is termed a *binary word*.

#### 1-2. SIGNALING SPEED VERSUS BITS PER SECOND

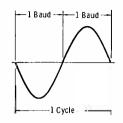

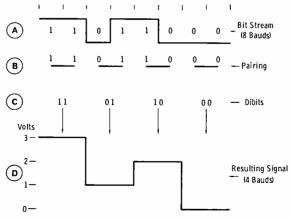

Digital transmission rates may be expressed in terms of *bits per* second (sometimes abbreviated bps) or *bauds*. These terms do not mean the same thing. The term *baud* is used as a measure of *signaling speed*. The term *bits/second* is used as a measure of the number of *information* bits per second. Let us clarify this now.

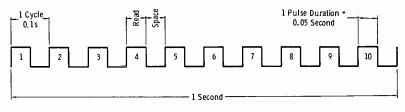

Assume you have the pulse train illustrated in Fig. 1-1. Ten pulses occur each second, so the frequency for the indicated train of pulses

10 bits/s = 10 Hz Fundamental Frequency Bauds = 1/0, 05 = 20 = Signaling Speed

Fig. 1-1. Bits and bauds in a pulse train.

is 10 Hz. The pulse repetition interval is 1/10 = 0.1 s. Thus, you have 1/0.1 = 10 bits/s. Assuming spaces equal to the pulse duration, the width of each pulse is  $\frac{1}{2}(0.1) = 0.05$  s, or 50 ms.

A baud is the reciprocal of the length of the shortest signal element. So:

1/0.05 = 20 bauds = signaling speed

The fundamental frequency is the reciprocal of the pulse repetition interval, or:

$$1/0.1 = 10 \, \text{Hz}$$

Note that when the spaces are equal to the pulse width (50% duty cycle, or square wave), a simple 2/1 relationship exists between bauds and fundamental frequency. Also, if each pulse (read period) carries one information bit (no synchronizing pulses such as start-stop), a simple 2/1 relationship holds between baud rate and bit rate. It is assumed here that the "spaces" do not carry information. An example is the electronic pulse counter.

You can see that the term *baud*, since it is defined as the reciprocal of the shortest signal element, is somehow related to bandwidth. In practice, the required bandwidth is related to the desired bits/ second transmission speed (channel capacity), signal power, and noise. Thus, the baud specification is not particularly useful to the practicing engineer or technician. It is explained here only because a specification for a given system may be given in terms of bauds, and you should know what the terminology means.

NOTE: Bits/second vs bandwidth is covered in Section 1-4.

Please note that these examples assume a return-to-zero pulse format. This and other formats are covered in Section 1-3.

Some systems, such as the Teletype code, employ start and stop pulses in addition to character *information* pulses. Assume as an example that the start pulse is 25 ms wide, the five information bits are each 20 ms, and the stop pulse is 30 ms. The five information bits BITS, BYTES, BAUDS, AND BANDWIDTH

are required to make up a single *character*. The total of 7 bits per character is termed the *unit code*.

The baud rate is:

$$1/0.02 = 50 =$$

signaling speed in bauds

The total time for a character transmission must include the information bits plus the start and stop pulses. So:

Start pulse = 25 ms

5 information pulses = 5(20) = 100 ms

Stop pulse = 30 ms

Total = 25 + 100 + 30 = 155 ms for one character

Then the bit rate is:

$(1/0.155) \times 5 = 6.45 \times 5 = 32.3$  information bits/second

Now assume that a code format requires the insertion of a 40-ms *space* period between the stop pulse for one character and the start pulse for the next. The baud rate would remain the same, since the duration of the shortest bit is still 20 ms. However, the *rate of information flow* would be *reduced*, since the total time for one character is now 155 ms + 40 ms = 195 ms. Then:

$(1/0.195) \times 5 = 5.13 \times 5 = 25.6$  information bits/second

SUMMARY: The baud rate determines the type of channel required for transmission. Bits/second describes the rate of information flow. When parity bits are used, they are counted the same as information bits.

It is important to note that the rate of information flow is not necessarily the same as the total bits/second used in a given channel. The *channel capacity* (Section 1-4) must consider the total number of bits, or unit code, transmitted per second. In the last example above, there were a start pulse, five information pulses, a stop pulse, and a space pulse. This was a total of 8 pulses which required a time interval of 195 ms. Therefore, the *total* number of pulses sent was:

$$(1/0.195)$$

$(8) = 5.13$   $(8) = 41.0$  pulses/second

On the other hand, if all eight pulses carried message information (including any parity bits), the rate of information flow and the total bits/second would be identical.

#### 1-3. PULSE FORMATS

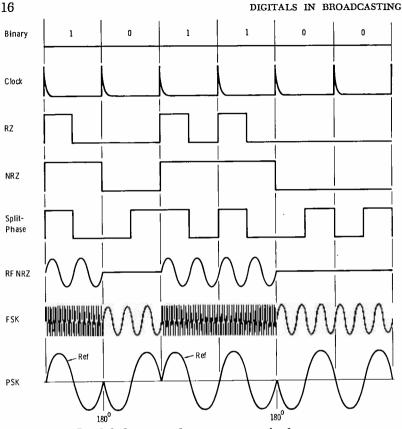

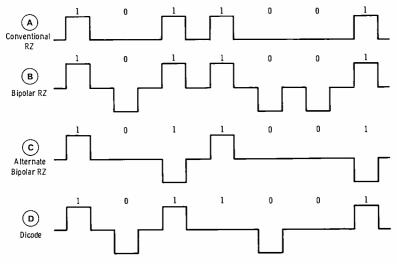

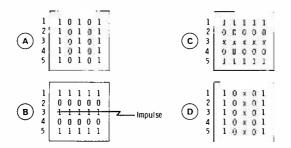

A summary of the most common pulse formats is shown in Fig. 1-2. A binary value of 101100 (read "one-zero-one-one-zero-zero")

Fig. 1-2. Summary of most common pulse formats.

is listed on the top line as an example. The second line shows the sampling time, which may be either the leading or the trailing edge of the clock pulse. The clock pulse is the main timing pulse for a synchronous system.

RZ. This is the return-to-zero bit representation for binary 101100. This is the format discussed in Section 1-2.

NRZ. This is the nonreturn-to-zero format for the data indicated. Note that a 1 pulse is wider in this code than in the corresponding RZ format, and that two consecutive 1's employ just one (wider) pulse (does not return to zero). The baud rate is about one-half that of the RZ code, requiring about one-half the bandwidth for a given message. Another way of saying this is that for a given bandwidth, the NRZ format can handle a higher data rate than the RZ code.

Split-Phase. This format has a low-to-high transition for each bit, whether 0 or 1. A 1 has a transition from high to low in the middle

#### BITS, BYTES, BAUDS, AND BANDWIDTH

of a bit ( $\frac{1}{2}$ -bit duration). A 0 is signified by a low-to-high transition in the middle of a "mark" (sampling time). This is an excellent format for synchronization and accuracy, and it can be self-clocking. The special SMPTE time edit pulse (Chapter 5) is a biphase adaptation of this format.

RF NRZ. This is a straight pulsed carrier wave. Carrier represents 1, and lack of carrier represents 0. If RZ is used, the carrier is pulsed on for each bit with appropriate spaces.

FSK. This is frequency-shift-keying in which 1 is represented by a higher deviation frequency and 0 by a lower deviation frequency.

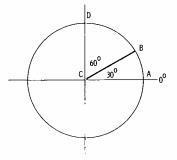

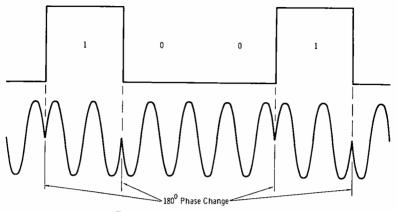

*PSK.* This is phase-shift keying in which 1 is a leading phase deviation limit and 0 is a lagging phase deviation limit. In the example shown, a complete  $180^{\circ}$  phase inversion exists between 1 and 0.

NOTE: Fsk or psk may involve either modulated tones or modulated carriers.

In one example of psk, a 950-MHz carrier is used. An audio tone at 5.4 kHz is phase-shifted 180° to identify a single bit of information. This tone is used to modulate the carrier.

Polar and bipolar pulses are discussed in Chapter 8.

#### 1-4. BASIC DIGITAL SYSTEM THEORY

A digital data signal changes only in discrete levels, rather than in a continuously varying (analog) manner. Furthermore, the data are usually binary so that the discrete steps are limited to two, 0 and 1.

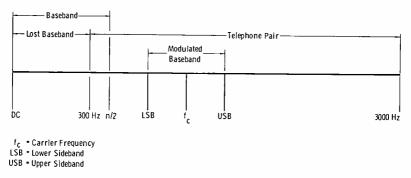

There are two basic types of digital systems, *baseband* and *modulated*. A baseband signal is the direct-coded data signal sent over a transmission path without modulation. A pulse-modulated signal is a carrier modulated in one or more modes (Chapter 8).

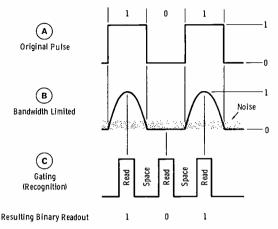

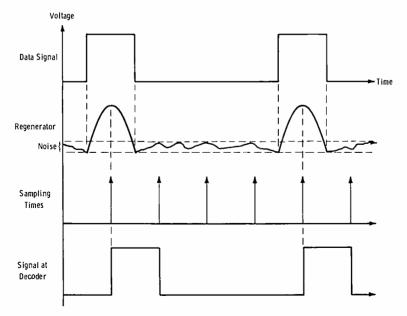

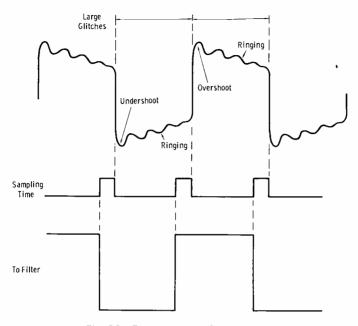

A binary signal is seldom a pure rectangular waveform, particularly in transmission systems. Fig. 1-3B illustrates that a bandwidthlimited rectangular wave has the same information (0 or 1) as the original signal (Fig. 3-1A). An extremely wide bandwidth is necessary to pass a fast-rise-time pulse without distortion. Bandwidth limiting (such as by a linear-phase filter) eliminates the need for extreme bandwidths. You should understand that the digital pulses may be limited in bandwidth by transmission facilities, but the gating waveform, regenerated at the receiving terminal from transmitter information, is as nearly ideal in waveshape as possible.

The binary system is normally gated (Fig. 1-3C) only at the time necessary to determine the 0 or 1 condition. This eliminates all noise except that which occurs simultaneously with the pulse

Fig. 1-3. Bandwidth limiting and gating in binary system.

level. Note that noise above a given threshold in the binary 0 position could trigger a false 1. This is treated later in this section.

A binary channel carries a stream of pulses that simply represent zeros or ones. The *capacity* of any binary channel (usually measured in bits/second) depends on the channel bandwidth, B (in hertz); the *average* signal power, s; and the *average* noise power, n:

$$C = B \log_2 (1 + s/n)$$

where,

C is the channel capacity in bits/second,

B is the bandwidth in hertz,

s/n is the signal-to-noise ratio (power basis).

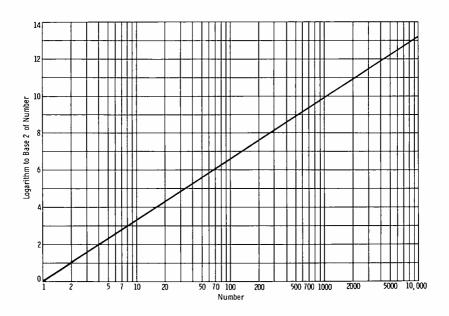

Note that for binary digits (bits), the logarithm to the base 2 is used rather than the more conventional logarithm to the base 10. Some calculators have a means of finding the logarithm to any base.  $Log_2$  tables are not readily available. However, base 10 (common) logarithms can be used, in which case the answer is in *hartleys*. This answer multiplied by 3.3 gives the answer in bits/second. We will solve an example in both ways so that you can use this relationship.

NOTE: For a close estimate when extreme accuracy is not required (usually the case), you can use the graph given in Appendix C to find  $\log_2$  of any number between 2 and 10,000. Or, simply find  $\log_{10}$  of the number, and multiply by 3.3.

Assume a channel with a bandwidth of 2500 Hz (near the upper limit of ordinary unequalized telephone lines). This channel has an s/n ratio of 30 dB. What is the maximum rate at which data can be transmitted on this channel? BITS, BYTES, BAUDS, AND BANDWIDTH

To get the answer directly in bits/s,  $\log_2$  is used:

$C = 2500 \log_2 (1 + 1000)$

NOTE: 30 dB = 1000/1 power ratio.

$C = 2500 \log_2 (1000)$

(The 1 can be dropped.)

$$C = 2500 (9.9) \\= 24,750 \text{ bits/s}$$

Now solve by the  $\log_{10}$  method:

$C = 2500 \log_{10} (1000) \\= 2500(3) \\= 7500 \text{ hartleys}$

To convert from hartleys to bits/second:

$$7500(3.3) = 24,750 \text{ bits/s}$$

Remember that this formula gives the *absolute maximum* (theoretical) information rate for a given channel with uniform random noise. The relationship of channel capacity, bandwidth, and s/n ratio is derived from *Shannon's theorem*, and it is used by engineers to determine the theoretical limits of one unknown value from the two known variables.

IMPORTANT: To comprehend channel capacity correctly, remember that this includes all 1's and all 0's (yes-no decisions). It *does not* mean just the 1 bits.

Before leaving the subject of logarithms to the base 2, remember that a logarithm is an exponent. When you are working with direct powers of 2 (Table 2-3, Chapter 2),  $\log_2$  is evident. The number of information bits (I) required to identify a particular selection from a group of *n* possible selections is  $\log_2 n$ :

$I = \log_2 n$

For example, if you have eight characters to be recognized,  $\log_2 8 = 3$ . Note from Table 2-3 that  $2^3 = 8$ . This simply means that the power of 2 is the  $\log_2$  of 8, and three bits are required to define eight characters.

A common communication code contains 128 different characters. How many bits must it have per character? Answer:  $\log_2 128 =$ 7 bits (2<sup>7</sup> = 128). This is evident from Table 2-3.

Also note that  $2^9 = 512$  and  $2^{10} = 1024$ . This means that  $\log_2 512 = 9$  and  $\log_2 1024 = 10$ . In the previous example, you could have closely estimated the value of  $\log_2 1000 = 9.9$  from this relationship.

Note two important points that can be derived from Shannon's relationship:

- 1. A message occupying bandwidth B1 can be sent over a channel of lesser bandwidth B2 if the signal power is increased (greater s/n ratio).

- 2. A given channel capacity (C) can be maintained with a lesser s/n ratio if the bandwidth is increased.

You may wish to disagree with the latter statement, since noise power increases with bandwidth. However, the noise increases only as the *square root* of the increase in bandwidth. Thus, if the bandwidth is doubled, the noise increases as the square root of 2, or 1.4 times. A bandwidth increase of 9 times increases the noise 3 times.

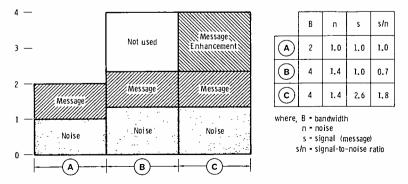

Now let us see what increased bandwidth really means in a digital system. Observe Fig. 1-4. In A, the system has an arbitrary bandwidth of 2 units. Since the noise is 1 unit and the signal (message) is 1 unit, s/n = 1.

In B and C, the bandwidth is doubled. The noise increases to 1.4 times its value in A. Since the signal has the same value in B as in A (1 unit), the s/n ratio deteriorates to 0.7 times that in A. The remaining capacity of the increased bandwidth is not used in B.

In C, the extra bandwidth is used for *message enhancement*. This means that the increased capacity is used to enhance the digital information by some form of *redundant* transmission. You can say that each character is "explained" much as you do on a noisy telephone or communication channel. Here you can see that the s/n ratio is increased to 1.8 times that in A.

Message enhancement takes many forms, such as multiple parity bits, special codes (Chapter 5), actual redundant transmission (repetition), or complement parity.

Fig. 1-4. Improvement of digital system with increased bandwidth.

#### BITS, BYTES, BAUDS, AND BANDWIDTH

The *complement* of a binary word is simply its inverse value; all zeros are changed to ones, and ones are changed to zeros (Chapter 2). For example, a 16-bit command word may be followed by a 16-bit parity that is the complement (interchanged 1's and 0's) of the preceding command word. Unless the command word is followed by its complement, nothing happens, and the code is repeated. This provides reliable random or impulse noise immunity, and it virtually eliminates false commands and erroneous functions in the presence of noise. Review Fig. 1-3 and note how effective this could be when noise occupies a considerable portion of the 0 level, triggering a false 1.

Note also from Shannon's relationship that the minimum s/n power ratio necessary for a binary channel of known bit rate and bandwidth can be found. The simplified relationship in terms of s/n ratio is:

$$s/n = 2^{C/B} - 1$$

For example, assume you have a 2500-Hz channel with a bit rate of 10,000 bits/second.

$$s/n = 2^{10,000/2500} - 1$$

$$= 2^4 - 1$$

$$= 16 - 1 = 15$$

Thus, the minimum power ratio must be 15/1. To convert a power ratio of 15 to decibels:

$$dB = 10 \log 15$$

= 10 (1.176)

= 11.76, or 12 dB minimum

The problems concerning random (white) noise and impulse noise are explored in Chapter 8.

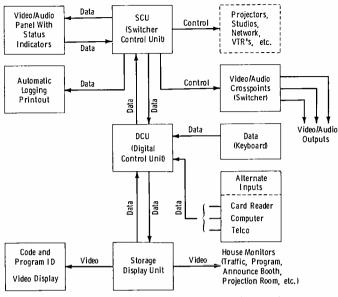

#### 1-5. AUTOMATION

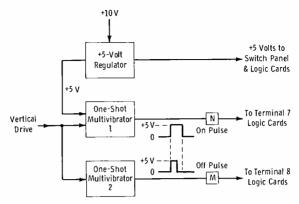

Fig. 1-5 is a block diagram of a typical automation system for a television studio. The heart of such a system is the *digital control unit* (dcu). This unit includes the *clock*, a master timing device used to provide the basic sequencing pulses for operation. It also incorporates a high-capacity *memory* (storage) bank.

The clocked storage display unit is a memory register (Chapter 6) that automatically records the progress of real time (or some approximation to it), records the number of operations performed, and provides a visual display of contents yet available to the auto-

Fig. 1-5. Typical automated control of tv studio.

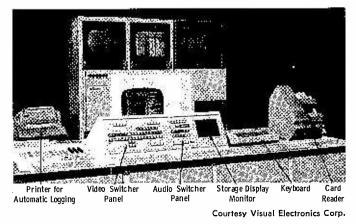

mated segment of programming. Note that this involves conversion of digital data to a video signal. Fig. 1-6 illustrates an automated switcher system, showing the display on a video monitor.

The switcher control unit (scu) prerolls and "takes" film projectors and video tape recorders (vtr's), and it "takes" selected studios, remote sources, or network sources. It also interrogates the dcu memory and receives data concerning characters and their loca-

Fig. 1-6. An automated tv switcher.

tions, compares the data with information in the scu memory, and then operates the appropriate relays or electronic crosspoints in the video/audio switcher. The scu also inserts data into the dcu memory to perform the countdown function, the upshift function as events go on the air, and the forward count of the true-time indication. Bypass of automation to allow manual operation from the video/ audio panels is always provided in such systems. Automated controls are covered in Chapter 9.

#### 1-6. REMOTE CONTROL OF TRANSMITTERS

Remotely controlled transmitters are commonplace in the broadcasting and general communications fields. The digital system, due to its extreme reliability and immunity from the effects of noise, has become the most prevalently used system.

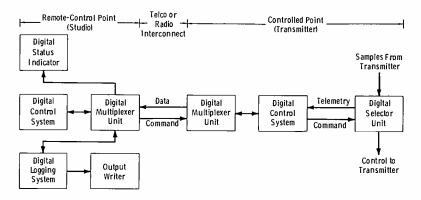

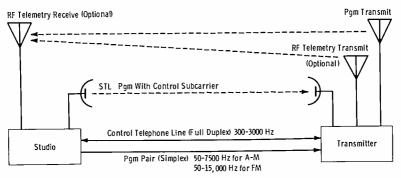

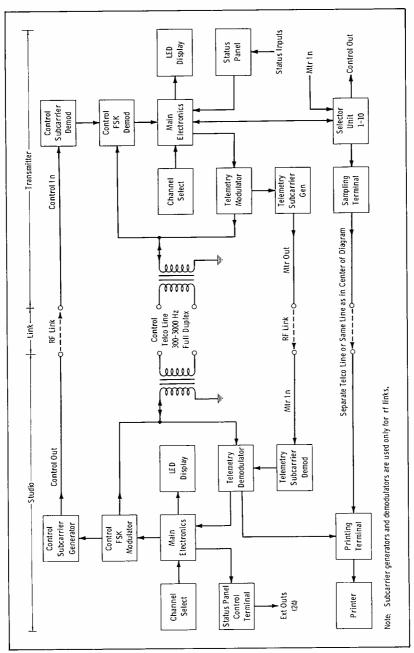

Fig. 1-7 represents a typical remote-transmitter control system employing digital techniques. *Telemetry* is a process by which measurement of a quantity is transferred to a remote location to be displayed or recorded, or to actuate a process. The type of telemetry depends on whether the interconnection link is a land line (as through Telco facilities) or an rf carrier or subcarrier between sending and receiving points. In the latter case, fsk or psk is often used; tones (or modulated tones) are used with land lines.

The *multiplexer* allows multiple channels of information to be transmitted and received on a single wire pair or rf channel. It may work on the frequency-division or time-division principle.

A typical basic system may provide 32 channels. This allows 32 parameters to be displayed. With any such system, the number of command functions is twice the number of display functions, since a "raise" and "lower" command are required for each parameter

Fig. 1-7. Typical transmitter remote-control system.

#### DIGITALS IN BROADCASTING

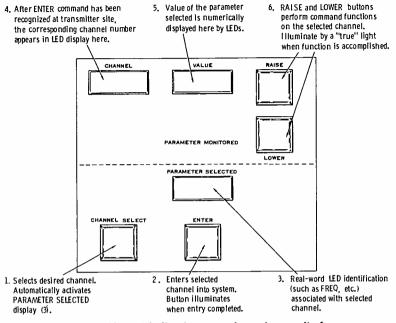

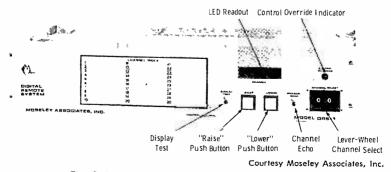

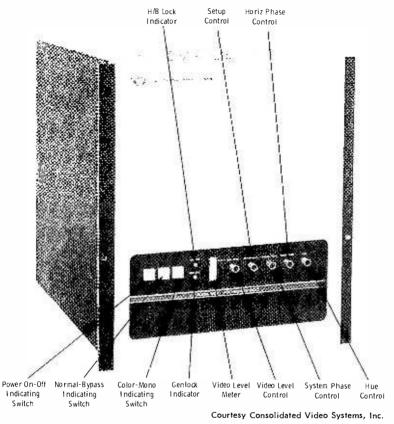

Fig. 1-8. Typical indicating control panel at studio for remote control of transmitter.

monitored. Many systems can be expanded to as many as 96 channels, with 192 individual command functions.

Fig. 1-8 represents a typical indicator and control panel installed at the studio for remote control and monitoring of the transmitter. Follow the numbers from 1 to 6 for a description of the way the system works.

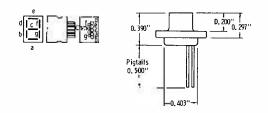

Bipolar pulses (Chapter 8) are used so that the metering functions can indicate either positive or negative values. For example, assume the CHANNEL SELECT switch is set on number 10, and that this number selects the measurement of transmitter frequency. The reading indicated by the light-emitting diode (LED) display in the value window may be either above or below the authorized frequency. Thus, the reading is preceded by the proper sign (- or +)to indicate whether the "raise" or the "lower" command signal needs to be operated.

#### 1-7. DIGITIZED AUDIO AND VIDEO

The conversion of aural, visual, and other analog information to digital form is a new and intensely fascinating field. Digital signals can be conveniently "stored" in a memory (Chapter 6). This information can then be "read out" on any convenient time base required. You cannot distort a binary bit. You may completely change its position, or even lose it, but you will not distort it. Either it is there or it is not there.

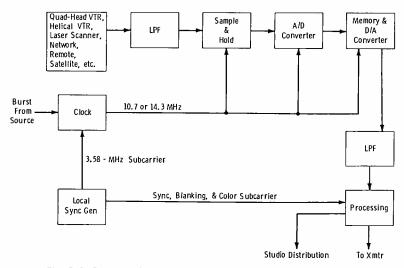

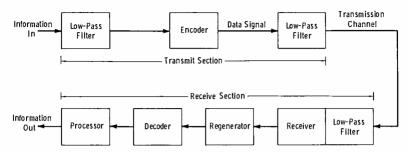

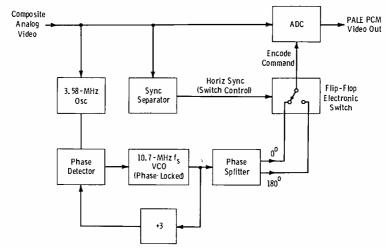

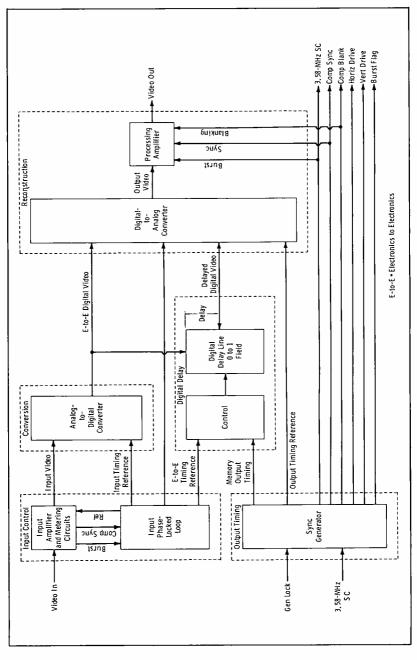

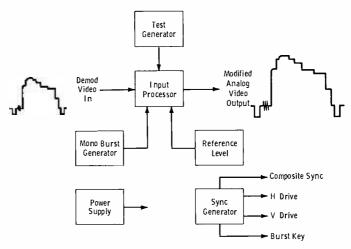

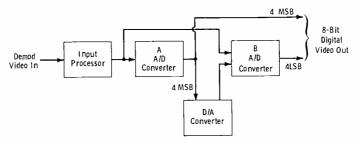

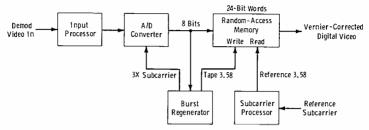

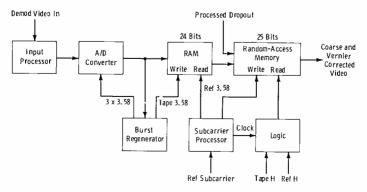

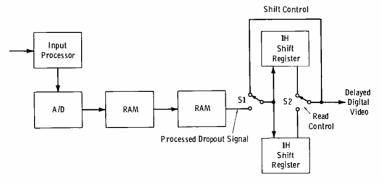

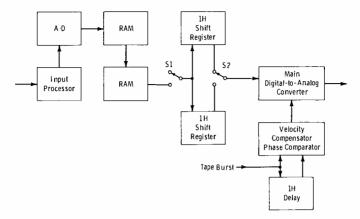

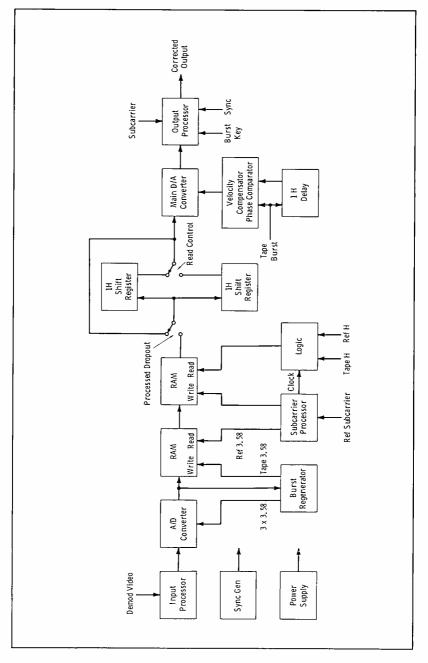

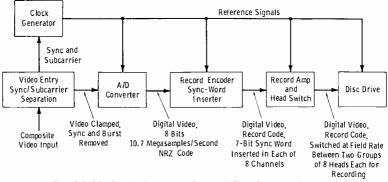

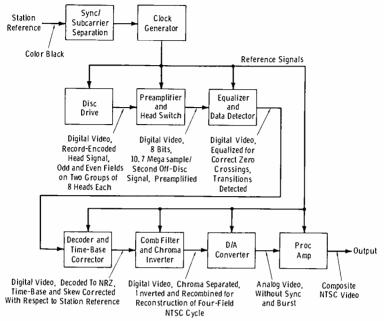

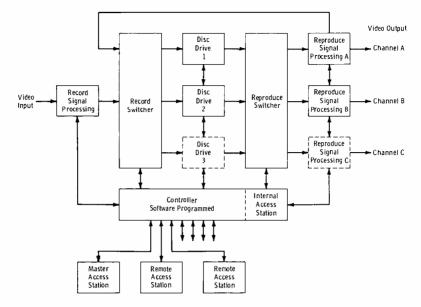

Fig. 1-9 is a block diagram of a typical in-plant application for a television broadcast studio. It makes no difference to the digital system whether the input is from a quad-head or helical-scan vtr, a laser scanner, nonsynchronous network or remote sources, etc. The output signal is in time-base-corrected analog form, is raster- and color-synchronous with the local sync generator, and, in special cases when desired, is changed in format, size, or other characteristics. Processing in digital form is virtually limitless.

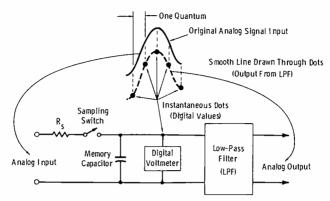

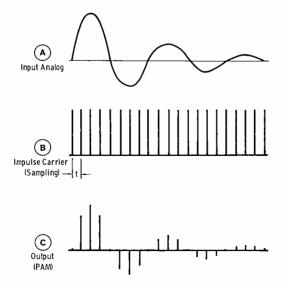

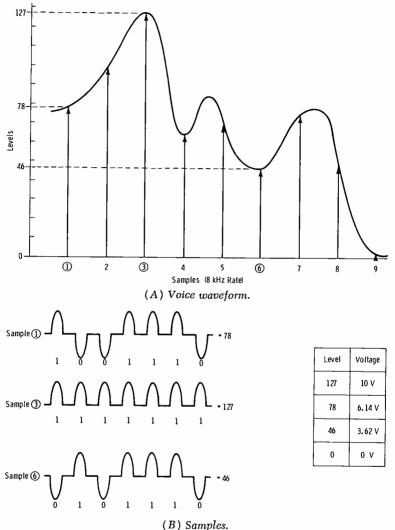

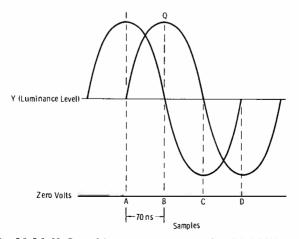

Analog information is converted to digital form by sampling the signal and converting each instantaneous sampled level to a corresponding binary number. This process is termed *pulse-code modulation*, or pcm. After processing for whatever functions are to be performed, the binary signals are reconverted to analog form for distribution in the conventional system.

In the example of Fig. 1-9, the system clock operates at three or four times the color subcarrier rate. This provides the reference sampling and timing frequencies.

The analog video signal is fed through a low-pass filter (lpf) to remove noise and harmonics above 4.2 MHz. The signal is then sampled at the clocked rate, which results in a pulse amplitudemodulated (pam) signal. Each sampled level is "held" sufficiently long for the analog-digital (a/d) converter to generate the binary

Fig. 1-9. Simplified block diagram of in-plant digital function.

group (byte) associated with the corresponding level. The signal is now in pcm binary form, and it is stored in the memory bank.

The system clock, which is derived from the local sync generator, reads the information from the memory. A digital to analog (d/a) converter feeds the analog information to another low-pass filter to remove switching and pulse transients over 4.2 MHz. The analog signal is now locked element by element to the local generator and is processed for distribution.

A few examples of such applications in television broadcasting are: tape, laser, or other recorders; time-base correctors; image enhancers; automatic synchronizers and timers; standards conversion; video compressors; special effects; all-electronic slide (storage) projectors, etc.

Present-day applications in television use a sampling rate of three times the color subcarrier frequency, or 10.7 MHz. An 8-bit byte is used for each sampled level, providing 256 possible levels to be recognized. Thus, the transmission rate is:

(10.7 MHz)(8) = 85.6 megabits/second

When parity bits are used, the rate comes close to 100 megabits/ second.

If 4 times the color subcarrier is used:

(4)(3.58 MHz) = 14.3 -MHz sampling rate

The transmission rate is:

(14.3 MHz)(8) = 114 megabits/second.

Transmission rates of this (and greater) magnitude are quite feasible in closed-circuit applications today. For long-distance transmission, such as by rf carrier (lower s/n ratio), bandwidth-reduction schemes are used.

#### EXERCISES

There is a group of exercises at the end of each chapter; the solutions are given in Appendix B. Try to respond to each question on your own without looking at the answer. If you cannot answer a question, review the chapter carefully and try again. In a few cases, exercises cover an addition to the chapter material, but an addition that is inclusive within the framework of the subject covered. This checks your ability to apply knowledge.

Q1-1. Define the following terms:

- (A) bit. (D) word.

- (B) byte. (E) baud.

- (C) character.

#### BITS, BYTES, BAUDS, AND BANDWIDTH

- Q1-2. Assume a pulse train consisting of a start pulse and five information pulses, all of which have a 1-ms duration. A stop pulse of 4-ms duration is used. Find the:

- (A) transmission speed.

- (B) rate of information flow.

- Q1-3. Assume the stop pulse in the pulse train of Q1-2 is reduced to 2-ms duration. Find the: (A) transmission speed.

- (A) transmission speed.

- (B) rate of information flow.

- Q1-4. What is the total capacity requirement (in bits/s) for the interconnecting link in Q1-3?

- Q1-5. Give the basic mathematical relationship for converting (A) hartleys to bits/second and (B) bits/second to hartleys.

- Q1-6. If you have a land line with a 5000-Hz bandwidth and an s/n ratio of 50 dB, what is the maximum capacity in bits/second for a baseband signal? (Use common logarithms to get the answer in hartleys; then convert to bits/second).

- Q1-7. If each character is made up of 8-bit bytes, how many characters/ second would the link of Q1-6 transmit?

- Q1-8. If it is desired to maintain the same capacity as that obtained in Q1-6, but the s/n ratio is only 30 dB, what bandwidth will be required? (Hint: Convert bits/second to hartleys and use common logarithms.)

- Q1-9. You have a 100-megabit-per-second signal (baseband). What is the required bandwidth for the interconnecting link, assuming the s/n ratio is 50 dB?

- Q1-10. In digital applications, is there any use for a link having a noise level the same as the signal level? Assume the available bandwidth is 2500 hertz.

## CHAPTER 2

## **Binary Math**

The binary number system provides the simplest form of mathematics in existence. Each element (bit) can be only a 0 or a 1. A pulse represents 1; no pulse represents 0.

#### 2-1. THINKING BINARY

You have heard the mandate "think metric." Let's see what this really means.

Remember the old saying, "An ounce of prevention is worth a pound of cure"? How popular would this saying become if it were in metric form? Converted to metric quantities, the saying becomes, "28.35 grams of prevention is worth 0.4536 kilogram of cure." Certainly no popular saying there! But if you were really "thinking metric," you would simply say, "A gram of prevention is worth a kilogram of cure." That's the point!

Learn to "think binary." This does not mean that we should forget decimals. Rather, we must learn to interface the real world of decimals, letters, and symbols with computer-type machines that use equivalent binary numbers as a language.

When you have completed this chapter, you should continually practice the interfacing of binary numbers with decimal numbers and vice-versa. You will find that the rules become mentally automatic in a short time.

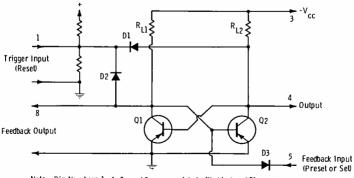

#### 2-2. THE BISTABLE FLIP-FLOP

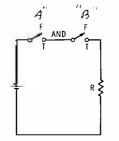

The bistable flip-flop is the foundation of logic and binary structure. It uses either a positive or a negative trigger (never both) to change its state from off to on, or on to off. It is "stable" in either mode, and it does not change state between triggers. You know that a flip-flop (or any multivibrator) has two output pulses of opposite polarity. Do not worry about the mechanics at this time. The binary system uses only zeros and ones. A given output is either a 0 (low) or a 1 (high). The outputs reverse in polarity for a change in state.

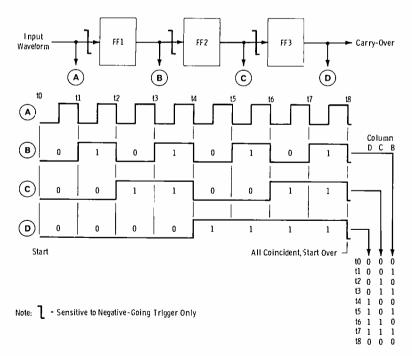

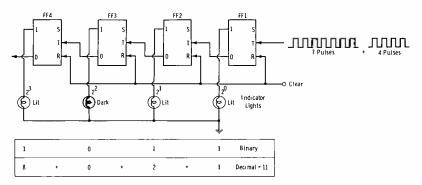

In Fig. 2-1, note that the flip-flops are sensitive to negative-going edges only. In practice, the "triggering" can be either positive-edge or negative-edge.

Just put the waveforms down as in Fig. 2-1 and analyze them as follows:

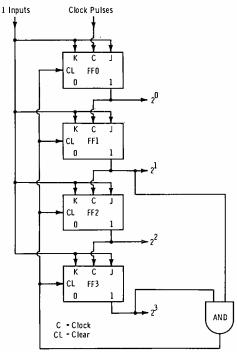

Waveform A: The input pulses (waveform A) form a series of zeros and ones. However, since the flip-flops respond only to negative-going transitions, only those transitions that occur at t1, t2, etc., are significant in this example. At time t0, all "1" outputs are 0. We are going to "count," or "accumulate," only the "1" outputs. Thus, the series of flip-flops and associated "storage" can be termed a *counter* or an *accumulator*; either term is correct.

Waveform B: Waveform B is the "1" output of FF1. Note that the first negative-going transition of the input waveform (A) occurs at t1, the next negative-going transition is at t2, and so forth. There-

Fig. 2-1. Basic binary formation.

fore, waveform B changes level at each of these times. Write this in column B as a series of alternate 0's and 1's.

Waveform C: The first negative-going transition of waveform B is at t2. This turns FF2 on. The next negative-going transition of waveform B is at t4. This turns FF2 off. Waveform C thus has a series of two 0's and two 1's; put them in column C.

Waveform D: The first negative-going transition of waveform C is at t4. This turns FF3 on (waveform D). The next negative-going transition of waveform C is at t8. It turns FF3 off. This makes a series of four 0's and four 1's; write them down in column D. Note that at this point all waveforms are coincident (0, or low) and the process starts over. You have gone as far as possible with three digits in the binary system.

When you read binary notation, read it only as zeros and ones. Thus, at t0 (Fig. 2-1), read "zero-zero-zero." At t4, do not read "one hundred," but "one-zero-zero."

NOTE: A "set-reset" flip-flop as used in practical circuits is covered in Chapter 4.

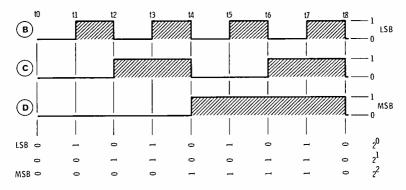

Now redraw the output waveforms of Fig. 2-1 as shown in Fig. 2-2. The 1 state of each flip-flop is the shaded area. At time t7, you have "accumulated," or "counted," seven input pulses to get the equivalent of decimal 7. Look at it this way:

The waveforms are in either a 1 state or a 0 state, regardless of pulse duration. For each input pulse, an output pulse is added to one of the waveforms in Fig. 2-2. At t0 you have no pulses (000). At t1 you have one pulse (in waveform B), or 001 = 1. At t2 you have accumulated two 1's, one in waveform B and one in waveform C, for a binary count of 010. Since this 1 is in the 2<sup>1</sup> column, it is equivalent to decimal 2. At this point, you have counted to 2 one time, or  $2^{1}$ .

Fig. 2-2. Counting to decimal 7 with three bits.

#### BINARY MATH

Continue this reasoning on to t7. At this time, you have four 1's in waveform B, two 1s' in waveform C, and one 1 in waveform D, for a total of 7.

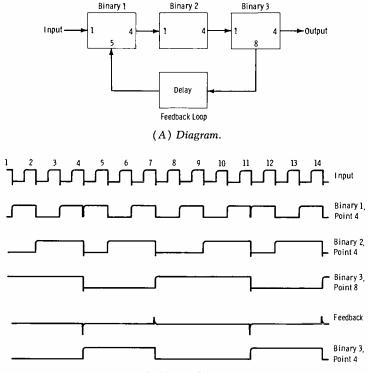

Each flip-flop has divided by 2, which is its basic function. So, you have a single 1 state in waveform D for eight input pulses, or a divide-by-eight divider. The chain of flip-flops is called a *divider*, *accumulator*, or *counter*, depending on the particular application in which the circuit is used.

#### 2-3. POWERS OF NUMBERS (EXPONENTS)

In our conventional decimal system,  $10^1 = 10$  and  $10^{-1} = 0.1$ . So,  $10^0$  must lie between  $10^1$  and  $10^{-1}$  to represent 1. It is a fundamental rule of mathematics that *any* number raised to the zero power is equal to 1. So  $2^1 = 2$ ,  $2^{-1} = 0.5$ , and  $2^0 = 1$ .

Table 2-1 reviews the decimal (base-10) system for four digits. The  $10^{\circ}$  column contains units of ones, the  $10^{1}$  column contains units of tens, the  $10^{2}$  units of hundreds, and the  $10^{3}$  units of thousands. Thus, the number 4826 = 4000 + 800 + 20 + 6. The power is normally termed the *positional weight* of the number. Thus, a 6 in the  $10^{3}$  column would represent 6000, but a 6 in the  $10^{\circ}$  column would represent only 6. In Table 2-1, the least significant digit (LSD) is in the  $10^{\circ}$  column, and the most significant digit (MSD) is in the  $10^{3}$  column.

Table 2-2 shows the binary system for four bits. Here, instead of ascending powers of ten, we have ascending powers of two. Only zeros and ones are used. A 1 in the  $2^{0}$  column (least significant bit, or LSB) is equal to 1. A 1 in the  $2^{1}$  column is equal to 2. A 1 in the  $2^{2}$  column is equal to 4. A 1 in the  $2^{3}$  column (MSB for a 4-bit system) is equal to 8.

To convert any 4-bit binary number to its equivalent decimal value, count from right to left and give each 1 its equivalent decimal value from the "weight" of its given position. For example, bi-

| Positional Weight | 10 <sup>3</sup> | 10 <sup>2</sup> | 101 | 10 <sup>0</sup> |                       |

|-------------------|-----------------|-----------------|-----|-----------------|-----------------------|

| Equivalent        | 1000            | 100             | 10  | 1               |                       |

|                   | 4               | 0               | 0   | 0               |                       |

| 4826 ==           |                 | 8               | 0   | 0               | = 4000 + 800 + 20 + 6 |

| 4020              |                 |                 | 2   | 0               | = 4000 + 800 + 20 + 8 |

|                   |                 |                 |     | 6               |                       |

|                   | = 4             | 8               | 2   | 6               |                       |

|                   | Î ↑             |                 |     | 1<br>1          |                       |

|                   | MSD             |                 |     | LSD             |                       |

Table 2-1. Decimal System for Four Digits

| Binary Weight      | 2 <sup>3</sup> | <b>2</b> <sup>2</sup> | 21 | <b>2</b> <sup>0</sup> |               |

|--------------------|----------------|-----------------------|----|-----------------------|---------------|

| Decimal Equivalent | 8              | 4                     | 2  | 1                     | Decimal Count |

|                    | 0              | 0                     | 0  | 0                     | 0             |

|                    | 0              | 0                     | 0  | 1                     | 1             |

|                    | 0              | 0                     | 1  | 0                     | 2             |

|                    | 0              | 0                     | 1  | 1                     | 3             |

|                    | 0              | 1                     | 0  | 0                     | 4             |

|                    | 0              | 1                     | 0  | 1                     | 5             |

|                    | 0              | 1                     | 1  | 0                     | 6             |

|                    | 0              | 1                     | 1  | 1                     | 7             |

|                    | 1              | 0                     | 0  | 0                     | 8             |

|                    | 1              | 0                     | 0  | 1                     | 9             |

|                    | 1              | 0                     | 1  | 0                     | 10            |

| }                  | 1              | 0                     | 1  | 1                     | 11            |

|                    | 1              | 1                     | 0  | 0                     | 12            |

|                    | 1              | 1                     | 0  | 1                     | 13            |

|                    | 1              | 1                     | 1  | 0                     | 14            |

|                    | 1              | 1                     | 1  | 1                     | 15            |

|                    | MSB            |                       |    | LSB                   |               |

Table 2-2. Binary Table for Four Bits

nary 0110 is simply 2 + 4 = 6. Binary 1001 is simply 1 + 8 = 9. Binary 1111 = 1 + 2 + 4 + 8 = 15.

#### Going Beyond Four Bits

Note from Fig. 2-1 that the output of FF3 is termed a *carry-over*. This could feed another flip-flop whose output would then be  $2^3 = 8$  in decimal form. If added to the waveforms of Fig. 2-1, its output would have a series of 8 zeros and 8 ones. The 1's would start at t8, or the negative-going transition of waveform D. There would then be four bits of information, not counting the input waveform. Table 2-3 lists the positive powers of 2 for values up to decimal 4096. Note that each additional power (weight) doubles the decimal equivalent value. Thus, Tables 2-1 and 2-2 can be expanded to as many powers as required for a particular application. For example: binary 100101 = 32 + 4 + 1 = 37. Binary 1100101 = 64 + 32 + 4 + 1 = 101. Simply count the spaces to the left and give each bit the appropriate decimal equivalent; then add. In counting from right to left, just say 1-2-4-8-16-32-64-128-256-etc.

#### The Modulus

The odometer (mileage indicator) in an automobile normally has a decimal readout capacity of 99,999.9 miles. When you travel an-

| Power of 2                       | Decimal<br>Equivalent |

|----------------------------------|-----------------------|

| 2°                               | 1                     |

| 21                               | 2                     |

| 2 <sup>2</sup>                   | 4                     |

| 2 <sup>3</sup><br>2 <sup>4</sup> | 8                     |

| 24                               | 16                    |

| <b>2</b> <sup>5</sup>            | 32                    |

| <b>2</b> <sup>6</sup>            | 64                    |

| 27                               | 128                   |

| 2 <sup>8</sup>                   | 256                   |

| 2°                               | 512                   |

| <b>2</b> <sup>10</sup>           | 1024                  |

| <b>2</b> <sup>11</sup>           | 2048                  |

| 2 <sup>†2</sup>                  | 4096                  |

Table 2-3. Positive Powers of 2

other 1/10 mile beyond that, the odometer "resets," or "clears," to 00,000.0, which actually represents 100,000 miles. Therefore, for this device the *modulus* is 100,000. The modulus of any counter is the fixed capacity of the counter plus one increment of the least significant digit (LSD).

Note from Table 2-2 that the 4-bit binary counts from 0 to 15. This is 16 "levels," counting zero, and is the modulus  $(2^4 = 16)$ . Another way to look at this is to realize that the maximum decimal count is the modulus minus 1.

#### 2-4. ADDING BINARY ZEROS AND ONES

The preceding discussion may be entirely logical to flip-flops, but is it logical to you? You cannot draw numerous waveforms to handle binary arithmetic. You will need to work out your arithmetic on paper.

Start by writing down four 0's:

0000 (make this equal to 0)

- + 1 (add 1)

- 0001 (this equals 1 in the decimal system)

Now remember that decimal 9 is the highest number used in base-10 arithmetic. Thus, when you reach 9, the addition of 1 changes 9 to 0, and a 1 is "carried" to the tens column.

In the binary system, the highest number used is 1. When 1 is added to 1 in the binary system, the sum is 0, and a 1 is carried to the next column to the left. If there is already a 1 in that column, the sum is again 0 and the 1 carries to the left again, etc.

Adding 1 to 0001:

$\begin{array}{r}

0001 \\

\pm 1 \\

0010

\end{array}$

This equals 2 in the decimal system because you have accumulated two 1's, and the 1 is the second space to the left, which is in the 2 column (Table 2-2).

Now add another 1:

$\frac{0010}{0001}$   $\frac{0001}{0011}$  (This is 1 + 2 = 3 in the decimal system)

Add another 1:

$\begin{array}{r}

0011 \\

\pm 1 \\

0100

\end{array}$

This is 4 in the decimal system, since the 1 is now in the third space to the left  $(2^2 = 4$ , as shown in Table 2-2).

When you continue this process to 1111, you will have developed the 4-bit binary table of Table 2-2.

For practice, add 0111 and 0110 as in Fig. 2-3. Row 1 contains the augend and row 2 the addend. Row 3 shows the addition of 0 and 1 = 1 with no carry. Row 4 shows the sum of 1 + 1, giving 0 and carry 1. In row 5 column C, you already have two 1's with a previous carry of 1. In this case, you must put down your previous carry as shown; then you still carry 1 to the next column. In row 6 column D, you simply record the carried 1. The total, 1101, is in row 7.

Check this addition in decimal form. You know that binary 0111 is equal to decimal 7 (1 + 2 + 4 = 7). Also, 0110 = 6. So 7 + 6 = 13, and binary 1101 = 13.

Table 2-4 reviews binary addition. We will refer back to this as we progress.

You have already noted that the digits to the left of the binary point are coefficients of increasing *positive* powers of 2, with  $2^{\circ}$  adjacent to the binary point. The digits to the right of the point are

| Row | (   | Colu | lwL | 1 |                       |

|-----|-----|------|-----|---|-----------------------|

|     | D   | С    | В   | Α |                       |

| 1   | a   | 1    | 1   | 1 | Augend                |

| 2   | + 0 | 1    | 1   | 0 | Addend                |

| 3   |     |      |     | 1 | No Carry              |

| 4   |     |      | 0   |   | Carry 1               |

| 5   |     | 1    |     |   | 1 Carried and Carry 1 |

| 6   | 1   |      |     |   | 1 Carried             |

| 7   | = 1 | 1    | 0   | 1 | Binary Total          |

Fig. 2-3. Addition of binary numbers 0111 and 0110.

| BINARY A + | в+  | PREV | CARRY = | SUM | NEW CARRY |

|------------|-----|------|---------|-----|-----------|

| 0 +        | 0 + | 0    | =       | 0   | 0         |

| 0 +        | 0 + | 1    | =       | 1   | 0         |

| 0 +        | 1+  | 0    | #       | 1   | 0         |

| 0 +        | 1+  | 1    | =       | 0   | 1         |

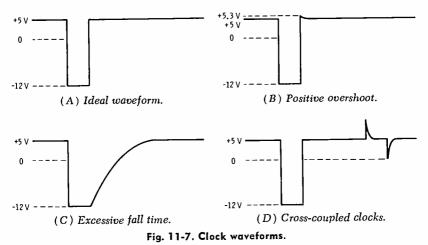

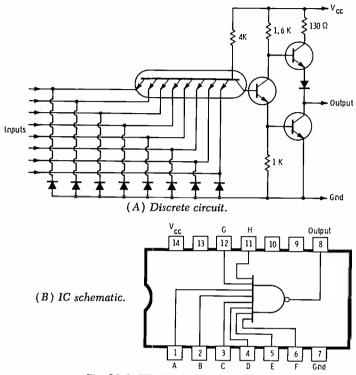

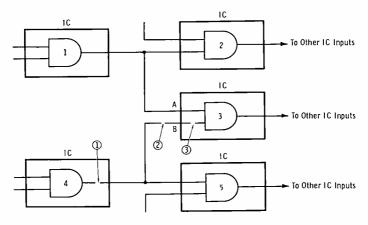

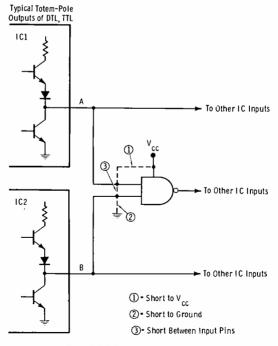

| i +        | 0 + | 0    | =       | 1   | 0         |