July 1976

Volume 46 No. 7

Founded 1925 Incorporated by Royal Charter 1961

"To promote the advancement of radio, electronics and kindred subjects by the exchange of information in these branches of engineering."

## The Radio and Electronic Engineer

The Journal of the Institution of Electronic and Radio Engineers

### The Public Image of the Engineer

Since the amenities of civilization have been largely created by engineers it is sad to see a revival of Shakespeare's thought, 'For 'tis the sport to have the engineer hoist with his own petard'. Written over 350 years ago into his most exaggerated tragedy Shakespeare's words still '... go hard' with those who have had the patience and diligence to prove their right to be called 'engineers' only to receive little praise and, so often, little reward. Too often criticism of their labours is but a diversion to distract from political, economic and other ills.

Does the engineer therefore stand in need of tutors to inform government and the public on the importance of the engineer in society? Maybe public appreciation of the engineer has been dulled by the munificence of his products: radio and television in all its international communication roles; electronic navigation systems without which air travel could never have reached its present magnificence; the art of recording for entertainment, for teaching and as a scientific tool; and as a final example the electronic processing of food and steel manufacture. These are but a few demonstrations of how the public benefit from the labours of the professional radio and electronic engineers. Are these not as great monuments as the one that over 200 years ago gave Christopher Wren his epitaph 'Si monumentum requiris, Circumspice'—'If you would see his Monument, look around'.

The examples chosen do not deprecate the contributions of members of our sister Institutions to modern living. To the contrary even members of much older branches of the engineering profession are equally concerned with undervaluation of the status of engineers whose services to modern society are taken for granted. Such lack of appreciation acts as a brake on recruitment, especially to the manufacturing industry which creates the main wealth of the country. A Gilbertian situation which might be corrected by using promoters of public relations as recommended by the Council of Engineering Institutions. A far cry from the epitaph of Wren but a consequence uf the soccess of pressure groups which now influence legislation and public opinion.

Before embarking on a public relations exercise it is important to understand both problem and purpose. The problem is to educate all sectors of the public on the fact that the professional engineer provides 'skilled services for which both an academic and a vocational qualification are required. These require previous training and years of delay before earning capacity is achieved. All professional men and women therefore begin their lives with a sacrifice of leisure and income.'

These basic qualifications apply to engineers of varying specializations. Just as the Civil, Municipal, Mining or Marine Engineer would never claim to have engendered the technology of radio and electronics nor does the electronic and radio engineer claim *especial* public recognition of his training and achievements. There is common concern about the evaluation of the engineers rôle in society.

This theme was developed by Lord Hailsham when he gave the 'Rivers Lecture' at The Institute of Chartered Secretaries and Administrators in which he asked, 'If there can be a Confederation of British Industry why can there not be a Confederation of British Professional Associations, however loosely associated, to identify the problems which affect us all?'

It is in identifying '... the problems which affect us all' which is the nub of Lord Hailsham's Lecture. He emphasized the growth in the number of professions and that their services more than ever in the past were essential in the common weal. How best can engineers present this case?

G.D.C.

The Rt. Hon. Lord Hailsham of St. Marylebone was Lord President of the Privy Council when in 1961 the Institution received its Royal Charter.

# Contributors to this issue<sup>\*</sup>

Tuvia Lamdan (Member 1976) received his M.Sc. degree in 1957 from the Hebrew University in Jerusalem, and his Ph.D. degree in 1963 from the University of Manchester, as a result of research in the Electrical Engineering Department. Until 1969 he served with the Scientific Department of the Israeli Ministry of Defence and in 1969 joined the Department of Applied Mathematics of the Weizmann

Institute of Science. Here Dr. Lamdan's responsibilities included development of the input/output system of the *Golem B* computer. His present interests include computer hardware and architecture, design automation of digital systems and computer instrumentation systems.

the Technion in Haifa, Israel, receiving the B.Sc. in electrical engineering in 1969; and he obtained the M.Sc. in 1975. For several years he was a Design Electronic Engineer in the Research and Design Laboratories of Tadiran at Givataim, Israel. He is now working in Canada as a Design Electronic Engineer with Glenayre Electronics of North Vancouver, British Columbia.

Moshe Aharon was educated at

Godfrey Townsend received the degrees of B.Sc. and Ph.D. in physics at the University College of Swansea in 1952 and 1956 respectively. From 1955 to 1958 he was a Scientific Officer at the Royal Aircraft Establishment, Farnborough, working on silicon rectifier development. He then returned to the Department of Electrical and Electronic Engineering at Swansea, where he stayed for sixteen years,

initially as a Lecturer and then as a Senior Lecturer. During this period he was responsible for setting up a laboratory for making and studying prototype silicon active devices. He has concentrated particularly on the application of f.e.t.s in linear circuits and is co-author (with W. Gosling and J. Watson) of 'Field Effect Electronics', as well as of numerous technical papers. His other research interest is in silicon solar cell technology. This work he is continuing at the Royal Military College of Science, Shrivenham, where he has been Professor and Head of the Physics Branch since 1974.

<sup>\*</sup>See also pages 331 and 336.

Andreas Demetriou studied electronics and telecommunications at the University of Wales Institute of Science and Technology and was awarded the B.Eng. degree by the University of Wales in July 1970. He then researched in solid-state physics at the University College of Swansea, and gained his Ph.D. degree in July 1975. He joined the MOS Technology Group at the Standard Telecommunications Lab-

oratories Ltd. in November 1973, and at present is working on the development of new processes and devices and their applications.

Zvi Riesel (Member 1960. Graduate 1950) is an Associate Professor of Computer Engineering at the Weizmann Institute of Science, Rehovot. He joined the staff of the Institute in 1954 and has since then taken part in the design and construction of three digital computers: the WEIZAC (1955), the Golem A (1964) and the Golem B (1974). In 1970 he was awarded the Rothschild Prize for his con-

tribution to the design of *Golem A*. His main interest at present is design automation of digital systems.

Roger Owens received the degree of B.Sc. in physics from the University of Bristol in 1962, and an M.Sc. in microwave physics from the University of London in 1968. He worked on aerial systems and microwave components for EMI Electronics Ltd., Feltham, from 1962 to 1967, when he moved to the Royal Military College of Science, Shrivenham, as a Research Assistant in the Electronics

Branch, studying Gunn oscillators and their equivalent circuits. In 1972 he was appointed a Senior Research Fellow at RMCS, and has since been concerned with the design of microwave integrated circuits.

Don Price obtained a degree in physics at the Royal College of Science, London, in 1952, and for the next ten years worked at the British Aircraft Corporation (Guided Weapons Division) on guidance systems and ground equipment for guided weapons. Since 1963 he has been employed by Marconi Elliott Avionic Systems Limited, initially in the Automatic Test Equipment Division. Since 1968 he has held the post

of Technical Manager of the Flight Automation Research Laboratory.

## The development of an automatic wiring analyser system for testing telephone switching rack backplanes

### **B. COOLBEAR\***

and

G. LOVITT, M.B.C.S.†

Based on a paper presented at the Conference on Advances in Automatic Testing Technology held in Birmingham from 15th to 17th April 1975.

#### SUMMARY

This paper describes the various stages in the evolution of a computer controlled automatic test system for checking the validity of the backplane wiring of very large electronic telephone exchange switching racks. Although the basic testing requirements are simply wiring continuity and insulation testing, the large physical size and the diversity of hardware to be tested in an essentially random sequence necessitated a very large and complex test system.

The solutions to the difficult interface problems and those of handling are described, together with the approach taken to solve the complex software and programming problems, including those caused by the large volume of data to be handled.

#### **1** Introduction

TXE 4 is the name of the new generation of electronic telephone switching systems currently being installed in telephone exchanges by the Post Office. It was a firm requirement that the backplane wiring on the racks must be demonstrated to be better than one wiring error in every five thousand wiring terminations. This was intended to minimize the expensive and time-consuming task of rectifying wiring errors on installation, a situation which is aggravated by the increasing shortage of skilled engineers to do the work.

Until this time production wiring inspection had always been done manually by conventional 'bridge and buzz' methods. Apart from the difficulty of establishing exactly the efficiency of a manual inspector, there is the overriding problem that however good the inspection is, there is no final demonstrable evidence of the quality of the finished wiring, particularly the presence of additional wires.

A design study was therefore started to examine the problems and produce a specification for an automated test system. A system of this type divides into two halves, the first half being the fixturing, which includes product handling, contact accessing and machine interface, and the second half which is the wiring analyser and control system.

Initial consideration was given to manufacturing the whole test system in-house, but neither the time nor the expertise was available to produce the analyser and control half as appeared to be required for such a test system. A number of small test systems are being operated within STC for testing the modules which plug into the TXE 4 racks but experience with these was insufficient to build a rack wiring analyser with confidence. A market survey was therefore conducted to find a suitable supplier for this part of the system, and work continued on the design requirements of the fixturing with a view to producing this ourselves.

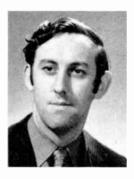

#### 2 TXE 4 Racks

A TXE 4 rack is a bulky structure, standing  $3 \cdot 2 \text{ m}$  (10 ft 6 in) high by  $0 \cdot 91 \text{ m}$  (3 ft) wide by about  $0 \cdot 46 \text{ m}$  (18 in) deep, with a framework made from aluminium alloy extrusions. Figure 1 is an outline of the rear view of a typical rack.

The rack is subdivided into a number of sub-racks or shelves with sets of guides for printed circuit cards or card modules, and the main backplane consists largely of rows of edge connectors with wire wrap pins. There are several rectangular 12-pin power connectors in various positions on the backplane for power supply modules, the wiring to these being soldered.

Above the main backplane is a variable-sized terminal field positioned in a different vertical plane, built up from loosely retained 72-pin blocks with wire wrap pins on both sides. This field is used for the inter-rack exchange cabling. The bulk of the rack wiring consists of interconnections between these three types of connector, with a limited number of additional wires to a fuse panel

<sup>\*</sup> Standard Telephones and Cables Limited, Telephone Switching Division, Oakleigh Road South, New Southgate, London N11 1HB.

<sup>†</sup> Standard Telecommunication Laboratories Limited, London Road, Harlow, Essex CM17 9NA.

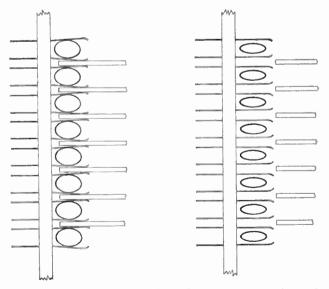

Fig. 1. Rear view of a typical rack.

at the top, and to a small but highly variable number of test sockets and indicator lamps on a lower front panel.

There are about thirty different basic rack types, each of which has a different number or combination of the four basic shelf sizes, to a maximum of ten shelves per rack. The number and position of edge connectors on the shelves is variable up to a maximum of 40 per shelf. The number and position of the power connectors is also variable. On a number of racks there is an additional problem of having from one to four of the 72-way terminal field connectors mounted at the end of certain shelves, but more or less in the same plane as the edge connectors (see Fig. 2). By virtue of this variability, each rack type is physically different, in the way it is equipped, from any other type.

Apart from the physical differences, there are also problems with the wiring. Due to the unique switching requirements of each telephone exchange, a small percentage of the wiring on each rack has to be specific to the exchange where the rack will be installed. The bulk of the wiring on a rack, that which remains the same from one unit to the next on any type, is termed basic wiring, and the additional variable wiring (which in practice may also include some deleted wires) is termed contractual strapping. The overall effect is that each rack manufactured is virtually a one-off model.

Production is organized on a small batch basis, partly due to the exchange by exchange ordering procedure, and partly because any attempt to build longer runs of basic rack types would require excessive storage space and tie up large sums of capital. It is also doubtful if any

Fig. 2. A view of part of a typical TXE4 rack showing the variety of connectors to be accessed.

significant improvement in quality or throughput would be achieved, as most of the wiring is of a random and non-repetitive pattern. One of the basic requirements of a test system was therefore, that it should be able to test racks presented in an essentially random sequence.

#### **3 Access Problems**

One of the basic and most important problems was how to make access to the wiring terminations. There are up to 50 000 termination points on some racks and although not all points are wired, they should be accessed to detect possible wrong terminations and extra wires.

Access to the rear of the backplane was ruled out due to a number of factors such as the possibility that wire wrap pins become bent out of line during manufacture; the mixture of solder tags and wire wrap pins; the float in the connectors; and the thick mat of wiring which would hinder access. Additionally, of the various access techniques available, the only one generally applicable in this case would be spring pin probes, and apart from the lack of adaptibility to cope with the variations of rack configuration, this technique would require an impossibly complex and massive back-up structure to resist the huge total spring loads applied.

Frontal access to the backplane requires entry into the body of the rack, and the question then is, 'Can the backplane be removed and tested independently?' The problems here include the fact that the terminal field is a separate item, but integrally wired to the main backplane, which would present handling problems. Due to noise segregation, some of the wiring runs are away from the backplane, inside the rack structure, which would make removal and replacement hazardous. The backplane is an assembly of separate connector frames built-in as an integral part of the jig assembled main structure thereby making removal impracticable.

In retrospect it is clear that considerable simplification of the whole test system might have been achieved had the automatic test access requirements been a requirement of the initial rack equipment practice design. But the design was now too far along the road to full production to effect more than minor modifications to ease the access problems and so we were faced with an additional problem of devising a mechanical handling system for massive racks weighing up to 320 kg each in the process of testing them.

For the method of accessing the edge connectors, which contain the bulk of the access points, there was really only one technique; to use test cards plugged into the edge connectors and wired via some form of interface to the test system, as yet unknown. In view of the large number of cards involved and their relatively high insertion force, it was decided that the best, the most economic and least time-consuming method would be to devise an adapter unit system, comprising some form of box-like structure containing a shelf load of cards, which would be loaded into a shelf position, and to have a mechanism to push the cards the last half an inch into engagement. The adapter units would be easily re-equipable with new cards, and this would also enable us to provide a special module to mate with the power-connectors which could

be quickly inserted in the appropriate position just prior to loading the adapter units. This general approach was made easier by virtue of the fact that the racks are designed using a modular dimensioning system. The connectors are mounted on insert strips with holes at a precise 0.8 in (20.32 mm) pitch, and in the rack vertical axis, all equipment sizes and spacing is based on an exact 0.6 in (15.24 mm) pitch. Also, there are basically only two shelf aperture sizes although, as previously mentioned, these can have connector arrays of four different heights fitted to them on the backplane. Fortunately any one connector frame will only have one size of connector fitted to it. This meant that the adapter system could be limited to two basic sizes of adapter units and cards with only the mating ends of the cards in different sizes.

The most difficult access problem remained to be solved, how to access the terminal field connectors. These are a specially developed design with 72 through pins of rectangular cross-section in an 8×9 layout on 0.2 in (5.08 mm) pitch in both axes. On each side of the connector there is room for one wire wrap, then the ends of the pins are reduced in cross-section to receive special 18-way sockets on the exchange cabling. This plug and socket arrangement is a deliberately high insertion force design (approximately 4.5 kg per 18 ways) with very sharp-edged tin plated pins. This provides reliable connections for a few insertions in normal use but is a highly destructive combination for any socket used on test equipment which must withstand many hundreds of insertions. Additionally the high insertion force prohibited the ganging of sockets for manual insertion, and the limited strength of the backplane eliminated ganged mechanized insertion. It was clear that a specially designed zero or low insertion force connector would have to be used which, to minimize plug-up time, would have to access large groups of pins at one time.

There remained a number of terminations not so far considered, such as the fuses and lower front panel. With one exception, however, these had such highly variable configurations that in view of the small number of wires involved, the complexity and cost of making access would be prohibitive. The rationale was therefore applied, that providing that the machine accessed terminations could be verified to a very high accuracy, say 1 error in 20 000, then the anticipated error rate from manually inspecting these few remaining wires would not derate the error level for the whole rack to worse than 1 error in 5000 as required. This residual wiring was also of a nature which was inherently much more easily inspected.

The one exception to this philosophy was for a group of rack common services connectors which were of a consistent configuration, and although they were difficult to access, it was felt that a connector could be devised, and would probably be used on a flying cable.

#### 4 Test System/Adapter Unit Interface

In order to be able to connect to the test system the various combinations of adapter unit with which a rack might be equipped, it would be necessary for every adapter unit to be fitted with some form of common interface connector or connectors.

The initial schemes for the system envisaged some form of fixture to hold and support the rack, the latter being loaded with appropriate adapter units, and then, with some form of structure supporting the cabling, the interface connectors would be manually positioned and attached to the adapter units. This simple-sounding plan had a multitude of pitfalls.

Firstly, for example, the majority of shelves have a total of either 3120 or 5040 possible terminations. Therefore, for a common interface, this requires connectors with at least 5040 pins. The largest connectors commercially available have only about 100 or so pins, which would require at least 50 connectors for each adaptor. This was obviously not practicable. A prototype low insertion force connector was produced by Smiths Hypertac which was a compact 1276-pin connector with a single jacking screw. The prototype was surprisingly easy to operate and if used would have only required four connectors for each adapter unit; but it would still have needed a considerable amount of effort to use and, more important still, a long time to interface the rack on line with the tester, thereby wasting valuable testing time.

The second problem was the bulk of cabling to the interface connectors. Whatever testing attitude was adopted for a rack, only a proportion of the weight of cabling and connectors could be supported mechanically, leaving probably between 4.5 and 6.4 kg per connector to be handled by the operator, and in addition, with the large numbers of wires involved, each cable would be very stiff and difficult to handle.

Partly in response to these cabling problems, a parallel study was carried out, to investigate the approach of mounting semiconductor switching logic directly on to the access cards in the adapter units. This would have the advantage of drastically reducing the number of wires to the access array. The major disadvantage of semiconductor logic is the low operating voltage, typically 5 volts, which precludes high voltage insulation testing. It was decided that, as commercially available test systems using this technique, at that time, were insufficiently well proven to our satisfaction, and to embark on an inhouse development programme was not desirable, we would have to reject this approach.

#### 5 Choice of Supplier

It was becoming evident that the extent of the unsolved fixturing problems, of which only a few have been enumerated, was too great to allow us to develop an optimum solution in a reasonable timescale with our available manpower and resources. With a requirement for progressively more of the fixturing to be machinecontrolled it also seemed desirable to have the fixturing manufactured by the supplier of the analyser and control system, to ensure the maximum degree of compatibility between the various parts.

Our market survey had found very few potential suppliers of large wiring analysers with adequate complex fixturing experience, who did not also appear to consider fixture designing as some form of engineering loss leader to encourage analyser sales.

After very careful assessment of overall capability, we chose Hughes Aircraft Company of Los Angeles to design and build the test system to a very comprehensive specification produced by STC.

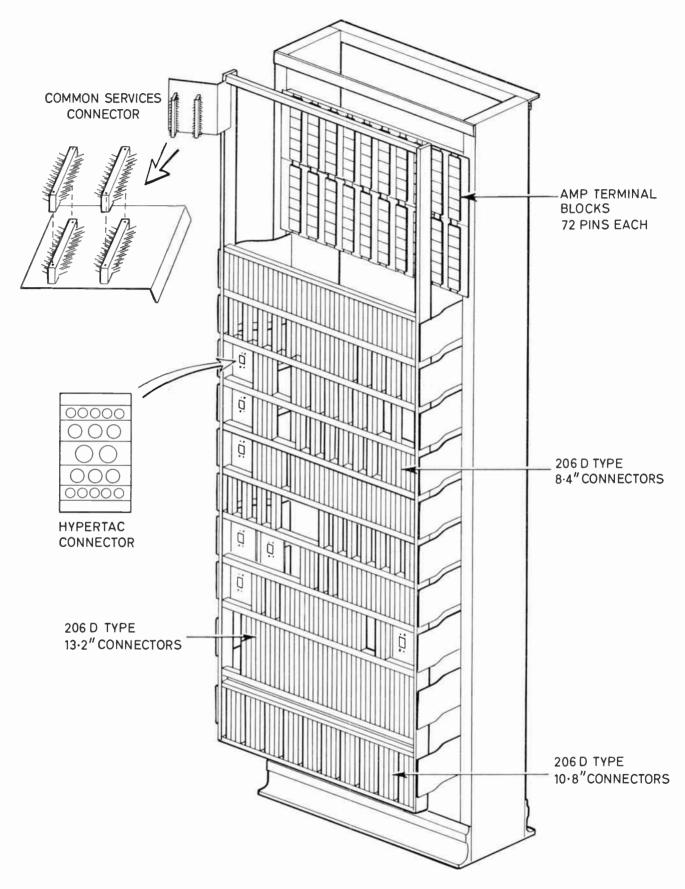

#### 6 Basic Test System

The heart of the Hughes test system is the FACT II (Flexible Automatic Circuit Tester) wiring analyser. This is a high-speed reed-relay based continuity and insulation leakage tester. With its built-in control, which is in effect a dedicated mini-computer, it is able to receive a prepared test program from any one of a variety of peripheral devices, execute the circuit testing of the unit under test (u.u.t.), including the issuing of command instructions to any automated fixturing, and will then output the test results to the chosen peripheral device. A comprehensive range of features and facilities are available on this reliable machine, which is extensively used in the aerospace and telecommunications industries in particular. The test rate for this machine is 4000 continuity tests per minute and 2000 leakage tests per minute.

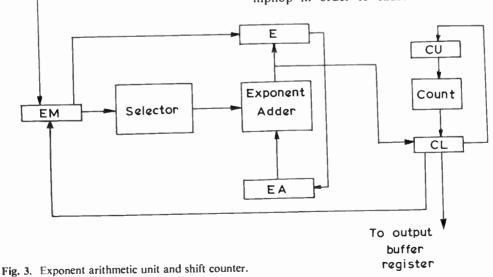

This company has also developed a number of specialized techniques to assist in the rapid adaptation of a u.u.t. In our case, in particular, they were the only supplier capable of demonstrating a proven method of zero insertion force adaptation to our terminal field connector. This particular adaptation method is called LIFT (low insertion force technique, see Fig. 3) and consists of rows of terminal pins set in a non-conductive base material, at a spacing adequate to allow the friction-free insertion of the contacts to be mated. Inflation of a thin pneumatic bladder threaded between the LIFT pins causes them to engage and hold the test contacts. Operation is at about 240 kN/m<sup>2</sup> (35 lbf/in<sup>2</sup>) and is positive and rapid.

With the use of this technique it was possible to design drop-in adapter units for the terminal field on the racks, to access blocks of 2880 pins at once with the only effort

Fig. 3. Schematic representation of LIFT connector shown in pressurized and depressurized states.

being to support the weight of the unit whilst locating it in position. This size of adapter was chosen as a convenient part of the terminal field nearest in pin total and physical size to a small shelf adapter. A number of this size of terminal field adapter and some smaller sizes, a total of six units, can be used in various combinations to access any size of terminal field on a rack, using no more than three units at any one time. Hughes have also had considerable experience in designing adapter units similar to those required for our shelves of edge connectors. In this application the adapter units were designed to contain a full complement of 40 extender cards. Each card has a set of contact pads to mate with an edge connector in the rack, and at the opposite end another set of smaller contact pads, both sets of pads linked by copper strips. The shape of the extender cards is tailored to match the various sizes of edge connectors used on the rack, but in every case the opposite end of the card has a common pattern of contact pads. The end result is that when a rack is loaded with adapter units. all adapter units irrespective of size, present a uniform array of rows of 40 identical printed card edges. This corresponds to the adapter unit common interface described earlier. Using another application of the LIFT technique, the test access heads of the analyser contain rows of bladder-actuated pins, behind a slotted check plate guide, matched to the extender cards in the adapter In order to reduce the number of redundant units. contacts and due to a number of other constraints, the larger sizes of shelf extender cards have the interface contact pads divided into two groups, both equal in size to those on a small adapter unit, and therefore large adapter units are mated with two test access heads at once. The six terminal field adapter units are internally hard wired from their LIFT contacts to a set of printed card edges so that they also present a common interface

The use of this combination of techniques results in the time taken to connect the test access heads of the analyser being reduced to a few seconds, minimizing wasted testing time, with the job of loading adapter units, which takes about 30 minutes, carried out as an off-line operation. The basic method of operation is to leave the adapter units in the racks until all test, rework and retest cycles have been completed, but they may be off-loaded if, for instance, the first rework is likely to take a long time, or there is a temporary shortage of a particular type of adapter unit.

#### 7 Test System Mechanical Operation

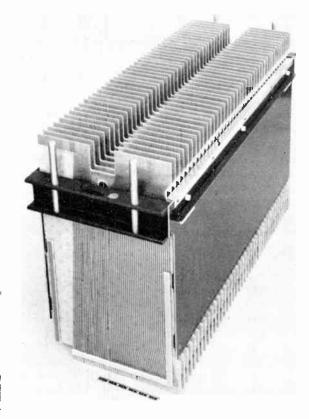

when loaded into a rack (see Figs. 4 and 5).

A TXE 4 rack is normally moved between work stations lying on its side on a set of castors bolted to it. When ready for testing, it is rolled into one of a number of large mobile holding jigs, known as rack transporters, where it is manually clamped in position. The transporters are equipped with electrically-powered lifting and rotation facilities. The rack is raised from the floor and turned on to its back, that is, with the wiring plane on the underside. Adapter units are now loaded, with the assistance of overhead hoists, and the extender cards are pushed into the edge connectors with a portable automatic card inserter. The transporter is docked against

Fig. 4. Rack adapter unit to access one large shelf in a rack.

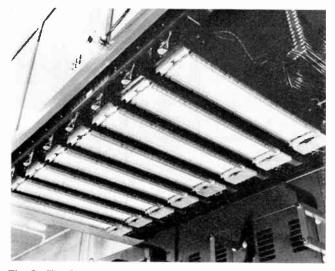

the front of the access fixture and automatically clamped in position beneath eight test access heads. The test is initiated and the rest of the test cycle is carried out automatically. The eight heads are lowered together sufficiently to be able to engage pairs of index pins on the adapter units. The heads are then traversed along the rack until they are correctly registered over an adapter unit, using the index pins as a reference, and are then lowered to engage the extender cards with the LIFT connectors in the heads. The LIFT bladders are inflated

Fig. 5. The 8 test access heads of the analyser test fixture, viewed from below. These accept the plug blades at the top, of the boards in Fig. 4.

to make contact and testing is carried out. When testing is completed, the bladders are deflated, the heads are raised fully up and traverse back to their starting point. After disengaging the transporter and collecting the wiring error print-out, the rack is wheeled away for rework. The rack can be rotated in the transport to a suitable attitude for rework and is also adjustable for height.

Although TXE 4 racks contain up to possibly 50 000 termination points, of which the vast majority must be tested by the machine, in fact only 26 400 test points were specified for the analyser. Of these, only 25 920 are allocated to the test access heads, and 80 are used on two small hand-attached LIFT adapters for the common services connectors on the rack, which are on flying leads from the fixture. The remaining terminations are used for calibration or spare.

This economy of test points is effected by the adoption of a multi-pass mode of operation, described in Section 9.

#### 8 Size of Machine and Test Philosophy

The choice of what size of analyser to have, in terms of the number of points accessed at one time, is more difficult than it might appear at first sight. There are two basic options, firstly to choose a machine with sufficient test access points to test the largest foreseeable product in one accessing operation, or secondly to have a smaller analyser, only partially accessing the product in one step, and to use a multi-pass mode of operation, where the test access points are moved along the product in discrete steps, performing testing, in effect, as a permutation of any X from Y number of stages.

The choice is primarily an economic one, with the cost of any analyser being almost directly proportional to the number of test points after an initial basic price, not forgetting that for every analyser test point there must be an additional adapter access point in the fixture, the relative cost of both being very high.

Some secondary considerations affecting the choice are, for a single-pass mode, the advantage of only performing the minimum number of tests without duplication, and the minimum on-line accessing time which is important with high production throughput, with a fairly simple fixture control system, set against the drawbacks of the fact that for a large part of the time some test points may remain unused if the product is of variable size as in our case, and also the need for a more massive fixture. The pros and cons of a multi-pass mode, apart from cost, are, as generalizations, not impressive. The system is fully utilized, the hardware is less bulky and is easier to repair and maintain, but it will take longer to perform a whole test, due to the extra time taken to reposition the test access heads and the large potential number of redundant tests that would be carried out. This last factor can be significantly improved by a carefully planned test routine which suppresses a proportion of these extra tests.

The control of the fixture is, of course, more complex in a multi-pass mode and if, as in our case, the pattern of passes is different from one product to another, the programming is more complicated. Despite this lack of positive advantages, in some circumstances multi-pass can be a quite satisfactory method. Consideration of the parameters of the STC system may bring this out better.

#### 9 Multi-pass Operation

When a rack is loaded with adapter units, there are normally between 8 and 13 rows of card edges presented to the 8 test access heads. Their pattern of movements is in fact more complicated than the simplified sequence quoted in Section 7. Let us assume our u.u.t. has 12 access positions. The cycle will start as indicated earlier by the heads being partially lowered, followed by traverse to the first 8 access positions. The heads are lowered, testing carried out, and heads raised, but now heads 5 to 8 move to access positions 9 to 12 and all heads are lowered and a second test pass is carried out. The 8 heads are raised again, and this time heads 1 to 4 move to positions 5 to 8 and a third test pass is made. Finally all heads are raised and return home. For racks with only 8 positions, of course, only one test pass is needed; for racks with up to 11 or 12 positions, which are the majority, some variation on the 3 test pass sequence above is used; and for racks with 13 positions 4 test passes are required.

However, the total time for all head movements in any test cycle does not exceed  $2\frac{1}{2}$  minutes in a total test cycle time of between 12 and 20 minutes per rack. This rate is fast enough to deal with the anticipated rack throughput.

#### **10 Control System**

At some stage in the evolution of the specification it became obvious that we needed a computer to control the system. One very strong reason was that the solution to the contractual strapping wiring problem referred to in Section 2 required the use of a computer. Rather than generating a completely different test program for every rack that is to be tested, which would be very costly and cumbersome, an alternative method was sought. Examination of the wiring data for the racks revealed the fact that the contractual strapping was generally of a fairly stereotyped pattern even though the pattern changed from rack to rack, with recognizable single or groups of wires to be added or deleted. A table of these strapping elements was produced so that any set of strapping could be defined as a series of these elements or options. Therefore a test program would consist of the basic wiring plus the contractual strapping options. Some constraints had to be imposed on our engineering departments to adhere to this format when generating the rack wiring data. The test system mini-computer works in conjunction with a dual disk storage unit. A number of basic wiring test programs are stored on disk together with the library of strapping options. Only a short call-up tape needs to be generated for each rack giving its code, the appropriate reference for its basic test program and list of contractual When these data are strapping option references. received by the computer, it extracts the information from the disk and amalgamates this to produce the rack test program. The operation takes from a few seconds to a few minutes, but will not normally constitute a delay as the processing is carried out whilst the rack is being set up for testing.

This arrangement has another important advantage in that because each rack is virtually unique, its test program is of value only whilst that rack is in the test area, hence the short call-up tape, which need only be punched just before the rack is ready for test, can be easily disposed of afterwards and is much more suitable for keeping with the manufacturing paperwork accompanying the rack than would the half dozen or more reels of paper tape of a discrete test program.

With a computer we were now able to operate a more efficient multi-pass mode of operation, and use it to perform translations between analyser pin notation and rack pin notation.

The system was also specified to be able to operate a second analyser with the same computer, on a timesharing basis, to enable the system to be expanded at a later date.

The computer is used to derive data from the test results for a management information system (m.i.s.). Various statistics are compiled whilst the system is in operation, such as the number of racks of various types processed, the number of faults per rack, the accumulative totals of faults, system faults failures and input messages, all referenced to a time of day clock built into the system. These statistics are stored and transferred periodically to magnetic tape for off-line analysis, in order to provide a management tool for production monitoring.

The test system is furnished with a comprehensive collection of fault monitors and error detection devices. These range from internal electronic test circuits, to air and power supply monitors and to physical fault detectors such as access head position and misalignment, u.u.t. and adapter unit alignment, and various other fixture parameter checks.

Faults which arise during operations, either shut down or stop the operations if sufficiently important, or else produce an error information printout on a teletype. There is also a comprehensive array of monitor displays to assist in rapid fault isolation and repair.

The test system is programmed to perform automatically a full self-test routine once every day, which exercises the system down to the contacts in the LIFT heads, beginning at start-up in the morning and continuing between periods of product testing until a complete self-test cycle has been made.

#### **11 Software Philosophy**

Although the provision of suitable data for the test system is an obvious necessity, it perhaps is less apparent that it must be made an integral part of the system design and will even affect the choice and design of the hardware. For TXE 4 the manufacturing information for backplane wiring was already computer-produced from engineering data input. It was found possible to use the same engineering data input also to generate the test data, thereby guaranteeing the validity of the tests, i.e. manufacturing has been correctly carried out to the wiring information. If the test data had been manually prepared, the cost would have been prohibitive and the accuracy would have been poor. Having opted for a computer-controlled test system, careful decisions were made on how much processing could reasonably be expected from the SPC16 minicomputer controlling the analyser. The manufacturing information is produced in a batched processing mode on an IBM 370/135 and it was decided to split the new software required between the IBM main processor and the mini-computer. The data processing involving large table look-ups with massive rearrangement of data was put on the main processor. The mini-computer was used for the analyser control, the storage and retrieval of test programs and control of the contractual strapping options, and generation of the m.i.s. statistics.

This division enables full use of a large computer with batched processing and on-line facilities without overload on the analyser system. The format of the engineering data input had been dictated by manufacturing requirements and certain incompatibilities were found when considering the new interface for the analyser. These were resolved with either extra constraints on the input data or extra software. An example of this difficulty was a first assumption that pins of the same signal name represent a wired net. In practice this was not the case as sometimes the net is not completed until the units are plugged into the rack. In order to satisfy the need that only complete nets are presented to the analyser, all pins associated with a signal name were checked for continuity by the software and split into one or more nets.

A further complication was introduced as some wiring does not appear on the original engineering rack wiring data input. This is sub-assembly pre-wiring of the TXE 4 connectors and was required to be tested. As the analyser system does not fully access all rack terminations simultaneously, the software had to divide the test data into separate analyser cycles. The large number of rack types and the variable nature of the shelves means that the cycle division is complex. Permanent system files containing physical information for each rack type, details for each shelf type and connector types were set up. For manufacturing purposes only those pins wired had been identified, but the insulation tests required that all pins on the rack be identified.

#### **12 Software Description**

The software can be split into functional areas of system file generation and maintenance; production of a test program in magnetic and paper tape forms; storage of the test program on the analyser disk; retrieval of the test program and an analyser run on the rack under test. For system file generation and maintenance software, programs were of a simple utility nature. Ease of file maintenance using minimum input, and the provision of comprehensive checks and reports were essential.

The interface between the two computers was exactly defined. For each rack an analyser test program was made in magnetic and paper tape forms. This test program was produced by a suite of software programs in sequence. The physical data relating to the rack is extracted from the system files, including shelf heights and details of pre-wiring and special connectors. The engineering input data are read and all the relevant data consisting of wire segments and associated signal name are placed on a disk work file. At the same time the pins used are marked in a complete bit matrix for every pin on the rack. A list of unused pins is thus generated. The

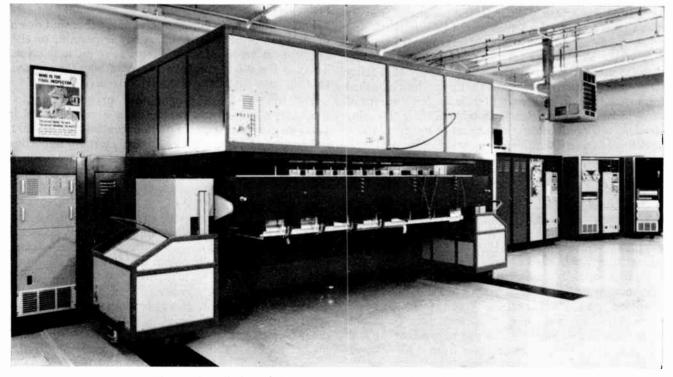

Fig. 6. Overall view of the analyser, computer, and test fixture, showing a TXE 4 rack loaded into a transporter in position for testing.

disk work file is sorted to bring all the wire segments associated with a signal together. One signal at a time is read into core and is checked for logical continuity as one electrical net or is split into several nets. Pre-wiring of TXE 4 connectors is merged at this stage by checking every pin against the table of connectors. These nets are written to a second disk work file which is used by the next stage to break the nets into the separate analyser cycles and output to a third file. A sort is made to divide the information on the third work file by analyser cycle. The list of unused pins is also similarly divided by analyser cycle and is merged with the third work file in producing the final output test program. At this final stage the translation from the manufacturing pin numbering system to that required by the analyser is carried out and extra control information for the analyser is inserted at the start of each cycle.

The separate, one stage at a time approach was essential because of the large volume of data being input and generated. A large rack will have an engineering input of 16 000 card images and an output of 1500 m (5000 ft) of paper tape. Some earth nets have over 1000 pins to be sorted. As the paper tape is only for emergency use, in the event of a mini-computer failure, it only contains data for continuity testing, in order to keep the total quantity of tape to be produced and stored to a manageable amount, and can only contain tests on the basic wiring. The magnetic tape holds all the data for both continuity and leakage tests. The mini-computer will transfer the contents of the magnetic tape to its removable disk pack so that rapid access can be obtained for any stored rack test program.

#### **13** Conclusions

The complete test system is physically very large (Fig. 6), the fixture and cabinet assembly being nearly 6 m (20 ft) from end to end, with a very high capital investment. In addition, the amount of floor space needed to operate all of the peripheral hardware such as rack transporters, and adapter unit handling and servicing facilities, is also high with over  $1100 \text{ m}^2$  ( $12\ 000\ \text{ ft}^2$ ) of factory floor committed to testing alone. Nevertheless, it has been estimated that the system will pay for itself quite quickly, for instance, the saving on not having to rectify wiring faults during installation alone would probably repay the cost in about three years, apart from obvious savings in other areas.

Therefore, although the initial reasons for acquiring the system were technical, it has also proved to be an investment.

#### **14 Acknowledgments**

Acknowledgment is made to Standard Telephones and Cables Limited and Standard Telecommunication Laboratories Limited for permission to publish this paper, and to the Industrial Products Division, Hughes Aircraft Company, Los Angeles, California, USA for their assistance and co-operation.

Manuscript received by the Institution on 30th December 1974 (Paper No. 1723/EPT 1.)

© The Institution of Electronic and Radio Engineers, 1976

### The Authors

Bruce Coolbear started work with Smiths Industries, Aviation Division, at Bishops Cleeve, in 1959 as a student apprentice, and studied at North Gloucestershire Technical College, obtaining an HNC in mechanical engineering with endorsements. For a number of years he worked on the design and development of aircraft flight deck instruments and then moved to ICL at Stevenage for a short period, where he

worked on the design of computer peripherals. Since 1970 he has been with STC at New Southgate and is currently a Senior Mechanical Design Engineer in the Test Equipment group, designing test equipment for telephone exchange electronic switching equipment.

Graham Lovitt was educated at Imperial College, London, and Enfield College, studying mathematics and physics. With this background, he joined Standard Labora-Telecommunication tories Ltd. in 1964 and for two years was concerned with the study of the optical properties of thin evaporated films used for infra-red optical filters. The evaluation led mathematical naturally into computer pro-

gramming and in 1966 he was engaged as a full-time analyst programmer in the computer applications division of STL. He is now a senior systems analyst and has worked on various systems including printed circuit board design and a compiler of a high-level test language for circuit boards. Currently he is developing and improving systems for telephone exchange cabling and back plane wiring.

## Letters

From: Professor J. Kroszczyński, Dr. habil. ing. J. K. Hsiao, M.Sc., Ph.D.

#### **Dual-frequency M.T.I. System**

In a recent paper<sup>1</sup>, Hsiao analyses the dual-frequency moving target indication system. While acknowledging that an analysis of this kind of m.t.i. system was conducted in my papers published before,<sup>2.3</sup> he writes further: 'Unfortunately, Kroszczyński's analysis is based on the assumption that the clutter return has only a single Doppler frequency ... Furthermore, Kroszczyński's result is not in a convenient form to compare with a conventional single-frequency m.t.i. system. In this paper we shall attempt to treat this subject in more general terms.'

I find Hsiao's remarks rather astonishing, because in my second paper<sup>3</sup> the analysis is conducted explicitly under the assumption that both the signal and clutter return are Gaussian stochastic processes (compare the text between eqn. (1) and (2) and summary in Ref. 3). In Hsiao's paper<sup>1</sup> only the clutter return is assumed to be a random process, but the signal has only a single frequency (compare eqns. (2a) and (2b) in Ref. 1). Therefore, I would have serious doubts if Hsiao's approach can be described as treating the subject in more general terms. It should be noted, of course, that Hsiao is to be credited for including in his analysis the effects of noise and an interesting discussion of its influence on the performance of the dual-frequency m.t.i. system.

I would also call attention to the fact that in my second paper<sup>3</sup>, eqns. (17) and (21) express the results in a very simple form, containing only the input signal-to-clutter power ratio and the clutter attenuation ratio (CA) of the canceller; the latter is known and has been used for quite a long time in the literature<sup>4</sup> concerning conventional m.t.i. radar systems. The question of convenience may be of course a matter of personal opinion, but I feel that eqns. (16), (17) and (20), (21) in my paper convey essentially the same meaning as expressed in Hsiao's conclusions on page 353 of Ref 1.

In further discussion, one point concerning the method of analysis may be stressed. To derive the improvement factor of a m.t.i. system, the input and output signal-to-interference ratios must be known. For such inherently non-linear systems as the dual-frequency m.t.i. this offers some difficulties, at least as far as the output signal-to-interference ratio is concerned. Hsiao circumvented this by separating appropriate terms in his theoretical expression (eqns. (4 a-f) in Ref. 1), while I have introduced a new concept: the ratio of average power at the output when signal present to the average power at the output when signal absent eqn. (11) in Ref. 3. This ratio can be measured in a straightforward manner at the output of any circuit, while it seems that rather the opposite may be stated in the case of an attempt to measure the signal-to-random clutter ratio at the output of a real, highly non-linear circuit. Therefore, while Hsiao's analysis is quite interesting from a theoretical point of view and gives much insight into the functioning mechanism of the dual-frequency m.t.i. system, it seems that for many applications the other way of approach would be more practical.

At the end of these comments I would like to add that I was very glad to learn that my papers have stimulated interest in the dual-frequency m.t.i. system. In my opinion, Dr. Hsiao conducted a detailed and worthwhile analysis of many aspects of this system and, apart from the points discussed above, I found his paper very interesting.

JAN KROSZCZYŃSKI

Przemysowy Instytut Telekomunikacji, Warszawa, Poland

29th December 1975

#### References

- 1. Hsiao, J. K., 'Analysis of a dual-frequency moving target indication system', *The Radio and Electronic Engineer*, **45**, No. 7, pp. 351-6, July 1975.

- 2. Kroszczyński, J., 'The two-frequency m.t.i. system,' The Radio and Electronic Engineer, 39, No. 3, pp. 172-6, March 1970.

- 3. Kroszczyński, J., 'Efficiency of the two-frequency m.t.i. system', *The Radio and Electronic Engineer*, 41, No. 2, pp. 77–80, February 1971.

- 4. Grisetti, R. S., Santa, M. M. and Kirkpatrick G. M., 'Effect of internal fluctuation and scanning on clutter attenuation in m.t.i. radar', *IRE Trans. on Aeronautical and Navigational Electronics*, ANE-10, pp. 37-41, March 1955.

Kroszczyński's papers on the two-frequency m.t.i. system are interesting and useful. However, I found that certain areas in these papers can be extended. For the first paper, clutter should be treated as a random process. For the second paper, the m.t.i. performances analysis can be extended to the cases of more than three cancelling pulses. Discussion on the choice of optimal filter weights and performance comparison with single-frequency system may be included. Effects of noise should be treated. These motivations were intended to be explained in the introduction to my paper. Unfortunately, during the process of editing, rewriting and oversight on my part, these comments are changed and replaced by sentences which may sound very critical. I regret this and wish to offer my sincere apology to Professor Kroszczyński.

J. K. HSIAO

Search Radar Branch, Naval Research Laboratory, Washington, D.C. 20375

24th June 1976

(*Editorial Note*. The original copy of Prof. Kroszczyński's letter was lost in transit to Dr. Hsiao.)

# Radio propagation in London at 462 MHz

R. C. FRENCH, Ph.D., C.Eng., M.I.E.R.E.\*

#### SUMMARY

Propagation measurements at 462 MHz relevant to a base station on a ten-storey office block and a mobile operating at seventeen locations in London are described. Signal level as a function of range is given and a slightly altered version of Okumura's prediction is shown to agree well with the measurements. Mean signal level distributions are found to be log normally distributed with a standard deviation of 5 dB. The envelope of the received signal level is shown to have a Rayleigh distribution.

\*Mullard Research Laboratories, Redhill, Surrey RH1 5HA.

The Radio and Electronic Engineer, Vol. 46, No. 7, pp. 333-336, July 1976

#### 1 Introduction

Information on radio propagation is necessary for the successful design of mobile radio systems for the police, fire brigade, ambulance service and many commercial users. Propagation is rarely line of sight and generally a number of waves are received at the vehicle by reflection from hills and buildings, etc. The interference of these waves produces a standing wave pattern which gives a variation of field strength (known as 'fading') along the street. As the vehicle moves through the fading pattern rapid fluctuations in the received signal level occur. This paper gives the analysis of measurements of received signal level (or, more accurately, the level of the signal envelope) made during field measurements in London.

A method of predicting the mean received signal level is given in references 1 and 2, based largely on measurements by Okumura *et al.* in Japanese cities and in cities in the USA. In essence the method consists of calculating the free space path loss and adding an empirical excess path loss given in graphical form against range and frequency. Corrections can be made for the base station and vehicle antennae height and for the type of buildings, which may be urban, suburban or rural. Measurements are compared with predictions made in this manner.

The measured signal level information is considered in three ways. First the dependence of the mean signal on range is found; this is needed to determine the coverage given by a transmitter. Secondly, the variation in the mean is found at a given range, which gives the expected error in a signal level prediction. Finally the variation in the received signal level relative to the short term mean is found at a number of locations at which the vehicle was driven over a prearranged route of about 1 km length. In a number of cities in the USA and Japan the signal level has been reported as having a Rayleigh distribution and consequently a 'Rayleigh' model is generally used in assessing diversity techniques aimed at reducing the signal variations. It is therefore important to know whether or not in London the signal level has a Rayleigh distribution.

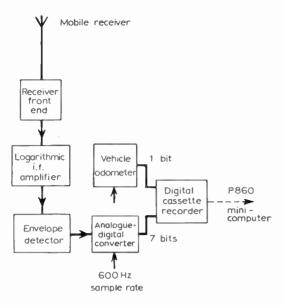

#### 2 Measurement System

Figure 1 shows a conventional mobile radio receiver front-end driving a precision logarithmic i.f. amplifier and filter. An envelope detector passes the received signal level to an analogue-to-digital converter which samples at 600 Hz to 7-bit accuracy. A single bit from the vehicle odometer (used in vehicle speed measurements not reported here) is added to give a 4800 b/s data signal for recording on a digital cassette recorder. In the laboratory the cassettes are replayed to a Philips P860 mini-computer for analysis. It should be noted that the signal level information is recorded as a function of time, not distance run by the vehicle.

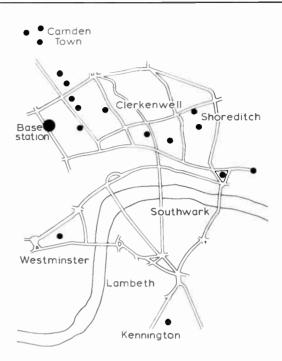

Measurements were made at  $462 \cdot 425$  MHz with a base station transmitter of  $3 \cdot 5$  watts output mounted on the roof of Mullard House, a ten-storey office block near Tottenham Court Road, London. The vertical base station aerial was 35 m high and had a gain of 2 dB relative to an isotropic aerial. The mobile aerial was 2 m high and had a gain of 5 dB. Signal levels are quoted in

Fig. 1. Measurement system.

dB relative to 1  $\mu$ V p.d. in 50 ohms (-107 dB mW). A map of some of the seventeen locations where measurements were made is shown in Fig. 2.

#### 3 Mean Signal Level against Range

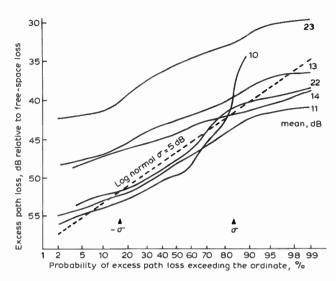

A mean signal level for a location was found by averaging the  $2.5 \times 10^5$  signal level samples collected during a seven-minute run over the prearranged route. Before averaging the samples were converted to linear form. Figure 3 shows a plot of these means as a function of range. Each group of points results from repeated measurements at a location.

Fig. 3. Mean signal levels as function of range for various conditions (462 MHz).

- 1. Free space

- 2. Best fit inverse power law

- 3. Okumura prediction

Fig. 2. Locations in London.

Three curves are also plotted in Fig. 3; one is the freespace signal level derived from the equation:

$$P_0 = P_t^{\uparrow} \left[ \frac{c}{4\pi df} \right]^2 g_b g_m \tag{1}$$

where  $P_0$  and  $P_t$  are the received and transmitted signal powers, d and f are the range and frequency in metres and hertz, and  $g_b$  and  $g_m$  are the base and mobile aerial gains. The second curve in the Figure is an inverse power law where the power has been chosen to give the best fit to the plotted data in the sense of minimizing the r.m.s. error between curve and data points. The third curve is the Okumura prediction obtained from reference 1, with London taken as an urban environment even though its buildings are more suburban in height.

As seen in the Figure the measured signal levels are 30 to 50 dB lower than would be received in free space, according to the inverse square law (curve 1). The Okumura prediction (curve 3) is mainly optimistic and lies about 7.5 dB higher than the best fit inverse power law (curve 2) at 1 km range and about 5 dB at 2.5 km range. At 7 km the curves cross. The best fit inverse power law has a power of 2.5 which shows a faster rate of attenuation than indicated by the inverse square law. This corresponds with the increasing excess path loss with range in the Okumura prediction.

The prediction agrees quite well with the measured data, even though London and Tokyo are very different from a propagation point of view, and Tokyo was the source of the empirical data used in the prediction. London has short streets with random directions and frequent bends and has few tall buildings. The lower buildings make London look more suburban from a propagation point of view which according to reference 1

Fig. 4. Cumulative distribution of short-term mean signal level for six locations.

should lead to signal levels 18 dB stronger than in a city. In practice they are 5 dB lower.

One speculation to account for the difference is that London streets will prevent the long range propagation of radio waves that occurs down the streets and avenues of a city built on a grid. Fewer waves will contribute to the sum at each point, leading to lower signal levels.

#### 4 Mean Signal Level Distribution

A short-term mean is calculated over 2800 signal samples, corresponding to 4.7 seconds or 42 m at 20 miles/h. The next short-term mean is found by adding 400 new samples and discarding the oldest 400, giving in effect a sliding mean. Between 300 and 600 such means are used in the distributions of Fig. 4.

Fig. 5. Signal level distributions for three locations.

The plotted curves show a reasonable approximation to log normal in the 10 to 90% region, which is all that can be expected with the number of measurements made. The standard deviation of the distributions is about 5 dB which agrees well with the result of 6 dB in reference 1 (page 123).

#### 5 Signal Level Distributions

The received signal level varies as the vehicle moves along a street. There are two aspects to this variation, one is the rapid variation caused by multi-path propagation and the other is a much slower variation due to changes in parameters like street width or building height. The first is wave interference, which can result in sharp nulls caused by wave cancellation, and the second is shadowing. To study the rapid variations due to fading it is necessary to separate them from the slower changes in signal level, which result from a different mechanism and have a different statistic. The slower variations are represented by the short-term means found above and the rapid variations are extracted by normalizing the signal levels to their short-term mean. Four hundred signal samples are considered at a time and normalized to a mean extending over 2800 samples centred on the 400.

The cumulative distribution of the signal level relative to the short-term mean is plotted on a probability axis scaled by the function:

$$y = \text{constant} + \frac{1}{n} \log_{10}(-\log_e \text{prob})$$

(2)

Consequently functions with a cumulative distribution of the form:

$$y = \exp\left(-x^n\right) \tag{3}$$

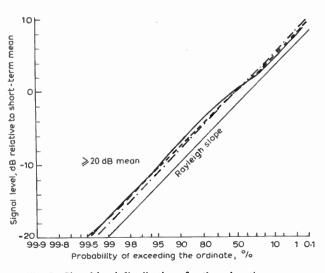

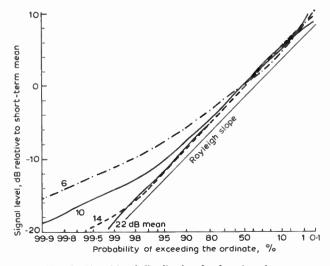

will give a straight line, of slope equal to n. The Rayleigh distribution has n = 2 and this slope is shown in Figs 5 and 6 where the results for a number of locations are given. (The log<sub>10</sub> is included because the signal is plotted in dB.)

Figure 5 shows the distribution for three locations where the mean signal level is about 20 dB. The distribu-

Fig. 6. Signal level distribution for four locations.

tions are very close to Rayleigh, and are typical of six such results. Figure 6 shows the distributions in four locations with long-term mean signal levels ranging from 6 dB to 22 dB. With a long-term mean of 6 dB the plotted distribution falls away from the 'Rayleigh' slope for relative signal levels below 0 dB, indicating an increased probability of exceeding these low signal levels. This is caused by receiver front-end noise which produces an output from the envelope detector during the deeper fades which obscures the distribution of the smaller signal levels. To prevent the receiver noise ( $\sim 0 \text{ dB}$ ) from obscuring a signal distribution down to -20 dB relative to the short-term mean, the short-term mean must be greater than 20 dB. With lower means the departure from a straight line does not indicate a non-Rayleigh distribution. The conclusion is that where the mean signal level permits a valid measurement the signal level has a Rayleigh distribution.

#### 6 Conclusions

Propagation measurements in London at 462 MHz have shown that the mean signal level as a function of range can be predicted using Okumura's method (and subtracting 5 dB). In the prediction London is considered to be an urban environment even though its building height is nearer to suburban by American and Japanese standards. Alternatively the propagation can be taken to be inverse 2.5 power law with an excess path loss of 20 dB.

London's short streets with their random orientation is offered as a reason why the lower building height in London compared with those of Tokyo has not resulted in signal levels higher than predicted. The mean signal level has been shown to be roughly log normally distributed with a standard deviation of 5 dB. The prediction method is therefore useful since the probable error is quite small.

The signal level (envelope) has been shown to have a Rayleigh distribution for a variety of locations in London.

#### 7 Acknowledgments

I should like to acknowledge the contribution made to this work by my colleagues P. J. Mabey, R. Wells, T. W. Whiter and K. J. Wheatley; and to thank Pye Telecommunications, Cambridge, for their advice about the radio equipment.

#### 8 References

- Jakes, W. C. (Ed.), 'Microwave Mobile Communications', pp. 79-131 (Wiley, New York 1974).

- Okumura, Y., et al., 'Field strength and its variability in v.h.f. and u.h.f. land mobile service', *Rev. Elect. Commun. Lab.*, 16, p. 825, September and October 1968.

- Turin, G. L., et al., 'A statistical model of urban multipath propagation', IEEE Trans. on Vehicular Technology, VT-21, No. 1, pp. 1-9, February 1972.

- 4. W. C. Y. Lee, 'Statistical analysis of the level crossing and duration of fades of the signal from an energy density mobile radio antenna', *Bell Syst. Tech. J.*, 46, pp. 417–48, February 1967.

Manuscript first received by the Institution on 26th September 1975 and in final form on 4th December 1975. (Short Contribution No. 178/Com. 129.)

© The Institution of Electronic and Radio Engineers, 1976

### The Author

**Richard French** (Member 1964, Graduate 1959) studied telecommunications at Norwood Technical College and after two years national service in the RAF joined Muirhead and Co. to work on facsimile equipment. In 1960 he moved to the Mullard Research Laboratories, Redhill, where he has been concerned with a variety of projects in the Communications Group. In 1973 he was awarded a Ph.D. by the

CNAA for work on speech scrambling and synchronization techniques undertaken at MRL and Brighton Polytechnic. His current work is on data transmission in mobile radio networks.

# A circuit for high-speed carry propagation in l.s.i.-f.e.t. technology

T. LAMDAN, M.Sc., Ph.D., C.Eng., M.I.E.R.E.\*

and

M. AHARON, M.Sc.†

#### SUMMARY

A circuit configuration for high-speed carry propagation employing serial floating field effect transistors in parallel digital adders is presented. Circuit parameters affecting the performance of the suggested configuration are evaluated. Results of comparisons with alternative m.s.i. and l.s.i. adder circuits are given and show that the present suggestion is superior to the alternatives.

\*The Weizmann Institute of Science, Department of Applied Mathematics, Rehovot, Israel.

†Glenayre Electronics Ltd., North Vancouver, B.C., Canada.

The Radio and Electronic Engineer, Vol. 46, No. 7, pp. 337-341, July 1976 C

#### 1 Introduction

The speed of parallel binary adders is affected, mainly, by the speed of carry propagation. Many methods of speeding-up carry propagation are known.<sup>1</sup> The most popular methods rely on some variation of the carry-lookahead technique which is, in fact, a procedure for resolving the problems of fan-in and fan-out limitations of the logic circuit. Another method, carry completion detection, relies on the fact that the average length of propagation is obviously shorter than the full length of the adder -which is the maximum length of propagation. different solution to the same problem employs a special high-speed switch in the carry chain.<sup>2,3</sup> This circuit which is, conceptually, very simple has not, apparently, become popular with logic circuit designers and manufacturers, probably because of circuit complications involved in the realization of the serial switch.

The dramatic increase in recent years of the usage of f.e.t. technology in digital systems justifies an updated evaluation of the carry problem under the constraints of that technology. This is true in particular when considering m.s.i. and l.s.i. circuits.

Two features of the field effect transistor prove to be important with regard to its implementation in the serial switch configuration:

(1) its general characteristics as a switch,

(2) the action of the f.e.t. as a floating device.

Generally, the f.e.t. proved to be very suitable for use in the configuration of serial switch. Nevertheless, because f.e.t.s are not in fact, perfect switches, the actual performance achieved with the carry circuit is device dependent and its behaviour and characteristics are investigated in the sequel.

#### 2 Carry Propagation Employing Serial Switches

A possible elementary representation of sum  $(S_i)$  and carry  $(C_i)$  equations for stage *i* of an adder with inputs  $X_i$  and  $Y_i$  follows in equations (1) and (2):

$$S_i = (X_i Y_i U \overline{X}_i \overline{Y}_i) C_{i-1} U (X_i \overline{Y}_i U \overline{X}_i Y_i) \overline{C}_{i-1} \quad (1)$$

$$C_{i} = X_{i} Y_{i} U X_{i} C_{i-1} U Y_{i} C_{i-1}$$

(2)

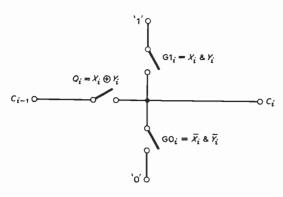

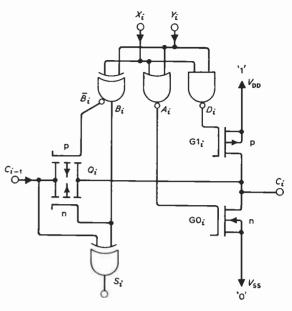

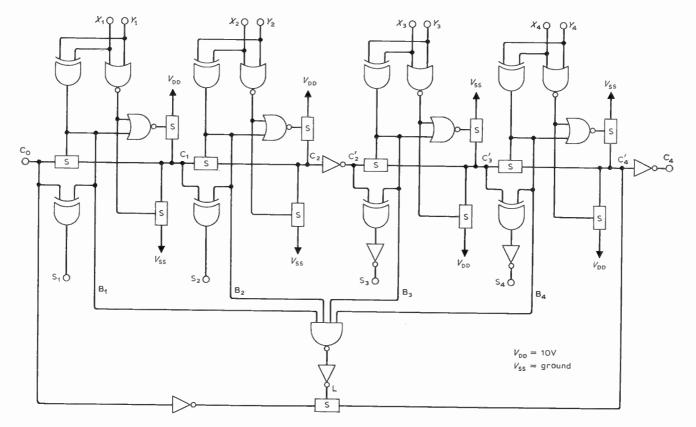

The dependence of the carry of stage i on stage i-1 and consequently on all previous stages is apparent. Another carry logic configuration which employs a serial switch is presented in Fig. 1. The circuit employs three switches  $G1_i$ ,  $G0_i$  and  $Q_i$ . The action of this circuit is as follows: switch  $GO_i$  is closed when  $\overline{X}_i$  and  $\overline{Y}_i = 1$  and forces  $C_i = 0$ , switch G1<sub>i</sub> is closed when  $X_i$  and  $Y_i = 1$  and forces  $C_i = 1$  and finally switch Q<sub>i</sub> is closed when  $X_i \neq Y_i$  and causes  $C_i = C_{i-1}$ . The three cases are the 'zero carry' generation, 'one carry' generation and 'carry-propagate' conditions respectively. For any input combination one and only one of the three switches is closed. For an *n* bit parallel adder (i = 1, n), all switches in the *n* stages are controlled concurrently when  $X_i$  and  $Y_i$  (i = 1, n) are applied. The speed of addition is dependent on the speed of propagation of the carry signal which, in worst case must be propagated via the series of all switches  $Q_i$  (in fact for addition i = 2, n only

Fig. 1. Carry circuit.

but in other operations the first stage may be involved also). That is, the total delay of an adder based on this configuration consists of three parts: (1) delay of concurrent actuation of switches  $GO_i$ ,  $GI_i$  and  $Q_i$  in all stages. (2) Propagation of the carry via all stages in which carry propagation conditions exist, and (3) sum generation which, for any stage of the adder, can be generated only after its input carry is known.

In many cases a major effort is devoted to minimization of carry propagation delay. Adder circuits based on this configuration employing bi-polar germanium transistors have been reported by the previously mentioned sources. But, as stated in the Introduction, the two versions of the circuit seemed to have encountered severe problems which have actually prevented their wide acceptance in the industry. To the best of the authors' knowledge no equivalent circuit using silicon transistors has been adapted probably because of similar reasons. In particular, the specifications of switch  $Q_i$  necessitate the employment of a 'symmetrical' floating switch which can propagate signals of both polarities. This symmetry is difficult to achieve in planar bi-polar silicon integrated circuits technology.

#### 3 An Adder Stage Employing Field Effect Transistors

A circuit implementing one stage of the adder using m.o.s. circuits is shown in Fig. 2. The logic gates  $A_i$ ,  $B_i$ ,  $D_i$  and  $S_i$  perform the input and sum logic,  $A_i$  being a NOR and  $D_i$  a NAND gate while  $B_i$  and  $S_i$  are exclusive-OR gates.  $B_i$  provides the invert of its output also.

Assuming positive logic (high for '1') a p-type transistor acts as a Gl<sub>i</sub> switch an n-type transistor acts as GO<sub>i</sub> switch. A parallel combination of a p and n transistor provide for the Q<sub>i</sub> switch. In similar manner to the operations of the switches explained with regard to Fig. 1, here also when both X<sub>i</sub> and Y<sub>i</sub> are '1', D<sub>i</sub> is low and causes Gl<sub>i</sub> to conduct forcing '1' to C<sub>i</sub>; under these conditions transistors GO<sub>i</sub> and Q<sub>i</sub> are non-conducting. Similarly when both X<sub>i</sub> and Y<sub>i</sub> are '0' (low) A<sub>i</sub> is high causing GO<sub>i</sub> to conduct forcing '0' to C<sub>i</sub>. Finally, when either X<sub>i</sub> or Y<sub>i</sub> is '1' but not both of them, one of the transistors in switch Q<sub>i</sub> conducts causing C<sub>i</sub> = C<sub>i-1</sub>. In this case, transistors G1<sub>i</sub> and GO<sub>i</sub> are non-conducting. Gate S<sub>i</sub> performs the sum logic in a simple manner.

The explanation so far deals with the static behaviour of the circuit. Dynamically other problems arise. First,

Fig. 2. Full adder stage.

under transient conditions more than one switch may be conducting. The effect of this is to reduce the speed of the initial settling time but has no accumulative effect on the operation of the parallel adder. The extra current and power dissipated as a result of this transient effect is limited by the internal impedance of the transistors and practically may be neglected.

Also, the transistors do not behave as ideal switches, in particular input and output capacitances of the various components and the resistance of conducting transistors have appreciable effect on the speed of operation of this configuration. This problem is discussed in detail in the following Section.

#### 4 An *n*-stage Parallel Adder

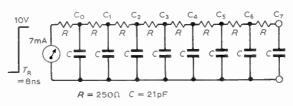

Using the basic circuit of Fig. 2 a parallel adder is implemented by connecting such stages in series. An n-bit parallel adder uses n stages in which the 'carry out' line of one stage is connected as 'carry in' of the next stage. The 'carry in' of the first stage is controlled in the proper way. In order to be able to evaluate the dynamic performance of the parallel adder, in particular its behaviour in the carry propagate mode, its equivalent circuit may be studied. In the state of carry propagation, a single-stage carry circuit can be replaced by an equivalent RC network and the whole adder carry circuit may be represented by an RC ladder network being driven by a voltage step. R represents the resistance of the conducting serial transistor and C the total capacitance loading the carry out node. In the present work the lumped parameter equivalent circuit proved to give good results when compared to experimental measurements as is shown in the following Sections.

Note that in practice the driver is not an ideal voltage source and the real circuit should be approximated by shaping the source accordingly. The delay  $T_D$ , and the rise-time,  $T_R$  of the ladder network have been calculated for a practical circuit using a circuit simulation program (Appendix I) and the strong dependence of  $T_{R}$  and  $T_{D}$  on the number of stages is obvious. Comparable results have been obtained when calculating the 'Elmore'4 delay  $T_{(e)D}$  and rise-time  $T_{(e)R}$  for an RC ladder network fed by a voltage source. It can be shown that at any point M of an N stage RC ladder:<sup>8</sup>

$$T_{(e)D} = \frac{RC}{2} \left[ N^2 - (N - M)^2 \right]$$

(3)

which for the case M = N reduces to:

$$T_{(c)D} = \frac{RC}{2} N^2 \tag{4}$$

Also, from calculations for specific values of RC, it was found that<sup>6</sup>

$$T_{(e)R} \gtrsim RCN^2$$

. (5)

For practical circuits  $T_{R}$  may become prohibitive and measures are needed for its reduction. This can be achieved, at the expense of increasing the delay  $T_{\rm D}$ , by just introducing buffer stages at selected points along the carry path.

#### An Adder Circuit for Experimental 5 **Evaluation**

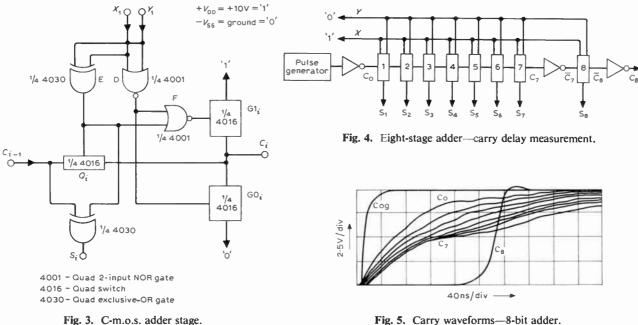

In order to evaluate the proposed configuration experimentally an adder was built using available c.m.o.s. i.c.s, components from the RCA CD4000A series<sup>5</sup> being chosen. The circuit for a one-stage full adder (Fig. 3), consists of two NOR gates (type 4001) and two 'exclusive-OR' gates (type 4030) for performing input and sum logic and three bilateral switches (type 4016) for the carry. All interconnections between packages were done by wiring. Measurements reported here are for 10 V supply at room temperature (25°C).

The settling time for the input logic was measured to be equal to 44 ns. Similarly, the delay of the sum logic measured with respect to the carry in signal was 28 ns.

Note that these measured delays are about 25% faster than those expected from the typical delay times quoted in data sheets.

In order to measure the carry propagation delay an 8-stage adder, shown in Fig. 4, was built on a  $10 \times 15$  cm board. Inverters  $C_0$ ,  $C_7$  and  $C_8$  are added for the purpose of reshaping of signals.

Carry propagate conditions are established at inputs X and Y and a pulse generator feeds carry signal to input of C<sub>0</sub>. Shapes of wave forms at various points along the carry path are reproduced in Fig. 5.  $C_{0g}$  and  $C_0$  are, respectively, the unloaded and loaded output signals of inverter Co.

The measured results for this circuit are summarized in Table 1. The current limiting effect due to the input stage,  $C_0$ , driving the ladder network is manifested by the initial linear rise time of the waveforms. The knee in the waveforms at about the threshold voltage due to the higher resistance of the transistor is evident.

Table 1. Measured results for the 8-stage adder.

| Stage No.      | $T_{\rm D}$ (ns) | $T_{\rm R}$ (ns) |  |

|----------------|------------------|------------------|--|

| C <sub>0</sub> | 55               | 165              |  |

| C1             | 68               | 250              |  |

| C <sub>2</sub> | 85               | 300              |  |

| C <sub>3</sub> | 105              | 330              |  |

| C <sub>4</sub> | 115              | 360              |  |

| C <sub>5</sub> | 130              | 365              |  |

| $C_6$          | 140              | 370              |  |

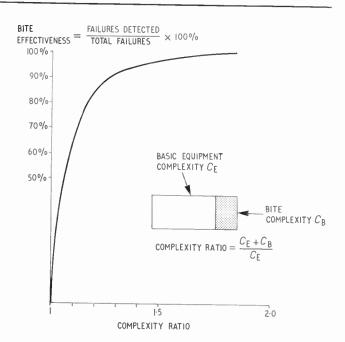

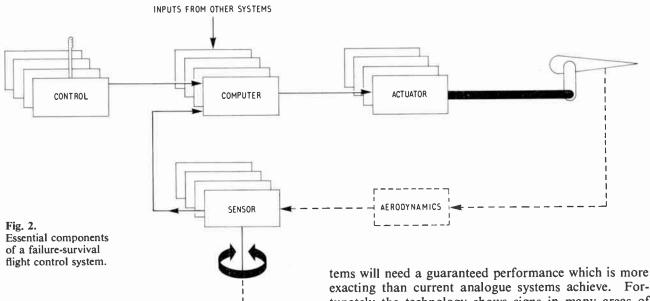

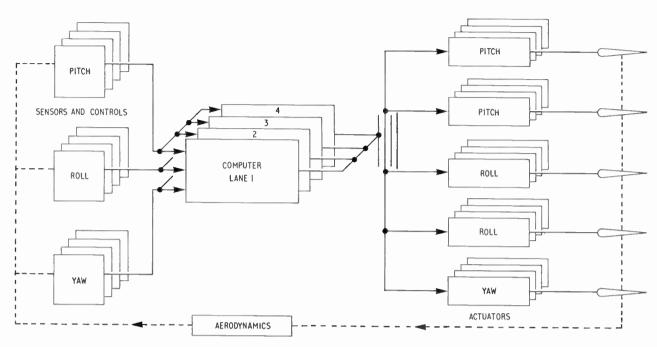

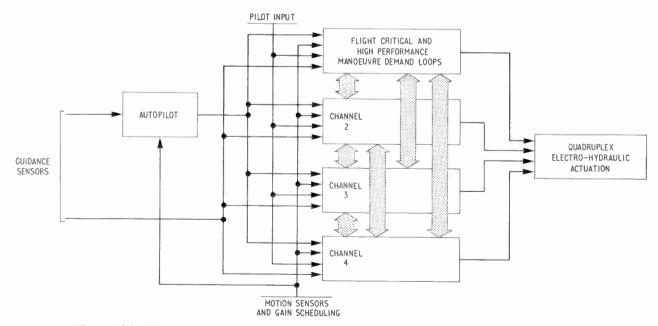

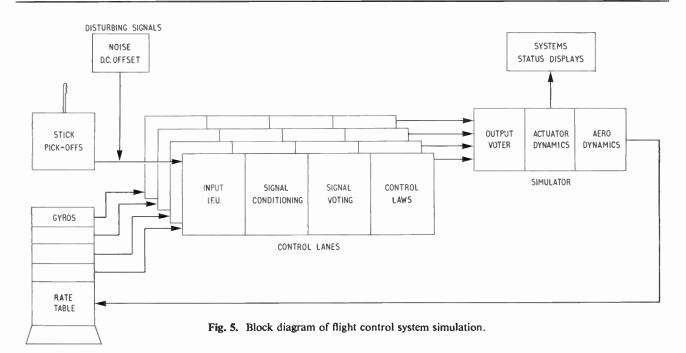

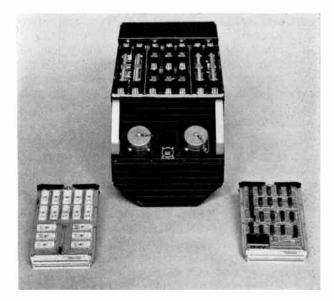

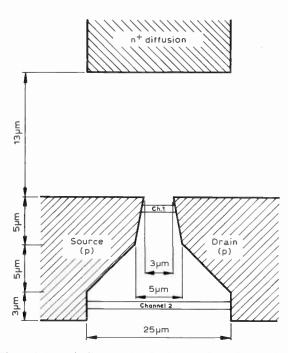

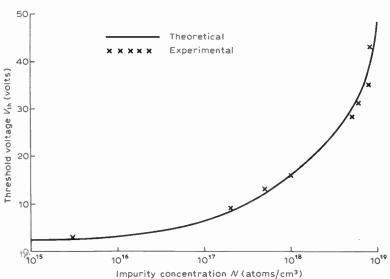

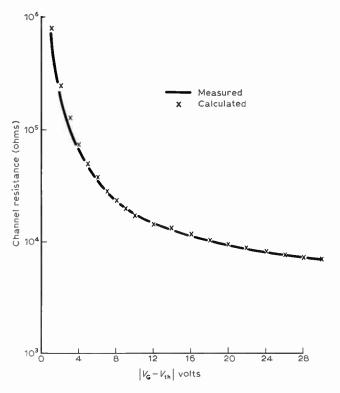

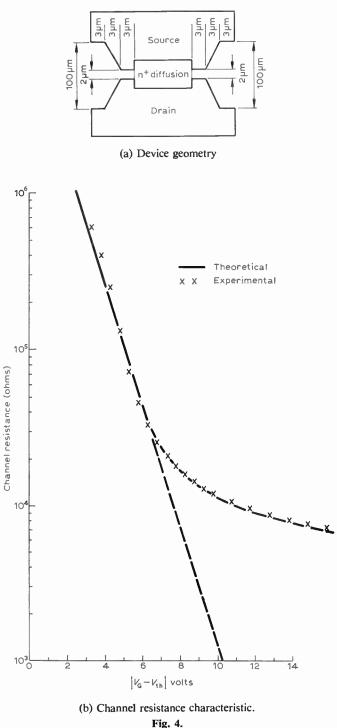

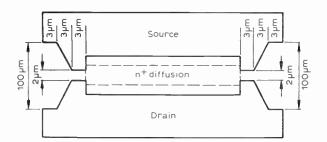

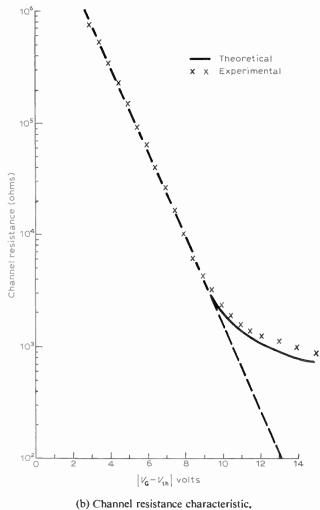

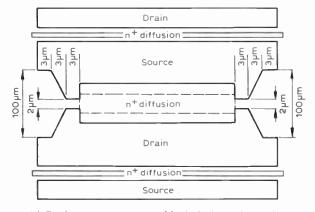

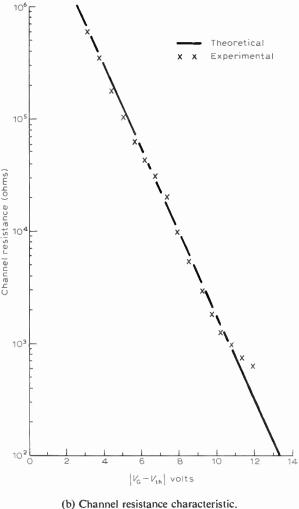

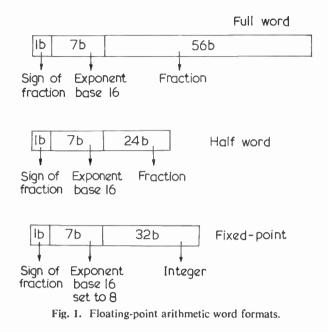

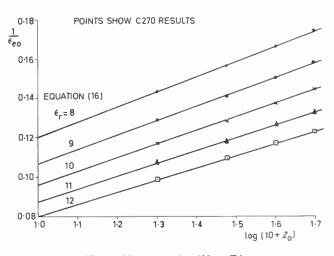

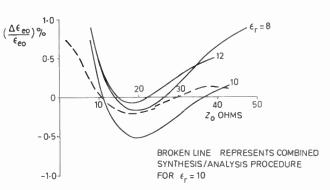

| $C_7$          | 155              | 375              |  |