Volume 47 No. 7

Founded 1925 Incorporated by Royal Charter 1961

To promote the advancement of radio, electronics and kindred subjects by the exchange of information in these branches of engineering

# The Radio and Electronic Engineer

The Journal of the Institution of Electronic and Radio Engineers

### **Encouragement for the Components Industry**

$E^{ARLY}$  this year a new kind of intervention into the British Electronics industry by the Secretary of State for Industry took place, when Mr Eric Varley announced in January that he was applying a scheme of selective assistance for the electronic components sector as envisaged under Section 8 of the Industry Act 1972. In the first instance a sum of £20,000,000 was being provided. Looked at in relation to the total turnover of the components sector, estimated to be nearly £1,000M for 1976, this can be considered a mere drop in the ocean, but apart from the stated intention that further assistance will be given if the response warrants it, the aid scheme has been welcomed by the industry who see it as providing support and encouragement for a limited number of relatively small projects which it might not otherwise be able to carry out.

Under the scheme UK-based firms will be encouraged to undertake projects intended to improve their efficiency and competitiveness. New products and production technologies can be promoted, companies can be restructured to rationalize production and independent studies by consultants can be commissioned.

In more detail, assistance may be given for design, development and production launching of new products and production technologies, including the research, design, development and production of new products and key electronic materials: the improvement of production technologies for productivity, quality and standardization through BS 9000: and the strengthening of engineering support in production launching. Assistance will be available in the form of a grant usually not exceeding 25% of the total eligible cost of the project but could be a 50% shared-cost contract recoverable by a levy on future sales. Costs of a project must normally not be less than £50,000 and it must be completed by 31st December 1980 as far as the Department's contribution is concerned.

Assistance will also be available for wide ranging projects involving restructuring of a company or a group of companies and associated resources, including the cost of independent consultants to advise on improvements to efficiency. Grants towards investment in capital equipment, plant, machinery and buildings with both production and restructuring projects, can also be made.

Clearly the Department of Industry requires to be satisfied that projects are viable and industrially desirable and that restructuring proposals are beneficial to the companies involved and desirable in terms of the industry as a whole. It may therefore not be just a coincidence that very soon after the announcement of the aid scheme, a streamlining of the component industry's trade associations was announced. Historically these have tended to be somewhat diverse, active components at one time being covered by two associations (BVA and VASCA), respectively linked with consumer and professional devices, while there was an association (RECMF) looking after the interests of the passive device manufacturers. Several years ago the first two merged to form the Electronic Components Board and now there is to be one organization, the Electronic Components Industry Federation (ECIF). It could be said that this change reflects that integration of active and passive components themselves which is now a technical fact of life.

The new Federation has stated that it looks forward to working closely with the National Economic Development Office Sector Working Party on Components who originally advised the Department of Industry on the desirability of the £20,000,000 aid which is now to be given. These close relations between industry, government-sponsored organization and a government department, though on the face rather involved, should provide a means of enabling the industry to meet new challenges—and these today are legion!

#### The Radio and Electronic Engineer, Vol. 47, No. 7, July 1977

В

July 1977

#### General Interest Paper

# The application of microprocessors to main frame design

Professor M. V. WILKES, M.A., Ph.D., F.R.S., C.Eng., F.I.E.E.

Keynote Address at the Conference on Computer Systems and Technology held at the University of Sussex from 29th to 31st March 1977.

Microelectronics has given us low-cost microprocessors and will soon give us low-cost high-speed memory. Some of the ways in which main frame computer architecture may develop are discussed against this background.

#### Introduction

At the present time we have both large computer centres consisting of main frames with a variety of peripheral and telecommunication equipment attached and also innumerable mini-computers scattered in laboratories and offices. Many of these are free-standing, but some have a data link to other computers. A feature of the last few years has been the growth of computer networks to which both large computer centres and small mini-computers can be, and often are, attached.

The essential feature of a main frame as found in a large present-day computer centre is that it provides processing power in a highly centralized way. It consists of several banks of core or semiconductor memory, amounting perhaps to as much as four megabytes serving one or two—rarely more very fast processors. Everything is done to maximize the throughput of the processors, for example, by providing them with pipe-lines and with slave or cache memories. Directly connected to the main frame are banks of disk files, magnetic tape decks, card readers and punches, plotters, and similar devices. There are also remote job entry stations that are similarly directly connected. Indirectly connected, usually via a small computer used for switching, are teletypes, v.d.u.s, and small satellite computers.

The work-load of a typical large computer installation having a fast powerful main frame commonly consists partly of jobs big enough to tax the resources of the entire system and partly of a miscellaneous collection of small jobs. The operating system required to handle this work and to share the resources of the system between the various jobs in hand is very complex. In a purely batch operation this complexity can be handled and the object of the operating system, which is to achieve a high throughput through the sharing of resources between the various jobs, can be achieved. If, however, the same system is required to provide interactive access with a rapid response to a hundred or more users, then the problem of designing, implementing and tuning the operating system increases very

**Professor M. V. Wilkes** is Professor of Computer Technology and Head of the Computer Laboratory in the University of Cambridge. He studied pure and applied mathematics at Cambridge University and did his doctoral thesis work at the Cavendish Laboratory in radio physics. During the war he was engaged in radar and operational research and, when the war was over, returned to Cambridge to take charge of the Mathematical Laboratory (now the Computer Laboratory). He was responsible for the construction of EDSAC 1, which was working early in May 1949.

With two colleagues, Professor Wilkes published, in 1951, the first book on computer programming and he is author of several other books. He has received numerous honours from universities and societies in Great Britain and abroad, and the British Computer Society, of which he was the first President (1957–1960), has made him a Distinguished Fellow.

greatly in complexity and is on the limit of what can be successfully achieved by a software team. Moreover the proportion of system resources consumed by the operating system itself tends to increase. In order to secure satisfactory performance, especially as regards interactive response time, it is necessary to provide a great deal of high-speed memory. Some of this is occupied by modules of the operating system and some is shared between the various jobs. None of the latter are permanently resident, but are brought in from a disk or drum when they become eligible for a slice of processor time. This is accomplished in one of several ways, namely, by rolling in and rolling out the entire program, by bringing modules in under the control of a space allocation routine in the operating system, or by the use of a hardware-supported paging system. There must be enough high-speed memory to support a sufficiently high level of multi-programming to enable use to be made of processor time that would otherwise be wasted in waiting for disk or drum transfers to take place.

Microelectronics has already given us low-cost microprocessors, although those at present available are slow in operation compared with the processors in main frames. We have yet to experience the availability of very low-cost highspeed memory. At present the relatively high cost of memory is limiting what can be done with microprocessors. Their main application—and it is one for which they are ideally suited—is in special-purpose applications, such as the control of peripheral equipment, the instrumentation of experiments, the control of industrial and other systems, and the like. In such applications each microprocessor can be provided with exactly the right amount of memory for the function that it has to perform.

### An Operating System Implemented in Microprocessors

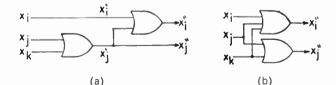

A computer operating system may be regarded as-and indeed is-a control system. There would thus appear to be scope for implementing an operating system by means of a number of interconnected microprocessors dedicated to the purpose, each microprocessor handling some specific task, for example, scheduling, memory allocation, etc. The operating system so implemented would control a main frame of the conventional kind. As far as possible its design would follow conventional practice, except that the various processes would run in microcomputers provided for the purpose instead of running in the main frame under multi-programming. The messages (sometimes known as events) that are sent from one process to another in a normal operating system would be sent from one computer to another along a low-speed channel provided for the purpose. A separate high-speed channel would be provided for the transfer of data in bulk and this would be connected to the main frame via one of the regular channels. Certain high level scheduling and accounting operations, while being properly considered as the concern of the operating

The Radio and Electronic Engineer, Vol. 47, No. 7, pp. 302–304, July 1977

system, are conventionally performed by programs that run under the operating system as though they were programs belonging to users. These would continue to be run in the main processor. The filing system would be under the control of a microprocessor, but some help from object programs running in the main frame might be provided.

Since the various functions of the operating system would be performed in microcomputers and only object programs run in the main processor, the amount of process switching in the main processor would be much less than in a normal system. This would simplify the problem of memory management and reduce the amount of memory needed by the main frame. One would like to think that this, together with an increased throughput of object programs, would more than compensate for the cost of the microprocessors and their associated communication system.

The philosophy behind the proposal that has just been made is that functions that are well understood, and for which the necessary resources can be closely determined, are better done in inexpensive and relatively slow microcomputers, with direct access to the memory that they need, rather than in a very fast central processor. There is, however, the further motivation that, by divorcing the operating system from the central processor, one could hope to reduce significantly the excessive complexity of modern operating system that has already been remarked on. At the present time the designer of an operating system can have no confidence that it will not be misused in practice, for example, by attempting to run it with too small an allocation of memory. A self-contained system, with its resources permanently allocated to it, is likely to have advantages in this respect.

#### The Main Frame of the Future

One sometimes hears it suggested that the time is approaching when the costly main frame at present in use could be economically replaced by a group of microcomputers capable together of executing the same number of operations per second. For example, one could replace a pipe-lined processor with an average instruction time of 100 nanoseconds by a group of 25 microprocessors with an instruction time of 2.5 microseconds. If one divided up the memory with which the fast processor might be equipped-say 1 million wordsamong the microprocessors they would each get about 40 k words each. It could be claimed that the resulting system of separate computers would have the same power as far as small jobs are concerned as the original one. However, input and output must also be considered and it would be expensive to provide each of the 25 computers with its own input device and printer. Moreover no one running a computing service would want to have to look after 25 independent machines. He would prefer to have a common input route and for the results to come out on a group of printers. Moreover, he would want to have a single filing system in which library programs and users' programs and data could be kept. Viewed in this way it will be seen that what we are really discussing is whether the conventional main frame should be replaced by a main frame with 25 separate computing channels and a suitable buffering and control system for sending work through them and collecting the results. In other words, we are not so much discussing the replacement of the main frame in a computer centre by a battery of independent microcomputers, but rather we are discussing an alternative design for the main frame. The numbers in the above example reflect the state of affairs in late 1976 and will very rapidly become out-of-date. Microprocessors will improve in speed and semiconductor memory will become less costly; fewer channels will therefore be needed and the total amount of memory installed will much exceed what we are used to today.

Another argument sometimes advanced is that computing centres will become a thing of the past and that anyone who needs computing facilities will be able to have a personal computer of his own. Few people, however, would find this entirely adequate to their needs. They would require facilities for obtaining hard-copy on an adequate scale and would also require access to a central filing system, so that they could obtain the use of standard material and could share their programs and data with other users. This is sharing as a user requirement and is to be clearly distinguished from sharing imposed by a need to use equipment economically.

If a personal computer is to be connected to a central filing system there must be a telephone line between the user's office and the central facility; it becomes a good question to ask: at which end of the line should the personal computer be put? Personal possessiveness and distrust of central services demand that it should be at the user end, but the technical arguments tend to go in the other direction. The personal computer needs to communicate both with its owner via his v.d.u. and with the central filing system. The former it can perfectly well achieve through a telephone line of limited bandwidth; the latter can well use a greater bandwidth both in order to speed up transmission and to simplify buffering. Maintenance and testing would be much simplified if the computers were centrally located and those responsible for the maintenance would have the satisfaction of knowing that they were housed in suitable conditions. Finally, there would be a pool of central computers that could be allocated to casual users who dialled in. We are here back to sharing and even the most staunch advocates of low-cost stand-alone computers must recognize that there will always be users whose work-load would not justify the owning of their own computer.

There is, however, one economic argument in favour of the user having his personal computer in his own office and that is connected with the cost of telephone lines. Some users may need only infrequent access to the central filing system; given a computer of their own they could dial in briefly when they required such a connection and would not need to bear the cost of a connection maintained the whole time that they were working. This is perhaps the strongest argument for the installation of personal computers and the outcome depends on the attitude of the telephone administrations in the various countries. If they are able and willing to give us low-cost computer communications, we in the computing community will be glad to make use of them to their profit as well as our own. Otherwise we will seek to take advantage of the power that developments in microelectronics give us to make ourselves as independent as possible of communications.

The above argument has led to another view of the design of the main frame of the future, namely, that it should consist of a number—perhaps a large number—of computers each with its own memory. When he logged in, a user would become linked to one of these computers and would have exclusive use of it for the remainder of the session. When he was not computing it would remain idle.

All the computers available to users would not necessarily have the same amount of high-speed memory and a user would choose one suited to the needs of his work. It is tempting to propose that there should also be some high-speed memory available for sharing. It would then be the responsibility of the user—I am thinking of a sophisticated user dealing with a large problem—to distribute his programs and data between the dedicated and shared memory to the best advantage. This is the kind of challenge that experienced computer users take up readily and there is something to be said for letting them come to grips with it, instead of attempting to provide a system solution which can in the nature of things be only partially successful. I have always felt that existing multi-user console

١

systems do not make as much use as they might of the combined intelligence of the users who connect themselves to the system, but instead, put their entire trust in unintelligent software. However, any proposal for sharing high-speed memory presents formidable switching problems. If a satisfactory way of enabling a large number of processors to share a large bank of high-speed memory could be devised, then we would not be talking about dedicated memory at all.

#### Conclusion

This paper has explored some of the ways in which microprocessors might find application in the design of computer main frames. So far the application of microprocessors has been limited by the fact that the necessary memory to associate with them is still expensive, but this situation will change.

Many of the difficulties experienced with present-day computer systems using main frames with one or two multiprogrammed processors arise from the acute disparity of speed between their high-speed memories and the fixed-head disks or drums used for paging or swapping. In due course it will become possible to replace the disks or drums by solid-state devices, such as bubble memories or charge-coupled memories, operating at greater speed. In the long term, the availability of really low-cost semiconductor memory may enable this level of memory hierarchy to be done away with altogether. In view of the improvement in performance that these developments will give, it would be a mistake to assume that main frames of the type that we are used to will not survive in essentially their present form.

Manuscript received by the Institution on 31st January 1977 (Paper No. 1773/Comp. 180).

© The Institution of Electronic and Radio Engineers, 1977

The photograph shows part of the new test facility at the Ferranti Special Components Department's new inspection area at Moston for precision coils and c.r.t. package systems. These include fibre optic c.r.t. packages for a medical recorder, large precision packages for photo-type-setting, flying-spot scanner units for telecine applications and a wide range of c.r.t. coil assemblies.

# A digital highfrequency multipath propagation simulator

W. MATLEY, B.Sc., C.Eng., M.I.E.E.\*

and

R. E. H. BYWATER, B.Sc., Ph.D., M.B.C.S., C.Eng., M.I.E.E.\*

#### SUMMARY

A digital h.f. multipath propagation simulator is described which can be applied to communications receiver and modulation techniques evaluation and operator training. It can also be applied to a variety of applications in the high-frequency field where programmable and repeatable ionospheric conditions require simulation. Simultaneous communications paths are simulated, four of which exhibit independent delays, Doppler shifts, Rayleigh fade and phase variations and attenuation consistent with ionospheric reflection (skywave) paths.

\* Department of Electronic and Electrical Engineering, University of Surrey, Guildford, Surrey GU2 5XH,

The Radio and Electronic Engineer, Vol. 47, No. 7, pp. 305–314, July 1977

The requirement for the High-Frequency Multipath Propagation Simulator described in this paper originated from investigations into modulation techniques suitable for use in the 1 to 30 MHz communications band. The resulting instrument is a novel exploitation of current semiconductor technology and embraces some new system concepts in propagation simulator design.

Severe ergonomic problems were posed by the requirement for both manual and remote computer control of the large number of settable coefficients. This led to the design of a special interface panel.

Propagation simulation is carried out at the intermediate frequency of 100 kHz to facilitate integration of the medium propagation characteristics into the total system studies.

The design study and development of the simulator were carried out by a university team under the auspices of the Industrial Electronics Group of the University of Surrey.

#### 2 Simulator Parameters

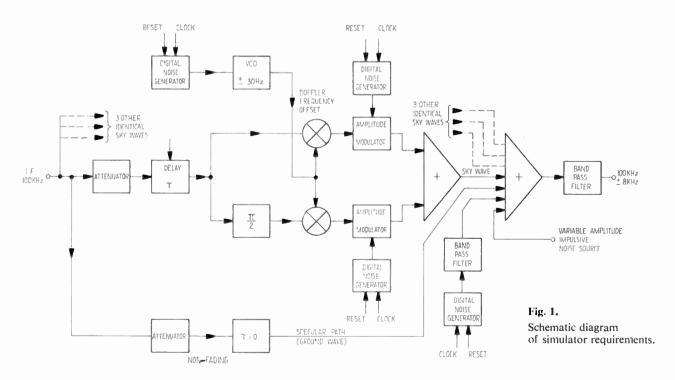

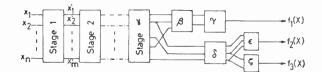

The operational requirement was for an equipment to simulate the multipath propagation medium which is experienced in h.f. communications. Specifically, five independent and simultaneous communication paths were to be simulated, relating to a communications bandwidth of  $\pm 10$  kHz. The paths comprise: one specular (or ground wave) subject only to attenuation, and four ionospheric reflection (or sky wave) paths each subject to independent delays, Doppler shifts, Rayleigh fade and phase variations and attenuation. The equipment works at the receiver i.f. of 100 kHz (in real time) or at a lower frequency for expanded time scale operation. Control of the simulator parameters is carried out locally with an electronically interlocked panel or remotely from a digital computer. The specification is set out in Table 1, and the requirements are shown in schematic analogue form in Fig. 1.

#### 3 Design Approach

At the core of the investigation was the problem of the implementation of a long delay line with suitable attenuation and dispersal characteristics and able to be tapped at several points simultaneously over 100 steps from 0 to > 10 ms. A previous project, reported in this Journal,<sup>1</sup> suggested that a digital delay line provided a reasonably economical and compact solution and one which could be implemented using r.a.m.s with a sliding address algorithm.

Commitment to a digital delay line leads naturally to digital methods for the implementation of the various other machine parameters, i.e. Doppler shifts and Rayleigh phase control. Delay for all of these can be achieved through r.a.m. address modification. Consideration of all the phenomena to be realized through delay line manipulation led to a specification for the r.a.m. in terms of bits per sample, read/write rates and number of locations.

Having decided on so much of the simulator being

| Number of simulated paths: | 1 specular (SPEC)<br>4 ionospheric                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:                 | Real time (100 kHz) and non-real time                                                                                                                                                                                                                                                                                                                                            |

| Non-real time operation:   | 10 kHz, 1 kHz (20% bandwidth)                                                                                                                                                                                                                                                                                                                                                    |

| Path parameters:           | Delay—0 to > 10 ms in increments<br>of 100 $\mu$ s<br>Doppler—0 to $\pm$ 30 Hz in increments<br>of 1 Hz<br>Fade rate—0.1 to 25 fades per second<br>in a binary geometric progression.<br>Fading can be omitted from any<br>channel, if desired<br>Attenuation—0 to 40 dB in<br>increments of 1 dB. Infinite<br>attenuation can be applied to any<br>channel that is not required |

| Calibration accuracy:      | Better than ±1%                                                                                                                                                                                                                                                                                                                                                                  |

| Noise sources:             | Gaussian white noise (G.w.n.) level<br>variable from 0 to $-40 \text{ dB}$ (or zero<br>level)<br>Impulsive noise (IMP) level as for<br>G.w.n. Mean interpulse-arrival-time<br>(MIT) variable from 0.1 to 16 seconds<br>in a binary geometric progression                                                                                                                         |

| Parameter control:         | Either by front panel controls or<br>digital control from a Hewlett-<br>Packard 2100 processor; control<br>source selectable                                                                                                                                                                                                                                                     |

| Environment:               | Laboratory                                                                                                                                                                                                                                                                                                                                                                       |

Table 1. Specification of the h.f. simulator

#### Notes:

(i) All parameters which are independent random variables, e.g. fading, are derived from pseudo-random sequence generators whose initial conditions can be defined to ensure repeatability of the simulated propagation conditions.

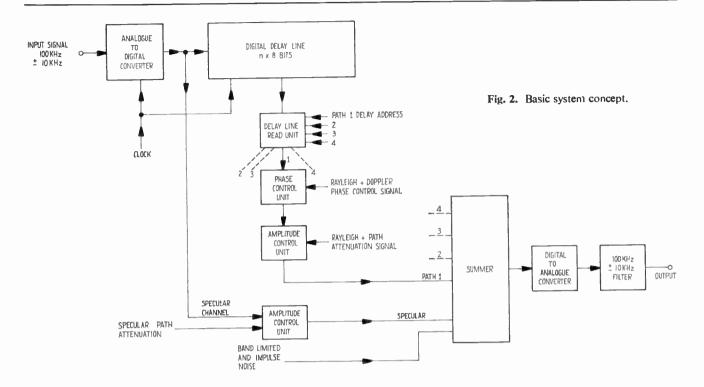

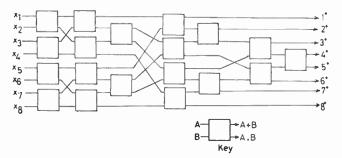

(ii) Since the specular (or ground wave) path must always arrive first at any receiving location, it can be subjected to zero delay in the simulation, so that all sky wave delays are relative to the ground wave datum. implemented digitally, consideration was naturally given to digitizing the rest of the processor, i.e. the Rayleigh fade mechanism, attenuation control, noise generation signals mixing and parameter setting. Parameter setting is inherently digital if computer originating data are used and noise generation is easily implemented digitally using m-sequence generators. Therefore, it was decided to execute all processing digitally. Figure 2 shows, in outline, the translation of the analogue model of Fig. 1 into digital form.

Input signals, which are at an i.f. of  $100 \pm 10$  kHz, are passed through a narrow window sample-hold amplifier and converted to digital samples in an analogue to digital convertor. The processed digital output, from the channels summer, is a series of digital samples which are converted to a train of analogue levels by a fast slew rate digital to analogue convertor (d.a.c.). The output envelope of the d.a.c. is at a sub-carrier frequency defined by the original sampling frequency. This sample train can be converted to a 100 kHz i.f. signal either by straight filtering as shown in Fig. 2 or by a low-pass sub-carrier followed by an up-convertor.

#### **4** Design Concepts

It was decided to sample the incoming i.f. at 80 kHz at 8 bits per sample. This was based on information bandwidth/Nyquist sampling and dynamic range criteria respectively, backed up by the precedents of Reference 1. From these two fixed parameters, the storage capacity of the r.a.m. could be calculated and the slipping address algorithm defined. At 80 (eight bit) samples per millisecond, the rate of storage of bits is 640/ms. The requirement was for a signal delay of at least 10 ms leading to

#### A DIGITAL HIGH-FREQUENCY MULTIPATH PROPAGATION SIMULATOR

6400 bits of storage. However, since the high density semiconductor r.a.m.s are available in units of 4096 bits, it was agreed that 2 of these should be used, yielding a total capacity of 8192 bits or 12.7 ms of delay.

The delay for each sky wave can then be determined by selecting the appropriate word address in the delay line. In principle, there is no limit (apart from resolution) to the number of delayed channels which may be generated; this is not so in practice, since the r.a.m. read/write rate imposes an upper limit of about 20 to 30 channels for the method of r.a.m. organization chosen.

In addition to the control of the delay time per channel, two other channel parameters need to be controlled independently; these are phase and amplitude.

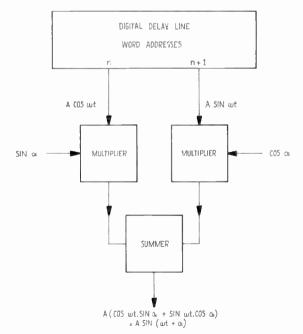

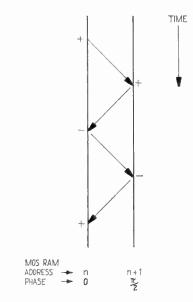

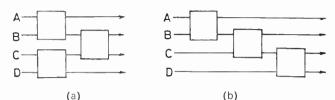

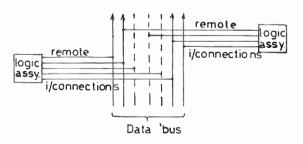

(a) Phase control is exercised by utilizing the fact that the envelope of the samples on the delay line is at a frequency of 20 kHz (a down-conversion product of the input i.f. at 100 kHz and the sampling frequency of 80 kHz) and adjacent word addresses in the delay line represent a signal phase difference of 90°. Referring to Fig. 3, if the signal envelope appearing at word address (n+1) is represented by  $A \sin(\omega t)$  then the signal envelope at word address n is  $A \cos(\omega t)$ . These two adjacent address points, when multiplied by  $\cos \alpha$  and  $\sin \alpha$  respectively, and summed together, produce an output  $A \sin(\omega t + \alpha)$ .

Phase control is thus effected by controlling  $\alpha$  which in turn makes possible a signal sample with any phase relative to the current signal sample. Rayleigh phase variations are caused by pseudo-random Markovian variations of  $\alpha$ at the appropriate rates, and Doppler shift by steady increments of  $\alpha$  at a rate determined by the selected Doppler frequency for the channel in question.

(b) Amplitude control is fulfilled by passing the digital signals through further multipliers. The multiplier coefficients are: a steady programmable number which determines the path attenuation and a pseudo-random variable which simulates the Rayleigh amplitude variation.

The two multiplications are done digitally as are the two for phase control. Therefore, for sky-wave processing alone, 16 multiplications are carried out in one  $12.5 \,\mu s$  interval (corresponding to 80 kHz). Including the processing of the ground wave and noise sources, the total is 20.

Fig. 3. Implementation of skywave phase control.

The four independently controlled sky-wave channel signals are summed together in a final summer together with (a) a ground-wave signal controlled in amplitude only, (b) a combined band-limited and impulsive noise signal and (c) an external noise source, to form a final composite output digital signal. After conversion from the resultant series of digital samples into analogue form, the composite simulated signal of  $100 \pm 10$  kHz is recovered by suitable filtering.

All the nominally random digital noise signals are derived from a master pseudo-random binary sequence (m) generator which enables any correlation between the phase and amplitude component of the Rayleigh fades to be readily implemented.

#### **5 Ergonomics**

Since the requirement was for both local (i.e. front panel) and remote computer control, and because there are a total of 8 channels each with about 5 independent variables, it was important that considerable effort be devoted to optimizing the man/machine interface.

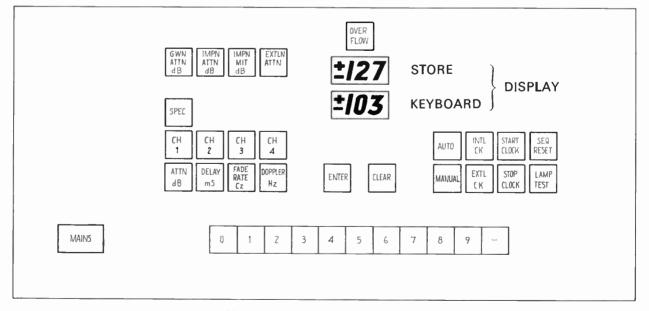

Because the proposed simulator is a digital machine, it was originally envisaged that parameter control would be exercised by a series of digital thumbwheel switches which would also act as parameter stores. However, this method of interface design was not considered to be in accord with established ergonomic principles since the operator would be confronted by around 90 decade thumbwheel switches (in addition to the system control functions, e.g. sequence start, clock rate start/stop, etc.). This leads, in turn, to difficulties such as the small non-optimum size of indication of the parameter numerals, problems of logical grouping of controls to help operator appreciation, etc. Consequently, it was proposed that a keyboard entry system be adopted with an optimized data indication and editing facility. The general format of the control panel is shown in Fig. 4, the control keys for the select parameter, select channel and status control functions are of the illuminated type; the data set-up keys control the lower parameter read-out display with its editing facility.

The design is such that when the simulator is in the 'auto (remote)' condition, all parameter control is exercised by a remote computer (which enters data directly into a parameter store (r.a.m.) and takes over the running of 'sequence reset'). While in this condition, the stored parameter data can be displayed by keying the appropriate parameters and channels, the stored data from the computer then appearing in the upper digital read-out position (labelled 'store display' in Fig. 4). The data set-up keyboard is not operative when in 'auto (remote)'.

When manual is selected, the operator's panel becomes available. As before, selection of the appropriate parameter and channel keys causes the appropriate stored data to be displayed in the upper position, the selected keys remain illuminated to identify the displayed parameter. Additionally, if the operator wishes to enter new data into the parameter store, he can key in the data which appear in the lower read-out position. In case of wrong keying, a clear key is available. After visual verification, the new data may be entered to the parameter store using the 'enter' key.

Facility is provided for resetting all the pseudo-random sequences to a fixed starting condition, altering the clock frequency for expanded time-scale operation and stopping the clock.

In order to provide for logical grouping of controls and unambiguous state indications, extensive interlocking logic is provided. Design of this system was almost an engineering project in its own right in view of the large number of keys and permissible (and impermissible) combinations. The resulting system prevents the operator from selecting impossible parameter configurations, e.g.

Fig. 4. General format of control panel.

out-of-range parameters (say > 12.7 ms delay) or impossible combinations such as 'ground wave Doppler coefficient'.

#### 6 Engineering Design

Standard 74 series (or equivalent) logic is used throughout, because of its availability, cost and compatibility with other equipment to which the simulator is interfaced. Discrete m.o.s. logic and all microprocessor technologies were considered but discarded on account of the processing speeds demanded. An appreciable proportion of the logic is needed to provide an operator interface which is foolproof. It would have been unnecessary if only computer originating data had been used as software checking could have been implemented in the HP 2100.

#### 6.1 Panel Interface

The operator selects a channel (or noise source) and a parameter prior to keying in a decimal value. A typical example might be: channel No.: 4; parameter: attenuation coefficient (dB); parameter value: 39 (dB). In order to (a) avoid impossible combinations (in the logic), (b) avoid the need for invalid combinations detectors/indicators and (c) reduce the operator loading, a system of 4 *n*-stables is employed to ensure that any key operation results in a valid combination (which is related to the last key pressed). Each *n*-stable operates so as to make each of its *n* outputs mutually exclusive.

The *n*-stable outputs are:

(i) channel 1, 2, 3 and 4 (4 states)

(ii) specular channel, null (2 states)

(iii) delay, Doppler, Rayleigh fade, Rayleigh phase, attenuation (5 states)

(iv) G.w.n., external noise, IMP-MIT, null (4 states).

In addition, certain key operations associated with a given *n*-stable forces the states of other *n*-stables or extinguishes the indicators associated with a given *n*-stable (without changing the latter's state). For example, selection to 'specular channel' extinguishes the channel number indicators without losing track of the last channel number selected. Selection of a non-specular parameter causes a return to the channel selected immediately before specular was selected. Any key selected which is associated with *n*-stable (i) puts *n*-stables (ii) and (iv) in the null state. Selection of 'specular' forces *n*-stable (iii) to the attenuation state.

The channel/parameter combination is always valid and is indicated by the appropriate keys being illuminated. Each parameter value is entered via a decimal (0-9)keyboard which assembles the value as a  $2\frac{1}{2}$ -digit signed b.c.d. quantity. This quantity is displayed on a  $2\frac{1}{2}$ -digit seven-segment gas discharge indicator. As it is keyed in, a check is made that the value entered so far is within range for the parameter selected. If not, the display is automatically cleared so that a fresh quantity may be

#### 6.2 Computer Entry of Data

When computer originating data are to be entered, they are received by the simulator as a fixed format block of 21 eight-bit signed binary words: 8 attenuation coefficients for the ground and sky wave channels and 3 noise sources, IMP-MIT, and Doppler, Rayleigh fade rates and delay coefficients for the sky wave channels. To receive external data, the simulator is first put into an Auto mode which makes the panel inoperative (except for return to the Manual mode). Furthermore, Stop and Start signals are also derived externally when the system is in Auto.

#### 6.3 Parameter Storage

The 21 parameters are stored in sign and modulus b.c.d. in r.a.m.s, as received. This is convenient, for binary to b.c.d. conversion is unnecessary when the r.a.m. contents have to be displayed. This latter occurs automatically as a result of data entry or merely selection of any channel/parameter combination. The store display is, like the key parameter value display, a  $2\frac{1}{2}$ -digit gas discharge indicator. However, in the case of the store display, IMP-MIT and Rayleigh fade rates are displayed as absolute rather than encoded values. (Suitable decoders exist on the r.a.m. data output lines for this purpose.)

#### 6.4 H.f. Signal Entry

The incoming signal to be processed may take the form of an analogue waveform (100 kHz carrier modulated at 10 kHz bandwidth and to be sampled at 80 kHz) or an 80 kiloword, 8 bits/word data stream. If it is analogue, the waveform is sampled with a narrow window ( $\sim$  50 ns) sample-hold amplifier, analogue-to-digital converted and stored in a buffer register ready for writing into the m.o.s.-r.a.m. delay store. If the data are received digitally, they are merely logged in the buffer register. The a.d.c. is required to convert in less than 12.5 µs and in practice operates in around 10 µs.

No anti-aliasing filters are provided at the input of the simulator because of the incoming signal bandwidth specification.

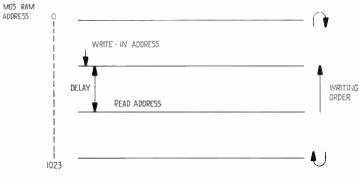

The signal samples are mapped in reverse order contiguous locations in the delay m.o.s.-r.a.m. (which has 1024 eight bit locations). Wrap-around therefore occurs once per 12.8 ms (Fig. 5). The m.o.s.-r.a.m. is read 8 times in each 12.5  $\mu$ s interval to give 4 pairs of contiguously addressed samples—1 pair of each sky wave channel. As the two members of a pair are only 1 location apart, their phase difference is  $\pi/2$  radians based on a down-converted carrier of 20 kHz derived from 80 kHz sampling. The pair is then used in the angle interpolation system described in Section 3.5. The m.o.s.-r.a.m.

#### W. MATLEY and R. E. H. BYWATER

Fig. 5. Delay m.o.s. r.a.m. addressing.

address for the pair is (a+b) modulo-1024 and (a+b+1)modulo-1024 where a is the current m.o.s.-r.a.m. write address (stored in a down counter) and b is the channel delay coefficient (obtained from the delay location of the parameter r.a.m.). (For each unit of delay, i.e. 100 µs, b is incremented by 8, i.e. the m.o.s.-r.a.m. address is advanced by 8 units.)

The specular channel has no delay associated with it (the ground wave arrival instant is taken to be the time origin for the simulation). Thus each sample of the incoming analogue waveform is used directly it arrives as well as being written in the m.o.s.-r.a.m.

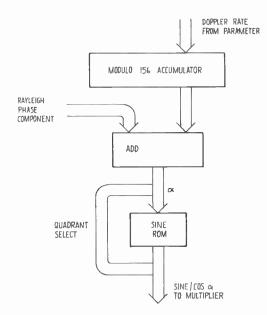

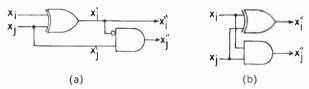

#### 6.5 Doppler Shifting

Doppler shifts could have been simulated by advancing or retarding the delay value for a channel at a certain steady rate but this is impractical as the delay required would become excessively large (positive or negative) within a very short time. The method adopted is to advance or retard the delay in a 'marking time' mode (Fig. 6). In this, the delay is increased steadily by interpolation between m.o.s.-r.a.m. locations n and n+1; returned to n, then n+1. The sine and cosine values (of  $\alpha$ ) are obtained from a sine table r.o.m., the address for which is obtained from a counter whose count rate and direction is determined by the desired Doppler frequency. (This r.o.m. address may be further modified if Rayleigh phase components are also to be expressed.) If the Doppler shift is 1 Hz, the phase advance/retard required of the carrier is  $2\pi$  or 4 sample intervals/second. The sine r.o.m. has I quadrant  $(\pi/2)$  divided into 128 parts (approx. 0.71 degrees), and sampling occurs at 80 kHz. Thus the sine r.o.m. address needs to be changed by I every  $80\ 000/512 \approx 156$  samples. At the maximum Doppler rate of 30 Hz, the sine table address is changed once per 156/30 samples (Fig. 7). Both sine and cosine Doppler weighting coefficients are obtained from the same r.o.m. by using complementary addressing. In order to obtain rolling of the phase over  $2\pi$  radians, whilst retaining use of the same pair of contiguous samples (which are only separated by  $\pi/2$ ), a combination of complementary addressing and the annexing of a suitable sign bit to the sine table output is employed. Thus, for cos 210°, sine 60°

Fig. 6. Doppler rolling mechanism.

is looked up and a sign (negative) annexed to the r.o.m. output.

The resulting 9-bit word is then in binary (sign and modulus) notation.

#### 6.6 Noise Sources

'Noise sources' in this section refer to the G.w.n. and impulsive noise generators, Rayleigh amplitude and phase coefficient generators. They are obtained from a single 31st order m-sequence generator for which the polynomial  $1+x^3+x^{31}$  is used. The generator is clocked 32 times at 10 MHz once per 12.5 µs. It therefore has a period of about 7 hours.

Five functions of a suitable distribution are then derived from combinations of bits in the generator at each  $12.5 \ \mu s$ iteration.

Fig. 7. Doppler frequency to ' $\alpha$ ' weighting coefficients translation.

#### 6.6.1 Impulsive noise

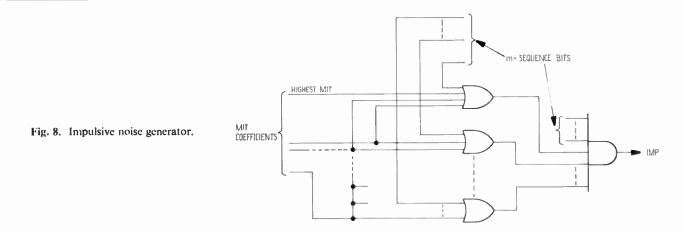

There is a single source of impulsive noise for the simulator which is generated as 200  $\mu$ s (16 iterations) wide pulses of constant amplitude. The noise can then be subjected to up to 40 dB of attenuation using the multiplier. The time of occurrence of each noise impulse is determined by taking a group of m-sequence bits  $(x^n)$  from the polynomial and passing them through an AND gate. In order to vary the mean inter-pulse arrival time, some of the bits are ORed with the MIT coefficient so as to effectively disable them, causing a greater impulse rate to be effected (Fig. 8). The m-sequence generator is ideally suited for impulsive noise generation as such noise is assumed to have a distribution of impulse inter-arrival times which follows a negative exponential law. (Any bit of an m-sequence generator has the same property.)

The output from this noise generator is then passed to the multiplicand input of the multiplier as a unit signal.

#### 6.6.2 Gaussian white noise (G.w.n.)

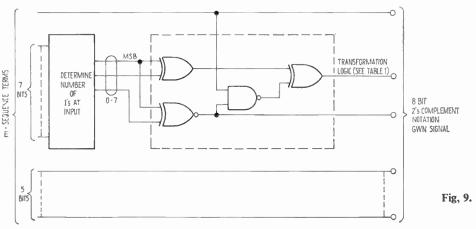

There is a single source of G.w.n. which is also derived from the 31-bit m-sequence generator. The group of bits used is split into two groups, one for the most significant portion of the noise signal which follows a roughly Gaussian distribution and a second group which is left untreated and merely used to provide an even distribution of signal amplitudes between the more coarsely quantized levels. The coarsely quantized Gaussian levels are obtained by taking a group of 8 m-sequence terms, using one for an otherwise untreated sign bit and the remaining 7 to create the desired distribution. Each of the 7 bits is passed to an adder tree to determine the weight of the bits (0-7) and then into a combinational logic circuit which transforms this weight into levels according to Table 2. This transformation logic is also used to convert what

Table 2 G.w.n. distribution generator

| Input weight |              | 2's Complement |

|--------------|--------------|----------------|

| (plus sign)  | Output level | code           |

| 7            | 3            | 011            |

| 6            | 2            | 010            |

| 5            | 1            | 001            |

| 4            | 0            | 000            |

| 3            | 0            | 000            |

| 2            | 1            | 001            |

| 1            | 2            | 010            |

| 0            | 3            | 011            |

| -0           | 3            | 101            |

| -1           | 2            | 110            |

| -2           | 1            | 111            |

| -3           | 0            | 000            |

| -4           | 0            | 000            |

| -5           | 1            | 111            |

| -6           | 2            | 110            |

| -7           | 3            | 101            |

Fig, 9. Gaussian white noise generator.

would otherwise be sign and modulus information into 2's complement notation, suitable for the multiplier's multiplicand port. The multiplier is used to append the appropriate attenuation factor (Fig. 9).

#### 6.6.3 Rayleigh amplitude<sup>3</sup>

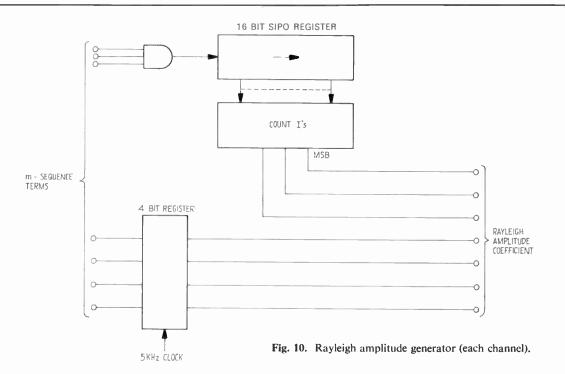

Four signals are generated to modulate each of the four sky-wave channels according to a Rayleigh distribution. Three m-sequence terms are obtained for each of the 4 channels. These bits are passed through a 3-input AND gate to give an 8-fold division in the occurrence of 1's from the m-sequence generator and then through a 16-bit shift register whose content of 1's at any time is used as a coarse amplitude (modulation) coefficient for the skywave channel in question. On average, the shift register has only two logic 1's in it but the distribution will roughly follow a law of the form  $x \cdot \exp(-x)$ . The shift register contents are monitored in a saturable counter whose contents are limited to 7 quanta. The counters contents (3 bits) are then used as the most significant portion of the Rayleigh instantaneous amplitude coefficient. For each channel, a group of 4 m-sequence terms are then used to provide a less significant 'fill-in' of uniform distribution. These are only updated at a low rate (around 5 kHz) so that the band-pass filter on the simulator's output does not cause 'dips' in the Rayleigh distribution between the coarse quantization points (Fig. 10).

#### 6.6.4 Rayleigh phase 'walk'

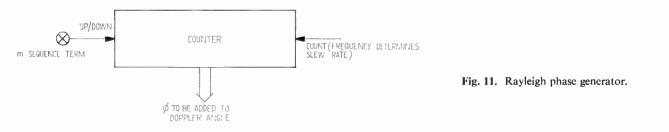

Four channels of this phenomenon are provided, one for each sky wave. It is generated in the manner of a pseudo-random rate limited walk using terms from the m-sequence generator to determine walk 'direction'  $(\Delta\phi)$ .  $\phi$  is used to drive the trigonometric r.o.m. to provide sin  $\alpha$  and cosine  $\alpha$ , in conjunction with the Doppler generator. The latter provides a steady 'rolling' of  $\alpha$ between 0 and  $2\pi$  radians whilst the former superimposes an additional Markovian walk. For each channel, a single m-sequence term provides the walk direction at any time and a suitable sub-multiple of the 80 kHz system clock provides rate limitation (Fig. 11).

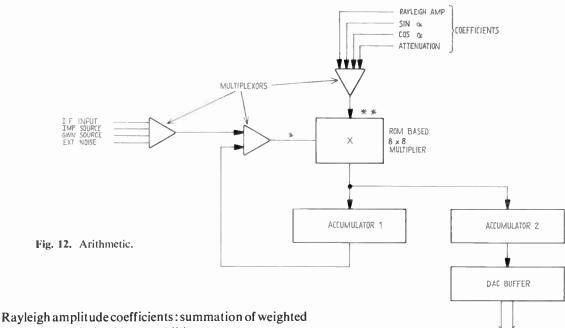

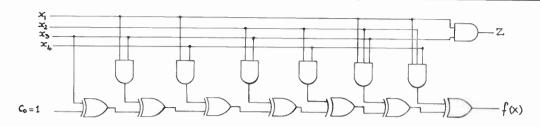

#### 6.7 Arithmetic

The arithmetic unit for the h.f. simulator has only multiplication and two levels of accumulation to perform. However, a complete process has to take place within  $12.5 \ \mu s$  (including m.o.s.-r.a.m.) cycles. The arithmetic processes are:

(i) Weighting of 4 pairs of m.o.s.-r.a.m. words with sine and cosine components and multiplication by

#### A DIGITAL HIGH-FREQUENCY MULTIPATH PROPAGATION SIMULATOR

pairs (12 multiplications, 4 additions).(ii) Weighting of weighted pairs, noise sources and the

specular signal with attenuation coefficients (8 multiplications, 8 additions) (Fig. 12).

Accumulator 1 collects the trigonometrically weighted samples for each channel prior to the application of the Rayleigh amplitude control and attenuation coefficients; accumulator 2 collects the finally weighted signals from the 5 channels and the noise sources. Signals enter the multiplier at port \* and are in 2's complement notation. Multiplier values enter at \*\* and are in sign and modulus form. The multiplier output is in 2's complement notation so that it is suitable for both (i) re-entry to the multiplier at input port \* and (ii) and for a conventionally signed accumulator.

As 20 multiplications have to be performed in about  $4 \mu s$ , a purely combinational design, based on r.o.m.s, is used.<sup>2</sup> Although 8-bit operands are used, only an 8-bit

product is derived because of the uncertainty associated with each operand. Treating each operand (x, y) as a signed fraction of range  $\pm 1$  in steps of  $2^{-7}$ , then the uncertainty of each operand is  $\pm 2^{-8}$  (at least). Thus the product x.y has an uncertainty of about  $2^{-8}(x+y)$ . If x and y assume their maximum magnitudes and the uncertainties are assumed to aggregate, the product uncertainty becomes  $\sim \pm 2^{-7}$ .

The accumulators are conventional adder/register pairs but use multi-bit adders with internal carry look-ahead to improve speed. Accumulator 2 contains the final result after all the arithmetic operations have been carried out.

#### 6.8 Output

The digital results can be presented, *per se*, to any 8-bit (80 kiloword/second) receiver or, more often, passed

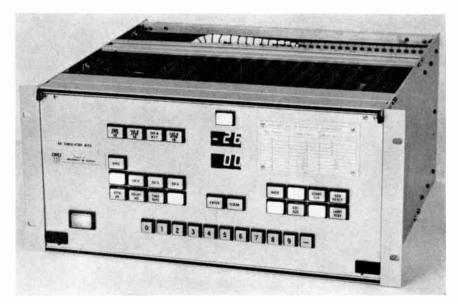

Fig. 13. Rack mounting version of H.F. Multipath Propagation Simulator.

through a digital-to-analogue convertor, sample-hold amplifier (to remove glitches, etc.) and a 100 kHz fourthorder Butterworth filter for presentation in band-limited analogue form.

#### 6.9 Construction and Power Supply

The construction follows conventional practice using vertically mounted cards in a card frame. However, the amount of power required, around 80 W, has required careful choice and placement of the power supply units. Heat dissipation is greatly reduced by the use of a switching regulator for the main logic supply. The complete prototype instrument is shown in Fig. 13.

#### 7 Conclusion

The h.f. propagation simulator described in this paper is currently undergoing trials at the Admiralty Surface Weapons Establishment and all the design criteria have been verified except for the nature of the correlation requirement between the Rayleigh amplitude and phase noise generators. This point is being studied in the initial evaluation programme, and, if required, any necessary minor modifications to the Rayleigh noise sources can be carried out.

Field trials have suggested that the digitally derived models of Gaussian noise and Rayleigh fade and phase phenomena correspond well with those experienced in ionospheric propagation. A mathematical treatment of these models is to be the subject of a later paper.

#### 8 Acknowledgments

This work has been carried out with the support of the Procurement Executive, Ministry of Defence and is published with their permission. Particular thanks are due to Dr. M. Darnell and Mr. J. Pennington of the Admiralty Surface Weapons Establishment for originating the specification to which the equipment was constructed. Thanks are also due to Dr. N. Ream and Mr. T. G. Jeans of the Department of Electronic and Electrical Engineering, University of Surrey for their efforts in designing the pseudo-random sequence generators and systems filters, respectively, and also to Messrs. D. Brock and R. Hawkes for engineering design and implementation.

#### **9** References

- 1 Bywater, R. E. H., Matley, W. and Brock, D., 'Design of a flexible phase reversal modulation correlator', *The Radio and Electronic Engineer*, **46**, No. 3, pp. 129–35, March 1976.

- 2 Bywater, R. E. H., 'A binary multiplier for signal processing applications', *Digital Processes*, 1, pp. 261-5, 1975.

- 3 Law, H. B., et al., 'An improved fading machine', Proc. Instin Elect. Engrs, 104B, pp. 117-23, March 1957.

- 4 Ralphs, J. D. and Sladen, F. M. E., 'An h.f. channel simulator using a new Rayleigh fading method', *The Radio and Electronic Engineer*, 46, No. 12, pp. 579–87, December 1976.

- 5 'H.F. Ionospheric Channel Simulators', XIIIth Plenary Assembly CCIR, Geneva 1974, Vol. 3, Report No. 549.

- 6 Rice, S. O., 'Statistical properties of a sine wave plus random noise,' *Bell Syst. Tech. J.*, 27, pp. 109–57, January 1948.

- 7 Sterling, J. T., 'An Introduction to Pseudo-noise Codes and Correlators', General Electric Technical Information Series No. R62 DS D34, 1962.

- 8 Wheeler, H. K. and Law, H. B., 'The Piccolo 32-tone Telegraph System Subject to Noise and Fading', GPO Research Report No. 20879, March 1964.

Manuscript first received by the Institution on 23rd December 1976 and in final form on 17th March 1977 (Paper No. 1773/Com. 152).

C The Institution of Electronic and Radio Engineers, 1977

Wallace Matley is a graduate of London University and the first eleven years of his professional career were spent in the Royal Naval Scientific Service on all aspects of radar R & D from systems research to post design development. From 1954 to 1956 he was with the Australian Department of Supply designing and developing rocket range instrumentation. He returned to the RNSS in 1956 and for the

next five years worked on microwave aerial research, missile system command and display development. From 1961 to 1964 he was Chief Engineer at the Royal Observatory, Edinburgh, implementing the application of electronics to astronomy, and in 1964 he went to the Government Communication Headquarters to do communication system research. Since 1969 he has been a Senior Lecturer and Leader of the Industrial Electronics Research Group in the Department of Electronic and Electrical Engineering, University of Surrey.

Robert Bywater graduated from Battersea College of Technology, London, with a B.Sc. degree in electrical engineering in 1964. After spending a further year reading computer engineering, he joined the Computer Systems Development Group of ICL, then English Electric Computers. Currently, he is a Lecturer in electrical engineering at the University of Surrey with research interests in special purpose com-

puters. He gained his doctorate in 1975 for a thesis arising from his work.

The Authors

# Analysis of insertion loss repeatability of coaxial connectors

P. PÁKAY, Dipl.Ing., Dr. Techn.\*

and A. TÖRÖK, Dipl.Ing.\*

Based on a paper presented at the IMEKO VII Conference held in London on 10th to 14th May 1976

#### SUMMARY

The repeatability of insertion loss of the most commonly used coaxial connector pairs was tested between 100 MHz and 12 GHz. The resolution of the measurements was better than 0.0001 dB. With carefully performed connections the repeatability expressed in standard deviation varied between 0.0002 and 0.002 dB. These values are some 2–3 times smaller than those published by Bergfried and Fisher.<sup>1</sup> The method described is particularly suitable for measuring the attenuation of small-loss elements such as adapters, air-spaced lines, etc.

\* Department of Electronic Measurements, National Office of Measurement, Budapest, Hungary.

#### Nomenclature

- $\sigma$  standard deviation of the insertion loss variation of the connector pair, dB.

- $\sigma_{\Gamma}$  standard deviation of the reflection factor variation of the connector pair (ratio).

- $|\Gamma_0|$  mean of the absolute value of the connector pair reflection factor.

#### **1** Introduction

During the last few years considerable work has been done to improve the characteristics of r.f. and microwave instrumentation. This has increased interest in coaxial connectors as no measuring system can omit them.

Coaxial connectors are specified by performance characteristics such as v.s.w.r., insertion loss, contact resistance, r.f. leakage, electrical length, as well as the repeatability of these parameters. Repeatability is the permanency of the given parameter during the connectdisconnect cycles. Among the parameters mentioned, insertion loss has a particular importance, since its repeatability includes in practice the effects of all the other parameters.

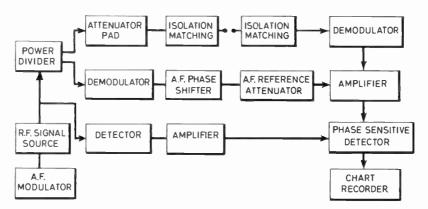

The difficulty in measuring the insertion loss repeatability of precision coaxial connectors results from the fact that very small variations of attenuation, often of the order of  $10^{-4}$ , must be detected. This needs a measuring system of appropriate stability and resolution capability. To meet these requirements an improved version of the a.f. substitution method described by Korewick and Pakay<sup>2.3</sup> was used for the present tests. The most widely applied precision and semi-precision coaxial connectors were tested between 100 MHz and 12 GHz. The repeatability of the insertion loss was expressed in terms of the standard deviation and system drift was excluded from the results by applying linear correction. From the results conclusions can be drawn concerning the choice of suitable connector types and their fields of application.

#### 2 Measurement Method

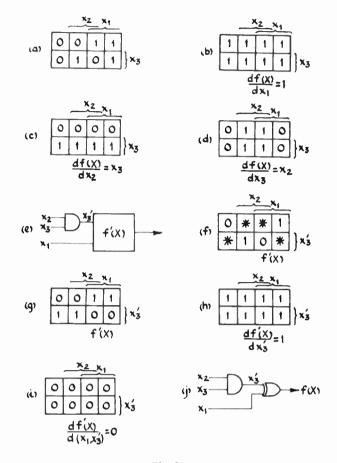

The block diagram of the dual-channel a.f. substitution measurement system is shown in Fig. 1. The given method is specially capable for the precise measurement of small attenuations. The dual channel system assured a compression of the r.f. signal source level instability by a factor of 30-40 depending of the symmetry of the barretter demodulators. The 7-digit inductive ratio transformer used as a.f. reference attenuator was capable of indicating the small changes of attenuation of the order of  $10^{-4}$ – $10^{-5}$ dB. For detector a phase-sensitive device was used. Its reference signal was obtained by detecting the square wave modulated r.f. signal. By means of the indication of the signals below noise level the phase-sensitive detector made possible the extension of the dynamic range of the measurement by approximately 10 dB in comparison with that of the usual narrow-band detector or an equivalent one-order extension of the resolution. With 100  $\mu$ W r.f. input power the a.f. output voltage of the applied barretter

Fig. 1. Block diagram of the insertion loss repeatability measurement equipment.

mounts was some 2 mV. In this case a change of level of 30–40 nV at the ratio transformer corresponded to a change of attenuation of  $\sim 10^{-4}$  dB. The sensitivity of the phase-sensitive detector permitted a resolution better than  $10^{-4}$  dB. However it would not have been reasonable as the short-time stability of that simple system without any particular concern for r.f. source level control of thermostatic facilities is of the order of  $10^{-4}$  dB. For better evaluation the results were displayed on a chart recorder connected to the output of the phase-sensitive detector (Fig. 2). The generator and detector sides were matched at the insertion point for v.s.w.r. < 1.01 by means of

Fig. 2. Typical insertion loss repeatability chart for SMA connector pair at 10 GHz.

coaxial tuners. The matching elements gave some thermal isolation between the insertion point and the test barretter as well which was needed to reduce heat transfer from operator's hands.

In assembling the measurement system care was taken to eliminate the parasitic signals, e.g. earth loops.

The measurements were performed under normal laboratory conditions with a temperature stability  $\pm 0.5^{\circ}$ C.

#### 3 Measurement Technique

The intention was to test the repeatability with carefully performed connections, made under usual working conditions.

During the tests it was found that the quality of the connections depends on two factors of mainly mechanical character; namely, tightening torque and transverse alignment force.

Therefore the connectors to be tested were mounted vertically to minimize the transverse alignment force necessary for proper connection. However to get a better approach to real life conditions the connectors were tightened by hand though in a careful way. Average torque for 7 mm connectors was about 1 Nm. The importance of the alignment of the connectors is demonstrated by the 10 GHz measurements performed on the same connectors in both vertical and horizontal arrangements. (Table 1.)

| Table 1. | The results of insertion loss repeatability measurements |

|----------|----------------------------------------------------------|

|          |                                                          |

|                                              |          |        | Standard | deviation (dB | )       |                  |

|----------------------------------------------|----------|--------|----------|---------------|---------|------------------|

|                                              | 100 M Hz | l GHz  | 6 GHz    | 10 GHz        | 10 GHz† | 12 GHz           |

| APC 7                                        | 0.0002   | 0.0002 | 0.0009   | 0.0007        | 0.0009  | 0.0008           |

| SMA Sub-miniature, semi-precision (Amphenol) | 0.0003   | 0.0004 | 0.0004   | 0.0006        | 0.0008  | 0.0010           |

| N stainless steel (MIL C39012)               | 0.0002   | 0.0006 | 0.0009   | 0.0010        | 0.0014  | 0.0014           |

| Dezifix A                                    | 0.0003   | 0.0012 | 0.0014   | 0.0020        | 0.0021  | 0· <b>0</b> 019‡ |

| GR 900                                       | 0.0003   | 0.0003 | 0.0005   |               |         |                  |

| GR 874                                       | 0.0005   | 0.0009 |          |               |         |                  |

| UHF                                          | 0.0002   | 0.0009 |          |               |         |                  |

| Dezifix B                                    | 0.0004   | 0.0009 |          |               |         |                  |

<sup>†</sup> Horizontal arrangement. <sup>‡</sup> Connector Prezifix A.

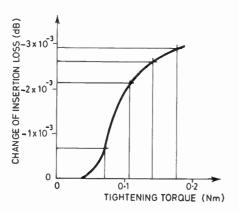

Fig. 3. Insertion loss versus tightening torque for SMA connector pair at 10 GHz.

A wrench (with about 0.2 Nm torque) was used only for SMA connectors since it is customarily used in practice. The insertion loss versus tightening force characteristics of these connector pairs were also measured (Fig. 3).

#### 4 The Results of the Measurements

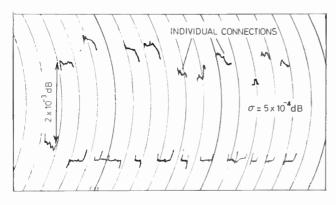

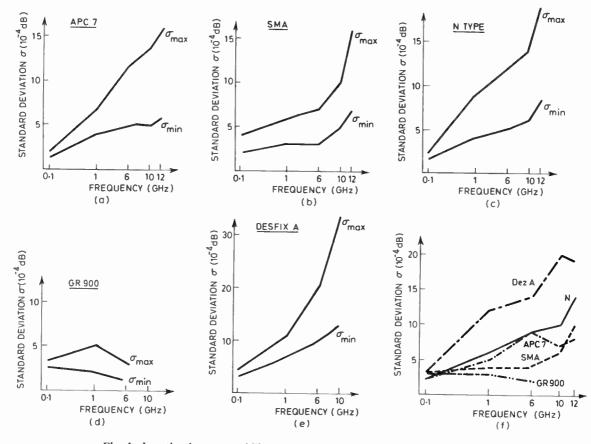

The results of insertion loss repeatability tests versus frequency are presented in Fig. 4(a-f) and in Table 1.

Three or four specimens of each connector types were tested. The average number of measurements varied

between 20 and 30 and experience showed that 20 was the number of measurements where the standard deviation approached the value characteristic of the given connector pair. Since the standard deviations for the individual connectors and for repeated series of measurements on the same connectors were not necessarily identical the boundaries belonging to the maximum and minimum  $\sigma$  values are shown at the diagrams. In Table 1 and Fig. 4(f) the  $\sigma$  represents a mean of the repeated series of measurements and it can therefore be considered as an average standard deviation characteristic of the type of connector pair at the given frequency.

At 100 MHz and 1 GHz the tests included those semiprecision coaxial connectors as well at which the measurements at higher frequencies were not reasonable. The results of the 10 GHz measurements performed in horizontal arrangement are presented separately.

Table 2 summarizes the results of the insertion loss measurements of some commonly used coaxial adapter pairs. Since only one specimen of each type was tested the results are of informative nature. The systematic error of the measurement estimated from the v.s.w.r. at the insertion point and that of the item to be measured was < 0.003 dB with the exception of the u.h.f. adapter pair at which it was well over  $\pm 0.01$  dB at 1 GHz. The

Fig. 4. Insertion loss repeatability versus frequency for various types of connector. (a) APC 7 connectors; (b) SMA connectors; (c) N type connectors; (d) GR 900 connectors; (e) Dezifix A connectors; (f) Mean of the plots for each of the five types of coaxial connector.

measurements were performed on adapters between the connector listed and N type connectors (100 MHz and 1 GHz) and APC 7 connectors (6 GHz and 10 GHz). The adapter pairs were formed with the connectors listed in Table 2 interconnected, so that male and female N connectors (100 MHz and 1 GHz) or APC 7 connectors (6 GHz and 10 GHz) appeared at each end of the assembly for testing.

#### 5 Evaluation of the Results

To estimate the confidence of the data one must determine the error sources of the a.f. substitution system. The errors are partly of random and partly of systematic character<sup>3</sup>:

(a) reference attenuator errors

(b) errors due to demodulator and the associated circuitry (primarily the barretter non-linearity error)

- (c) mismatch error

- (d) parasitic signals

- (e) noise-limited detector sensitivity

- (f) system instability.

The errors (a) to (e) can be neglected partly because very small changes in attenuation had to be measured and partly because of reasons mentioned above. The accuracy of the results obtained was determined ultimately by the overall instability of the measuring system resulting from the following principal components:

power variations of the r.f. signal source (secondary effect because of non-identical characteristics of the test and reference barretters);

temperature sensitivity of the r.f. elements first of all of the barretter mounts;

mechanical instability of the r.f. circuitry (this means to what degree the associated r.f. elements are resistant to the small but unavoidable deforming forces during the connection cycles).

The above instabilities were each of the order of  $10^{-4}$  dB for a short time. The slow drift of the measurement system was <0.0006 dB over the 10 minutes time taken for 20 measurements.

| Table 2   |      |    |         |       |  |  |

|-----------|------|----|---------|-------|--|--|

| Insertion | loss | of | adapter | pairs |  |  |

|                   | Insertion loss (dB) |       |        |        |  |  |

|-------------------|---------------------|-------|--------|--------|--|--|

|                   | 100 MHz             | 1 GHz | 6 GHz  | 10 GHz |  |  |

| APC 7             | 0.008               | 0.040 |        | 0.113† |  |  |

| SMA               | 0.007               | 0.024 | 0.069  | 0.097  |  |  |

| N stainless steel | 0.004               | 0.011 | 0.064  | 0.082  |  |  |

| Dezifix A         | 0.002               | 0.012 |        |        |  |  |

| GR 900            | 0.005               | 0.051 | 0.054† |        |  |  |

| GR 874            | 0.004               | 0.015 |        |        |  |  |

| UHF               | 0.028               | 0.26  |        |        |  |  |

| Dezifix B         | 0.003               | 0.017 |        |        |  |  |

† Between N type connectors.

The standard deviation of the connection repeatability was evaluated in a similar way by using linear correction. The application of the more complicated second-order correction would not have been reasonable.

Figure 2 gives an example for the recorded results of some 10 cycles in a test series. Here the slow drift being very small, the standard deviation calculated with and without correction was nearly identical.

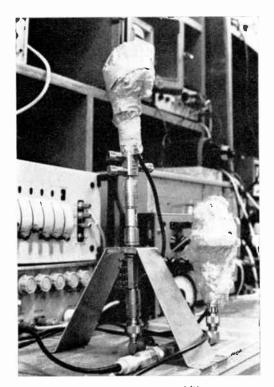

At 10 GHz, as mentioned previously, repeatability measurements were performed in both vertical and horizontal arrangements. The vertical arrangement mounted on a stand made easier the axial alignment of the connector pairs to be measured (Fig. 5). The deviation between the results of the two kinds of measurements is an index of how definitely the axial alignment is assured by the coupling mechanism itself at the given type of connectors (Table 1).

The insertion loss versus tightening torque relationship was examined for SMA connector pairs at 10 GHz. The results in Fig. 3 indicate that to get a good reproducibility it is necessary to use a torque > 0.2 Nm, i.e. where the gradient of the curve significantly decreases. The decrease in insertion loss of the SMA connector pair with increasing tightening torque is related to that insertion loss value corresponding to 0.035 Nm torque at reference 0 dB.

Fig. 5. The vertical system for repeatability measurements.

The Radio and Electronic Engineer, Vol. 47, No. 7

Because of the small physical dimensions of the connector, however, good reproducibility could be ensured only by torque wrench.

The standard deviation values obtained at the 100 MHz reproducibility measurements fell nearest to the system instability level, representing a limit for the applicability of the method.

The reasons for the variation of insertion loss of connector pairs are associated with both the variation of dissipation and reflexion of energy at the junction point. The permitted change in contact resistance can appreciably influence the dissipation loss, whereas the effect of a possible change in r.f. leakage is quite negligible for precision connector pairs. The variation of the reflection coefficient at the junction can also have a considerable effect on the reflection loss and in this way alter the insertion loss.

This relationship can be expressed in explicit form provided the other effects are neglected and the system reflection at the insertion point is small compared to the reflection of the connector pair to be tested. The approximate relation in this case is as follows:

#### $\sigma \approx 8.7 |\Gamma_0|\sigma_r$

If the system reflection cannot be neglected full phase information becomes necessary to describe the phenomenon.

#### 6 Conclusions

According to the results obtained under normal conditions but with carefully performed connections, the insertion loss repeatability of the precision coaxial connector pairs ranged between  $2 \times 10^{-4}$  and  $20 \times 10^{-4}$ dB up to 12 GHz. These values seem to determine the practical limits of accuracy for insertion loss measurements of coaxial attenuators and other components.

In the frequency range of the present tests the differences in repeatability between the various types of precision and semi-precision connector pairs did not surpass one order of magnitude. However the sharp degradation of repeatability above 10 GHz indicates that in the vicinity of the upper frequency limits of the connectors considerable differences are to be expected.

With the applied method it was possible to examine how variations of some mechanical parameters influence the quality of the connections. In that respect the connector insertion loss versus tightening torque and loss repeatability versus connector positioning relationships were tested.

Concerning the better repeatability of the coaxial connector pairs compared with those obtained by Bergfried and Fischer this is thought to be due partly to the improvement of the measurement apparatus regarding its stability and sensitivity, and partly to the carefully performed connections.

#### 7 References

- Bergfried, D. and Fischer, H., 'Insertion-loss repeatability versus life of some coaxial connectors', *IEEE Trans. on Instrumentation* and Measurement, IM-19, No. 4, pp. 349-53, November 1970.

- 2 Korewick, J., 'A-m system measures microwave attenuation', *Electronics*, 27, No. I, pp. 175-7, January 1954.

- 3 Pakay, P., 'Simple method for the accurate measurement of low attenuations', Colloque International sur l'Electronique et la Mesure, Paris 1975, France.

Manuscript first received by the Institution on 18th May 1976 and in final form on 24th January 1977 (Paper No. 1774/M15).

C The Institution of Electronic and Radio Engineers, 1977

Peter Pákay received the Diploma Engineer and the Doctor of Technology degrees from the Technical University of Budapest in 1966 and 1973 respectively. In 1966 he joined the National Office of Measures, Hungary, where he is a research worker at the Division of High Frequency Measurements. His main fields of interest are in attenuation measurements, particularly the precise measurement of low attenuation.

Andras Török received the Diploma Engineer degree in telecommunication engineering from Technical University the of Budapest in 1966. After graduating, he joined the National Office of Measures, Hungary where he is present at a research worker. His main fields of interest are in precision microwave power and attenuation measurement especially in the development of standard equipment for microwave measurements.

The Authors

### Letters

From: H. M. Merklinger, Ph.D.

J. M. Hovem, Dr. Ing.

R. Benjamin, D.Sc., Ph.D., C.Eng., F.I.E.E., F.I.E.R.E.

#### **Non-linear Acoustics**

The paper 'A new sub-bottom profiling sonar using a nonlinear sound source'<sup>1</sup> accurately presents one of the promising applications of non-linear acoustics. The references cited in the paper fail, however, to emphasize the role of British Science in this development.

Until the 1965 publications of Tucker<sup>2</sup> and Berktay<sup>3</sup> from the University of Birmingham, the phenomenon reported by Westervelt<sup>4</sup> was largely of academic interest. The recognition that this non-linear effect was of practical utility was a very significant event. The methods by which the effect could be exploited were set down by Berktay.<sup>3</sup> With only one exception, the acoustic theory reported by Pettersen *et al.*<sup>1</sup> is contained in the papers of Westervelt,<sup>4</sup> Berktay<sup>3</sup> and Merklinger.<sup>5</sup> References 7–12 cited by Pettersen *et al.* consist largely of developing and polishing these original ideas.

The authors are to be commended for engineering a sophisticated instrument, but I feel their references might lead readers to believe that the acoustic principles involved were probably developed entirely within the United States of America. I think it would be true to say that the original invention was American, but that the subsequent practical development was largely British.

#### HAROLD M. MERKLINGER

Defence Research Establishment Atlantic, P.O. Box 1012, Dartmouth, N.S. B2Y 3ZY, Canada.

27th May 1977

#### References

- I Pettersen, P., Hovem, J. M., Lovik, A. and Knudsen, T., *The Radio and Electronic Engineer*, 47, No. 3, pp. 105–11, March 1977.

- 2 Tucker, D. G., 'The exploitation of non-linearity in underwater acoustics', J. Sound Vib., 2, pp. 429-34, 1965.

- 3 Berktay, H. O., 'Possible exploitation of non-linear acoustics in underwater transmitting applications', J. Sound Vib., 2, pp. 435-61, 1965.

- 4 Westervelt, P. J., 'Parametric acoustic array', J. Acoust. Soc. Am., 35, pp. 535-7, 1963 (Ref. 6 of paper by Pettersen et al.).

- 5 Merklinger, H. M., 'Of finite amplitude plane waves and of endfire arrays', Proc. 3rd Symposium on Nonlinear Acoustics, pp. 114-25, University of Birmingham, 1st-2nd April 1971.