## Argus Specialist Publications . . .

REMOTE CONTROL PHOTOGRAPHY Nikon Infra-red Remote 1984 Components and Hardware ty Power Supply Linit Ield Strength Meter – with memory Timing Strobe for accurate motor tunk Survey The Longest Calibign SPECIAL REVIEW: Angus McKenzie investigates the new icom 271 + muTek front end - the ultimate 2m performer

... for the latest in electronics, computing and radio

### Volume 4 No. 4 INTRODUCT

In order to understand computers, you must know some electronics; so the first part of this volume, Configurations, is a summary of some of the most frequently met circuits in electronics. This section assumes that you have already met transistors - if this is not the case, then we suggest turning first to Electronic Digest Volume 4 No 1 — Introduction to Circuit Design.

The Interlude deals with a few topics that don't fit into either of the other two sections, yet that will still be of use to you.

The final section is the description of computer systems itself. While we cannot hope to teach you all there is to know about the workings of computers in such a slim volume, we hope that what is presented here will equip you to understand the more advanced books and articles that you will come across.

### CONFIGURATIONS 3: Transistors with common collector connection ......10 5: Sawtooth generators ......16 6: Operational amplifiers ......19 7: Sine wave oscillators ......22 8: Audio power amplifiers ......25 INTERLUDE Video systems ......41 Computer-controlled live music ......47 User's guide to microphones ......51 MICROCOMPUTERS 3: Read only memory ......70

5: Input and output for computers ......81 6: Input and output for humans ......87

7: Magnetic tape and floppy discs ......94

**Editor:** Dave Bradshaw **Special Publications Editor:** Wendy J. Palmer **Managing Editor:** Ron Harris **Advertisement Manger:** Paul Stanver

**Chief Executive:** T. J. Connell

**ORIGINATED BY: Tabmag,** Northampton. **PRINTED BY: Garden City Press,** Letchworth.

### © 1984

Subscription rates upon application to Electronics Digest, Subscriptions Dept., PO Box 35, Wolsey House, Wolsey Road, Hemel Hempstead, Herts HP2 4SS.

PUBLISHED BY: Argus Specialist Publications Ltd, 1 Golden Square, London W1R 3AB.

DISTRIBUTED BY: Argus Press Sales & Distribution Ltd, 12-18 Paul Street, London EC2A 4JS (British Isles).

© Argus Specialist Publications Ltd 1984. All material is subject to worldwide copyright protection. All reasonable care is taken in the preparation of the magazine contents, but the publishers cannot be held legally responsible for errors. Where mistakes do occur, a correction will normally be published as soon as possible afterwards. All prices and data contained in advertisements are accepted by us in good faith as correct at time of going to press. Neither the adver-tisers nor the publishers can be held responsible, however, for any variations affecting price or availability which may occur after publication has closed for press.

## CONTENTS

Not our answer to James Burke but a series aimed at the designer. Ian Sinclair will be looking at some of the basic workaday circuits that often get eclipsed by the more glamorous ICs, showing you how and why they work and how and why to use them. We kick off with common-emitter transistor bias.

onfigurations is a series which aims to provide you with fundamental circuit design data for a number of the most commonly used circuit blocks. A very large amount of circuit work concerns these standard arrangements, so that you will be able to build up a complete designer's handbook of circuits and their design data. We're starting with the most fundamental of all biasing and calculating gain and bandwidth of the singlestage common-emitter amplifier, using a silicon transistor with a resistive load.

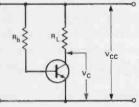

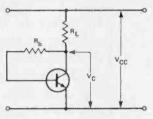

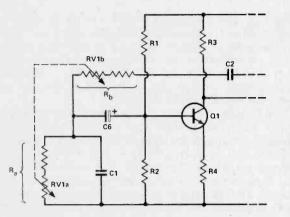

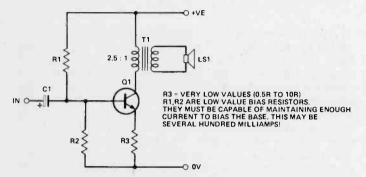

Fig. 1 Simple single-resistor bias circuit. The value of resistance depends critically on the value of h<sub>fe</sub> for the transistor.

The simplest bias circuit, of course, is that of Fig. 1, using a single bias resistor connected between the base and the supply positive. We're not going to spend much time on this one, because it's not a very good bias method from any point of view. The reason is that the resistor value has to be spot on for this method of work, and you have to know the current gain ( $h_{ie}$ ) value for that particular transistor (not just the average for the type) to a fair degree of accuracy. If you need to use that method and have a box of 1% tolerance resistors handy, then the design data is illustrated in Fog. 1. One of the few things that can be said for the circuit is that a high input resistance is attainable, but more on that subject later.

### **A Favourable Bias**

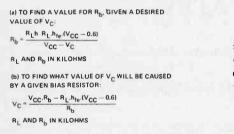

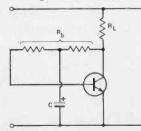

A much more practical bias method is illustrated in Fig. 2. This makes use of DC shunt feedback between the collector and the base of the transistor, and is less likely to be upset by the changes that occur in the characteristics of the transistor as it heats up. You still have to know the  $h_{fe}$  value for the transistor, but the collector voltage won't be so far out if you just use an average value for the type and it happens that the one you're using is at one end of the range of values. The formula, like the previous one, assumes that the base-to-emitter voltage when the transistor is conducting will be 0V6 and since this is the

(a) TO FIND A VALUE FOR R. GIVEN A DESIRED VALUE OF VC

$$\begin{split} R_{b} &= \frac{R_{L} h_{fe} (V_{C} - 0.6)}{V_{CC} - V_{C}} \\ R_{L} \text{ AND } R_{b} \text{ IN KILOHMS} \\ \text{EXAMPLE: IF } R_{L} = 2k2, h_{fe} = 100, V_{CC} = 9V, V_{C} = 3V, \text{ THEN} \\ R_{b} &= \frac{2.2 \times 100 \times 2.4}{6} = 88k \end{split}$$

(b) TO FIND A VALUE FOR V<sub>C</sub>. GIVEN R<sub>b</sub>:  $V_{C} = \frac{R_{b} \cdot V_{CC} + 0.6R_{L} \cdot h_{fe}}{R_{b} + R_{L} \cdot h_{fe}}$  Fig. 2 Shunt-feedback bias. The value of collector voltage is less dependent on the h<sub>fe</sub> value. Note the units, with all resistances in kilohms.

quantity that changes most as a silicon transistor heats up, it's worth while taking a look at how this bias method is affected.

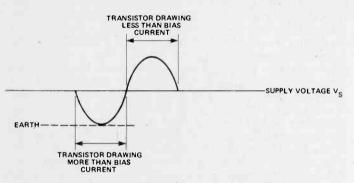

Figure 3 shows two calculations of collector voltage, both assuming a supply voltage ( $V_{cc}$ ) of + 9 V, load resistor of 2k2,  $h_{fe}$  value of 100, and bias resistor  $R_b$  of 88k. However, one uses 0V6 as the  $V_{be}$  figure and the other uses

ASSUME IN BOTH CASES THAT  $P_b = 88k$ ,  $h_{fe} = 100$ ,  $V_{CC} = 9V$ ,  $R_L = 2k2$ . WHEN  $V_{be} = 0V6$ ,  $V_C = \frac{88 \times 9 + 0.6 \times 2.2 \times 100}{88 + 2.2 \times 100} = 3V$ WHEN  $V_{be} = 0V5$ ,  $V_C = \frac{88 \times 9 + 0.5 \times 2.2 \times 100}{88 + 2.2 \times 100} = 2V93$ DIFFERENCE IN  $V_C = 70 \text{ mV}$

Fig. 3 Effect of temperature. The  $V_{be}$  (assumed 0V6 for a silicon transistor) decreases as the temperature rises. The calculations show that the collector voltage value is hardly affected.

0V5. The difference in the collector voltage is negligible, which points to this method of bias as being a very useful one when you are worried about the effect of temperature changes on the performance of the transistor.

The circuit uses feedback, of course, and unless something is done to remove the feedback of AC, the gain of the stage and its input resistance will be reduced. The

Fig. 4 Removing AC feedback by splitting the bias resistor into two sections and decoupling.

**ELECTRONICS DIGEST, SPRING 1984**

reduction in gain isn't serious for most circuits, but the input resistance problem can be more serious — it's detailed later in this article. Both can be tackled if AC is removed from the feedback path by splitting the bias resistor into two parts and decoupling it, as shown in Fig. 4.

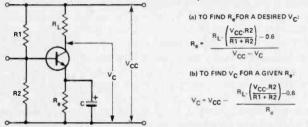

### An Arrangement With Potential

The most-extensively used of all bias methods is our old friend in Fig. 5, which uses a potential divider to provide a constant voltage (we hope) at the base of the transistor, and DC feedback (series feedback this time) through the emitter resistor to stabilise the bias. The notable thing about the formula is that  $h_{ie}$  doesn't appear anywhere in it, so that the bias should not be affected by the value of  $h_{ie}$ . This means that the circuit is very tolerant of wide ranges of  $h_{ie}$  values, providing the base current of the transistor is not so large that it disturbs the base bias voltage set by the potential divider. As a rule of thumb, if the current flowing through R1 and R2 (equal to  $V_{cc}/(R1 + R2)$ ) is something like 100 times the base current of the transistor, then the circuit will work exactly as per design, and any transistor whose base current is within limits can be used with the same bias components. If the base

Fig. 5 The potential-divider bias method. This is particularly useful for mass-produced circuits, because bias does not depend on h<sub>6</sub> values.

current of the transistor is far from negligible then complication arise, and it's easier just to use lower values of R1 and R2 — but for the effect on input resistance, see later. For voltage amplifier stages where the collector current is only about 1 mA, values like 6k8 and 1k5 on a 9 V supply will suit the circuit very nicely.

One disadvantage of the circuit is that there's an emitter DC voltage so that the available voltage swing at the collector is correspondingly reduced. The other point, which is important where space is limited, is that decoupling of the emitter resistor is essential. Without decoupling the gain is low; it's given by  $R_t/R_e$  and will be around two to six times for the kind of values you are likely to end up with in a practical circuit. The decoupling capacitor operates at low voltage, so that a 3 V or 6 V type is normally adequate, but its value has to be large to avoid a noticeable loss of gain at low frequencies. It certainly isn't enough to have the reactance of the capacitor equal to the resistance value of Re at the lowest frequency for which the amplifier is intended to be used, because if you make this assumption for each coupling and decoupling time constant, you'll end up with practically no gain at that frequency. Aim for a capacitor reactance of about one fifth of the emitter resistance value at the lowest frequency you intend to use and the results will be more acceptable. With C in microfarads and Re in kilohms, this means a value given by the equation  $C = 5000 / 2\pi f.R_{\odot}$

and for a 390 ohm emitter resistor, this indicates a capacitor value of around 50uF for a 40 Hz breakpoint. Even at 3 V working, this is going to be a component that will be larger than the resistors or the transistor.

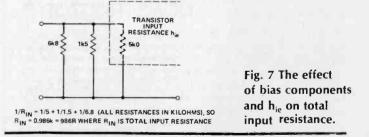

The input resistance of an amplifying stage is, as the name suggests, the ratio of input voltage to input current **ELECTRONICS DIGEST, SPRING 1984**

## IF $h_{ie}$ = INPUT RESISTANCE IN KILOHMS, IC = STEADY COLLECTOR CURRENT IN MILLIAMPS, AND $h_{fe}$ = VALUE OF CURRENT GAIN, THEN $h_{ie} = \frac{h_{fe}}{40.l_C}$

EXAMPLE: IF  $h_{fe} = 400$  AND  $I_C = 1mA$ , THEN  $h_{ie} = \frac{400}{40 \times 1} = 10k$

Fig. 6 Transistor input resistance,  $h_{ie}$ . Note this is for the transistor only, and assumes zero-signal conditions.

for an AC signal at a frequency in the middle of the bandwidth. The input resistance of a transistor is not constant, but if we take the value which it has at the setting of the bias current, with no signal, then this is a reasonable average to take for small signal inputs — small meaning millivolts. The value is calculated as shown in Fig. 6, and it depends on the  $h_{fe}$  value and the bias current. In general, using transistors with high  $h_{fe}$  values operated at low collector currents will give the highest input resistance values for the transistor, but you can usually assume values in the region of 1k0 to 10k.

These are just input resistance figures for the transistor itself, however, and the total input resistance will be affected by the bias components. When we use the potential divider bias circuit, for example, both R1 and R2 (in Fig. 5) are connected between the base and a line which is at 0 V (AC). How so, you ask? Well, as far as AC voltage is concerned, the supply positive line is as much of an earth as the genuine earth line, since they are connected to each other by a whopping great electrolytic in the power supply circuit. Hence all of these bias resistors are in parallel across the base-to-earth path, considerably lowering the input resistance (Fig. 7). If you think that the shunt feedback circuit of Fig. 2 is better then think again, because the collector end of the bias resistor is connected to a voltage which is in antiphase to (and of much greater amplitude than) the base voltage, so it behaves as if its value were R<sub>b</sub>/G connected to earth. G is the voltage gain of the stage, so that if  $R_b = 88k$  and G = 50, then the bias resistor is effectively 1k76 in parallel with the input resistance of the transistor itself.

### Gainful Employment

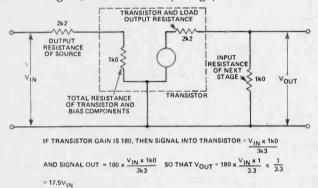

The output resistance of a single transistor amplifier consists of the output resistance of the transistor itself, usually around 30k, in parallel with the load resistor. Since load resistor values are usually of the order of 1k0 to 10k, this in practice means that we can use the load resistor value as the value for output resistance when we are dealing with resistor-capacitor coupled stages.

The crunch comes when we want to find what the gain of an amplifying stage will be. For a silicon transistor which has enough  $h_{le}$  to class it as being in the land of the living, the maximum voltage gain is given by  $40 \times V_{RL}$ , where  $V_{RL}$  is the voltage across the load resistor when no signal is applied — the bias voltage in other words across  $R_L$ . For example, if you are using a transistor with 4V5 across the load resistor, then the maximum gain is  $40 \times 4.5$ , which is 180 times, and that's the value which can be measured if you use a low impedance signal generator, a

5

very small signal amplitude, and a high-impedance oscilloscope to measure the output.

Practical circuits, however, use higher-resistance devices as signal sources and low resistance devices as signal loads, so that the gain when we take into account the potential-dividing effect of all these loss-makers is a lot less. For example, if we imagine our transistor stage to be fed with a signal from another stage with an output resistance of 2k2 and feeding into a stage with input resistance of 1k0 (and with these same values itself) then its gain (Fig. 8) will be a miserable 17.5 times. It's not the gain of the transistor which has fallen, notice; it's the attenuation caused by the potential dividers which is dissipating the signal. The moral is that input and output resistances are important when you are aiming for maximum gain, and that everything you can do to raise

Fig. 8 The effect of input and output resistances in forming potential divider circuits with the internal resistances of source and load.

ECTROVA

THE WISE

CONSTRUCTOR'S

I'ts amazing what you'll find in our current 32 page price list, be you beginner, expert or professional. The list below gives some idea of

the enormous stocks we carry, and our service is just about as good asmeticulouscareandalmost twenty years of experience

> Write, Phone or call for this price and products list now!

Good Bargains

Good choice

can make it.

input resistance and reduce output resistance can be useful.

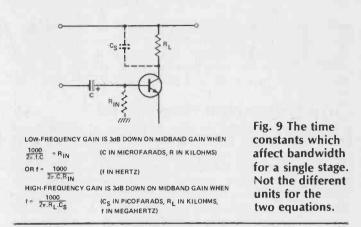

The bandwidth of an amplifier stage is defined as the range of frequencies over which the gain does not drop 3 dB below its mid-band value. For a simple amplifier stage, the limits of bandwidth are set by the time constants of the coupling and emitter-decoupling capacitors at the low frequencies, and by the effects of stray capacitance at the high frequencies - Fig. 9 shows the details. Most modern transistors have good high-frequency gain and since stray capacitance can be made small with modern circuit layouts, frequencies into the many megahertz range can be expected. This is much more than is necessary (or desirable) in many cases, and it's a wise precaution to trim the bandwidth for the purpose you need. This can be done by introducing a time constant into the feedback network of a simple filter.

## ` If an advertisement is wrong we're here to put it right.

If you see an advertisement in the press, in print, on posters or in the cinema which you find unacceptable, write to us at the address below.

## The Advertising Standards Authority.

ASA Ltd, Dept 3 Brook House, Torrington Place, London WC1E 7HN

### Please mention this special E.T.I. publication

February 1984

when applying

'Access' facilities Aerosols **Batteries** Boxes Breadboards Computers & equipmnt. Capacitors

Prompt mail order service Connectors Discounts Electrolytics Ferrites Grommets Hardware I.Cs. Knobs

Lamps Meters Opto-electrncs Quantity prices Quartz crystals Resistors Relays Semi-conductrs

Switches Solder tools Tools Transformers Vero products Visa 'facilities Zener diodes

It's FREE!

ELECTROVALUE LTD. 28 St. Jude's Rd. Englefield Green, Egham, Surrey TW20 0HB. *Phone* — (0784) 33603 Telex: 264475:Northern Shop 680 Burnage Lane, Manchester (Callers Only) EV (061-432 4945) Computing shop 700 Burnage Lane M/c. (061-431 4866).

Our topic this time is twins and triplets. Don't worry, you haven't picked up a copy of 'Mother and Baby' by mistake it's just Ian Sinclair explaining transistor amplifier feedback loops.

ne of the major problems about the straightforward transistor amplifier is the calculation of gain. As we saw last time, the gain of the transistor itself is easily calculated, but if we are to allow for the effect of input and output resistance, we have to know a lot about the particular transistor we are using. The task becomes even more difficult when the amplifier operates at high frequencies, so that we have to deal with input and output impedances rather than with pure resistances.

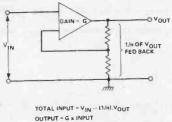

Negative feedback is the main method that we use to get around this problem. To start with, imagine an amplifier whose voltage gain is G — this is sometimes called the 'open loop gain', the gain with no feedback loop connected (Fig. 1). The amplifier has an input connection and a feedback connection, and 1/n of the output signal is fed back to the input. Since the output signal is  $V_{OUT}$ , the amount fed back is  $V_{OUT}/n$ , and so the actual signal available to amplify is  $V_{IN} - V_{OUT}/n$ , the input voltage minus the feedback signal. This is the signal which appears at the inputs of the amplifier to be amplified, so that with gain G, the output from this must be  $V_{OUT} = G(V_{IN} - V_{OUT}/n)$ .

$\label{eq:constraint} \begin{array}{l} \text{Int} & \text{Output} = \text{G} \times \text{INPUT} \\ \text{SO} \mbox{VOUT} = \mbox{G}(V_{IN} - V_{OUT}/n) \\ \text{THUS} \mbox{VOUT} (1 + \mbox{G}/n) = \mbox{G} \cdot V_{IN} \\ \text{AND} \mbox{VOUT} (V_{IN} = \mbox{G}/(1 + \mbox{G}/n) \\ \text{IF} \mbox{G}/n > 1, \mbox{THEN} \mbox{VOUT} / V_{IN} \approx n \end{array}$

Fig. 1 Principle of negative feedback.

### An Open And Closed Case

When we collect terms in this equation and rearrange it to get  $V_{OUT}/V_{IN}$  (which is the gain with the feedback connected), we get this figure as G/(1 + G/n). This is the gainwith-feedback or closed-loop gain, and this is the equation that should be used in calculations if G is small or n is large. If the ratio G/n is large compared with 1, however,

### **ELECTRONICS DIGEST, SPRING 1984**

we can ignore the 1 and rewrite the equation as G/(G/n), which is simply n.

This important result shows that if the open-loop gain is large enough the gain when feedback is used is independent of anything except the potential divider that produces the 1/n of the signal which is fed back. This is the result that is often quoted in textbooks, but with a slightly different proof. One important point is that feedback is useful only if there is gain — if an amplifier has zero gain under certain circumstances, no amount of feedback can produce gain.

### Looking On The Negative Side

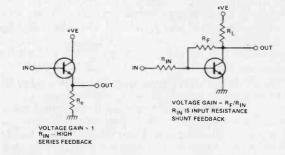

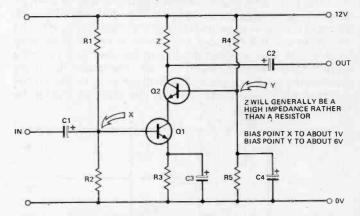

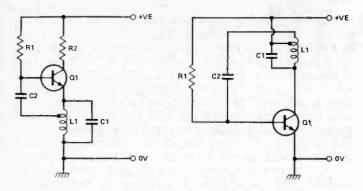

Given that negative feedback can be useful, let's look at some circuits that make use of it. Since gain is important, there's not too much point in spending time looking at single-transistor stages, though both of the circuits in Fig. 2 are important and are widely used. The equations are approximations which apply to silicon transistors; no bias components have been shown.

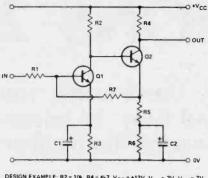

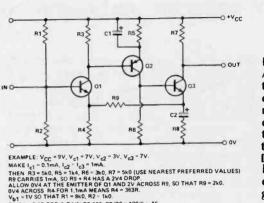

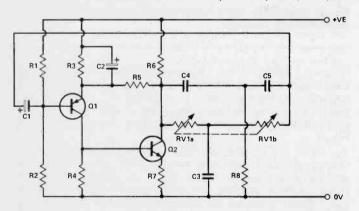

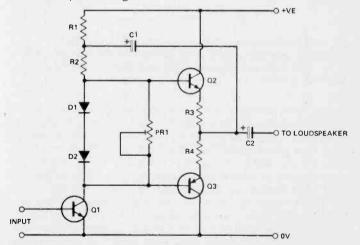

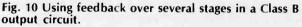

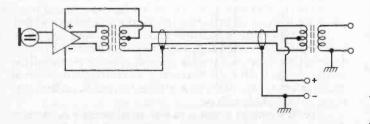

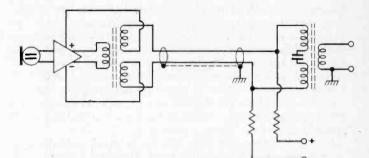

Negative feedback really comes into its own when two or more transistor stages are used, and if the feedback path is a DC one then both gain and bias will be controlled by the feedback. This is seldom completely convenient, so that the basic circuits have to be modified to allow for separating bias and signal feedback paths. One of the most-widely-used of these circuits is the feedback pair circuit of Fig. 3. In this circuit, the transistors are directcoupled, and the negative feedback path is from the emitter of Q2 to the base of Q1. Because of the bypass capacitor C2, there is no signal voltage across R6, and the signal voltage that is fed back is the voltage across R5 only. This value, along with the value of feedback resistor R7, can be chosen to produce the amount of gain that is

Fig. 2 Feedback over a single stage gives rise to these well-known circuits.

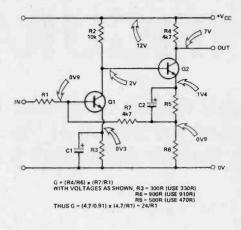

DESIGN EXAMPLE: R2 = 10k, R4 = 4k7, V<sub>CC</sub> = +12V, V<sub>c1</sub> = 2V, V<sub>c2</sub> = 7V. MAKING I<sub>c1</sub> = I<sub>c2</sub> = 1mA, V<sub>g2</sub> = 1V4. CHOOSE R3 = 220R SO THAT V<sub>g1</sub> = 1mA = 0.22 = 0V22 AND V<sub>b1</sub> = 0V82. VOLTAGE ACROSS R7 = 1.4 - 0.82 = 0V54. ASSUME h<sub>g</sub> = 100, THEN 1/100mA F.LOWS THROUGH R7 TO BASE OF 01. VALUE OF R7 MUST B6 0.584/1/1001 - 58k, 2 Fabs SHOULD DO NIGELY! R5 + R6 HAS TO PROVIDE 1V4 AT 1mA = 14. FW = MAK BR = 300R, R6 = 1.00, THEN GAIN = 56/R1 = A70.28 = 675/R1 (R7 MEASURED IN KILOHMS), WE CAN NOW SELECT THE GAIN WE WEED BY SPECIFYING A VALUE OF R1 - WHICH WILL INCLUDE THE OUTPUT RESISTANCE OF THE PREVIOUS STAGE.

### Fig. 3 A two-transistor negative feedback circuit using emitter-to-base feedback.

Fig. 4 A modified feedback circuit which is easier to design sample voltages are shown.

### **Further Feedback**

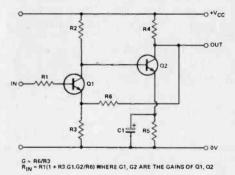

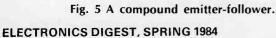

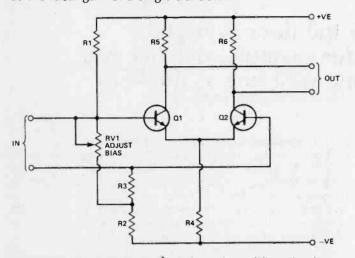

Figure 5 is another direct-coupled two-transistor circuit which uses negative feedback, but this time from the collector of Q2 to the emitter of Q1. As shown the circuit is impractical (because there are no bias components) and a very useful compromise is to combine this circuit for AC

Fig. 5 An alternative twotransistor circuit, using collector-toemitter feedback.

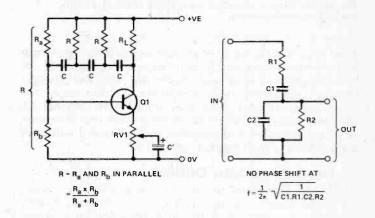

feedback with the previous circuit for DC feedback (Fig. 6). The gain of this example is approximately (R7 + R3)/R3, and the bias is set by the DC network R3, R6, R5. The design procedure is to decide on operating currents and voltage levels as before, calculate load resistor values, and then assuming that  $V_{c2}$  will be 0V6 less than  $V_{c1}$ , find a value for R5. Make R6 a size that will suit its use as an input load (around 4k7) and calculate a value for R3 which will make the emitter voltage of Q1 0V6 less than the emitter voltage of Q2. You can then pick a value for R7 which will give you the gain you want, but remember that R1 (the source resistance of the signal supply stage) will form a potential divider with R6, so that the overall gain will be lower than the calculated gain from the stage.

#### **ELECTRONICS DIGEST, SPRING 1984**

desired; providing of course, that the value is small compared to the open-loop gain which will be the product of the open-loop gain figure for each transistor multiplied by the loss for the potential divider effects of input and output resistances.

#### Getting Good Value(s)

Design of the circuit should start with the load and bias components. The values of the two load resistors R2 and R4 are fixed first; these should be fixed at values which will permit the transistor to operate at suitable currents. Values in the range 1k0 to 12k are usually suitable, though R2 can be in the range 15k to 47k if Q1 is operated at low current to reduce noise signals. If you prefer it, write down the desired collector voltages (Q2 must have a higher collector voltage than Q1) and choose current values, then use Ohm's law to calculate the load resistors.

Once the load resistor values, the currents and the voltage levels have been fixed, the bias components can be calculated. The voltage at the emitter of Q2 will be 0V6 less than the base voltage of Q2, and the voltage at the base of Q1 will be 0V6 higher than the emitter voltage of Q1. Subtracting these gives the voltage across R7, and we then have to pick a value which will allow the correct amount of base current to flow. Once this has been done, we can split the total resistance of R5 and R6 (which has to be calculated to produce the correct bias voltage) so as to allow for enough gain for Q2(R4/R6). We can then choose the total figure of gain by selecting R1, which is the sum of a resistor and the output resistance of the circuit that is providing the signal.

Though this circuit works well, it is never easy to get the bias spot on by calculation unless you know what base current Q2 requires, and the total gain is rather dependent on the source resistance value. The bias problem can be eased by a modification of the circuit shown in Fig. 4, where R7 has a fairly low value, around 4k7, so that the base voltage at Q1 is practically equal to the voltage across R6. This allows the  $h_{fe}$  value of the transistors to be neglected, but the penalty to be paid is that the gain is lower unless R1 is also small.

Fig. 6 Combining feedback systems, using one for DC and the other for AC.

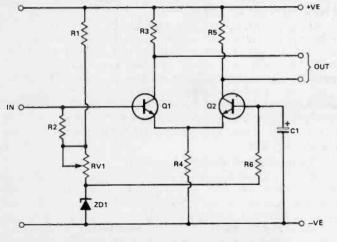

### After Twins, Triplets!

On the basis that negative feedback works best when there is plenty of gain, three-transistor amplifiers should perform better than twins. There's a catch, though, concerned with time constants. Each time constant in a signal path will cause phase shift at one of the extremes of frequency, high or low. Coupling capacitors will cause phase shift at low frequencies, as will emitter decoupling capacitors, and stray capacitances will cause phase shifts at high frequencies — usually beyond the audio limits. This phase shift in each time constant will cause a total phase shift over the whole amplifier circuit that can be quite large and when it approaches 180° your negative feedback is in danger of turning into the opposite type - positive feedback. This converts your amplifier into an oscillator if the gain in the amplifying part is greater than the losses in the time constants at the frequency where the 180° phase shift occurs, Calculations on this are far from simple unless you use a computer (and if you're waiting for the Sinclair QL, then it's quicker to work it out on an abacus anyway). Two useful points are (a) to use direct coupling as far as possible, and (b) if you must use time constants, don't use a set of identical time constants.

### **A Compromising Situation**

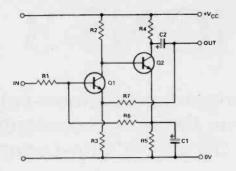

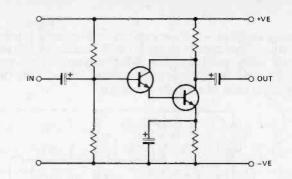

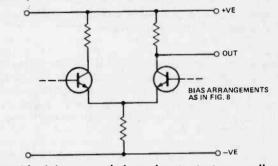

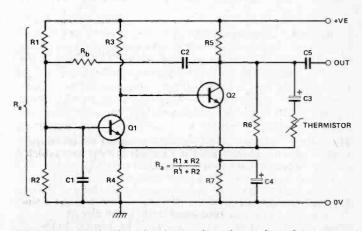

A circuit which can be a useful compromise is shown in Fig. 7. It uses direct coupling, made possible by having a PNP transistor as the intermediate stage, and the negative feedback is used to stabilise the bias as well as the gain. Looking at bias first, the base voltage of Q1 is set by R1 and R2, and the feedback of bias is achieved by passing all the DC current from Q2 through the emitter resistor of Q1. This would cause the AC gain to be very low, but by using R8, which is coupled to the emitter of Q3 through C2, the amount of AC signal at the emitter of Q3 can be reduced, allowing the amount of AC signal fed back to be controlled. The gain of the stage is given by (R7/R8) × (R9/R4).

Design starts as usual with biasing. Assuming, as is reasonable, that the first transistor will be run at a lower current than the others to reduce noise, we can choose current levels of 100 uA for Q1 and 1 mA each for the other two. We can then choose voltage levels, making the

voltage of the collector of Q1 reasonably high, the collector voltage of Q2 reasonably low, and the collector voltage of Q3 about midway between  $V_{cc}$  and the collector voltage of Q2. These figures and our selected currents allow us to calculate values for load resistors and for R5. With this done, we can start to look at R9 and R4. We

have to allocate the total voltage at the emitter of Q3 bet-

R9/R4 = 6 SO FOR A GAIN OF 100, R7/R8 = 100/6 = 16 THUS R8 = 5k0/16 = 300R.

Fig. 7 A threetransistor circuit, making use of a PNP transistor to change DC voltage levels and contribute gain.

ween these resistors, and a ratio of something like 5:1 is reasonable here - the voltage across R9 being about five times as much as the voltage across R4. I've used 6 in the example. Since R9 carries the allocated current of Q3, its value can be calculated right away, and the value of R4, which carries the current of Q1 as well as that of Q3 can be calculated.

The only remaining factor is R8, whose value then decides the total gain. Calculate the gain contribution of R9/R4, and divide this into the total gain required. This latter figure will then be the ratio R7/R8, and since you have already decided on a value for R7, a value of R8 can be calculated, followed by R1 and R2. C1 and C2 should have values which allow the gain to be maintained at the lowest frequencies at which the amplifier will be used, and the time constants R5-C1 and R8-C2 should be quite different.

#### Which Do You Prefer?

Finally, an important point. The resistor values which are obtained by calculation are seldom preferred values, so obviously you have to substitute the nearest preferred values. This is not a major worry, because feedback amplifiers are self-correcting, but there will be one resistor in each circuit whose value sets the gain and which will have to be adjusted – R8 is such a value in Fig 7. The other point which is often raised is - why bother about running Q1 at low current to reduce noise? Since this is a feedback amplifier, the feedback will do a pretty good job of noise reduction anyhow. The answer is that you use negative feedback to stabilise gain and operating conditions. It doesn't make a lousy amplifier into a good one; all it can do is to make a sound design easy to analyse and reliable to mass-produce, so you aim to start with a good amplifier and add negative feedback to it.

## So far we've looked at the common-or-garden common-emitter configuration, but this time we examine the not-so-common common-collector and common-base circuits. It's un-commonly good!

he usual configuration for a transistor amplifier is the common-emitter one that we have used in each circuit so far. A number of useful and interesting circuits, however, are based on the use of commoncollector and common-base configurations, and even more interesting variations can be assembled using two or more transistors in these circuits.

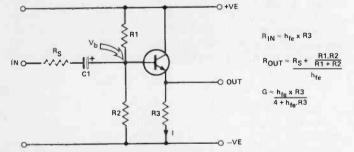

The classic single-transistor common-collector (or emitter follower) circuit is shown in Fig. 1. As shown, this uses two resistors to set the DC base voltage, but these and the input coupling capacitor C1 can usually be dispensed with by using direct coupling (Fig. 2) to the collector of the previous stage when the common collector stage follows another amplifying stage. The design of the circuit is sim-ple; just decide what current, I, that you want to flow in the transistor, and then the value of the emitter resistor R3 (in Fig. 1) is  $(V_b - 0.6)/I$ . The voltage gain is less than 1 (in other words, there is a loss of signal amplitude in the circuit) but the input impedance (resistance, if you're using low frequencies only) is very high and the output im-pedance is very low, which is ideal for a lot of purposes. It's particularly useful, for example, when placed between two common-emitter amplifier stages, because the emitter follower acts as a high resistance load for one amplifier stage and as a very low-resistance supply for the second stage. In this way, it's possible to get more gain from two transistors by adding a stage which causes a loss!

Fig. 1 The straightforward emitter-follower (commoncollector) circuit and bias network.

Fig. 2 Using an emitter-follower with direct-coupling.

### Low Gain Is No Loss

Though the voltage gain of the emitter-follower is less than 1, and can be a lot less than 1 if the emitter resistor has a low value, the stage has a current gain which is about the same as the current gain measured for the transistor operating in common-emitter mode. This makes the emitter-follower a useful driver stage where extra current is needed, but some care is required when the circuit is used with pulses or high-frequency signals. There are inevitably stray capacitances across the emitter resistor, and these will be charged by the current flowing through the transistor when the base voltage goes positive. When the base voltage drops, however, the emitter voltage cannot change at a rate faster than that permitted by the time constant of the emitter load resistor and the stray capacitance, so that the trailing edge of a pulse has a slow fall time. This principle can be deliberately used in a demodulator for AM signals, by connecting a capacitor across the emitter resistor so that the time constant is long compared with the carrier wavetime but short compared with the wavetime of the modulation.

Fig. 3 The effect of stray capacitances on a positive pulse. The emitter-follower cuts off at the negative edge, leaving the stray capacitance to discharge through Re.

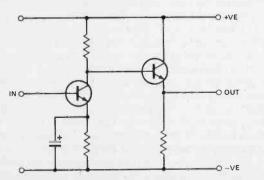

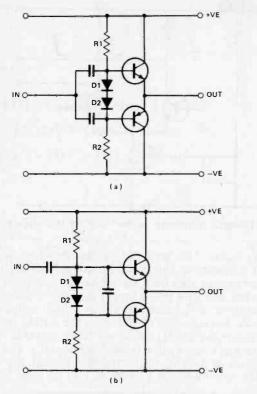

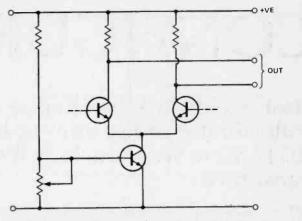

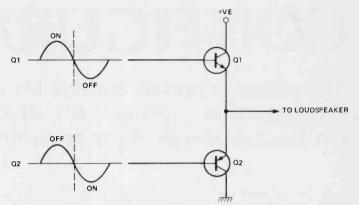

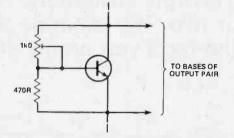

**Doubling Up** If pulses and high-frequency signals have to be used, a double emitter-follower is a better bet. The basic circuit is illustrated in Fig. 4a — it consists of an NPN emitter follower in series with a PNP one. The bias network uses two resistors R1 and R2, both of high value, and the diodes D1 and D2. The values of R1 and R2 have to be equal and large (100k to 2M2) to set the current through the transistors to a suitable value, usually 1 mA to 10 mA. Two parallel coupling capacitors are shown, but an alternative arrangement is a series coupling capacitor arrangement as shown in Fig. 4b. We'll look at this particular configuration in more detail in a later part when we consider power output stages, because it's the basis of most output circuits in transistor amplifiers.

Fig. 4 a and b Two different arrangements of a double emitterfollower, using PNP and NPN transistors.

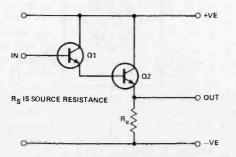

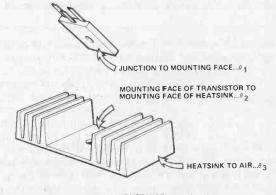

Meantime, take a look at the arrangement of Fig. 5, which is a type of double-emitter-follower. This circuit is often referred to as a Darlington Pair, a name I prefer to reserve for the version of the circuit which uses a load resistor in the collector circuit of both transistors. Bias is arranged in the same way as for a single emitter-follower, but the DC voltage drop between the input and the output is around 1V2, since there are two base-emitter junctions in series. The input resistance is very high, about  $R_e \times h_{fe1} \times h_{fe2}$ , in parallel with the bias components, and the output resistance is very low, about  $R_s/(h_{fe1} \times h_{fe2})$ . The current gain is  $h_{fe1} \times h_{fe2}$ , which is also very large. For example, if we use transistors with  $h_{fe} = 100$  for both stages, then the compound current gain is 10,000, the input resistance with  $R_e = 10k$  is 1M0, and the output resistance when the source resistance is 10k will be 1 ohm! For a lot of applications, Q2 can be a power transistor with a low value of h<sub>fe</sub>, and the circuit can be used to simulate the action of a power transistor with a high  $h_{fe}$  value. The Darlington circuit of Fig. 6 might be expected to have a very high voltage gain, but does not -- there is only one amplifying transistor, and the signal feedback from the collector of Q1 back to its base will reduce the overall gain quite noticeably if the circuit is driven (as it usually is) from a high value of source resistance.

Fig. 6 A Darlington amplifier circuit.

### Transistor Load? That's Cascode

The cascode circuit was one that was familiar to TV service engineers back in the days of valves (remember them?), but its transistor equivalent has never been so widely known, which is rather a pity. A cascode circuit consists of a common-emitter amplifier stage directly coupled to a common-base amplifier stage (Fig. 7). The input resistance is fairly low but the output resistance is very high, which makes the circuit particularly suitable for use with tuned-circuit loads or any other type of load which has a very high impedance. The gain is of about the same value as for a single transistor, but the impedance-transforming action (the reverse of the action of the emitter follower) can be very useful.

Fig. 7 The cascode circuit, which uses a common-emitter stage driving a common-base stage.

### Long-Tailed Pairs Live On!

Of all the two-transistor amplifier circuits, though, the most commonly used is the long-tailed pair, simply because it features so much in linear ICs. The long-tailed pair, a circuit adapted from the days of valves, is a differential amplifier; basically this is an amplifier with two inputs, whose output voltage is proportional to the difference between the signal voltages at the two inputs.

The basic circuit is shown in Fig. 8. The emitters of the transistors are connected, and the bases are biased to about the same DC voltage. The bias is correct when both transistors contribute the same amount of current to the common emitter resistor, and this may need some adjustment unless the transistors are well matched. For ideal action, the value of R4 has to be high, so that large values of R5 and R6 are also needed. A true differential signal at the bases will cause one base voltage to increase as the other decreases, so causing one collector voltage to decrease as the other increases. This creates a large difference signal between the collectors, and ideally the total current through R4 does not change. For a common-mode signal,

11

meaning a signal which is applied in the same phase to both bases, the collector signals will also be in phase so that the differential signal is, ideally, zero. The voltage gain, operated as a differential amplifier, is about the same as the ideal gain of a single transistor.

Fig. 8 The long-tailed pair (or balanced amplifier) circuit. This version is the balanced in, balanced out type.

The long-tailed pair is often used as a way of converting a single-ended input into a differential input for such purposes as driving push-pull circuits. The changes to the circuit to suit this purpose are shown in Fig. 9, illustrating in this case how a zener diode can be used to establish a 'half-supply' voltage level, as an alternative to using balanced power supplies. The voltage gain of the circuit when used in this mode is about the same as that of the differential mode.

BIAS: THE BASE VOLTAGES ARE SET BY THE VALUE OF THE ZENER DIODE. R4 SHOULD BE HIGH (22k OR MORE), AND THIS VALUE WILL SET THE TRANSISTOR CURRENTS I<sub>C1</sub> AND I<sub>C2</sub> SO THAT R4(I<sub>C1</sub> + I<sub>C2</sub>) = V<sub>b</sub> – 0.6. CHOOSE THE VALUES OF R3 AND R5 TO GIVE COLLECTOR VOLTAGE LEVELS MIDWAY BETWEEN THE SUPPLY VOLTAGE AND THE EMITTER VOLTAGE.

Fig. 9 A long-tailed pair used to convert unbalanced signals into balanced.

### **Transistor Tails**

The restriction that affects this type of circuit is the value of the common emitter resistor. Since the value should be high to achieve true differential amplifier action, the currents in both transistors are forced to be small, and this is not always desirable unless the amplifier is used in

Fig. 10 Using a transistor as the 'tail' of the circuit.

an early stage. The way out of the problem is to use another transistor as the emitter load, as indicated in Fig. 10. The currents can then be set to suit whatever values are needed, because this is simply a matter of biasing. The 'tail' transistor will, however, act as a high resistance for AC signals, because this resistance is the output resistance of the common-emitter transistor. This is nearer to the type of differential circuitry that is used in linear ICs, and further refinements of the circuit are possible, though the effort is not really worthwhile if a linear IC can be used instead.

Fig. 11 Obtaining an unbalanced output at one collector.

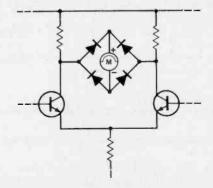

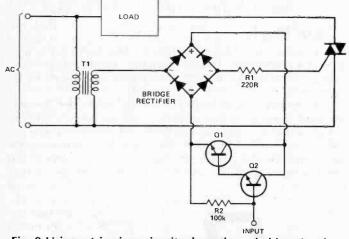

The long-tail pair circuit turns up in all sorts of applications, and one of them is the conversion of differential signals to single-ended output as illustrated in Fig. 11. The gain in this type of circuit is only half as much as can be expected in the differential mode. Another frequently used circuit is the metering circuit of Fig. 12 in which the differential signals at the output of the long-tailed pair are applied to a bridge rectifier and used to drive a meter. No part of the meter circuit is earthed, and zero setting is carried out by adjusting the biasing of the differential amplifier. This is a very useful basis for an AC milliammeter circuit.

Fig. 12 Driving a bridge rectifier circuit.

**ELECTRONICS DIGEST, SPRING 1984**

# Most readers will be familiar with the three types of multivibrator in the form of ICs (for example, the 555 and 4013). Here we show how it's done with just a couple of transistors.

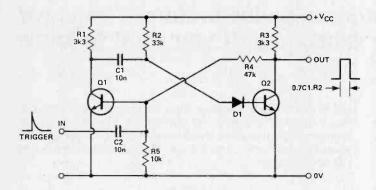

The multivibrator is a circuit of remarkable antiquity — it is attributed to Abrahams and Bloch at around 1918. Over the years, as various valve and subsequently transistor versions were devised, a variety of names were attached to them. However, the names astable, monostable and bistable are particularly useful as descriptions of the various multivibrator circuits.

The astable is a circuit which oscillates continually (no stable state — hence the name), producing steep-sided waveforms whose frequency can be adjusted by changing RC time constants. The monostable has only one stable state, and an input pulse will disturb this state for a time that depends on the time constant of the circuit, following which it returns to the stable waiting state. This circuit is widely used as a pulse generator, because ideally the duration of the pulse (the pulse-width) is independent of the repetition rate of the pulse, which is determined by the rate at which the monostable is triggered. The bistable circuit (two stable states) is the basis of digital circuitry, but is seldom used in discrete form nowadays because of the low cost of digital ICs. A source of confusion over names, incidentally, has been the use of 'flip-flop' by digital circuit designers, whereas the name was traditionally used to mean a monostable.

### **Astable Antics**

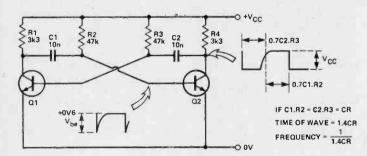

Two varieties of astable exist, the parallel and the serial, of which the parallel is much the better known. The basic circuit is shown in Fig. 1, but unless your needs are

Fig. 1 The simple multivibrator astable, with period formula.

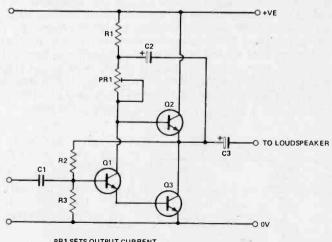

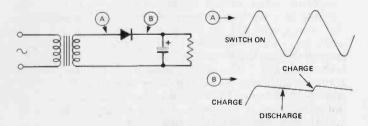

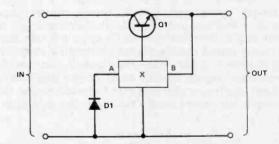

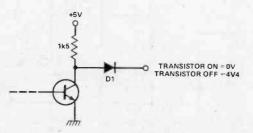

very simple, the waveform from this circuit is not really good enough without reshaping. A much better circuit is shown in Fig. 2; this uses a diode to isolate the collector from which the output is taken. When Q2 cuts off, its col-

### **ELECTRONICS DIGEST, SPRING 1984**

Fig. 2 Using an isolating diode to sharpen the leading edge.

lector voltage can rise sharply, leaving D1 reverse biased. In the simple circuit, a sharp rise of voltage at the collector of Q2 is made impossible by the capacitor C2 which has to be charged through the collector load resistor (R4 in Fig. 1). By using the diode, the collector voltage can rise sharply, and the charging of C2 is done at a slower rate by the additional resistor R5. This ensures a much sharper shape of waveform at the output.

Another problem of the simple circuit is that, contrary to theory, its frequency changes as the supply is changed. This is because silicon planar transistors will conduct readily in the reverse direction when the base voltage is negative with respect to the emitter (for an NPN transistor). This is a form of zener breakdown, but it can be prevented by connecting silicon diodes with a higher reverse breakdown voltage in series with the base leads, as shown in Fig. 3, so greatly improving the frequency stability of the astable.

Fig. 3 Using base-isolating diodes to prevent base-emitter breakdown.

### **Formula For Success**

The astable frequency is given by the formula shown in Fig. 1 — it depends on the two sets of time constants. These should not be greatly different — don't be tempted to try to produce pulses with very large or very small values of mark-to-space ratio by using an astable with very different values of the two time constants. The waveform will probably be disappointing, and the circuit may not start oscillating reliably.

The frequency stability of an astable is generally poor compared with that of the LC type of oscillator, and this feature makes the astable particularly useful inasmuch as it can be easily synchronised to external pulses. Unless the 'natural' frequency of the astable is reasonably close to the incoming frequency, however, synchronisation cannot be relied on, and slowly-changing waves such as sinewaves are not useful for synchronisation because the triggering point is liable to vary (or jitter) from one wave to the next. The astable can be synchronised by pulses at one base, and this can be done by pulsing a cut-off base into conduction or by pulsing a conducting base to cut-off.

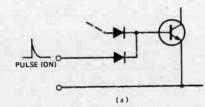

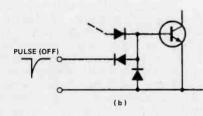

Whichever method is used, the trigger pulse should be isolated from the astable by diodes to prevent the astable interfering with the action of the trigger circuit (Fig. 4). If the 'pulse-off' method is used, a catching diode must be included to prevent the transistor base-emitter junction from being reverse-biased which would cause zener action on each negative pulse.

Fig. 4 Diodes are used in the synchronising circuits, too!

### **Breakfast Serial?**

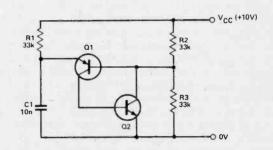

The other type of astable, much less well known, is the serial astable, which is a particularly good way of producing very short pulses which can pack a lot of energy. A circuit is shown in Fig. 5, and since the circuit is not so familiar as that of the parallel astable, a run through its action might be of interest. Note that only one time constant, R1.C1, is used, and that the transistors are complementary; one PNP, one NPN.

We can start by supposing R2 = R3 and  $V_{cc}$  = 10 V, with C1 discharged so that the emitter of Q1 is at a low voltage. Q1 will be cut off, and will stay that way until its base voltage is more negative than its emitter voltage, or to put it another way, until its emitter voltage rises to more than its base voltage. With the base voltage fixed at +5 V by R2 and R3, the capacitor will have to charge to around 5V6 before much will happen.

Meantime, because Q1 cut off, no current is reaching the base of Q2, and this transistor also is cut off. The circuit remains with neither transistor conducting until the charging capacitor reaches the voltage at which Q1 turns on. This also turns on Q2, because the collector current of Q1 goes to the base of Q2. This in turn drastically lowers the base voltage of Q1, and the emitter voltage will follow it, rapidly discharging C1. Once the emitter voltage of Q1 drops, however, the circuit recovers, and we're back where we started.

Unlike the parallel circuit, in which one transistor conducts while the other is cut off, the serial multivibrator spends most of its life with both transistors cut off, and only brief intervals with both turned on. The cut-off time is the time needed to charge C1 through R1 to about 0V6 above the voltage supplied by R2 and R3 — the formula for the time is shown in Fig. 5. The time for which both transistors are on is less easy to estimate because it depends on the effective resistance of the transistors at saturation; it is normally very short compared to the charging time.

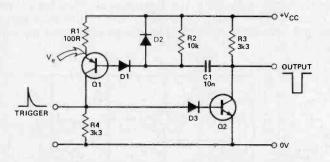

### Monostables

The classic monostable uses a parallel circuit with one DC coupling, as shown in Fig. 6. With no trigger-pulse input, Q2 is held on because of current flowing through R2. The collector voltage of Q2 is very low, and this ensures that Q1 is held off. This is the stable state of the circuit, and it wil remain in this condition, with C1 charged, until a positive-going trigger pulse arrives, with enough amplitude to make Q1 conduct. This pulse causes current to flow in Q1, so that the collector voltage drops, and the drop in voltage at the base of Q2 cuts Q2 off. This condition lasts until C1 charges through R2 sufficiently to turn the base of Q2 on again, when the circuit switches back. The diode in the base lead of Q2 prevents base-emitter breakdown from affecting the timing.

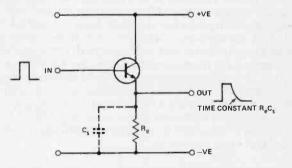

As in all parallel circuits, there is always one transistor conducting and the other cut off. The serial version of the monostable (Fig. 7) uses complementary transistors, and will pass no current in its waiting state. When a trigger pulse arrives, Q2 switches on, and the voltage at its collector drops. This switches on Q1, via the capacitor C1, causing the base circuit of Q2 to be heavily forward biased. C1 now charges through R2 until the voltage at the base of Q1 rises to its cut-off value of around  $V_e$ —0V6. Both transistors then cut off.

The pulse width of the output depends on the time constant of C1.R2, and will vary as the supply voltage varies. Diodes can be used to prevent base-emitter breakdown in the usual way.

Fig. 6 The parallel monostable circuit.

Fig. 7 — A serial monostable — a useful circuit which is seldom seen.

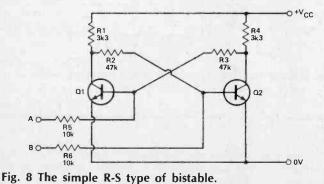

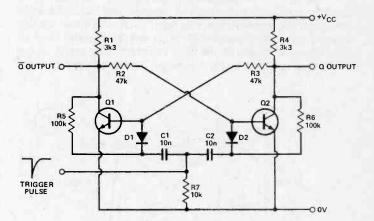

### Bistables, Two By Two

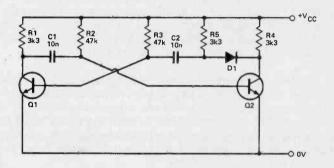

Figure 8 shows the classic bistable circuit using two NPN transistors. The circuit is stable with either Q1 on and Q2 off, or in the alternate condition of Q1 off and Q2 on. Switching is done by using the A or B inputs. With Q1 on, a negative pulse at A will switch the circuit over, and a negative pulse at B will switch it back. This action corresponds to that of the simple set-reset latch.

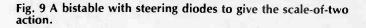

Counting action may be obtained if steering diodes are added to the basic circuit, as illustrated in Fig. 9. Suppose Q1 is conducting: its base voltage will be around

ELECTRONICS DIGEST, SPRING 1984

0V6, and its collector voltage about 0V1, so that D1 is almost conducting. D2 is cut off because its anode voltage will be about zero and its cathode voltage almost at supply voltage. C1 will carry virtually zero charge, while C2 will be charged to around supply voltage,  $V_{cc}$ . When a negative trigger pulse of amplitude around 1 V is applied D1 conducts, allowing Q1 to be cut off by the trigger pulse; however, D2 is held off by the charge on C2. The bistable then changes over so that Q2 is fully conducting and Q1 cut off. In this condition, it is D2 which is biased almost on and D1 completely off. When the next trigger pulse arrives, then, Q2 will be cut off by it, and the circuit will switch back to its original state. Hence, if the circuit is triggered regularly, either output will be a square wave with half the frequency of the trigger pulses.

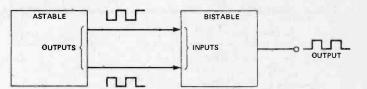

The waveforms at the collectors of a bistable can be much closer to square than those from simple astables, so that one way of creating well shaped square waves is to

Fig. 10 Following an astable with a bistable to sharpen the waveform.

drive a bistable from an astable (Fig. 10). In this circuit, the output from the bistable has the same frequency as the astable. Nowadays, the ready availability of bistables in integrated form discourages us from using the discrete variety — we'll look at IC types later in this series.

# Transistors as amplifiers, transistors as multivibrators — now we consider transistors as sawtooth generators. If you want to know the timebase, ask Ian Sinclair.

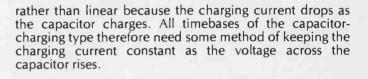

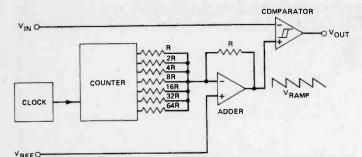

The timebase is a circuit which generates a sawtooth waveform, one whose voltage changes linearly with time: a graph of voltage plotted against time will be as shown in Fig. 1 (though it may be either positive-going or negative-going). The best-known application is in oscillosope timebases, but the circuit can also find use in digital-analogue converters and in timing circuits.

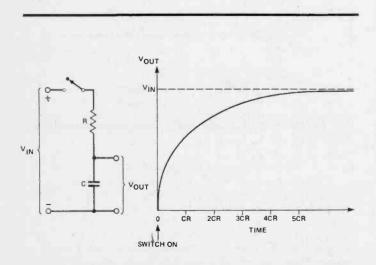

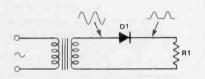

The most simple timing circuit is, of course, a capacitor charging through a resistor (Fig. 2). The time constant CR determines the total charging time which, though theoretically infinite, is in practice about four or five times the length of the time constant. The graph shape of voltage plotted against time is, however, exponential

### **Transistor Control**

In the days of valves, many elaborate circuits were devised to overcome the problem of constant current control, but it took the development of the transistor to come up with a really simple system with good perform-

Fig. 1 The waveform of a perfect timebase — this should be a straight line.

Fig. 2 Capacitor charging. When a capacitor is charged through a resistor the waveform is an exponential rather than a straight line.

Fig. 3 Using a transistor in place of a resistor for capacitor charging. Since the current through the transistor remains constant, the sweep waveform is straight rather than exponential.

Fig. 4 Block diagram of an oscilloscope timebase.

ance. A transistor whose base-emitter junction passes a constant current will also pass a (larger) constant current between its collector and its emitter, and this current can

be maintained up to the level where the collector voltage is less than half a volt different from the emitter voltage.

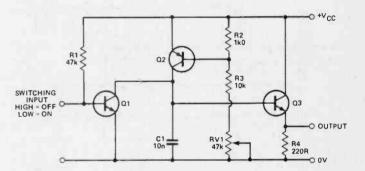

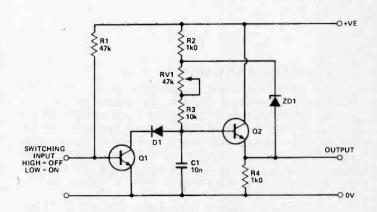

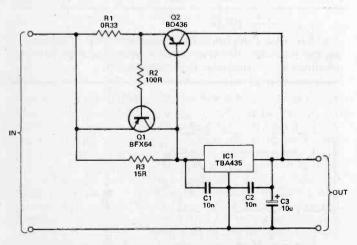

Figure 3 shows a simple timebase circuit using this principle. Q1 is a switching transistor which is normally conducting, keeping the voltage across the capacitor low. Q2 is a PNP transistor whose base current is set by the resistor chain R2, R3, RV1, and which can be varied by altering the value of RV1. Since the base current is constant, the collector current will also be constant. Q3 is simply an emitter-follower to avoid non-linear effects which would be caused by a resistive load connected across the charging capacitor (since a resistance takes more current as the voltage across it is increased). For best results, Q3 should be a transistor with a high h<sub>fe</sub> value, and a double emitter-follower is often preferable to ensure the highest possible input resistance.

The action is as follows. When Q1 is cut off by a negative pulse at its base, capacitor C1 can be charged by current flowing through Q2. This current will not change until the collector voltage of Q2 has reached a value close to the positive supply voltage, so that the wave form is linear up to this region. If Q1 remains cut off, the waveform will then flatten off, but if Q1 is switched on again before this point is reached, then a good sawtooth shape is preserved.

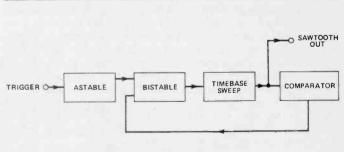

### **Timing The Timebase**

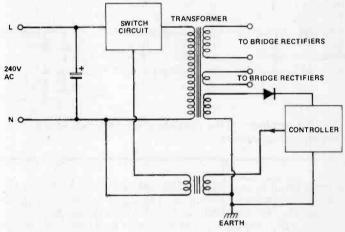

The action depends to a large extent on switching the transistor Q1 at the correct times, and all timebases consist basically of two sections - a square wave generator which handles the switching and a sawtooth generator which provides the desired waveform. An oscilloscope timebase would use a level-detecting circuit at the output to ensure that the switching transistor Q1 was switched off before the voltage level at the output reached the non-linear region — a block diagram with waveforms is shown in Fig. 4. In this arrangement, the repetition rate of the timebase is determined by an astable which provides a trigger pulse. The trigger pulse sets the bistable, which in turn cuts off the switching transistor of the timebase generator and so starts the charging of the capacitor. When the charging has reached some preset voltage level, the level detector (comparator) circuit switches the bistable back, so discharging the capacitor ready for another sweep. For many oscilloscope purposes, the astable is set to run freely at a low speed, and is synchronised to whatever waveform is to be displayed - this is the auto timebase system found on most modern oscilloscopes. The sweep speed is then determined by the time constant of the charging capacitor.

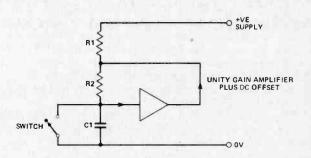

The use of a transistor as a constant current device for a timebase is good enough for many purposes, but two other methods of creating linear sweep waveforms from the basic capacitor charging circuit have been well established for many decades in oscilloscope circuitry. One of these is the bootstrap circuit. Bootstrapping is positive feedback applied over a circuit in which the gain is less than unity, so that it does not cause oscillation.

#### By His Bootstraps

The principle of the bootstrap is shown in Fig. 5. A capacitor is charged through two series resistors, and a unity-gain amplifier is connected so that the voltage across the capacitor can be applied, in phase but with its DC

**ELECTRONICS DIGEST, SPRING 1984**

level shifted, to the point where the resistors join. When the capacitor starts to charge, the increase of voltage across the capacitor causes a matching increase of voltage across R2, so that the voltage across R2 has not changed in this time. Since the voltage across R2 is constant, the current through R2 is also constant, which is the condition for a linear sweep.

Fig. 5 The principle of the bootstrap timebase circuit.

Fig. 6 A practical form of the bootstrap circuit, using an emitter-follower as the unity-gain amplifier.

The bootstrap depends on being able to keep the voltage at the junction of the resistors at a constant amount greater than the voltage across the capacitor. The whole idea seemed so absurd when it was first proposed that the (US) inventor remarked that it seemed "rather like lifting yourself by your own bootstraps". As so often happens, the name stuck.

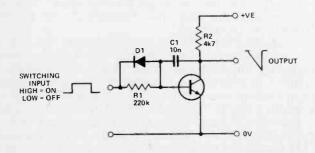

A practical form of the timebase is shown in Fig. 6. Q1 is, as before, the switching transistor which starts and stops the sweep. The charging resistor chain consists of R2, R3 and RV1, of which R3 is a limiting resistor whose value is set so that excessive current does not flow through Q1 when the variable is set at its minimum value. D1 is used to prevent C1 from discharging below about 0V7, so ensuring that Q2 will not switch off, causing non-linearity. If Q2 is allowed to switch off, then the timebase output will have a decided 'kink' at the voltage at which Q2 switches on.

Q2 is an emitter-follower, whose emitter is connected through a zener diode ZD1 to the junction of R2 and R3. The zener diode, along with the base-emitter voltage drop of Q2 determines the voltage across R3 and RV1, so that the charging rate can be calculated. For example, suppose the voltage is 6 V, the values of RV1 and R3 add to 56k and C1 is 22nF. The charging current I is 6/56 mA, which is 0.107 mA, and the rate of change of voltage across C1 is I/C1. Using units of milliamps and nanofarads, the rate of rise of voltage will be in volts/microsecond, and the example gives 0.00486, equivalent to 4.86 volts per millisecond. If you know the sensitivity figure for the cathode ray tube for which the timebase is to be used (in terms of centimetres of deflection per volt), then you can calculate what amount of amplification will be needed to obtain full screen coverage, and what time constants will be needed for the various scan speeds.

There are limitations on the voltage gain of the emitter follower and the frequency range over which the zener diode remains effective, but with suitable choice of components, good timebase circuits can be designed around this core configuration. Commercial circuits of this type often look remarkably complicated, but once the bootstrap section is separated from the other parts of the complete timebase (the triggering and the comparator sections), the essential simplicity of the circuit can be seen.

### **The Miller Alternative**

The other basic capacitor charging circuit is the Miller integrator. These two circuits, the bootstrap and the Miller, were curiously polarised for many years, with the bootstrap used on US equipment and the Miller on UK equipment almost exclusively. This is no longer completely true, but though you will see bootstrap timebases appearing on equipment designed in this country, you will even now seldom see a Miller timebase used on the other side of the pond.

The Miller timebase is named after (yes, got it!) Miller, who discovered the result of negative feedback across the anode-grid capacitance of triode valves. The name became attached to the timebase (which was not designed by Miller) because the Miller timebase makes deliberate use of such feedback to achieve linearity. The basic circuit is shown in Fig. 7, and the most startling thing about it is its simplicity, because the switching transistor is also the current regulator! If we imagine the transistor starting cut-

Fig. 7 The basic Miller timebase circuit.

off, then a square wave applied to the input will raise the base voltage until the transistor starts to conduct. When conduction starts, however, the collector voltage will drop, and the negative feedback through C1 will prevent the base voltage from rising to the level of the input voltage. Once this has happened, the base voltage can rise only as fast as the capacitor C1 can be discharged, and the discharge is at a steady rate because of the negative feedback.

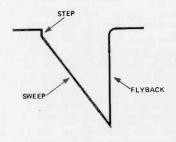

The time constant for the Miller integrator is given by the value of R1 and C1 rather than R2 and C1 as you might expect, and the conventional use of the circuit as shown here produces a timebase waveform which is negativegoing, with a small 'step', as shown in Fig. 8, just at the point where the transistor switches on.

The circuit will operate in the opposite direction, when the 'free' end of R1 is at ground potential. In this case, the voltage at the transistor's collector rises just quickly enough to keep sufficient current flowing into its base (and also R1) to keep it on. In both cases, the simplest way to achieve the fly-back is to connect a diode, D1, in parallel with R1. For operation in the opposite direction from that first described, the direction of the diode must be reversed.

Morè elaborate versions of the Miller use two stages of amplification with the output in phase, and a lowimpedance stage driving the capacitor. Very good results can be obtained, and with a wide-band op-amp used in place of a transistor, excellent timebase linearity is possible.

Fig. 8 The waveform from the simple Miller circuit.

Before we leave the subject, timebases can also make use of the growth of current through an inductor. The effect that is used here is the inductive equivalent of capacitor charging, and it is useful because if the inductor is also a deflection coil for a cathode-ray tube, then the timebase and deflection system can be combined. Linearity is much less easy to achieve, however, and one method is the use of a saturable reactor in series with the inductor which carries out the timebase action. The inductance of a saturable reactor will vary with the amount of voltage across it in order to keep the current constant. Using this and other components, it is possible to balance out the worst of the non-linearity of the charging process. For truly linear timebases, however, the capacitor charging circuits which we have described in this article are considerably superior to inductive timebases. No-one watching TV seems to care too much if the characters are very slightly fatter on the right hand side of the screen than on the left, but we need to know the truth from our oscilloscopes!

#### **ELECTRONICS DIGEST, SPRING 1984**

# And so to op-amps, the most venerable members of the linear IC family. Ian Sinclair traces their ancestors, descendents and lifestyle.

pefore the reason for the name becomes shrouded in The mists of history, perhaps it's just as well to look at the origins. Operational amplifiers were designed for analogue computers, which are machines used for solving mathematical equations. They do so, not by using binary arithmetic as digital computers do, but by connecting up a network of components which represents either a mathematical relation or an equation. In the case of a mathematical relation (eg,  $y = x^2$ ) the circuit will have an input, x, and an output, y, that will vary according to the relationset up and according to the value of x. Equations can be either ordinary (eg,  $x^2 + 4x + 3 = 0$ ) or differential (eg,  $d^2y/dx^2 + x = 0$ ); the circuit will be connected in a loop, and in the case of the ordinary equation it will give an output that represents the solution (or one of the solutions) to the equation. The solution to a differential equation is itself a mathematical relation (in the case of the example given above, y = Asin x + Bcos x), so the circuit will have an input and an output (the coefficients of the equation, A and B, will be determined by the initial values of the circuit voltages, but that takes us a bit beyond the present scope of this article).

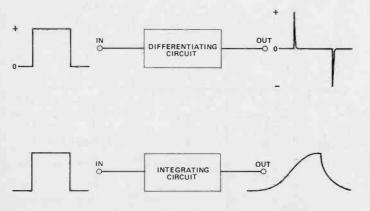

An essential part of representing a mathematical operation in electrical terms is an amplifier with very high gain whose frequency response can be modified by using negative feedback. Typical operations that can be simulated by amplifiers of this sort include the mathematically important ones of differentiation and integration (Fig. 1), and the amplifiers which were designed for these purposes very reasonably became known as operational amplifiers.

Fig. 1 The operations of differentiation and integration performed on a square wave.

### The Perfect Specimen

The specification for a perfect operational amplifier

**ELECTRONICS DIGEST, SPRING 1984**

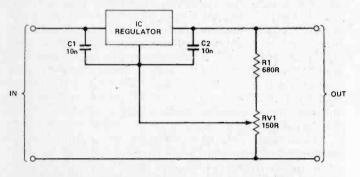

was that it should have infinitely high gain, infinitely high input resistance, zero output resistance, and as much bandwidth as was needed — it was particularly important to have the gain maintained right down to DC. Analogue computers are still produced, though they don't have the importance they once had, and the operational amplifiers which were once made using valves, and then transistors, are now made as ICs. The requirements are still pretty much the same, because our definition of an operational amplifier nowadays is as a high gain DC-coupled amplifier whose behaviour can easily be controlled by using negative feedback. Since the behaviour (gain, bandwidth, shape of gain-bandwidth curve) is so easily modified by the use of negative feedback, the operational amplifier is the nearest thing we have to an all-purpose amplifier, and that's why operational amplifiers were among the first linear ICs that were produced.

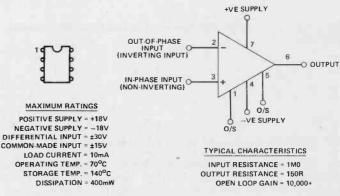

Fig. 2 Part of the specification for the 741 op-amp.

To start with, consider the typical specification of one of the best-known op-amps, the 741. This is illustrated in Fig. 2, to show how close we can get to the ideal specification. One point of importance is the bandwidth. If you use a 741 at its full gain, you must expect the bandwidth to be very severely limited — less than 100 Hz at maximum gain. Some care has to be taken if 741s are used in audio circuits, because in some feedback circuits that include filtering the chip may be working at a very high gain at the ends of the bandwidth, even though its midband gain is low.

#### **Offset Problems**

Getting down to configurations, the main point about op-amp circuits is how to bias them. Very few applications call for the 741 to be operated as a differential DC amplifier at full gain, but for these applications a balanced power supply is needed. Additionally, some form of input offset balancing will be needed. This is necessary because there are bound to be some very small mis-matches between the resistors and transistors that make up the two input circuits (see later). The gain of the op-amp is so high that any imbalance will be amplified up, so that with both inputs tied to zero, the output of the op-amp will not be zero by quite a margin.

Manufacturers usually specify typical and maximum input offset voltage and input offset current. These are the differences between the input voltages and the input currents (with both inputs very close to zero volts) needed to obtain an output voltage of zero. With the 741 and many other op-amps there are offset trim connections that allow you to trim out the voltage offset. A circuit for the 741 is shown in Fig. 3. However, the input currents will still be slightly different, and there may be the odd circuit across the chip is 3 V.

When this configuration is used, the inverting input voltage remains practically constant when a signal is applied. When a balanced power supply is used, in fact, the inverting input is virtually at earth voltage, and this 'virtual earth' effect means that signals applied to the input terminal (one end of R1) are flowing through R1 to a point

Fig. 3 Using the offset adjustment to balance out the internal currents.

for which this will need to be taken into account.

The offset adjustment will have to be repeated at intervals, because the settings *drift*. The effect of temperature and time conspire to make the output voltage change (drift) away from zero, so that an op-amp at full gain is a rather unstable device which needs frequent checking. Fortunately, we seldom need to make use of the full gain of the op-amp, and most of the circuit configurations make use of feedback bias circuits.

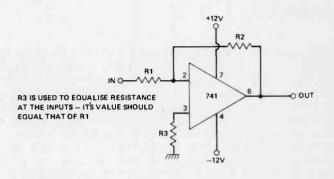

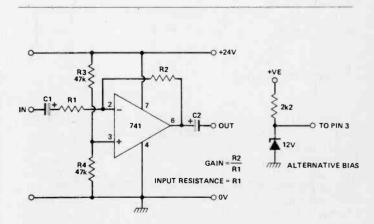

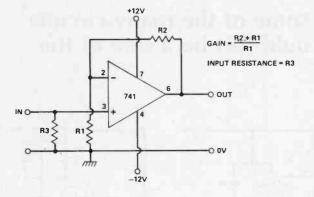

Figure 4 shows one of the most common bias methods. The circuit uses a balanced power supply, and bias is obtained by connecting a resistor between the output and the out-of-phase or inverting input (+) is connected to earth, so that the output voltage will be almost zero, just enough to apply the correct offset voltage (which is usually less than a millivolt) to the inverting input. The gain of this circuit depends on the resistance of the signal source. If we represent this as a resistor in series with the input, R1, then the gain is simply -R2/R1 (the - sign indicates that the signal is inverted).

This circuit is DC-coupled throughout, but if we do not need DC gain, then a single-ended supply version can be constructed, as indicated in Fig. 5. Capacitor coupling must then be used to avoid shorting out the bias voltage, choosing capacitors with low leakage, and the supply voltage must be adequate — the quoted minimum voltage Fig. 4 The feedback bias system in a circuit which uses the out-of-phase, or inverting input for signals.

which is as good as earthed as far as signals are concerned. This makes the input resistance of the circuit equal to the value of R1, and it limits the application of the circuit to some extent, because if the input resistance is to be reasonably high, then the feedback resistor R2 will have to be of an unreasonably high value to achieve a modest gain. If the feedback resistor has too high a value (in the megohm region), then the bias currents at the input of the chip, typically 200 nA, will cause voltage drops which we can't ignore without making our calculations go considerably astray. The input resistance of the op-amp itself is large, but the use of negative feedback to the same

Fig. 5 A single-ended power supply version of the Fig. 4 circuit.

input as the signal makes the input resistance low because of the 'virtual-earth' effect.

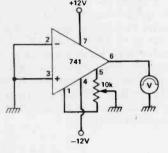

Fig. 6 Using signal input to the in-phase, or non-inverting input of the 741.

### Improved Impedances

Another configuration of the op-amp is illustrated in Fig. 6. This time the input is taken to the non-inverting input, and the inverting input is used only for the feedback. In this balanced version of the circuit, the input resistance can be higher, because the resistance R3 does not control the gain of the amplifier, and the source resistance is of no interest unless it is unusually high. The gain is given by (R2 + R1)/R1.

It's quite straightforward to combine the biasing arrangements of Fig. 5 with the non-inverting circuit of Fig. 6. However, a word of caution: all those resistors and all those capacitors combine to form low-pass filters, and at frequencies around their cut-offs, these will all produce considerable phase-shifts, and this may lead to what you've designed as an amplifer actually turning out to be an oscillator!

### **Slewing About**

The 741 type of operational amplifier has a lot a merits, but it is a design which is now showing its age. Much more recent designs have, in particular, wider bandwidths, and are impressively better in one respect — slew rate. The slew rate of an operational amplifier is the maximum rate-of-change of output voltage expressed in volts per microsecond, and it affects large signals (which change by a greater voltage) more than small signals. The point is that if the maximum rate of change of voltage is 1 V/us, then a 10 V change would need 10 us, and a 10 V signal is limited to one tenth of the bandwidth of a 1 V signal. The effect in practical terms is that the useful bandwidth of the amplifier for sine waves depends on the

#### **ELECTRONICS DIGEST, SPRING 1984**

amplitude of the waves, and the shape of output for a square wave input also depends on the amplitude of the wave.

Slew rate limiting is caused by stray capacitances within the chip. When voltages change, these stray capacitances have to be charged or discharged, and the amount of current which flows in the input stages is very small, not enough to allow these capacitances to be charged or discharged quickly. All amplifiers suffer from this to some extent, but slew rate is much less of a problem for discrete component circuits whose circuits are not DC-coupled and which can therefore use large currents and small values of load resistors. The typical slew rate of the 741 is 0.5 V/uS, and this is rather poor in comparison with more modern designs such as the Motorola MC1741S, which has a slew rate of 15 V/uS.

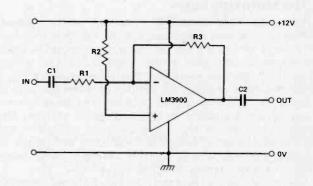

The other feature of the 741 which causes problems is that the peak amplitude of signal output must not be allowed to approach the supply voltage limits, because the internal biasing is no longer effective if this is done. This restriction can be quite irksome if the op-amp is to be used with low voltage single-ended supplies, and an alternative for such applications is the current difference amplifier (CDA), of which the best known example is the National Semiconductor LM3900N. This chip is an operational *current* amplifier whose internal circuitry, though remarkably similar to that of the 741, allows operation at output voltage levels very close to either of the supply voltages.

Fig. 7 A typical LM3900 circuit.

The design principles for CDAs are very different from those used in the 741. The output voltage depends on the difference between the currents at the two inputs, and the circuits that use these chips are distinguished by large resistor values. In the circuit of Fig. 7, for example, if we aim for an output voltage which is half of the supply voltage, then, remembering that the current through R3 must be the same as the current through R2, the value of R3 must be half of the value of R2. Since the input currents are very low, these resistor values have to be high, and values of several megohms are common. The voltage gain in the circuit shown is R3/R1, as for the 741 type of amplifier, but the voltage swing at the output can reach very close to the supply voltage limits. Current difference amplifiers are used mainly in circuits which operate at the lower ranges of frequency because of the effects of stray capacitances on the very large value bias resistors.

This time we turn out attention to some of the many circuits that can be used to make waves: could this be a sine of the times?

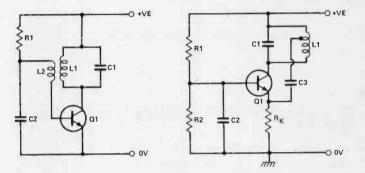

hen you first start to take an interest in circuit configurations, one of the first things that strikes you is the huge variety of sine wave oscillators, many of them known by names that go right back into the mists of time. When you look at these circuits more closely, however, what strikes you is not how different they are but how similar — and that's our starting point for this month.

An oscillator consists of an amplifier with a positive feedback loop and some circuit which has a time constant or is resonant to some frequency. Using this definition, we can include multivibrators among our oscillators, and rightly so, but since we dealt with multivibrators in Configurations Part 4, we'll confine ourselves to sine wave oscillators in this part.

### **The Shrinking Sine**

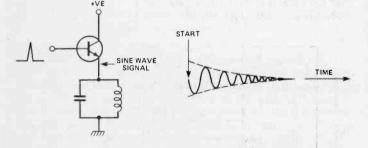

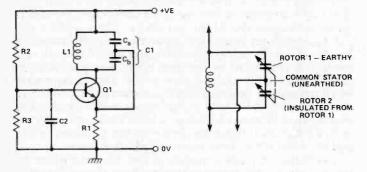

At times, the amplifier portion seems almost superfluous, because a resonant circuit, which is the most familiar way of forcing an oscillator to operate at some fixed frequency and give a sine wave, is a circuit which will, by itself, oscillate quite happily! The circuit of Fig. 1 will, for example, produce an oscillation when the base of the transistor is briefly pulsed positive. The peak emitter voltage of the transistor during this pulse charges the capacitor, and when the transistor cuts off again, the capacitor discharges through the inductor, setting up an oscillating current which in turn causes a sine wave voltage to appear across the circuit.

This wave decays, however, as Fig. 2 shows, because the coil has resistance and any resistance in a circuit will

Fig. 1 (Left)A ringing circuit, using a resonant circuit in the emitter of a transistor which is normally cut off, but which can be pulsed briefly into conduction.

Fig. 2 (Right) The form of the 'ringing' wave — this is a sine wave which decays to zero amplitude. If the circuit resistance is very low, the decay may take a 'long' time, meaning that many cycles of wave will be executed before the amplitude becomes zero.

Fig. 3 (Left) A simple two-winding oscillator. This is easy to construct, but not so easy to adjust for a pure sine wave.

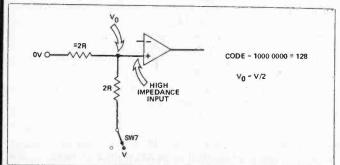

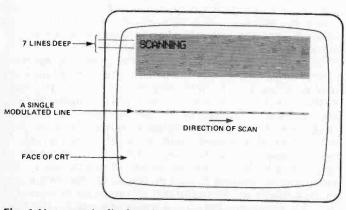

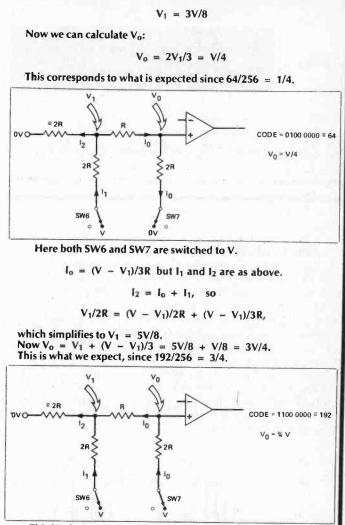

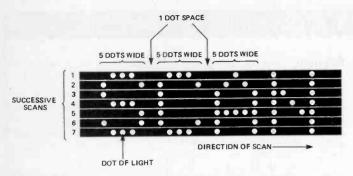

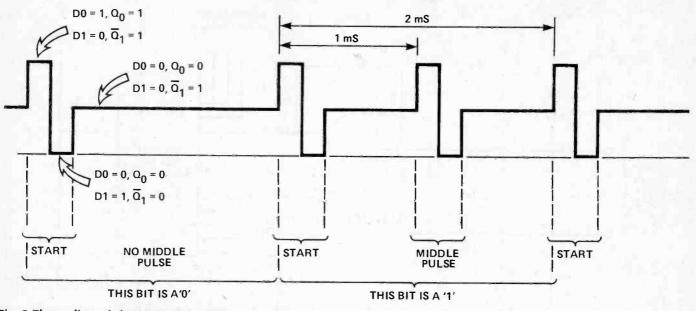

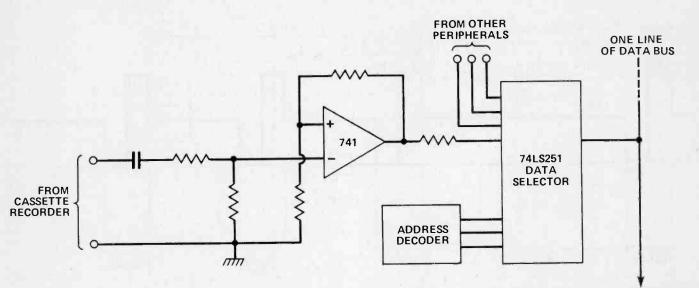

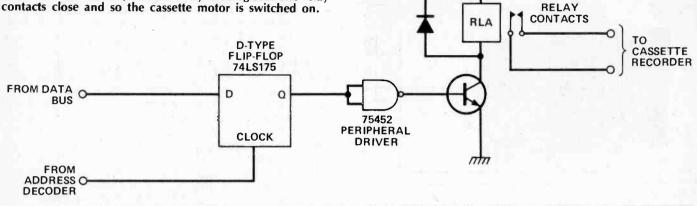

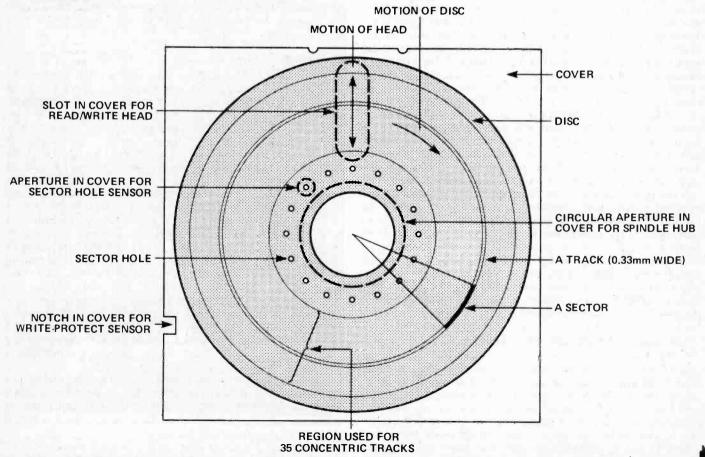

Fig. 4 (Right) The Hartley oscillator in one of its many forms. The positive feedback loop is from the collector circuit to the emitter.