FEBRUARY 1981 65p

**MPU Support** the chips are down Dolby Ca new noise reduction system **IR Beam Alarm project**

NEWS....PROJECTS....M

Ole Je Principality

...AUDIO

Digital design supplement p.51

Put on the pressure p.74

Your finger on the pulse p.46

Feel like a flutter? p.22

#### **FEATURES**

DIGEST

The newest in electronics

MPU SUPPORT CHIPS DOLBY C

Every micro needs them The latest in noise reduction

**MICROBASICS**

Heathkit building

CIRCUIT SUPPLEMENT

Digital design handbook 51 Your ideas in print

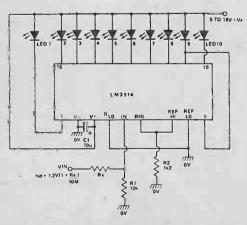

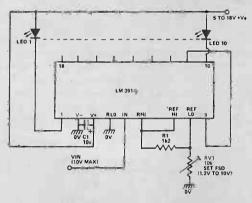

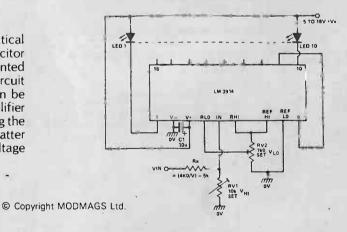

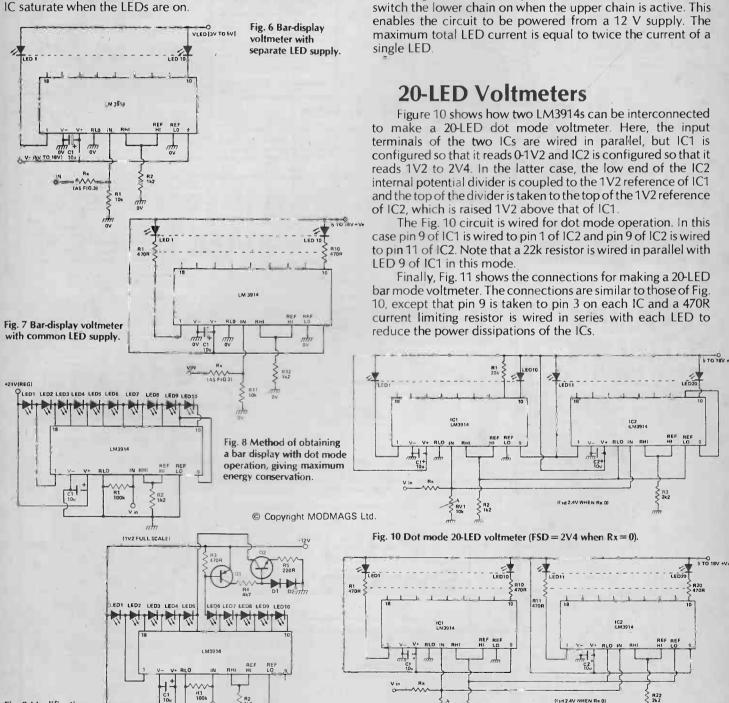

**TECH TIPS** DESIGNER'S NOTEBOOK 81 LM3914 applications

**ASTROLOGUE** 87 News from Saturn

#### **PROJECTS**

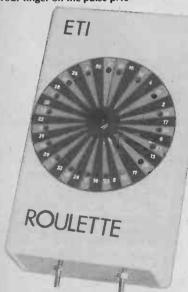

**ROULETTE GAME**

Have a flutter at home

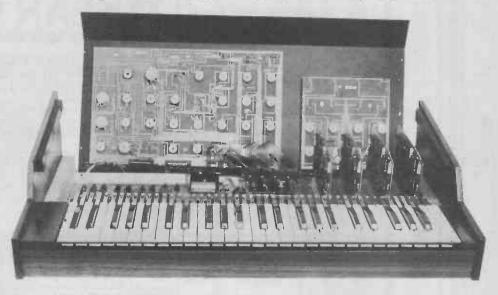

**POLYSYNTH**

32 Voice board building

PULSE GENERATOR INFRA-RED ALARM

Heartbeat synthesiser? 46 62 Burglars beware

SPL METER

Sound Pressure Levelling

FOIL PATTERNS 92 PCBs in print

#### **INFORMATION**

NEXT MONTH'S ETI 13 When the ETIs go Marching In

BOOK SERVICE 91 Out technical library

#### **EDITORIAL AND ADVERTISEMENT OFFICE** 145 Charing Cross Road, London WC2H 0EE. Telephone 01-437 1002/3/4/5

Ron Harris B.Sc. Editor lan Graham B.Sc. Tina Boylan Paul Wilson-Patterson

Assistant Editor Editorial Assistant

**Group Art Editor**

**Drawing Office Manager Project Editor** Paul Edwards Ray Marston

Steven Rowe Advertisement Manager Roy Perryment Advertisement Representative Managing Director

**OVERSEAS EDITIONS** and their

AUSTRALIA - Roger Harrison CANADA - Halvor Moorshead GERMANY - Udo Wittig

**EDITORS**

**HOLLAND** - Anton Kriegsman

Member of the Audit Bureau of Circulation

PUBLISHED BY DISTRIBUTED BY

Modmags Ltd., 145 Charing Cross Road, WC2 Argus Press Sales & Distribution Ltd. 12-18 Paul Street, London (British Isles) Gordon & Gotch Ltd. (Overseas)

PRINTED BY COVERS PRINTED BY

QB Limited, Colchester Alabaster Passmore

Electronics Today is normally published on the first Friday in the month preceding cover date

©MODMAGS LTD 1980 All material is subject to worldwide copyright protection. All reasonable care is taken in the preparation of the magazine contents, but the publishers cannot be held legally responsible for errors. Where mistakes do occur, a correction will normally be published as soon as possible afterwards. All prices and data contained in advertisements are accepted by usin good faith as correct at time of going to press. Neither the advertisers nor the publishers can be held responsible, however, for any vanations affecting price or availability which may occur after the publication has closed for press. Subscription Rates: UK £11 including postage Airmail and other rates upon application to ETI Subscriptions Service, PO Box 35, Bndge Street, Hernel Hempstead, Herts.

## DIGEST

We devoted a section of the Modmags stand to working projects like Space Invasion games and synthesisers.

#### **Breadboard 80**

Held as usual at the Royal Horticultural Society's New Hall, Breadboard once again proved to be a great success. By lunch-time on the opening day more people had arrived than on the whole of the first day last year. Our celebrity guest was Brian Rix, star of the Whitehall farces, and of course, famous (or infamous) for dropping his trousers, which, we are grateful to say, he did not do at Breadboard 80! The attractions were numerous — suppliers of components, home and business computers, CB accessories, space invasion games, hi-fi and disco

equipment as well as all the leading electronics magazines to name but a few. The Modmags stand (that's us folks!) was the undisputed star attraction(?) mobbed by huge crowds. We presume this was because our staff were so helpful and pleasant but there is a sneaking suspicion that it might have had something to do with the two space invasion games we were displaying, offering free games to all, with the opportunity of winning your

own with the highest recorded score. Ah well... The show was certainly the electronics enthusiast's idea of paradise with every conceivable electronic noise pounding the ears and millions of devices to delight the eyes. If you weren't there this year to see it all, don't miss next year. Make a note in your new diary for November the 11th to 15th for Breadboard '81, it'll be better than ever, definitely not to be missed!

Some lucky visitors left the exhibition better off than when they arrived. Here, John Barnes collects his prize from Mike Humphrey of Vero Electronics.

## Popular Electronics

The latest offering from Bernard Babani (Publishing) is a collection of no less than 73 circuits in 149 pages, covering the broad topics of audio, radio, test gear, music and household projects. Each circuit in Popular Electronics Circuit Book 1 by R.A. Penfold is explained in detail. The circuit diagrams are clear and IC/ transistor pinouts are given, so you don't have to wade through a data book before you start construction.

As the preface explains, the book is intended for readers with some experience of electronic construction and who can, therefore, work from a circuit diagram only. However, most of the designs are very simple and shouldn't pose any problems. Where necessary, setting up procedures are given

Popular Electronic Circuits Book 1 by R.A. Penfold is £1.95 from most component dealers and mail order suppliers. If you can't get hold of a copy, write direct to Bernard Babani (Publishing) Ltd, The Grampians, Shepherds Bush Road, London W6 7NF enclosing the price of the book plus postage.

## OOPS SW Converter

Please note that in the Spot Design for the Short Wave Converter (November 1980), it is the two 365pF tuning capacitors that should be ganged — the 50pF trimmer is separate.

#### **Time Control**

Smiths Industries Time Controls have recently launched a massive advertising campaign for their range of time switch products. This is the biggest advertising campaign ever undertaken by S.I. Time Controls. The theme of the campaign is 'make the most of your time' and is designed to illustrate the convenience and economy that can be provided by the time control devices, particularly in the home. As part of the advertising support, the London Underground will carry posters, these being ideally suited to explaining the advantages of the products to commuters who perhaps in their rush to get to work have left their immersion heaters/radiators/lights on all day by mistake. For further details on Smiths Time Controls contact: Smiths Industries Time Controls, Waterloo Road, Cricklewood, London NW2 7UR.

#### **Aquiline Logic**

Two new logic probes from Eagle International join the digital test gear market. The ELP 150 and the ELP 200 can operate from a supply of 5-15 V, so the equipment under test can likely power the probes. The logic level is shown by a red LED (logic 1) or a green LED (logic 0).

The more versatile ELP 200 also has a pulse stretcher to detect high speed switching (indicated by ½ S LED flashes) and a memory to detect infrequent signals without constant observation (shown by permanent LED illumination).

Both probes are TTL and CMOS compatible, have overload and reverse polarity protection and are covered by Eagle's two year guarantee. For further information on the ELP 150 and ELP 200, contact Eagle International, Precision Centre, Heather Park Drive, Wembley, Middlesex HAO 15U.

#### Invasion!

On our stand at Breadboard this year we had two of our Space Invasion machines on show, supplying free games to all comers, with the added bonus of winning your own machine for the highest recorded score. Needless to say, the competition was very hot! The overall winner was Mr A Weircigroth of North London. The show proved how tough our machines are. They stood up well to five ten-hour days, and only once after a bashing did one of the machines suddenly decide to give an unlimited number of bases for a short time during one of the days. Ah well, Space Invasion is a very emotive sort of game, the losers have to take it out on something! Anyway, great fun was had by all, and congrats to the winner!

Computer Pandas

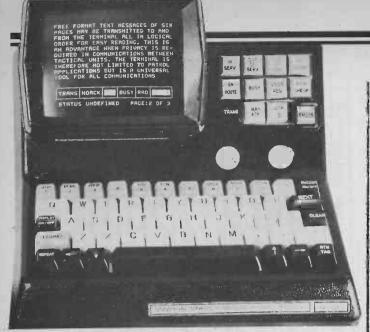

lext time you put the wind up the local Bobbies — beware — the glassy-eyed passenger could be staring at Plessey's new Universal Mobile Communications Terminal (UMCT). It's a dashboard-mounted keyboard and VDU that allows transmission of digital data and computer information retrieval over speech band radio from all types of vehicles. Units are already in use in Canada and the US and are undergoing field trials in Sweden.

A UMCT operator can transmit data at 4800 bits per second, so that a

full screen of 315 characters can be tansmitted in 0.6 S. 300 stations (vehicles) can, therefore, comfortably operate on one radio channel. The system features unique authorisation, automatic re-transmission, memory storage, graphic transmission and elaborate emergency facilities.

Information including road maps, car registration details, etc. can be accessed from a central data base in as little as 2 S. As the UMCT doesn't need any extra black boxes and is connected to the vehicle by only two leads (power and radio), it can be transferred from vehicle to vehicle in a matter of seconds. If necessary, it can even be plugged into the car cigarette lighter!

#### Cruising

EnviroSystems are now supplying what they claim to be the world's first 100% electronic cruise control system. Cruise controls aren't new, but existing units require adaptor kits for each make and model of car and fitting usually involves cutting into the vacuum line to the vacuum servo unit.

EnviroSystems' Cruise Sentry uses a small electric servo unit to accurately control the throttle (no cutting into the vacuum line) and picks up speed-related pulses from the coil. The unit is suitable for most

vehicles (4/6/8 cylinder, standard or electronic ignition), doesn't need fine tuning, is virtually maintenance free and can be fitted in about two hours.

Cruise Sentry can be set to keep your car at a constant speed, but it can be easily over-ridden in one of three ways for safety. If you need to accelerate for any reason, Cruise Sentry will automatically resume the present speed. The preset speed value can be changed while driving without disengaging the system.

Cruise Sentry is available directly from EnviroSystems Ltd, Hampsfell Road, Grange-over-Sands, Cumbria LA11 6BE. The recommended retail price is £78.50 + VAT.

## The Numbers Game

Casio calculators have done a lot of things in their time. Between showing the time, waking you up when it's time to go home and playing tunes, they've even been known to tot up a few digits quicker than you can pull out your slide rule. A slide rule is an antique calaculating device (for those of you too young to remember). This Casio, the MG770, calculates (eight digits capacity with independent memory and perfect percent), plays a 30 S pre-programmed chunk of 'When the saints go marching in', plays any melody you care to hammer into it (in music mode

the keys sound 11 notes) and plays an electronic combat game.

Throw the mode switch over to the game position and hit the game button. A series of random numbers move across the display. Use your aim button to match your defender with the intruder and daintily tread on the fire button to wreak murder and mayhem. The game gets faster until it's all a blur and it displays your score after ever game.

after evey game.

The MG770 is credit-card size (85 x 54 mm), but if you prefer something a bit bigger, the MG880 has all the same features in a wallet-size case (114 x 68 mm). Both are supplied with a leatherette case. Prices? The MG770 should cross the counter for less than Casio's RRP of £14.95 and the MG880 for less than £12.95.

# power 1025 LC crystal disp memory, so balance eve lt's power alkaline bat than other calculator procession of the calculator process

## Mini Printout

The new Hanimex Mini 1025LC produces a printed record of your calculations faster than a large desktop machine, using a new Seiko high speed, low power drain print head. The 1025 LC feature a 10 digit liquid crystal display with a non-volatile memory, so it remembers your bank balance even when it's switched off. It's powered from four size AA alkaline batteries, which last longer than other print and display calculator power units because of the Seiko print head.

## MPU SUPPORT CHIPS

There's no shortage of technical tomes on microprocessors, but there is a distinct dirth of texts on chips that make the MPU do its stuff. Ian Sinclair comes to the rescue.

he first essential for a microprocessor is a clock pulse generator. A clock pulse is simply a rectangular pulse which repeats at a high frequency, usually 1 MHz or more. All microprocessors need clock pulses, because each operation within a microprocessor is triggered by a clock pulse, so no clock pulse — no action. Each little piece of a program will take a definite number of clock pulses to carry out.

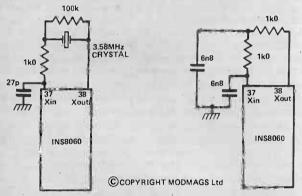

How do we generate clock pulses? A few microprocessors, notably the much-loved INS8060 (SC/MP Mk. II) used in the Science of Cambridge Mk. 14 kit, can generate their own clock pulses. The INS8060 has two terminals which can be connected to external components as shown in Fig. 1. Either RC or crystal oscillator circuits can be used, providing the frequency is fairly high — the internal circuits simply won't oscillate if the time constants are too large. Keep to the values suggested by the manufacturer and you should have no problems.

Fig. 1 Using a built-in oscillator — the INS8060 (SCMP II) can use its built-in oscillator along with a crystal or a simple R-C network.

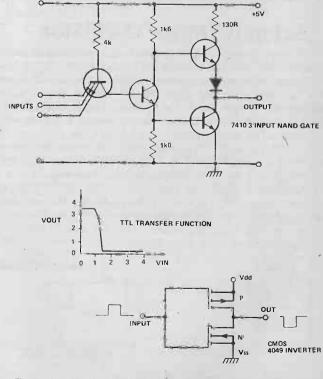

#### **Phase Relations**

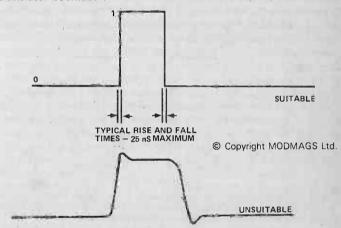

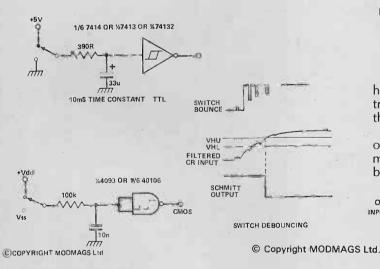

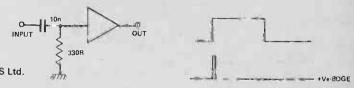

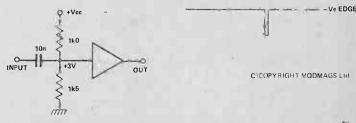

Most microprocessors, however, can't spare the extra pin for connections to a built-in oscillator and instead use only a single pin or a pair of pins for clock pulses. When a single pin input is used, the clock is a single phase clock (a straightforward oscillator). This can be obtained from a multivibrator or by squaring the output of a sinewave oscillator, but it's very important that the waveform should be steep-sided (Fig. 2). If you use a waveform which has long rise or fall times, so that its sides appear to slope when you view the waveform on the oscilloscope, then you'll have trouble when you try to use the microprocessor. The reason is that some gate circuits will oscillate if they are switched over too slowly and that can cause chaos. Don't be tempted to economise on circuits, therefore.

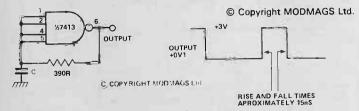

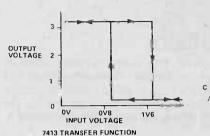

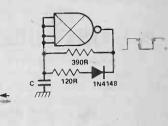

One particularly useful way of ensuring that all signals

entering the microprocessor have short rise and fall times is to use a type of TTL IC called a Schmitt trigger. Typical of these are the 74LS13 quad two input Schmitt NAND. Each of these chips has a Schmitt trigger built in, so the output will always be steep-sided even if the input is not. It's often easier to use a cheap 'n' simple oscillator and a Schmitt IC than to build an elaborate transistor oscillator.

Fig. 2 Clock-pulse shapes. Most discrete-transistor oscillators and certainly all linear IC oscillators (such as 555) cannot generate sufficiently steep-sided clock pulses when driving a capacitive load. A TTL pulse generator is ideal, or a generator which is buffered by a Schmitt inverter, such as the 74LS14.

#### **Refreshment Is Served**

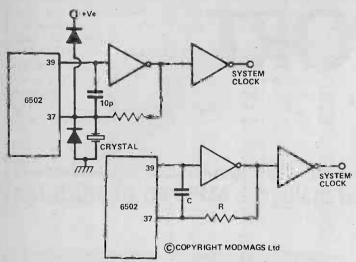

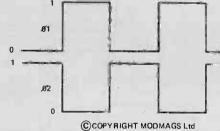

Several types of microprocessors, notably the 6800 and 6502, use two pins for the clock input. This is because the clock pulses have to be two-phase. One pin is being pulsed positive at a time when the other pin is at logic 0. Just to give one example, the 6800 carries out only internal actions on the second phase of its clock, so that during that phase all oututs are isolated. This means that you can run a low-cost memory system using dynamic RAM. Dynamic RAM needs refresh pulses and these can be delivered during the second phase of the clock pulse, when the memories are not connected to the microprocessor in any case.

#### **Buffers**

Buffers are the next group of ICs which have to be used in practically all microprocessor circuits. A buffer is basically an amplifier circuit with a three state output — explanation coming up. There are two reasons for using buffers. One is that microprocessor circuits use PMOS, NMOS or CMOS circuits,

Fig. 3 The clock-pulse generator of the 6502. Either a crystal or R-C circuit can be used, but the external inverters are necessary, though they need not be Schmitt types.

which can't sink or source much current, usually a couple of milliamps at the most. A lot of the circuits which will be connected to the microprocessor will need quite a bit more current, so a buffer is needed — a current amplifier which can be comfortably driven by the microprocessor and which will sink or source enough current at its output to drive a lot more circuitry.

Fig. 4 Two-phase clocks. Where a two-phase clock is used, different actions are carried out in the two different phases. The sketch cannot show the correct scale; there is no overlay between the two positive phases.

INPUT SIGNAL FROM MICROPROCESSOR -CAPABLE OF DRIVING ONE TTL GATE OUTPUT SIGNAL FROM BUFFER-CAPABLE OF DRIVING 10 TTL GATES

Fig. 5 Buffers, inverting and non-inverting. The MOS circuits of most microprocessors cannot provide enough current drive to activate more than one standard TTL gate and a buffer must be fitted between the MOS microprocessor and the TTL circuits if expansion is contemplated.

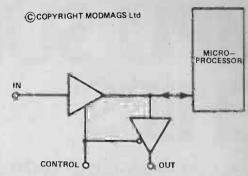

Buffers can also be used as switches. To take one example, the eight data lines of a microprocessor are used for feeding bits in and out. Since they can't do both at the same time, we need some method of switching so that input circuits are not connected at a time when the microprocessor is putting bits out on the data lines. This is another job for the buffer — in this case a three-state type of buffer.

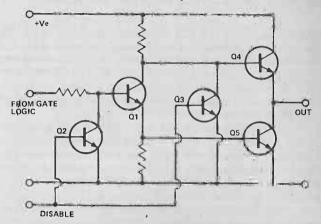

The term three-state sometimes causes a bit of confusion. It means simply that the output of the buffer amplifier can be 0, 1 or isolated from all other circuits. In the type of output circuit shown in Fig. 7, for example, the output can be floated by connecting both the bases of the output pair to earth. This needs extra circuitry inside the IC and an extra 'state' pin on the package, but the advantages of having the floating state are enormous.

Fig. 6 Using three-state buffers. In this example, when the control signal is at logic 1, the input buffer is enabled and the output disabled. With the control signal at logic 0, the output buffer is enabled and the input disabled. The output of the disabled buffer acts like an open-circuit.

Fig. 7 A simplified form of three-state control. The normal gate output circuit consists of Q1, 4 and 5. When the disable pin is high, Q2 and Q3 conduct, shorting the bases of Q1 and Q4, so that both transistors are cut off. This isolates the output completely.

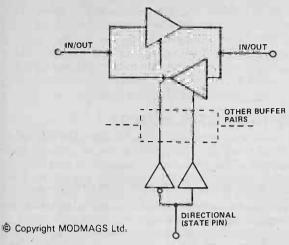

Buffers may be used unidirectionally or bidirectionally. A unidirectional buffer deals with the flow of signals in one direction only, perhaps from an input circuit to the data lines. Most of these are made in two versions, the difference being in the polarity of the three-state control pin. For example, one buffer may go open circuit at the output for a 1 at the three-state control pin and another type may go open circuit for a 0 at the control pin. When the buffer is being used unidirectionally, it's purely a matter of convenience which type is used. For example, if the buffer is used to connect input signals to the data lines and the microprocessor puts out a negative pulse at the time when it is ready to take in such information, then a buffer which is open circuit on a 1 signal and operates for a 0 signal at the state pin is ideal. If the other type of buffer is used, an inverter will need to be incorporated in the control line.

Much more common is bidirectional buffering, where a buffer amplifier is needed for both inputs and outputs. One single buffer can't do this, so a very common method is to use two lots. One lot is isolated by a 1Lon its state pin, the other by a 0 on its state pin, so that the outputs of one set of buffers can be connected safely to the inputs of the other set as shown in Fig. 8 with the state pins connected together. In this way, the combined buffers conduct one way when the state pin is at 1 and the other way when the state pin is at 0.

#### Ah Yes, I Remember It Well

Most books on microprocessors assume that the readers know all about memory ICs. Assuming that you don't, point number one is that we make use of two types of memory systems, ROM and RAM. You can get bits out of ROM (Read

### **FEATURE: MPU Support Chips**

Fig. 8 The bidirectional buffer. The buffer stages are connected input-tooutput with the enable lines driven so that the two buffers of a pair cannot be enabled at the same time. This arrangement is sometimes described as a 'transceiver'— an example is the quad transceiver 74LS243. An octal buffer such as the 74LS241 can also be used in this way by connecting the enable inputs together.

Only Memory) but you can't, in normal operation, put any bits in. ROM is used for 'non-volatile memory', so that the data bits are still stored even when the whole system is switched off.

RAM (Random Access Memory) is misnamed, because practically all the memory ICs we use have random access, meaning that we can get at any one set of bits in the memory without having to sort through all the others.

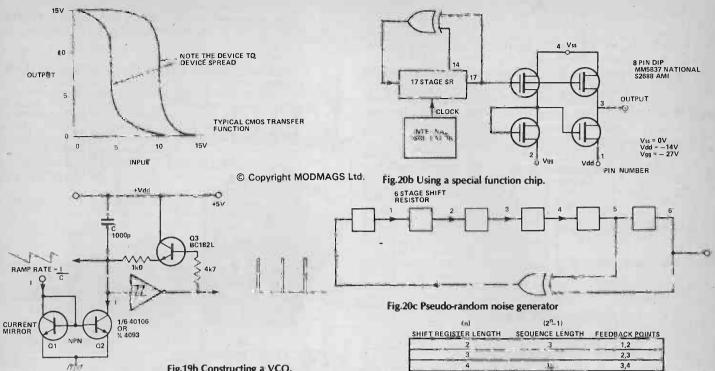

There are several different types of technology which are used to make these memory chips, but the two important varieties are the two types of RAM (static and dynamic). Static RAMs are based on flip-flops (bipolar or MOS which will flip over one way or the other when set or reset by an input. Dynamic RAMs are based on storage of charge in capacitors and this charge is called 'refreshing'. A dynamic memory is refreshed by applying a refresh pulse to each memory cell which stores a 1.

#### **Organisation**

Apart from the question of whether to use static or dynamic RAM, the main factor we need to take into account when dealing with memory is the way in which the memory is organised. Organisation in this sense means the way in which the memory cells are grouped. For example, one very popular way of organising memory is to have 1024 cells, each using a single common data input/output pin. This is classed as a 1K x 1 memory, the 1K (K in memory size means  $2^{10}$  (1024), not 1000) referring to the total number of groups of memory cells and the 1 meaning the number of data lines. A memory like this would (normally) need ten address lines (because  $1024 = 2^{10}$ ) so that 1024 different address numbers can be coded in binary on the lines.

A 512 x 4 memory, on the other hand, would have 512 groups of four cells each, with four data pins for input and output signals. With only 512 groups, only nine address lines are needed ( $2^9 = 512$ ), but at each address number, four bits are being written or read. The total number of bits stored in such a memory is 2048 ( $512 \times 4$ ).

#### **Chip-Ability**

An essential feature of all memory types is a chip-enable pin. At one logic voltage on the chip-enable, the memory can be used for reading or writing in the usual way, but with the chip-enable shut off, the memory data pins go 'floating' as if a three-state buffer were in circuit. This saves using an additional buffer chip and enables us to use large numbers of memories connected together without any other form of buffering.

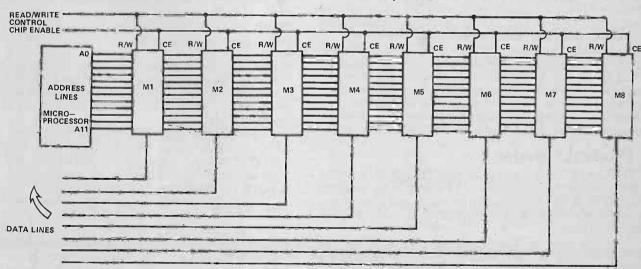

How, then, do we connect memory chips to the main microprocessor (or CPU) unit? There's no simple answer, because it depends on how the memory chips are organised. Take, for example, the use of  $4K \times 1$  chips. Each chip will pEovide one bit of data, so that we need eight chips to give a complete byte of memory data, 4K in this example. The data connections are simple, each data line from the CPU goes to a different memory chip. The memory lines are equally easy. 4K is 212, so that twelve address lines of the microprocessor are connected to all twelve address pins on each memory unit (Fig. 9). This would be the normal layout for a medium sized system using the INS8060, for example, which has only twelve address lines' other microprocessors which use 16 address lines would have four address lines left spare. The lines which are left spare are, of course, the higher order address lines numbered A12 to A15 (they start at AO, so the twelfth line is A11), because the lower order ones are the first to be connected.

The shape of the circuit board would have to be rather

Fig. 9 Using single-bit memory chips. Eight chips are needed to form a memory bank and the read/write and chip-enable signals for each chip must be taken from the microprocessor — they will probably need to be buffered.

© Copyright MODMAGS Ltd.

## FEATURE: MPU Support Chips

different if we were using, say 2K x 4 memories. Each memory chip would have four data pins, so that a complete data byte would need only two chips, and with only 2K to address, only 11 address lines would be needed. On the other hand, had we used 1K x 8, a single memory chip would be connected to all eight data lines and 10 of the address lines.

That's simple enough, but suppose we wanted more memory than could be supplied by a single band of memory ICs? We might, for example, find that 2K of memory obtained from two of the 2K x 4 chips was insufficient and that we needed another 2K. How do we cope with the extra? The answer is that we use one lot (two of 2K x 4) for the first 2K of memory addresses and the other lot for the second 2K of memory — but how? When we have two identical lots of memory chips they will all use the same address lines and the same data lines. In our example using 2K x 4 chips, we want to use the first two chips for the first 2K of memory and the second two for the next 2K. Each chip, being a 2K chip has 11 address lines and four data lines, and all the address lines will be parallelled. In other words, the A0 pin of each chip is joined and connected to the A0 pin on the CPU, the A1 pins of the RAM are similarly connected to the A1 pin of the CPU and so on. The data pins 0 to 3 of chips 1 and 3 are connected to data pins D0 to D3 of the CPU and the data pins 0 to 3 of chips 2 and 4 are connected to data pins D4 to D7 of the CPU.

**Bits Of Memory**

If these were the only connections, we wouldn't have a workable system, because a given address, say 10010110110, would fetch data from (assuming that we're reading memory) both lots of chips and something would end up frying tonight. 'Address decoding' solves the problem. The simplest method is linear address decoding. The highest address for chips 1 and 2 is 11111111111. The next number above this is 100000000000. The lower address lines are now all at 0, so that both lots of memories 1 and 2 along with 3 and 4 are fetching from address 0.

This is where the chip-enable pin comes into the picture. Suppose line A11 is connected to the chip-enable pin of memory chips 1 and 2, and an inverter, whose output is connected to the chip-enable pins of memory chips 3 and 4.

Consider what happens if the chip-enable is active, allowing the chip to operate, when it is at zero. Addresses 0000 up to 07FF (that's all zeros up to all 1s) will be fetched from chips 1 and 2 only, because line A11 is low, activating the chip-enable of those two chips. Because of the inverter, the chip-enable of memory chips 3 and 4 is high, putting their data outputs into the floating state. The data bytes for the first 2K of addresses are, therefore, read from memory chips 1 and 2 only. When the address number reaches 100000000000 (0800 in hexadecimal), the A11 line goes to 1, so that the chip-enable pin of memory chips 1 and 2 goes high, putting the data outputs of those chips into the floating state. The inverter action ensures that the chip-enable pin of memory chips 3 and 4 will be low, so that the next 2K of address numbers are read from these chips only.

#### **Partial Control**

This system is only a partial solution, though, because the decoding does nothing about lines A12 to A15. As the program count proceeds, these lines will be activated and if nothing is attached to them, the memory chips will be controlled purely by the lower lines.

Since the upper four lines can have  $2^4 = 16$  possible addresses on them for any given address on the lines which we're using, the sequence of use of memory can be repeated 16 times.

All this address decoding business, incidentally, applies

equally to ROM or RAM. The only extra complication which is present in RAM chips is the read/write pin which has to be taken to one logic voltage for writing data from the microprocessor to memory and to the other logic voltage for reading data from the memory to the microprocessor. The microprocessor CPU will control such pins directly from its read/write control pin, or pins, which will be indicated on the pinout diagram.

**Any Port In A Storm**

Most microprocessor systems need nothing like the 64K of memory which could be addressed by sixteen address lines. Even a computer with fairly extensive capabilities may use only 16K of RAM, though its ROM and other use of memory addresses can bring the total up to 32 K. All in all, then, there are several address lines floating about if we want to load data into the CPU directly or feed data out. An address-decoded or memory-mapped input/output system makes use of buffers and latches which are controlled by a signal gated out from the address lines.

For example, suppose the ROM and RAM that we use in a system take up a total of 8K. 8K of memory needs addresses up to  $2^{13}$ , so that it uses 13 of the 16 memory lines and there are three left. Now three lines can be used in  $2^3 = 8$  different sets of addresses, of which we have used one set in the 8K of memory addresses. That leaves seven sets of 8K (56K) of addresses which

are spare if the top lines are fully decoded!

We can, for example, choose to use an address such as 36D6, which involves decoding all the address lines, or more simply, use any address which has line A13 high. Normally this would activate the memory, but we can easily arrange things so that when A13 is high, a gate circuit will disable all the memory chips, making use of the chip-enable inputs. That way, any memory address which has line A13 high can be used to activate a buffer and so connect the data lines to a connecting strip. The buffer would also be controlled by the read/write signals to ensure that signals were going in the right direction. A more common type of interface is an eight-bit latch, which holds data temporarily stored until either the CPU or any external circuits can deal with the bits.

**Map Reading**

Memory-mapping is a very common method of making use of the address lines to control inputs and outputs; porting is another. A port is usually a separate IC which is connected to the data lines and also to the control lines of the CPU, though most CPUs use some of the address lines. A typical port or PIO (Peripheral Input/Output) will have one or two sets of input or output pins — the usual eight connections to the data bus, and several (typically six) pins for control signals. It's a one-chip method of obtaining input or output at a time when the memory chips are not being used and because it's a single IC, manufacturers usually load on a lot of extra functions, such as being able to use some bits for inputs and others for outputs simultaneously.

Port ICs are generally designed specifically for one particular CPU, though they are capable of a remarkable number of actions. No two are completely alike and there are always some restrictions on their use as compared to memory mapping. For this reason, memory mapping is used much more.

There's no end to the number of specialised chips which are produced for use with CPUs like the Z80. Even the humble SC/MP has a combined port/memory chip, the INS8154, which almost needs and instruction manual of its own. The units dealt with here are, however, the ones you're most likely to find in smaller systems and, more important, the chips you will use if you start designing your own microprocessor systems. Good Luck!

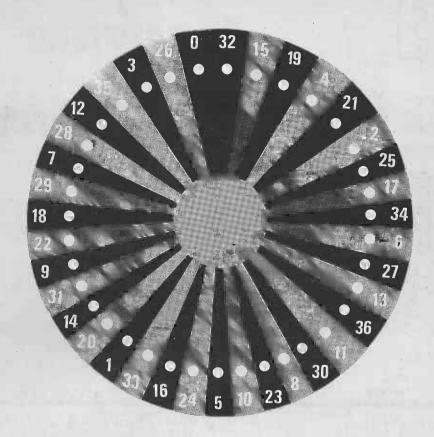

# ROULETTE GAME

This home-casino project is battery powered and has switch-selection of biased (in favour of the house) or unbiased (no house) options. Naturally, the project includes a realistic sound-effects generator.

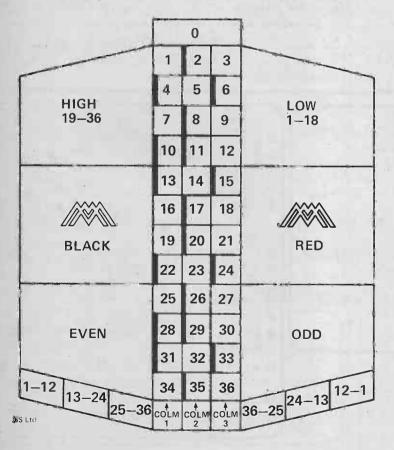

The basic concept of roulette is quite simple. On each spin, the wheel can randomly generate any one of 36 or 37 numbers (1-36 or 0-36). To start a game, each player forecasts (and bets money on) the number at which the wheel will stop by forecasting the number, or the colour of the number (red or black), or any of a variety of characteristics of that number. The wheel is then spun and eventually comes to rest against some randomly determined number, at which point the players with that number are declared winners and are each paid a sum determined by the rules of the game and the magnitudes of their initial bets.

A real-life wheel may generate either 36 or 37 numbers. On a 37-number wheel, the numbers run from 0 to 36, with 0 representing the house. The presence of the 0 biases the game in

favour of the house. On a 36-number wheel there is no zero; the numbers run from 1 to 36 and the game is said to be unbiased. The ETI roulette game has an option for 37 or 36 number operation via a selector switch. The wheel is 'spun' via a pushbutton switch and takes roughly 15 S to come to rest after each initial spin.

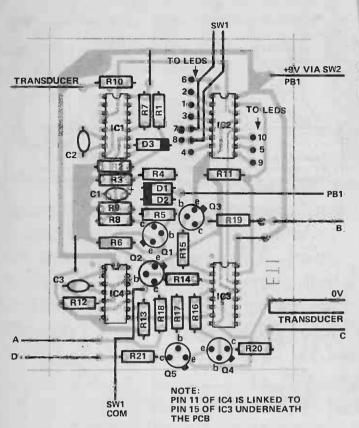

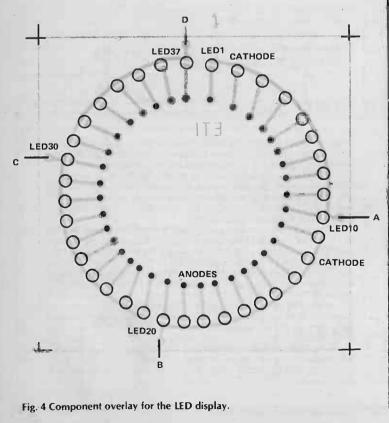

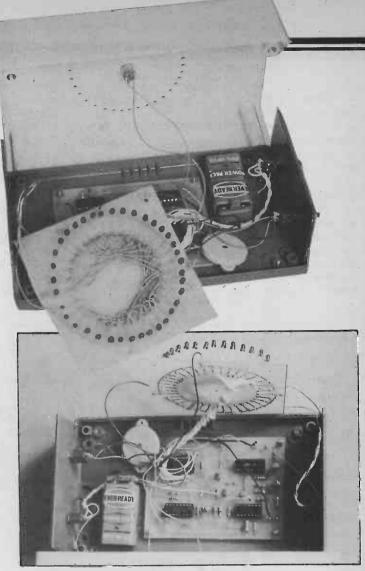

#### Construction

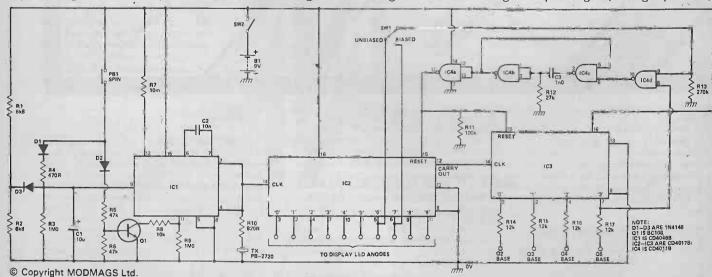

The ETI roulette game is built on two PCBs — one holding most of the electronic circuitry and the other holding the 37-LED display. Construction of the main board shouldn't present any problems. Construction of the display PCB, however, is rather fiddly, since it calls for a great deal of hardwiring between the LEDs (using Veropins) and to the main PCB. When constructing this board, confirm the functioning and polarity of all LEDs before soldering them into position on the PCB. Note that all cathodes go to the outer segments of the PCB ring. All LEDs should be given equal heights (as long as possible).

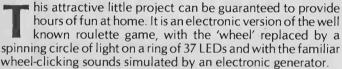

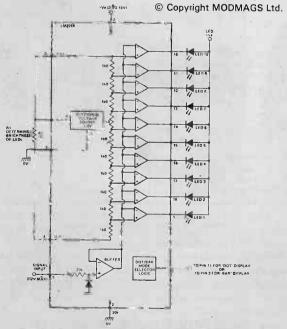

Fig. 1 Main circuit diagram. Biased and unbiased game options can be switch-selected.

When the LEDs are in place, carefully interwire them (on the top side of the PCB) to conform to the main circuit diagram and then make the 10 connections to IC2 (from the underside of the PCB) and the four connections to Q2-Q5 on the main PCB. At this point, wire the two toggle switches and the push-button switch into place, fit the transducer, connect the battery and give the unit a functional test. If the LEDs fail to illuminate correctly, re-check your interwiring.

When all is well, you can fit the two PCBs, etc. into a suitable case. Drill a circle of 37 holes in the top of the case, to coincide with the 37 LEDs and fit the push-button switch in the centre of the circle. The display board can be secured behind the case top by smearing drops of clear adhesive on the sides of the heads of a few of the LEDs and pushing them into the case holes. The project can be finished off by either marking the

roulette wheel artwork on top of the case by hand or by rubbing down a special ETIprint that we have prepared. Note that the numbers marked on the roulette scale do not, in fact, have to coincide with any particular LED numbers.

#### BUYLINES.

Your local component shop should be able to provide you with all the components needed to build the ETI Roulette game. In case of difficulty Ambit International, who advertise with us, will supply the PB-2720 transducer.

Fig. 2 LED display circuitry.

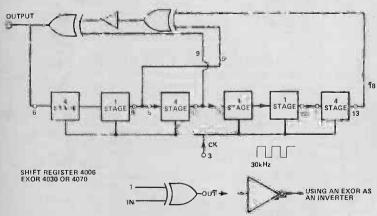

#### **HOW IT WORKS**

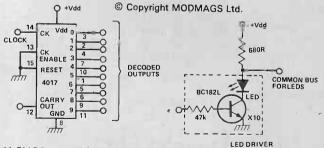

The circuit comprises a clock generator (IC1-Q1) and a multi-stage counter/decoder network (IC2-IC3-IC4) that drives a circle of up to 37 LEDs in the dot mode. The counter/decoder network is deceptively simple. CD4017 decade counter/decoders IC2 and IC3 are wired in series so that IC2 counts in units and IC3 counts in tens when the clock signal is fed to pin 14 of IC2. The '3' output of IC3 and the '6' or '7' output of IC2 are NANDed via IC4d and used to trigger monostable IC4b-IC4c, which generates a 16 uS pulse and resets both counters to zero via IC4a each time that these two outputs go high simultaneously. The cascaded counters thus divide the clock signal by a fixed ratio of 36 or 37 (depending on the setting of SW1) and effectively produce 36 or 37 fully decoded outputs, which are used to sequentially turn on LEDs in the roulette ring or wheel.

The LED ring comprises three segments of 10 LEDs and one segment of seven LEDs. The anode drive to all LEDs is controlled by IC2 (the units counter), but the cathode paths of the LEDs are controlled by IC3 (the tens counter) via transistors Q2 to Q5. Thus, on the '15' count the '5' output of IC2 goes high and Q3 is driven on via the '1' output of IC3, so that only LED 15 illuminates. This multiplexing technique enables the 37 LEDs to be driven by fairly simple counter/decoder circuitry, which turns the LEDs on sequentially and produces an apparently-rotating ring of light.

The clock generator circuitry is delightfully cunning and is

designed around the VCO section of a 4046B phase-locked loop chip. The frequency of this oscillator is controlled by the value of C2, the resistance between pin 11 and ground and the voltage on pin 9. Slight bias is applied to the VCO by R7 to ensure that the VCO frequency falls to zero when the pin-9 voltage is reduced to zero. The output of the VCO is available at pins 3-4 and is fed directly to the input of IC2 and by R10 to the transducer (Tx), which produces a click sound each time a clock transition is generated.

The VCO circuit operates as follows. When PB1 is closed, pin 9 of IC1 is pulled high via D1-R4 (thus charging C1 to maximum voltage) and Q1 is turned on by DR-R5, thus connecting R8 between pin 11 of IC1 and ground. Under this condition the VCO operates at a few tens of kilohertz and causes the LED display to appear to spin at a rate of several hundred revs per second, so that the number of spins cannot be predicted by PB1.

When PB1 is released Q1 turns off, so that only R9 is connected between pin 11 and ground and C1 abruptly discharges to half-supply volts through D3-R2. Under this condition the wheel rotates at an initial visible rate of about two revs/sec. From this moment, C1 discharges exponentially through R3, so the pin-9 voltage and the wheel spin rate steadily decrease until, after about 15 S, the VCO stops generating and the wheel comes to rest. The operating sequence is then complete.

Fig. 3 Component overlay of the main circuit board. Don't forget the under-board link.

Inside the box (right). Construction of the front panel LED display is greatly simplified by our LED board (see Fig.4).

Fig. 4 Component overlay for the LED display.

PARTS LIST

| Resistors all 1/4 V             | V 5%                                                    |

|---------------------------------|---------------------------------------------------------|

| R1, 2                           | 6k8                                                     |

| R3, 9                           | 1M0                                                     |

| R4                              | 470R                                                    |

| R5, 6                           | 47k                                                     |

| R7                              | 10M                                                     |

| R8                              | 10k                                                     |

| R10                             | 820R                                                    |

| R11                             | 100k                                                    |

| R12                             | 27k                                                     |

| R13                             | 270k                                                    |

| R14, 15, 16, 17                 | 12k                                                     |

| R18, 19, 20, 21                 | 1k0                                                     |

| Capacitors                      |                                                         |

| C1                              | 10u 35 V tantalum                                       |

| C2                              | 10n polycarbonate                                       |

| C3                              | 1n0 polycarbonate                                       |

| Semiconductors                  |                                                         |

| IC1                             | CD40468B                                                |

| IC2, 3                          | CD4017B                                                 |

| IC4                             | CD4011B                                                 |

| Q1, 2, 3, 4, 5                  | BC108                                                   |

| D1, 2, 3                        | 1N4148                                                  |

| LED1-37                         | 0.125" diameter (Red)                                   |

| Miscellaneous                   |                                                         |

| PB1                             | momentary push button Vero case (order code 202-21031G) |

| SW1, 2                          | SPDT miniature toggle                                   |

| 1 off PP3 9 V ba<br>Tx1 PB-2720 | ittery                                                  |

Fig. 5 Design for the 37 LED display.

Fig. 6 Table layout and details of the betting odds.

BETTING ODDS:

35:1 ANY SINGLE NUMBER

17:1 ANY TWO ADJACENT NUMBERS ON THE TABLE

11:1 ANY THREE HORIZONTALLY ADJACENT NUMBERS ON THE TABLE

8:1 ANY FOUR ADJACENT NUMBERS ON THE TABLE

5:1 ANY TWO ADJACENT HORIZONTAL ROWS ON THE TABLE

2:1 ANY OF THE SIX INDICATED BLOCKS OR COLUMNS OF 12 NUMBERS

1:1 HIGH,LOW,EVEN,ODD,BLACK OR RED

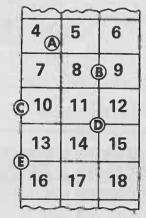

A. A BET ON A SPECIFIC NUMBER. (ODDS 35:1)

B. A BET ON TWO ADJACENT TABLE NUMBERS (ODDS 17:1)

C. A BET ON THREE HORIZONTALLY ADJACENT TABLE NUMBERS (ODDS 11:1)

D. A BET ON FOUR ADJACENT TABLE NUMBERS.(ODDS 8:1)

E. A BET ON TWO ADJACENT ROWS OF TABLE NUMBERS (ODDS 5:1)

Fig. 7 There's more than one way of placing a bet.

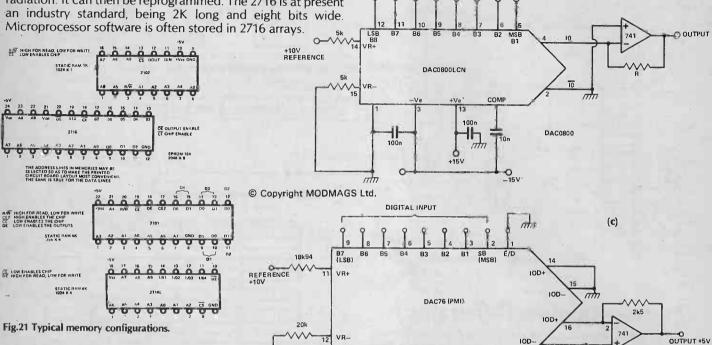

# DOLBY C-REVOLUTION OR REHASH?

lan Graham reports on the next generation of noise reduction systems from Dolby Laboratories — Dolby C.

f you're in the habit of reading the blurb on tape cassettes, then you're already familiar with the double D trademark of Dolby Laboratories. Perhaps you even have a posh tape deck with a Dolby selector switch. The system universally used in consumer hi-fi now is Dolby B, providing 10 dB of noise reduction above about 4 kHz. Tape noise has already been reduced a great deal — try listening to your favourite Osmonds tape with the Dolby system switched out. The noise tends to destroy the full esoteric impact of Littly Jimmy's lethal lyrics. Come to think of it. . . . .

#### $A, B, C, \ldots$

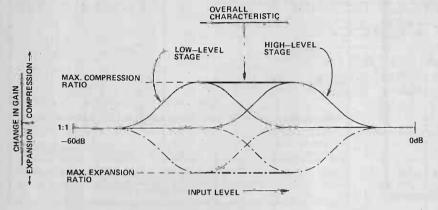

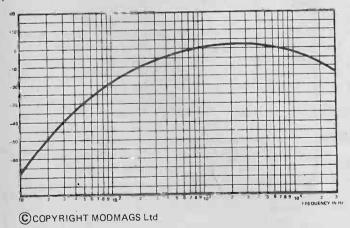

Dolby C, as the new system is called, will provide 20 dB of noise reduction above about 1 kHz (Fig. 1). The obvious question is — is it just a stretched version of Dolby B? The operation of the two systems is certainly similar. Dolby C uses existing B-type chips. However, a stretched Dolby B giving 20 dB reduction was found to be impractical. The subjectively much cleaner high frequencies revealed a muddy mid-frequency band at higher listening levels. Hence, the new C-type design achieves it full 20 dB reduction above about 1 kHz. It reaches the maximum B-type reduction of 10 dB at only 300 Hz, offering (subjectively) uniform noise reduction across the whole audio band.

#### **Design Points**

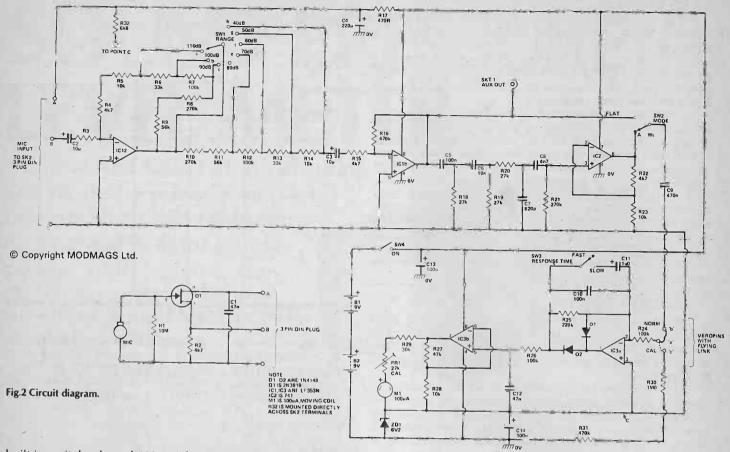

If you already know how Dolby B works, then the new system holds few surprises for you. In principle, lower level high frequencies are selectively boosted just before the signal is recorded onto the tape. When the encoded tape is played back, the boosted frequencies are attenuated back to where they were originally, reducing the noise added by the recording process.

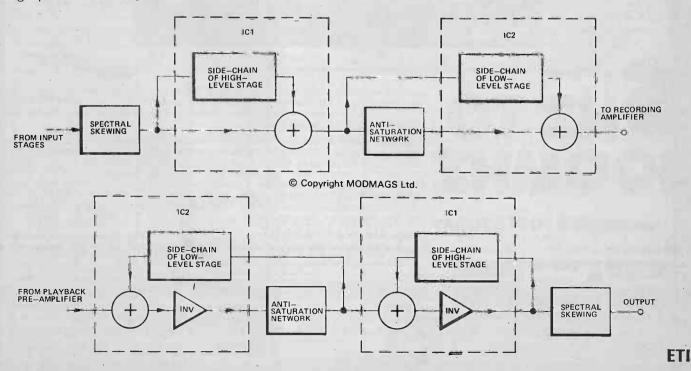

Signal processing is tackled in two stages in series, each supplying 10 dB of compression during recording and of expansion during playback (Fig. 2). The high level stage (Fig. 3) is sensitive to signals at about the same levels as are processed by a Dolby B network. The low level stage deals with signals in the previously unprocessed frequencies below the Dolby B region. Although the two stages are working together, at no time is a signal subjected to a full 20 dB compression or expansion with its accompanying undesirable side effects and inaccurate signal control.

#### **Noise News**

In addition, the C-type system incorporates a number of further innovations. Two are shown in Fig. 3. The anti-saturation and spectral skewing networks are frequency response modifications to reduce encode/decode errors, upper-middle and high frequency losses and intermodulation distortion. The end result is a new noise reduction system which is at least as free of side effects as the B-type system and just as practical in everyday use.

#### **Compatibility**

There's no point in producing a new noise reduction system if it is not compatible with existing tapes and hardware, so Dolby C has been designed with the universal use of Dolby B in mind. Recordings made using a C-type processor can be replayed on a B-type cassette machine with acceptable results and on machines without any noise reduction system. So, you don't have to rush out and buy a new tape deck tomorrow. Prototype C-type machines have already been on show across the Atlantic, so production models from all the major hi-fi manufacturers shouldn't be far behind. Because one half of the new system is essentially a B-type processor, tape decks can easily incorporate push-button selection of either B or C-type processing. Perhaps the first generation of cassette machines will feature this until Dolby C is as universal in use as its predecessor. Professional C-type encoders are being produced, so Cencoded cassettes will be available in the shops too. Dedicated Dolby C chips should be in production in about a year.

#### How Much?

Good question. Dolby C is bout 2½ times as complex as existing B-type circuitry, so, in terms of component cost only, a C-type NR processor will be about 2½ times as expensive as existing units. In addition, Dolby C demands first class electrical and mechanical performance from the recorder incorporating it, including very low noise levels in the circuitry surrounding the processor. I guess you've heard the moral before — it pays to buy the best you can afford. The new system will be most useful for recording material of a wide dynamic range to be replayed at very loud listening levels.

10000

Oost 15 B-TYPENR B-TYPENR B-TYPENR With cant 10 B-TYPENR B-TYPENR

Fig. 1 These curves show the maximum low level boost imparted by both C-type and B-type noise reduction in the absence of high frequency signals. Dolby C NR imparts more boost in recording and more cut in playback, thus providing more noise reduction. The effect also extends about two octaves lower with the C-type NR to maintain subjectively uniform noise levels across the spectrum. Processing at very low frequencies is not required with either system because low frequency noise is insignificant in properly engineered cassette recorders.

© Copyright MODMAGS Ltd.

Fig. 2 The two-level, two-stage configuration. At no time is the signal subject to significantly more than the maximum compression or expansion effect of a single stage. Yet the effects of the two stages multiply (add in decibels) to achieve the full 20 dB of processing required for C-type noise reduction.

#### **Revolution Or Rehash?**

The truth probably lies somewhere between the two extremes. Dolby C represents the next stage in the evolution of noise reduction. It employs a new approach (dual level processing) to noise reduction yet it is fully compatible with existing tapes and hardware.

Fig. 3 Block diagram of the Dolby C noise reduction system showing the encoder (below) and decoder (bottom).

## **POLYSYNTH**

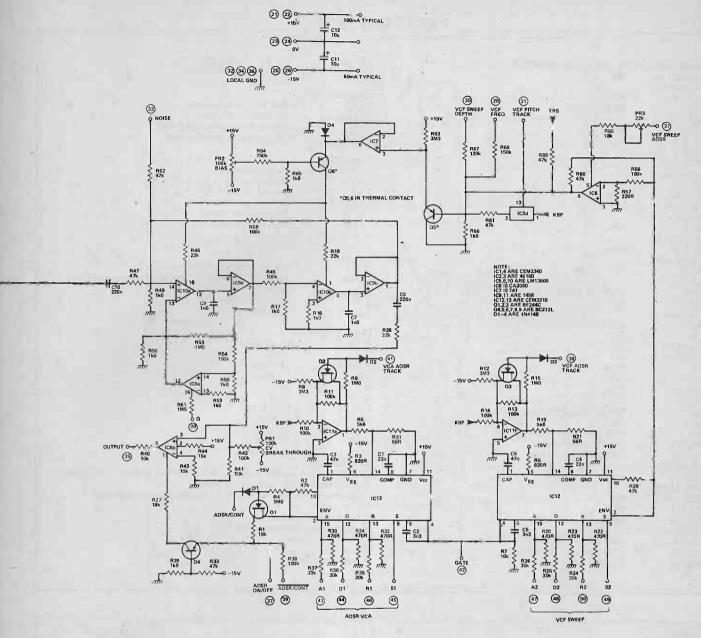

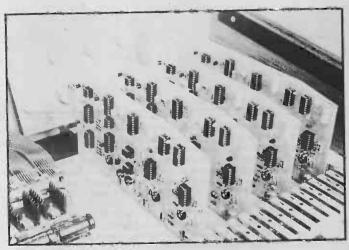

Part 3 of the Polysynth describes the voice boards and power supply, and shows how the four-voice expander unit may be built from the basic boards. Design and development by Tim Orr.

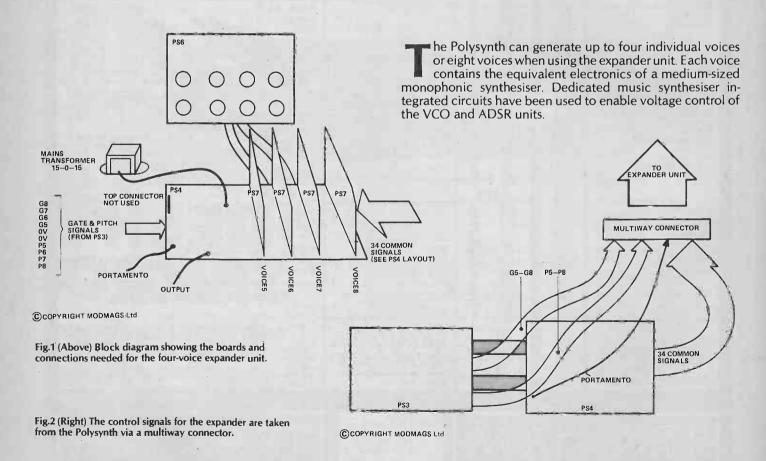

#### **Expander Unit**

In order to play eight voices, an expander unit is needed. (Fig. 1). It is self-powered and consists of a PS4 mother board, four PS7 voice boards, a PS6 panel board and a mains transformer. The tuning and alignment is exactly the same as for the first four voices. The expander unit is driven from a large multiway connector (Fig. 2). All 34 common signals plus the portamento are wired up on a one-to-one basis, that is vibrato to vibrato, transpose to transpose, etc. The independent pitch and gate signals are obtained separately from PS3 (don't forget to insert the extra sample and hold ICs on PS3). The output of the expander unit and the Polysynth have to be mixed externally.

#### **BUYLINES**

Powertran Electronics can supply a complete kit of parts for each option of the Transcendent Polysynth.

voice £320 £368 2 voices £464 3 voices

£295 4 voice expansion kit All prices are exclusive of VAT. Powertran Electronics, Portway In-

dustrial Estate, Andover, Hants SP10 3NM.

Fig.3 Block diagram of one voice of the Polysynth (PS7).

(C) COPYRIGHT MODMAGS Ltd

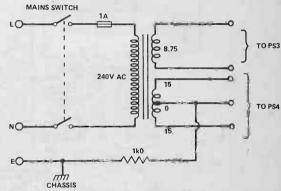

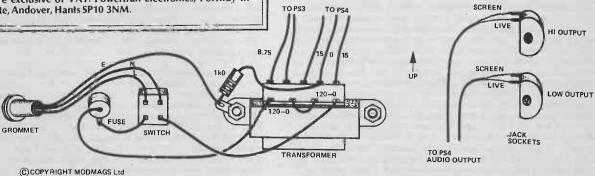

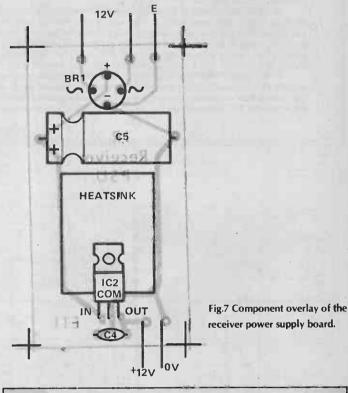

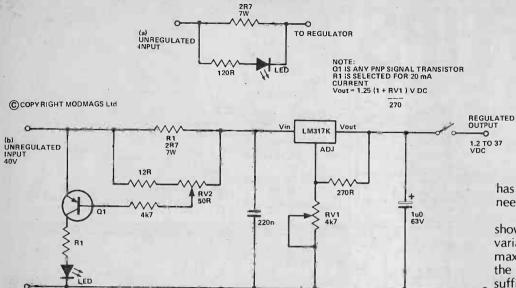

Fig.4 Circuit diagram of the power supply.

Fig.5 Wiring details for the components that mount on the back panel.

TO PS3

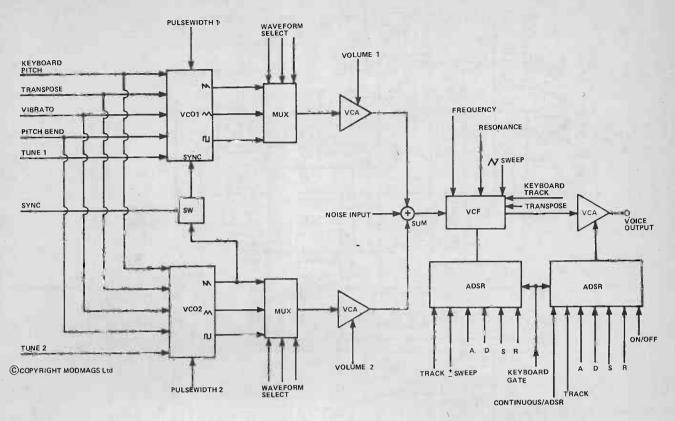

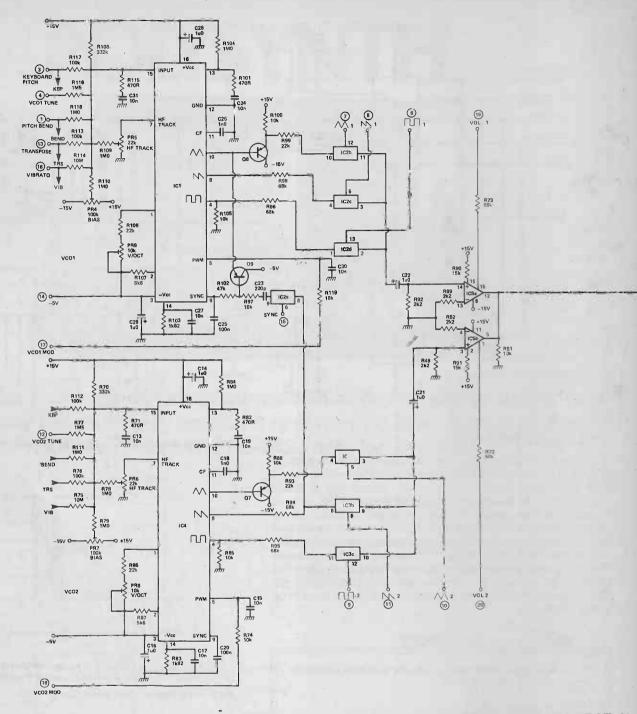

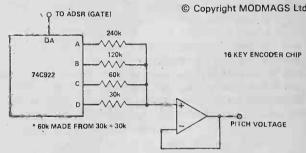

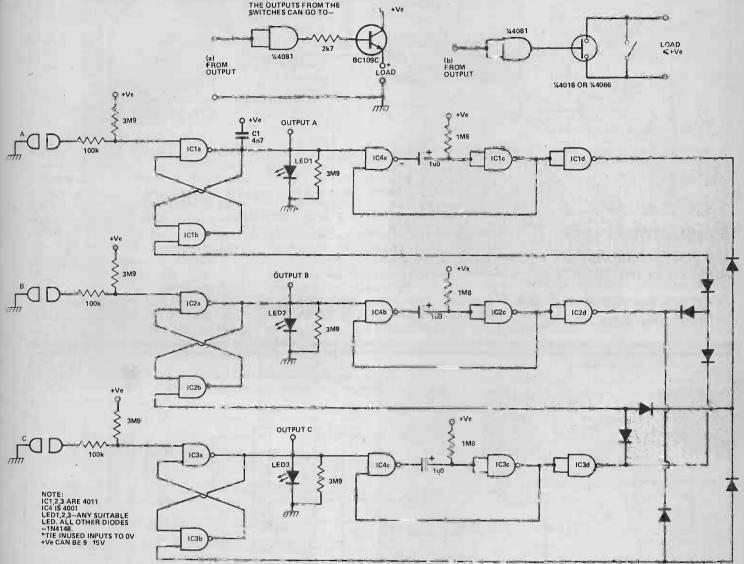

#### **HOW IT WORKS: PS7**

The VCOs are Curtis CEM3340 devices (IC1,4). These can generate three output waveforms; a ramp, a triangle and a square wave with a voltage-controlled mark/space ratio. The VCO has an internal exponentiator that converts the linear input voltages of 1 V per octave into musical intervals of one octave. The frequency control input is a virtual earth amplifier and so other frequency control voltages may be mixed resistively into this point. The device also has an internal temperature compensation circuit that minimises frequency and scale factor temperature drift problems.

factor temperature drift problems.

It is a very difficult task to produce a bank of VCOs that will track over a wide musical range (about seven-and-a-half octaves in this case) and which will not drift in pitch relative to each other or against absolute frequency. The CEM3340 devices perform this task as well as any other VCOs currently available. To ensure that the VCOs remain in tune when they are transposed it is necessary to match the 'transpose' and 'keyboard voltage' resistor pairs. These resistors are R117 and R113 (for VCO1) and R112 and R76 (for VCO2). The resistors

used are 0.1% tolerance and if possible they should be matched to 0.01%. Also, be very careful when inserting these resistors. Use pliers to hold the wire next to the resistor body when bending it and don't take too long soldering it in Thermal and mechanical stress can change the resistor value.

An analogue switch (IC2,3) is used to select the output waveforms from the VCOs. These signals are fed to IC5 which is used as a voltage-controlled amplifier. The VCO outputs are mixed together and fed into the VCF. This is known as a two-pole state variable lowpass filter with exponential frequency control and voltage-controlled resonance (Fig. 6). Two OTAs (IC10) are used as variable gain integrators. The gain is linearly proportional to the  $I_{ABC}$  current flowing into pins 1 and 16 of IC10. The filter cut-off frequency is linearly proportional to this gain. Therefore, a change in the  $I_{ABC}$  current will result in a similar change in the VCF frequency. Transistors Q5,6 convert the transpose, keyboard, frequency pot and sweep voltages into an  $I_{ABC}$  current (the

© Copyright MODMAGS Ltd.

Fig.6 Complete circuit diagram for one voice of the Polysynth (PS7). The ringed numbers refer to the edge connector sockets (see Fig.7).

collector current of Q6) which is exponentially proportional to the sum of these as seen at the base of Q5. IC8 (pins 12, 13,14,16) is used to voltage-control the Q factor of the filter. When the Labc current to the Q factor of the filter. device (pin 16) is zero, the Q factor is determined by R50 and R53, resulting in a high Q response. IC8 provides a negative feedback route so that as its IABC current is increased, more negative feedback is applied. This damps the filter which lowers the Q factor.

It is possible to sweep the filter with an ADSR waveform via IC6. When the ADSR sweep pot (molex pin number 27) is at 0 V, PR3 is adjusted so that an ADSR waveform produces no movement at IC6, pin 6. When the ADSR sweep pot is then set to -15 V, IC6 is turned off and so an ADSR waveform will generate a positive change at pin 6 via resistor R60. When the ADSR pot is set to +15 V, IC6 is turned fully on

so the ADSR waveform generates a negative change at pin 6 This circuit generates the characteristic synthesiser-swept filter sound.

There are two ADSR units, IC12, 13. These are Curtis CEM3310 devices. They have a 50,000:1 time-constant control range, with voltage control of all parameters and a true RC exponential envelope shape. Also, the voltage control of the time-constants is exponential. Every 18 mV increase at pins 15, 12 and 13 halves the A,D and R time-constants respectively. The time-constants of the ADSR units can also be transposed by injecting a voltage at pin 14. A + 18 mV increase at this point will double the time-constants. All natural instruments have attack and decay times that are frequency-clasted. The ten natural respectively. related. The top note on a piano dies away very quickly but the bottom note continues for a long time. It is possible to simulate this in the voice unit by injecting the keyboard pitch voltage into pin 14 of the CEM3310. This ADSR pitch tracking may be turned off by using FETs Q2 and Q3 to short out the keyboard pitch voltage.

IC12 is used to provide a sweep voltage for the VCF; IC13 generates the amplitude envelope for the output VCA (IC8 pins

1,2,3,4,5).

#### PARTS LIST: PS7

|               | / 5% unless otherwise stat<br>18k          |

|---------------|--------------------------------------------|

| R1,27,80      | IOK                                        |

| R2,33,47,60,  | 22k                                        |

| 62,102        |                                            |

| R3,6          | 820R                                       |

| R4,9,15,53,   | 4440                                       |

| 78,109        | 1M0                                        |

| R5,19         | 5k6                                        |

| R7,40,41,43,  |                                            |

| 51,74,85,88,  |                                            |

| 97,100,105,   | 401.                                       |

| 119           | 10k                                        |

| R8,12,63      | 3M3                                        |

| R10,11,13,14, |                                            |

| 38,42,45,54,  | 1001                                       |

| 56,58         | 100k                                       |

| R16,17,39,49, | 41.0                                       |

| 50,55,59      | 1k0                                        |

| R18,28,46,93, | ant.                                       |

| 99            | 22k                                        |

| R20,22,23,30, | 470R 2% metal oxide                        |

| 32,34         |                                            |

| R21,31        | 56R                                        |

| R24,25,26,35, | 30k 2% metal oxide                         |

| 36,37         | 4k7                                        |

| R29           | 4K7<br>15k                                 |

| R44,90,91     |                                            |

| R48,52,89,92  | 2k2                                        |

| R57           | 220R                                       |

| R61,77,116    | 1M5                                        |

| R64           | 750k                                       |

| R65           | 1k8                                        |

| R66           | 1k0 2% metal oxide                         |

| R67           | 120k<br>150k 2% metal oxide                |

| R68           |                                            |

| R69,81        | 47k 2% metal oxide<br>332k 0.5% metal film |

| R70,108       | 332k U.5% metal film                       |

| R71,82,101,   | 4700                                       |

| 115           | 470R                                       |

| R72,73,94,95, | 601                                        |

| 96,98         | 68k                                        |

| R75,114       | 10M                                        |

| R76,112       | 100k 0.1% metal film                       |

| R79,84,104,   |                                            |

| 110,111,118   | 1M0 2% metal oxide                         |

| R83,103       | 1k82 0.5% metal film<br>22k 2% metal oxide |

| R86,106       |                                            |

| R87,107            | 5k6 2% metal oxide                                        |

|--------------------|-----------------------------------------------------------|

| R113,117           | 100k 0.1% metal film                                      |

| K113,117           | 100k 0:170 Hickar min                                     |

| Potentiometers     |                                                           |

|                    | 100k horizontal preset                                    |

| PR1,2              | 22k horizontal preset                                     |

| PR3,5,6            | 100k cermet horizontal preset                             |

| PR4,7              | 10k multiturn cermet preset                               |

| PR8,9              | Tok multiturn cerniet preset                              |

|                    |                                                           |

| Capacitors         | 00 1 1 -1                                                 |

| C1,4               | 22n polycarbonate                                         |

| C2,5               | 3n3 ceramic                                               |

| C3,6               | 47n polycarbonate                                         |

| C7,9               | 1n0 polycarbonate                                         |

| C8,10              | 220n polycarbonate                                        |

| C11,12             | 10u 16 V tantalum                                         |

| C13,15,17,19,      |                                                           |

| 24,27,30,31        | 10n ceramic                                               |

| C14,16,21,22,      |                                                           |

| 28,29              | 1u0 35 V tantalum                                         |

| C18,26             | 1n0 polycarbonate (or Mullard ceramic multilayer          |

| C10,20             | for higher stability)                                     |

| C20,25             | 100n polycarbonate                                        |

| C20,23             | 220p ceramic                                              |

| C23                | 220p cerame                                               |

| Semiconductors     |                                                           |

|                    | CEM3340                                                   |

| IC1,4              | 4016B                                                     |

| IC2,3              | ** **=                                                    |

| IC5,8,10           | LM13600                                                   |

| IC6                | CA3080                                                    |

| IC7                | 741                                                       |

| IC9,11             | 1458                                                      |

| IC12,13            | CEM3310                                                   |

| Q1,2,3             | BF244C                                                    |

| Q4,5,6,7,8,9       | BC212L                                                    |

| D1-4               | 1N4148                                                    |

|                    |                                                           |

| Miscellaneous      |                                                           |

| PCB PS7, 4 off 8   | 3 pin DIL sockets, 2 off 14 pin DIL sockets, 7 off 16 pin |

| DII sockets 50     | ff 10-way Molex sockets.                                  |

| Transformer wit    | th 16-0-16 and 0-8.75 tappings (Powertran special)        |

| Mainsswitch        |                                                           |

| Mains lead and     | grommet                                                   |

|                    | fuseholder (1 A)                                          |

| 2 off 1/4" jack so |                                                           |

| 1k0 resistor       | CRCIS                                                     |

|                    | mohe                                                      |

| 36 instrument k    | IIODŽ                                                     |

|                    |                                                           |

Next month: We conclude the Polysynth project with full setting up and test details.

Fig.7 Component overlay for the PS7 voice board. Take care with the orientation of the ICs, especially IC1 and IC4. One corner of the board is cut off to avoid fouling the panel boards.

# Henry Budgett warms his soldering iron in the glowing coals of the office fire, dabs a spot of flux here and there and sets about building Heathkit's H8 computer kit.

ne of the best ways to get to grips with a microcomputer is to actually build one for yourself. Whilst the sheer complexity of this operation may seem to be beyond the average skills of an electronics enthusiast, the recent trends in personal computers has brought about a large number of micros that are available in kit form. Among the names that spring to mind are NASCOM, Acorn and Tangerine. One of the biggest electronic kit makers is Heathkit and, not surprisingly, they have a computer or two among their range. I have chosen to take their H8 computer as the basis of the next few parts of this series and I will actually build a complete system out of the various component parts that we have been discussing over the last few months.

#### **System Choice**

The selection of the H8 is based on two main points. It is supplied with the most incredibly detailed documentation, which is also available seperately and it's about the only personal computer system I could find that could be broken down into the component parts of CPU, memory, I/O and control.

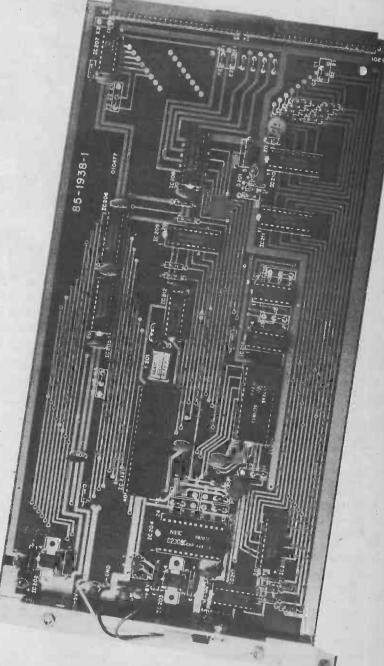

Certain parts of the system are supplied ready built regardless of whether you buy the kit or not. The CPU card and the 16K memory card are both built — for a good reason. The kit is by no means a simple one. It took me three very late evenings to build, but it is a tribute to the designers and the writers of the instruction books that it worked first time. Under normal circumstances I would have allowed a complete weekend for the construction of the main unit but editorial deadlines decided otherwise!

The basic kit consists of the box, the power supply, the

motherboard, the front panel controls and the ready-built CPU card. The manuals cover every possible apsect of the construction and possible fault-finding that you will be likely to need. The only possible quirk is that you will have to buy at least one memory card at the same time as you buy the kit or it simply won't work — frustrating for you, but ideal for me as I wanted a system made of spearate parts.

#### In Bits

If you have been following the series from the very beginning you will know that we can break a computer down into a number of parts — the CPU, the memory and the I/O. Whilst this is fine from a general point of view, there are other vital parts that need to be taken into account.

The power supply is a vital component and, in the H8, is of a distributed load type. The mains is transformed down to  $\pm$  18 V and  $\pm$  8 V. These voltages are supplied through the bus to each card in the system. The card carries voltage regulators for each required power line and thus each card draws the power it needs in regulated form. Some other systems use a regulated power supply which provides a constant supply of exact voltages.

The advantages of the distributed load system are that the main driving line, in our case +8 V, will drop in voltage as the current drawn from it increases. This apparent failing is, in fact, an advantage, because the thermal output from the on-board regulator is directly proportional to the excess voltage across them, the lower the supply rail drops towards 5 V, the less heat is produced by each regulator. In fact the heat output will remain roughly constant regardless of the number of cards you have plugged in.

#### **Slot Machine**

The H8 bus is a standard in its own right. It consists of 50 parallel connections between each of the cards that are plugged in, a maximum of eight slots are available. The first slot, the one nearest the front, is dedicated to the front panel control circuits and the last slot is dedicated to the expansion connector. The convention of the bus is such that the CPU is installed in slot two followed by the memory up to a maximum of 64K and then the I/O.

The signals carried by the bus are the address lines, the data lines and the necessary control signals as well as the power. We can break these down further. The 16 address lines are all inverted, that is they are normally at logic 1 and are set to logic 0 when active. The eight data bits follow the same convention, but they are capable of bi-directional operation, that is data can be sent and received and they can be isolated to allow processes like DMA (Direct Memory Access) to take place. The control bus consists of the signals and their functions given in Table 1

**Function**

Signal

| 0                                  |                                                                                                                                                              |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>15</sub>    | Tri-state address bus. Normally at logic 1, set to logic 0 when active.                                                                                      |

| $\overline{D_0}$ $\overline{D_7}$  | Tri-state bi-directional data bus. Normally at logic 1, set to logic 0 when active.                                                                          |

| 02                                 | CPU supplied clock signal derived from two-phase master clock.                                                                                               |

| HOLD                               | Input signal from bust that instructs the CPU to enter a hold state, this allows DMA type accesses to occur.                                                 |

| HLDA                               | The acknowledge signal from the CPU to show that it has entered the HOLD state. This signal occurs slightly before the bus assumes the high impedance state. |

| INT <sub>1</sub> -INT <sub>7</sub> | The interrupt request lines. The CPU will only honour the interrupt if the interrupt enable register is set.                                                 |

| RESET                              | Resets the CPU's program counter to location 0, resets the interrupt enable and HLDA register. Does not destroy register contents.                           |

| MEMR, IOR                          | Two control lines than enable READ operations on I/O and memory devices. Derived on the CPU card from DBIN and the appropriate status bit(s) of the CPU.     |

| MEMW, IOW                          | Control lines that enable write operations on I/O and memory. Derived from WR and the appropriate status bit(s) of the CPU.                                  |

| RDYIN                              | An asynchronous bus signal that causes the clock to produce a synchronous READY signal for the CPU.                                                          |

| M1                                 | CPU output to the bus that is set when the CPU is in the fetch cycle of the first byte of an instruction. Often used for synchronisation.                    |

| ROM                                | An input that allows the on-board monitor ROM to be turned off.                                                                                              |

| +8 V                               | Unregulated 10 A supply                                                                                                                                      |

| +18 V                              | Unregulated 250 mA supply                                                                                                                                    |

**Taking Control**

Our basic system consists of a CPU installed on the bus, a power supply unit, an amout of memory and a simple I/O device. As discussed last month this may seem OK, but it requires the magic ingredient of a monitor program to actually do any thing useful.

The H8 uses a true front panel as its basic control device and this is almost unique in the micro world. The usual basic operations may all be performed from a keypad and the corresponding results observed on a set of LED displays. At this point you may be wondering why this is so wonderful. The truth of the matter is that it is really a micro using mini operating principles. Those of you who have had the great good fortune to use the PDP 8 series of computer, especially the PDP 8A, will be instantly at home. The CPU is a conventional 8080A running at 2 MHz, but the displays are in octal, not the usual Hex. To avoid

Table 1 What you get on the bus and what it does. Who needs 100 pins now?

Unregulated 250 mA supply

-18 V

Fig. 1 16 keys but not Hex! The H8 keypad gives both octal entry and monitor control. All registers, memory and I/O functions can be controlled from here.

DUMPS FROM MEMORY TO TAPE

LOADS FROM TAPE INTO MEMORY

any confusion or misunderstanding I will give any relevant addresses in both Hex and octal.

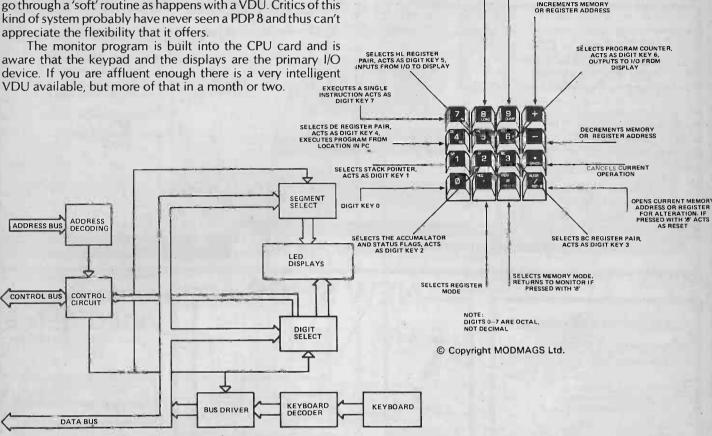

Each of the keys on the keypad can perform a number of functions. Figure 1 gives their layout and corresponding function, but their main advantage is that they give direct access to the memory and register locations without having to go through a 'soft' routine as happens with a VDU. Critics of this kind of system probably have never seen a PDP 8 and thus can't

aware that the keypad and the displays are the primary I/O device. If you are affluent enough there is a very intelligent

Fig. 2 Functional black diagram from the front panel. The keys are only connected to the displays through the monitor program. Any wrong keying is detected and an audio warning is given.

#### Mr. 10%

Because the monitor program has to continually scan the keyboard, some 10% of the CPU's time is taken up by this software. The addresses assigned to the keypad and the display are 360 (F0H7 and 361 (F1H) respectively. The displays require constant updating and the front panel circuitry (see Fig. 2 for a block diagram) issues an interrupt every 2 mS. This interrupt is decoded by the CPU and causes the data on the bus to be set into the I/O buffers and hence displayed on the LEDs. This write signal to the I/O device also causes the MON lamp on the front panel to be lit, indicating that the monitor program is running and hence servicing the front panel. Once the LEDs have been refreshed, the key pressed is locked into the data bus by a read

Once the CPU has 'fired up' it generates an M1 pulse at the start of each machine cycle, as we discussed earlier in this series. This pulse is stretched and used to turn on the RUN lamp. indicating that the processor is 'up-and-running'. This lamp will go out if the processor is in a HOLD or WAIT cycle.

As an indication that a key has been pressed on the keypad. an audio tone is generated. The tone is normally short unless the monitor has accepted the keyed command when it is twice the usual length or when you have made an error when it is maintained for as long as you try to make the error.

#### **Following On**

Having introduced the complete system, next month's exposé will concentrate on the CPU card and how it communicates with the various components of the system through the bus.

A few words of grateful thanks are due to Heathkit for the generous loan of the H8 and its associated parts. Those who are interested in constructing their own can buy the system manuals before you decide on buying the hardware. They cost £4 each and if you do buy the kit this will be deducted from the kit price.

The book that I mentioned, 'The use of microprocessors' by M Aumiaux, deals specifically with the 8080A and the 6800 and covers most of the groundwork needed by first-timers in the micro business. Published by John Wiley & Sons it will cost you £12 in hardback. For the seriously interested there can be no better source of information than Intel. After all, they do make the 8080A and they can be contacted at Dorcan House, Eldene Drive, Swindon, Wiltshire. They have a comprehensive range of both hardware and software manuals and these are well worth obtaining.

## PULSE GENERATOR

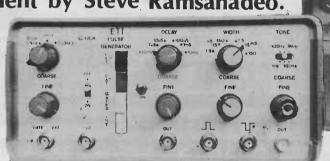

A versatile piece of test gear that can be used as a single or dual pulse generator, a delayed-pulse generator, or a direct or delayed tone-burst generator. Design by Ray Marston. Project development by Steve Ramsahadeo.

Pulse generators have a variety of applications in the modern electronics workshop/laboratory. In its simplest form, a pulse generator can be used for testing the performance characteristics of a common-or-garden digital circuit or for testing the transient responses of AF or RF amplifiers. In a more advanced form, as a delayed-pulse/ tone-burst generator, the instrument can be used for simulating or implementing sophisticated systems such as ultrasonic movement detectors, range-finders, or RADAR systems.

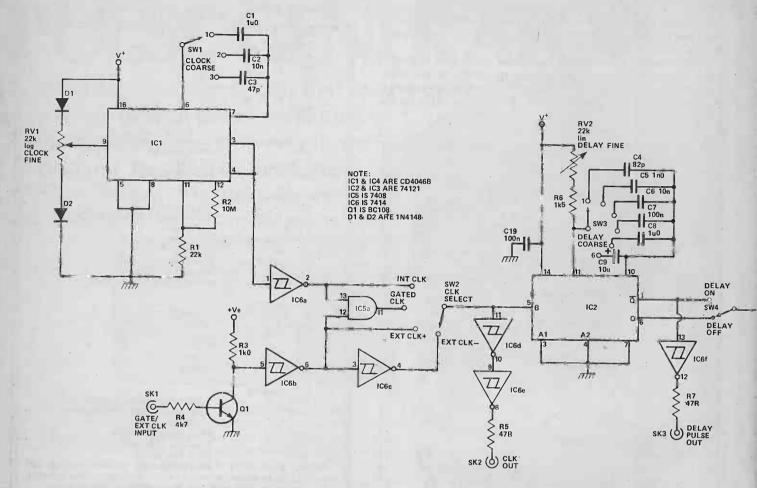

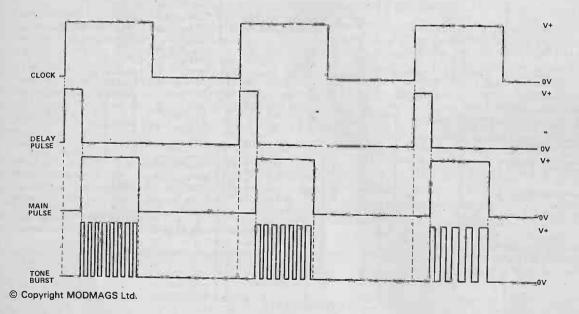

The ETI pulse generator is the most versatile instrument that you could possibly wish for. It has two built-in pulse generators (a delay and a width generator), which can be effectively clocked in parallel or series. When parallel clocking is used, the unit simultaneously generates two independently controlled pulses from each clock pulse. When series clocking is used, the unit generates an output pulse that is delayed from the clock pulse by a period set by the delay generator. The pulse width and delay times are both fully variable over the range 100 nS to 150 mS.

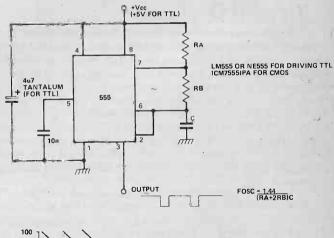

The two pulse generators can be clocked from either internal or external signals. The internal clock generator spans the full range of 0.5 Hz to 500 kHz and can be used directly or can be gated by external signals. The clock signal is made available externally via an output socket.

The delay pulse of the unit is made externally available via a single output socket, while the main width pulse is available in direct and inverted form via a pair of sockets. The main pulse can also be used to trigger and gate an internally generated tone burst signal, which is available via another socket. The tone burst signal is fully synchronised to both the clock signal and the leading edge of the main pulse and is fully variable over the 1 Hz to 1 MHz range.

All outputs of the unit are buffered and short-circuit proof. The outputs are driven by TTL and are fixed-amplitude with typical rise and fall times of about 20 nS. The complete unit consumes a mean current of about 40 mA and can be powered from either a 6 V battery pack or from a mains-derived 5 V regulated supply.

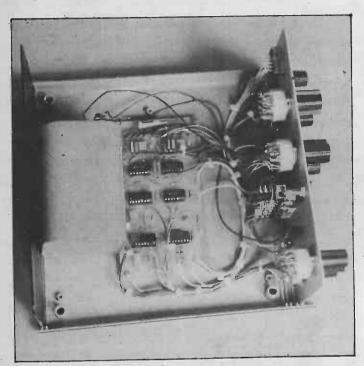

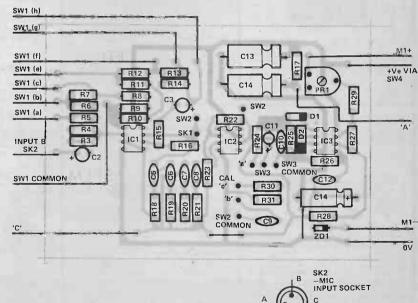

#### Construction

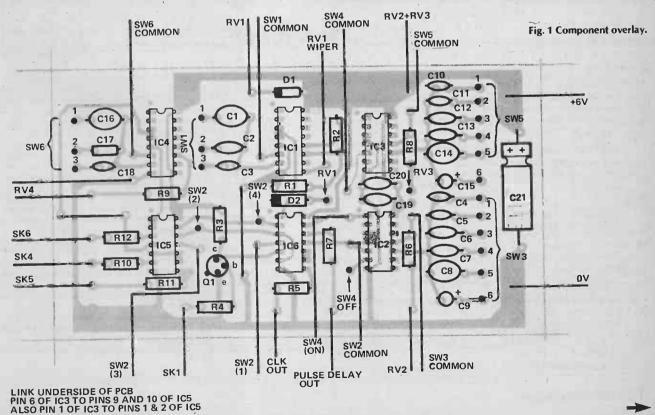

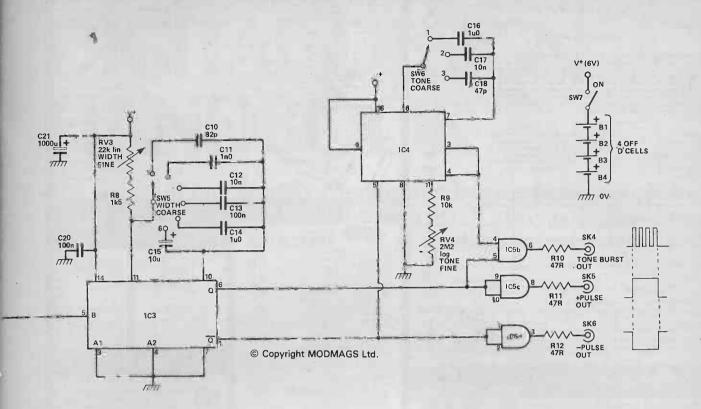

First, wire up the PCB as shown on the overlay, noting the use of a large number of Veropins for making external connections. Take the usual precautions over the polarity of semiconductors and electrolytics. Note that two connecting links are used on the top of the PCB and that, on the underside of the board, insulated wire links are made from pin 1 of IC3 to pins 1-2 of IC5 and from pin 6 of IC3 to pins 9-10 of IC5.

When construction of the PCB is complete, fit it into a suitable case, make the interconnections to all switches/pots/sockets, connect the circuit to a suitable power supply, and test/debug the circuit as follows.

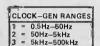

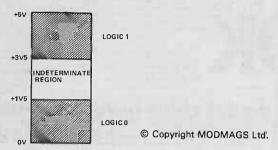

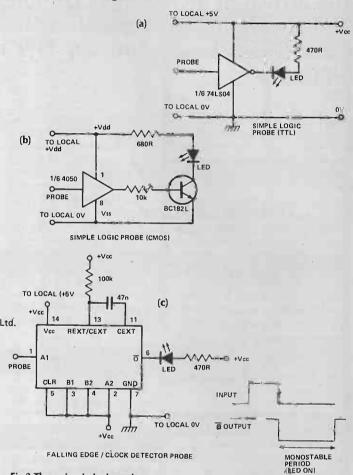

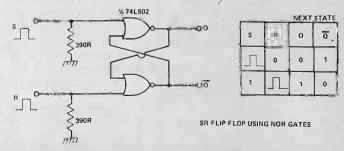

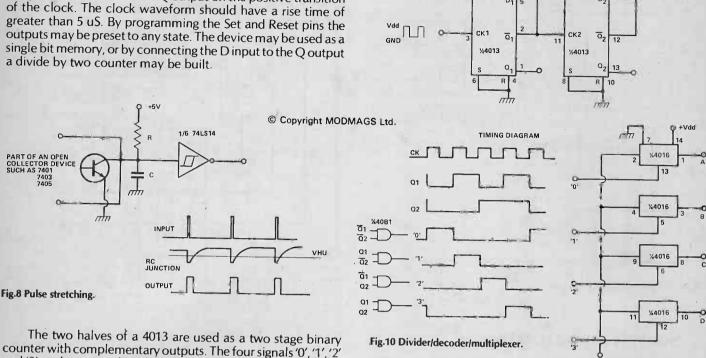

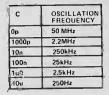

#### **Testing**